Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                             |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 72MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 56                                                                          |

| Program Memory Size        | 2MB (2M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                 |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-QFN (9x9)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b120f2048im64-ar |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.2.4 EM2 and EM3 Power Domains

The EFM32GG11 has three independent peripheral power domains for use in EM2 and EM3. Two of these domains are dynamic and can be shut down to save energy. Peripherals associated with the two dynamic power domains are listed in Table 3.1 EM2 and EM3 Peripheral Power Subdomains on page 13. If all of the peripherals in a peripheral power domain are unused, the power domain for that group will be powered off in EM2 and EM3, reducing the overall current consumption of the device. Other EM2, EM3, and EM4-capable peripherals and functions not listed in the table below reside on the primary power domain, which is always on in EM2 and EM3.

| Peripheral Power Domain 1 | Peripheral Power Domain 2 |

|---------------------------|---------------------------|

| ACMP0                     | ACMP1                     |

| PCNT0                     | PCNT1                     |

| ADC0                      | PCNT2                     |

| LETIMER0                  | CSEN                      |

| LESENSE                   | VDAC0                     |

| APORT                     | LEUART0                   |

| -                         | LEUART1                   |

| -                         | LETIMER1                  |

| -                         | 12C0                      |

| -                         | 12C1                      |

| -                         | 12C2                      |

| -                         | IDAC                      |

| -                         | ADC1                      |

| -                         | ACMP2                     |

| -                         | ACMP3                     |

| -                         | LCD                       |

| -                         | RTC                       |

### Table 3.1. EM2 and EM3 Peripheral Power Subdomains

### 3.3 General Purpose Input/Output (GPIO)

EFM32GG11 has up to 144 General Purpose Input/Output pins. GPIO are organized on three independent supply rails, allowing for interface to multiple logic levels in the system simultaneously. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

### 3.4 Clocking

## 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32GG11. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

### 3.5.6 Pulse Counter (PCNT)

The Pulse Counter (PCNT) peripheral can be used for counting pulses on a single input or to decode quadrature encoded inputs. The clock for PCNT is selectable from either an external source on pin PCTNn\_S0IN or from an internal timing reference, selectable from among any of the internal oscillators, except the AUXHFRCO. The module may operate in energy mode EM0 Active, EM1 Sleep, EM2 Deep Sleep, and EM3 Stop.

#### 3.5.7 Watchdog Timer (WDOG)

The watchdog timer can act both as an independent watchdog or as a watchdog synchronous with the CPU clock. It has windowed monitoring capabilities, and can generate a reset or different interrupts depending on the failure mode of the system. The watchdog can also monitor autonomous systems driven by PRS.

#### 3.6 Communications and Other Digital Peripherals

#### 3.6.1 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous/Asynchronous Receiver/Transmitter is a flexible serial I/O module. It supports full duplex asynchronous UART communication with hardware flow control as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with devices supporting:

- ISO7816 SmartCards

- IrDA

- I<sup>2</sup>S

#### 3.6.2 Universal Asynchronous Receiver/Transmitter (UART)

The Universal Asynchronous Receiver/Transmitter is a subset of the USART module, supporting full duplex asynchronous UART communication with hardware flow control and RS-485.

#### 3.6.3 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup> provides two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud. The LEUART includes all necessary hardware to make asynchronous serial communication possible with a minimum of software intervention and energy consumption.

### 3.6.4 Inter-Integrated Circuit Interface (I<sup>2</sup>C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C bus. It is capable of acting as both a master and a slave and supports multi-master buses. Standard-mode, fast-mode and fast-mode plus speeds are supported, allowing transmission rates from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also available, allowing implementation of an SMBus-compliant system. The interface provided to software by the I<sup>2</sup>C module allows precise timing control of the transmission process and highly automated transfers. Automatic recognition of slave addresses is provided in active and low energy modes.

#### 3.6.5 External Bus Interface (EBI)

The External Bus Interface provides access to external parallel interface devices. The interface is memory mapped into the address bus of the Cortex-M4. This enables seamless access from software without manually manipulating the I/O settings each time a read or write is performed. The data and address lines are multiplexed in order to reduce the number of pins required to interface to external devices. Timing is adjustable to meet specifications of the external devices. The interface is limited to asynchronous devices.

The EBI contains a TFT controller which can drive a TFT via an RGB interface. The TFT controller supports programmable display and port sizes and offers accurate control of frequency and setup and hold timing. Direct Drive is supported for TFT displays which do not have their own frame buffer. In that case TFT Direct Drive can transfer data from either on-chip memory or from an external memory device to the TFT at low CPU load. Automatic alpha-blending and masking is also supported for transfers through the EBI interface.

# 4. Electrical Specifications

## 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on  $T_{AMB}$ =25 °C and  $V_{DD}$ = 3.3 V, by production test and/or technology characterization.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

Refer to 4.1.2.1 General Operating Conditions for more details about operational supply and temperature limits.

| Parameter                                       | Symbol                | Test Condition                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Max load current                                | I <sub>LOAD_MAX</sub> | Low noise (LN) mode, Heavy Drive <sup>2</sup> , T $\leq$ 85 °C | _   | -   | 200 | mA   |

|                                                 |                       | Low noise (LN) mode, Heavy<br>Drive <sup>2</sup> , T > 85 °C   | _   | -   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Medium Drive <sup>2</sup>                 | _   | -   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Light Drive <sup>2</sup>                  | _   | -   | 50  | mA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0         | _   | -   | 75  | μA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3         | _   | -   | 10  | mA   |

| DCDC nominal output ca-<br>pacitor <sup>5</sup> | C <sub>DCDC</sub>     | 25% tolerance                                                  | 1   | 4.7 | 4.7 | μF   |

| DCDC nominal output induc-<br>tor               | L <sub>DCDC</sub>     | 20% tolerance                                                  | 4.7 | 4.7 | 4.7 | μH   |

| Resistance in Bypass mode                       | R <sub>BYP</sub>      |                                                                | -   | 1.2 | 2.5 | Ω    |

### Note:

1. Due to internal dropout, the DC-DC output will never be able to reach its input voltage, V<sub>VREGVDD</sub>.

- 2. Drive levels are defined by configuration of the PFETCNT and NFETCNT registers. Light Drive: PFETCNT=NFETCNT=3; Medium Drive: PFETCNT=NFETCNT=7; Heavy Drive: PFETCNT=15.

- 3. LPCMPBIASEMxx refers to either LPCMPBIASEM234H in the EMU\_DCDCMISCCTRL register or LPCMPBIASEM01 in the EMU\_DCDCLOEM01CFG register, depending on the energy mode.

4. LP mode controller is a hysteretic controller that maintains the output voltage within the specified limits.

5. Output voltage under/over-shoot and regulation are specified with C<sub>DCDC</sub> 4.7 μF. Different settings for DCDCLNCOMPCTRL must be used if C<sub>DCDC</sub> is lower than 4.7 μF. See Application Note AN0948 for details.

| Parameter                                                                              | Symbol               | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption in EM3 mode, with voltage scaling enabled                          | I <sub>EM3_VS</sub>  | Full 512 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO                                     | _   | 3.4  | —   | μΑ   |

| Current consumption in<br>EM4H mode, with voltage<br>scaling enabled                   | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | —   | 0.94 | _   | μA   |

|                                                                                        |                      | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO                                              | —   | 0.56 | —   | μA   |

|                                                                                        |                      | 128 byte RAM retention, no RTCC                                                                         | _   | 0.56 |     | μA   |

| Current consumption in EM4S mode                                                       | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | —   | 0.1  | —   | μA   |

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled | IPD1_VS              | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _   | 0.68 | —   | μΑ   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled | I <sub>PD2_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _   | 0.28 | _   | μΑ   |

### Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.4 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

# 4.1.9 Brown Out Detector (BOD)

| Parameter              | Symbol                     | Test Condition               | Min  | Тур | Мах  | Unit |

|------------------------|----------------------------|------------------------------|------|-----|------|------|

| DVDD BOD threshold     | V <sub>DVDDBOD</sub>       | DVDD rising                  | _    | _   | 1.62 | V    |

|                        |                            | DVDD falling (EM0/EM1)       | 1.35 | —   | _    | V    |

|                        |                            | DVDD falling (EM2/EM3)       | TBD  | _   | _    | V    |

| DVDD BOD hysteresis    | V <sub>DVDDBOD_HYST</sub>  |                              | _    | 18  | _    | mV   |

| DVDD BOD response time | tDVDDBOD_DELAY             | Supply drops at 0.1V/µs rate | _    | 2.4 | _    | μs   |

| AVDD BOD threshold     | V <sub>AVDDBOD</sub>       | AVDD rising                  | _    |     | 1.8  | V    |

|                        |                            | AVDD falling (EM0/EM1)       | 1.62 | _   | _    | V    |

|                        |                            | AVDD falling (EM2/EM3)       | TBD  | _   | _    | V    |

| AVDD BOD hysteresis    | VAVDDBOD_HYST              |                              | _    | 20  |      | mV   |

| AVDD BOD response time | t <sub>AVDDBOD_DELAY</sub> | Supply drops at 0.1V/µs rate | _    | 2.4 |      | μs   |

| EM4 BOD threshold      | V <sub>EM4DBOD</sub>       | AVDD rising                  | _    | _   | 1.7  | V    |

|                        |                            | AVDD falling                 | 1.45 | _   | _    | V    |

| EM4 BOD hysteresis     | V <sub>EM4BOD_HYST</sub>   |                              | _    | 25  | _    | mV   |

| EM4 BOD response time  | t <sub>EM4BOD_DELAY</sub>  | Supply drops at 0.1V/µs rate | _    | 300 | —    | μs   |

## Table 4.11. Brown Out Detector (BOD)

## 4.1.12 General-Purpose I/O (GPIO)

| Parameter                                                                | Symbol                 | Test Condition                                        | Min       | Тур | Max       | Unit |

|--------------------------------------------------------------------------|------------------------|-------------------------------------------------------|-----------|-----|-----------|------|

| Input low voltage                                                        | V <sub>IL</sub>        | GPIO pins                                             | _         |     | IOVDD*0.3 | V    |

| Input high voltage                                                       | V <sub>IH</sub>        | GPIO pins                                             | IOVDD*0.7 | _   | _         | V    |

| Output high voltage relative                                             | V <sub>OH</sub>        | Sourcing 3 mA, IOVDD $\ge$ 3 V,                       | IOVDD*0.8 | _   | _         | V    |

| to IOVDD                                                                 |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sourcing 1.2 mA, IOVDD $\ge$ 1.62 V,                  | IOVDD*0.6 | —   | -         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sourcing 20 mA, IOVDD $\ge$ 3 V,                      | IOVDD*0.8 | _   | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

|                                                                          |                        | Sourcing 8 mA, IOVDD ≥ 1.62 V,                        | IOVDD*0.6 | —   | _         | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

| Output low voltage relative to                                           | V <sub>OL</sub>        | Sinking 3 mA, IOVDD ≥ 3 V,                            | _         | —   | IOVDD*0.2 | V    |

| IOVDD                                                                    |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sinking 1.2 mA, IOVDD $\ge$ 1.62 V,                   | _         | _   | IOVDD*0.4 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                     |           |     |           |      |

|                                                                          |                        | Sinking 20 mA, IOVDD $\ge$ 3 V,                       | _         | _   | IOVDD*0.2 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

|                                                                          |                        | Sinking 8 mA, IOVDD ≥ 1.62 V,                         | _         | _   | IOVDD*0.4 | V    |

|                                                                          |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                   |           |     |           |      |

| Input leakage current                                                    | I <sub>IOLEAK</sub>    | All GPIO except LFXO pins, GPIO<br>≤ IOVDD, T ≤ 85 °C | —         | 0.1 | TBD       | nA   |

|                                                                          |                        | LFXO Pins, GPIO ≤ IOVDD, T ≤<br>85 °C                 | —         | 0.1 | TBD       | nA   |

|                                                                          |                        | All GPIO except LFXO pins, GPIO<br>≤ IOVDD, T > 85 °C | —         |     | TBD       | nA   |

|                                                                          |                        | LFXO Pins, GPIO ≤ IOVDD, T ><br>85 °C                 | —         | _   | TBD       | nA   |

| Input leakage current on<br>5VTOL pads above IOVDD                       | I <sub>5VTOLLEAK</sub> | IOVDD < GPIO ≤ IOVDD + 2 V                            | -         | 3.3 | TBD       | μA   |

| I/O pin pull-up/pull-down re-<br>sistor                                  | R <sub>PUD</sub>       |                                                       | TBD       | 40  | TBD       | kΩ   |

| Pulse width of pulses re-<br>moved by the glitch suppres-<br>sion filter | t <sub>IOGLITCH</sub>  |                                                       | 15        | 25  | 35        | ns   |

## Table 4.20. General-Purpose I/O (GPIO)

| Parameter                                               | Symbol                   | Test Condition                                                                                         | Min | Тур  | Max | Unit |

|---------------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                                       | _   | 60.4 | _   | dB   |

| Noise band limited to 250<br>kHz                        |                          | 500 ksps, single-ended, internal 2.5V reference                                                        | —   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 65.8 | _   | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                                       | —   | 65.3 | _   | dB   |

| Noise band limited to 22 kHz                            |                          | 500 ksps, single-ended, internal 2.5V reference                                                        | —   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                             | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>1.25V reference                                                    | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal<br>2.5V reference                                                     | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                                          | _   | 70.0 | _   | dB   |

| Total harmonic distortion                               | THD                      |                                                                                                        | _   | 70.2 | _   | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                                        | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                                        | TBD |      | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                              | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                                     | TBD |      | TBD | mV   |

| Gain error <sup>5</sup>                                 | V <sub>GAIN</sub>        | T = 25 °C, Low-noise internal ref-<br>erence (REFSEL = 1V25LN or<br>2V5LN)                             | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature<br>range, Low-noise internal refer-<br>ence (REFSEL = 1V25LN or<br>2V5LN) | TBD |      | TBD | %    |

| External load capactiance,<br>OUTSCALE=0                | C <sub>LOAD</sub>        |                                                                                                        | _   | _    | 75  | pF   |

# 4.1.23.2 I2C Fast-mode (Fm)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|-----|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | _   | 400 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 1.3 | _   | _   | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.6 | _   | _   | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 100 | _   |     | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 | _   | 900 | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.6 | _   | _   | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.6 | _   | _   | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.6 | _   |     | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 1.3 | —   | _   | μs   |

## Table 4.32. I2C Fast-mode (Fm)<sup>1</sup>

Note:

1. For CLHR set to 1 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Fast-mode, refer to the I2C chapter in the reference manual.

3. The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

## 4.1.24 USART SPI

# **SPI Master Timing**

## Table 4.34. SPI Master Timing

| Parameter                      | Symbol               | Test Condition                                   | Min                           | Тур | Мах | Unit |

|--------------------------------|----------------------|--------------------------------------------------|-------------------------------|-----|-----|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    | All USARTs except USART2                         | 2 *<br>t <sub>HFPERCLK</sub>  | _   | _   | ns   |

|                                |                      | USART2                                           | 2 *<br>t <sub>HFPERBCLK</sub> | _   | _   | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   | USART2, location 4, IOVDD = 1.8<br>V             | -3.2                          | _   | 6.8 | ns   |

|                                |                      | USART2, location 4, IOVDD = 3.0<br>V             | -2.3                          | _   | 6.0 | ns   |

|                                |                      | USART2, location 5, IOVDD = 1.8<br>V             | -8.1                          | —   | 6.3 | ns   |

|                                |                      | USART2, location 5, IOVDD = 3.0<br>V             | -7.3                          | _   | 4.4 | ns   |

|                                |                      | All other USARTs and locations,<br>IOVDD = 1.8 V | -15                           | —   | 13  | ns   |

|                                |                      | All other USARTs and locations,<br>IOVDD = 3.0 V | -13                           | —   | 11  | ns   |

| SCLK to MOSI <sup>1 3</sup>    | t <sub>SCLK_MO</sub> | USART2, location 4, IOVDD = 1.8<br>V             | -0.3                          | _   | 9.2 | ns   |

|                                |                      | USART2, location 4, IOVDD = 3.0<br>V             | -0.3                          | —   | 8.6 | ns   |

|                                |                      | USART2, location 5, IOVDD = 1.8<br>V             | -3.6                          | —   | 5.0 | ns   |

|                                |                      | USART2, location 5, IOVDD = 3.0<br>V             | -3.4                          | _   | 3.2 | ns   |

|                                |                      | All other USARTs and locations,<br>IOVDD = 1.8 V | -10                           | _   | 11  | ns   |

|                                |                      | All other USARTs and locations,<br>IOVDD = 3.0 V | -9                            | _   | 11  | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>SU_MI</sub>   | USART2, location 4, IOVDD = 1.8<br>V             | 39.7                          | —   | -   | ns   |

|                                |                      | USART2, location 4, IOVDD = 3.0<br>V             | 22.4                          | —   | -   | ns   |

|                                |                      | USART2, location 5, IOVDD = 1.8<br>V             | 49.2                          | _   | _   | ns   |

|                                |                      | USART2, location 5, IOVDD = 3.0<br>V             | 30.0                          | _   | _   | ns   |

|                                |                      | All other USARTs and locations,<br>IOVDD = 1.8 V | 55                            | _   | _   | ns   |

|                                |                      | All other USARTs and locations,<br>IOVDD = 3.0 V | 36                            | _   | -   | ns   |

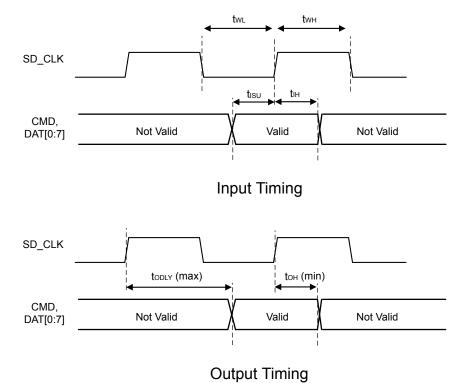

Figure 4.14. SDIO HS Mode Timing

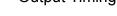

Figure 4.17. SDIO MMC SDR Mode Timing

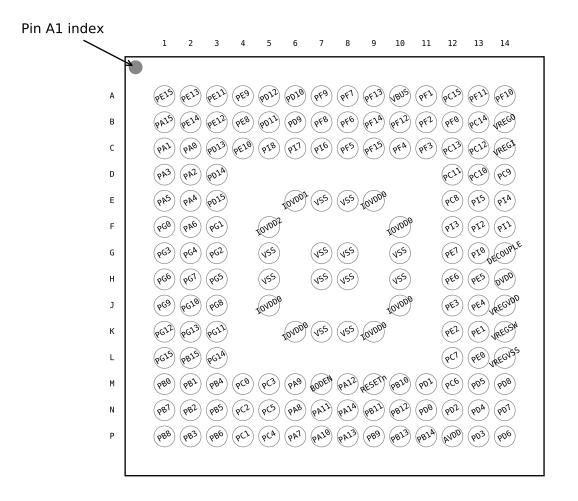

### Figure 5.2. EFM32GG11B8xx in BGA152 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description                                           |

|----------|--------|-------------|----------|--------|-------------------------------------------------------|

| PE15     | A1     | GPIO        | PE13     | A2     | GPIO                                                  |

| PE11     | A3     | GPIO        | PE9      | A4     | GPIO                                                  |

| PD12     | A5     | GPIO        | PD10     | A6     | GPIO                                                  |

| PF9      | A7     | GPIO        | PF7      | A8     | GPIO                                                  |

| PF13     | A9     | GPIO (5V)   | VBUS     | A10    | USB VBUS signal and auxiliary input to 5 V regulator. |

| PF1      | A11    | GPIO (5V)   | PC15     | A12    | GPIO (5V)                                             |

| PF11     | A13    | GPIO (5V)   | PF10     | A14    | GPIO (5V)                                             |

| Pin Name | Pin(s) | Description                                                                                                                                                                                                 | Pin Name | Pin(s)               | Description           |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|-----------------------|

| PB2      | 11     | GPIO                                                                                                                                                                                                        | PB3      | 12                   | GPIO                  |

| PB4      | 13     | GPIO                                                                                                                                                                                                        | PB5      | 14                   | GPIO                  |

| PB6      | 15     | GPIO                                                                                                                                                                                                        | VSS      | 16<br>32<br>58<br>83 | Ground                |

| PC0      | 18     | GPIO (5V)                                                                                                                                                                                                   | PC1      | 19                   | GPIO (5V)             |

| PC2      | 20     | GPIO (5V)                                                                                                                                                                                                   | PC3      | 21                   | GPIO (5V)             |

| PC4      | 22     | GPIO                                                                                                                                                                                                        | PC5      | 23                   | GPIO                  |

| PB7      | 24     | GPIO                                                                                                                                                                                                        | PB8      | 25                   | GPIO                  |

| PA7      | 26     | GPIO                                                                                                                                                                                                        | PA8      | 27                   | GPIO                  |

| PA9      | 28     | GPIO                                                                                                                                                                                                        | PA10     | 29                   | GPIO                  |

| PA11     | 30     | GPIO                                                                                                                                                                                                        | PA12     | 33                   | GPIO (5V)             |

| PA13     | 34     | GPIO (5V)                                                                                                                                                                                                   | PA14     | 35                   | GPIO                  |

| RESETn   | 36     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB9      | 37                   | GPIO (5V)             |

| PB10     | 38     | GPIO (5V)                                                                                                                                                                                                   | PB11     | 39                   | GPIO                  |

| PB12     | 40     | GPIO                                                                                                                                                                                                        | AVDD     | 41<br>45             | Analog power supply.  |

| PB13     | 42     | GPIO                                                                                                                                                                                                        | PB14     | 43                   | GPIO                  |

| PD0      | 46     | GPIO (5V)                                                                                                                                                                                                   | PD1      | 47                   | GPIO                  |

| PD2      | 48     | GPIO (5V)                                                                                                                                                                                                   | PD3      | 49                   | GPIO                  |

| PD4      | 50     | GPIO                                                                                                                                                                                                        | PD5      | 51                   | GPIO                  |

| PD6      | 52     | GPIO                                                                                                                                                                                                        | PD7      | 53                   | GPIO                  |

| PD8      | 54     | GPIO                                                                                                                                                                                                        | PC6      | 55                   | GPIO                  |

| PC7      | 56     | GPIO                                                                                                                                                                                                        | DVDD     | 57                   | Digital power supply. |

| DECOUPLE | 59     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    | PE0      | 60                   | GPIO (5V)             |

| PE1      | 61     | GPIO (5V)                                                                                                                                                                                                   | PE2      | 62                   | GPIO                  |

| PE3      | 63     | GPIO                                                                                                                                                                                                        | PE4      | 64                   | GPIO                  |

| PE5      | 65     | GPIO                                                                                                                                                                                                        | PE6      | 66                   | GPIO                  |

| PE7      | 67     | GPIO                                                                                                                                                                                                        | PC8      | 68                   | GPIO (5V)             |

| PC9      | 69     | GPIO (5V)                                                                                                                                                                                                   | PC10     | 70                   | GPIO (5V)             |

| PC11     | 71     | GPIO (5V)                                                                                                                                                                                                   | PC12     | 72                   | GPIO (5V)             |

| PC13     | 73     | GPIO (5V)                                                                                                                                                                                                   | PC14     | 74                   | GPIO (5V)             |

| PC15     | 75     | GPIO (5V)                                                                                                                                                                                                   | PF0      | 76                   | GPIO (5V)             |

| PF1      | 77     | GPIO (5V)                                                                                                                                                                                                   | PF2      | 78                   | GPIO                  |

| GPIO Name | Pin Alternate Functionality / Description |                                          |                                                                                               |                                                                                        |                                         |  |

|-----------|-------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------|--|

|           | Analog                                    | EBI                                      | Timers                                                                                        | Communication                                                                          | Other                                   |  |

| PB0       | BUSBY BUSAX<br>LCD_SEG32                  | EBI_AD00 #1<br>EBI_CS0 #3<br>EBI_A16 #0  | TIM2_CDTI0 #0<br>TIM1_CC0 #2<br>TIM3_CC2 #7<br>WTIM0_CC0 #5<br>PCNT0_S0IN #5<br>PCNT1_S1IN #2 | LEU1_TX #3                                                                             | PRS_CH4 #1<br>ACMP0_O #5                |  |

| PE0       | BUSDY BUSCX                               | EBI_A00 #2 EBI_A07<br>#0                 | TIM3_CC0 #1<br>WTIM1_CC1 #3<br>PCNT0_S0IN #1                                                  | CAN0_RX #6 U0_TX<br>#1 I2C1_SDA #2                                                     | PRS_CH22 #1<br>ACMP2_O #1               |  |

| PC7       | BUSACMP0Y BU-<br>SACMP0X OPA3_N           | EBI_A06 #0 EBI_A13<br>#1 EBI_A21 #3      | WTIM1_CC0 #3                                                                                  | US0_CTS #2<br>US1_RTS #3<br>LEU1_RX #0<br>I2C0_SCL #2                                  | LES_CH7<br>PRS_CH15 #1<br>ETM_TD0 #2    |  |

| PB1       | BUSAY BUSBX<br>LCD_SEG33                  | EBI_AD01 #1<br>EBI_CS1 #3<br>EBI_A17 #0  | TIM2_CDTI1 #0<br>TIM1_CC1 #2<br>WTIM0_CC1 #5 LE-<br>TIM1_OUT1 #5<br>PCNT0_S1IN #5             | ETH_MIICRS #0<br>US5_RX #2<br>LEU1_RX #3                                               | PRS_CH5 #1                              |  |

| PB2       | BUSBY BUSAX<br>LCD_SEG34                  | EBI_AD02 #1<br>EBI_CS2 #3<br>EBI_A18 #0  | TIM2_CDTI2 #0<br>TIM1_CC2 #2<br>WTIM0_CC2 #5 LE-<br>TIM1_OUT0 #5                              | ETH_MIICOL #0<br>US1_CS #6                                                             | PRS_CH18 #0<br>ACMP0_O #6               |  |

| PB3       | BUSAY BUSBX<br>LCD_SEG20 /<br>LCD_COM4    | EBI_AD03 #1<br>EBI_CS3 #3<br>EBI_A19 #0  | TIM1_CC3 #2<br>WTIM0_CC0 #6<br>PCNT1_S0IN #1                                                  | ETH_MIICRS #2<br>ETH_MDIO #0<br>SDIO_DAT6 #1<br>US2_TX #1 US3_TX<br>#2 QSPI0_DQ4 #1    | PRS_CH19 #0<br>ACMP0_O #7               |  |

| PC6       | BUSACMP0Y BU-<br>SACMP0X OPA3_P           | EBI_A05 #0                               | WTIM1_CC3 #2                                                                                  | US0_RTS #2<br>US1_CTS #3<br>LEU1_TX #0<br>I2C0_SDA #2                                  | LES_CH6<br>PRS_CH14 #1<br>ETM_TCLK #2   |  |

| PB4       | BUSBY BUSAX<br>LCD_SEG21 /<br>LCD_COM5    | EBI_AD04 #1<br>EBI_ARDY #3<br>EBI_A20 #0 | WTIM0_CC1 #6<br>PCNT1_S1IN #1                                                                 | ETH_MIICOL #2<br>ETH_MDC #0<br>SDIO_DAT7 #1<br>US2_RX #1<br>QSPI0_DQ5 #1<br>LEU1_TX #4 | PRS_CH20 #0                             |  |

| PB5       | BUSAY BUSBX<br>LCD_SEG22 /<br>LCD_COM6    | EBI_AD05 #1<br>EBI_ALE #3 EBI_A21<br>#0  | WTIM0_CC2 #6 LE-<br>TIM1_OUT0 #4<br>PCNT0_S0IN #6                                             | ETH_TSUEXTCLK<br>#0 US0_RTS #4<br>US2_CLK #1<br>QSPI0_DQ6 #1<br>LEU1_RX #4             | PRS_CH21 #0                             |  |

| PB6       | BUSBY BUSAX<br>LCD_SEG23 /<br>LCD_COM7    | EBI_AD06 #1<br>EBI_WEn #3<br>EBI_A22 #0  | TIM0_CC0 #3<br>TIM2_CC0 #4<br>WTIM3_CC0 #6 LE-<br>TIM1_OUT1 #4<br>PCNT0_S1IN #6               | ETH_TSUTMRTOG<br>#0 US0_CTS #4<br>US2_CS #1<br>QSPI0_DQ7 #1                            | PRS_CH12 #1                             |  |

| PD5       | BUSADC0Y BU-<br>SADC0X OPA2_OUT           | EBI_A09 #1 EBI_A18<br>#3                 | TIM6_CC1 #7<br>WTIM0_CDTI1 #4<br>WTIM1_CC3 #1<br>WTIM2_CC2 #5                                 | US1_RTS #1<br>U0_CTS #5<br>LEU0_RX #0<br>I2C1_SCL #3                                   | PRS_CH11 #2<br>ETM_TD3 #0<br>ETM_TD3 #2 |  |

| Alternate     | LOCA                                   | TION  |                                                                      |

|---------------|----------------------------------------|-------|----------------------------------------------------------------------|

| Functionality | 0 - 3                                  | 4 - 7 | Description                                                          |

| EBI_A23       | 0: PC0<br>1: PC11<br>2: PH11<br>3: PE5 |       | External Bus Interface (EBI) address output pin 23.                  |

| EBI_A24       | 0: PC1<br>1: PF0<br>2: PH12<br>3: PE6  |       | External Bus Interface (EBI) address output pin 24.                  |

| EBI_A25       | 0: PC2<br>1: PF1<br>2: PH13<br>3: PE7  |       | External Bus Interface (EBI) address output pin 25.                  |

| EBI_A26       | 0: PC4<br>1: PF2<br>2: PH14<br>3: PC8  |       | External Bus Interface (EBI) address output pin 26.                  |

| EBI_A27       | 0: PD2<br>1: PF5<br>2: PH15<br>3: PC9  |       | External Bus Interface (EBI) address output pin 27.                  |

| EBI_AD00      | 0: PE8<br>1: PB0<br>2: PG0             |       | External Bus Interface (EBI) address and data input / output pin 00. |

| EBI_AD01      | 0: PE9<br>1: PB1<br>2: PG1             |       | External Bus Interface (EBI) address and data input / output pin 01. |

| EBI_AD02      | 0: PE10<br>1: PB2<br>2: PG2            |       | External Bus Interface (EBI) address and data input / output pin 02. |

| EBI_AD03      | 0: PE11<br>1: PB3<br>2: PG3            |       | External Bus Interface (EBI) address and data input / output pin 03. |

| EBI_AD04      | 0: PE12<br>1: PB4<br>2: PG4            |       | External Bus Interface (EBI) address and data input / output pin 04. |

| EBI_AD05      | 0: PE13<br>1: PB5<br>2: PG5            |       | External Bus Interface (EBI) address and data input / output pin 05. |

| EBI_AD06      | 0: PE14<br>1: PB6<br>2: PG6            |       | External Bus Interface (EBI) address and data input / output pin 06. |

| EBI_AD07      | 0: PE15<br>1: PC0<br>2: PG7            |       | External Bus Interface (EBI) address and data input / output pin 07. |

| Alternate     | LOC                                      | ATION                                  |                                                      |

|---------------|------------------------------------------|----------------------------------------|------------------------------------------------------|

| Functionality | 0 - 3                                    | 4 - 7                                  | Description                                          |

| TIM2_CC1      | 0: PA9<br>1: PA13<br>2: PC9<br>3: PE12   | 4: PC0<br>5: PC3<br>6: PG9<br>7: PG6   | Timer 2 Capture Compare input / output channel 1.    |

| TIM2_CC2      | 0: PA10<br>1: PA14<br>2: PC10<br>3: PE13 | 4: PC1<br>5: PC4<br>6: PG10<br>7: PG7  | Timer 2 Capture Compare input / output channel 2.    |

| TIM2_CDTI0    | 0: PB0<br>1: PD13<br>2: PE8<br>3: PG0    |                                        | Timer 2 Complimentary Dead Time Insertion channel 0. |

| TIM2_CDTI1    | 0: PB1<br>1: PD14<br>2: PE14<br>3: PG1   |                                        | Timer 2 Complimentary Dead Time Insertion channel 1. |

| TIM2_CDTI2    | 0: PB2<br>1: PD15<br>2: PE15<br>3: PG2   |                                        | Timer 2 Complimentary Dead Time Insertion channel 2. |

| TIM3_CC0      | 0: PE14<br>1: PE0<br>2: PE3<br>3: PE5    | 4: PA0<br>5: PA3<br>6: PA6<br>7: PD15  | Timer 3 Capture Compare input / output channel 0.    |

| TIM3_CC1      | 0: PE15<br>1: PE1<br>2: PE4<br>3: PE6    | 4: PA1<br>5: PA4<br>6: PD13<br>7: PB15 | Timer 3 Capture Compare input / output channel 1.    |

| TIM3_CC2      | 0: PA15<br>1: PE2<br>2: PE5<br>3: PE7    | 4: PA2<br>5: PA5<br>6: PD14<br>7: PB0  | Timer 3 Capture Compare input / output channel 2.    |

| TIM4_CC0      | 0: PF3<br>1: PF13<br>2: PF5<br>3: PI8    | 4: PF6<br>5: PF9<br>6: PD11<br>7: PE9  | Timer 4 Capture Compare input / output channel 0.    |

| TIM4_CC1      | 0: PF4<br>1: PF14<br>2: PI6<br>3: PI9    | 4: PF7<br>5: PD9<br>6: PD12<br>7: PE10 | Timer 4 Capture Compare input / output channel 1.    |

| TIM4_CC2      | 0: PF12<br>1: PF15<br>2: PI7<br>3: PI10  | 4: PF8<br>5: PD10<br>6: PE8<br>7: PE11 | Timer 4 Capture Compare input / output channel 2.    |

| TIM4_CDTI0    | 0: PD0                                   |                                        | Timer 4 Complimentary Dead Time Insertion channel 0. |

| TIM4_CDTI1    | 0: PD1                                   |                                        | Timer 4 Complimentary Dead Time Insertion channel 1. |

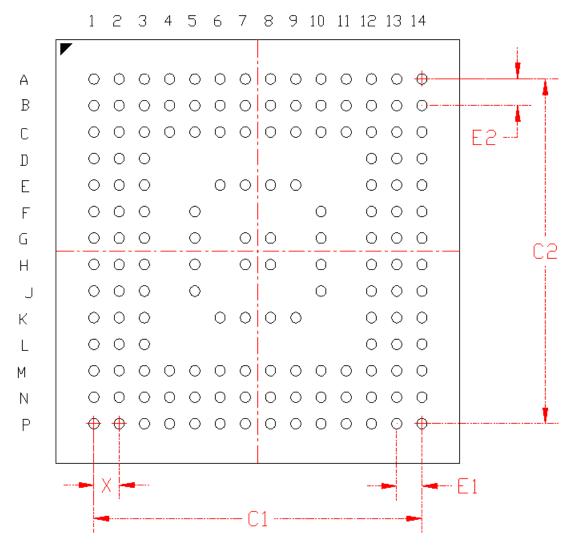

#### 7.2 BGA152 PCB Land Pattern

Figure 7.2. BGA152 PCB Land Pattern Drawing

| Dimension | Min       | Тур  | Мах  |  |  |

|-----------|-----------|------|------|--|--|

| A         | -         | -    | 1.30 |  |  |

| A1        | 0.55      | 0.60 | 0.65 |  |  |

| A2        | 0.21 BSC  |      |      |  |  |

| A3        | 0.30      | 0.35 | 0.40 |  |  |

| d         | 0.43      | 0.48 | 0.53 |  |  |

| D         | 10.00 BSC |      |      |  |  |

| D1        | 8.00 BSC  |      |      |  |  |

| E         | 10.00 BSC |      |      |  |  |

| E1        | 8.00 BSC  |      |      |  |  |

| e1        | 0.80 BSC  |      |      |  |  |

| e2        | 0.80 BSC  |      |      |  |  |

| L1        | 1.00 REF  |      |      |  |  |

| L2        | 1.00 REF  |      |      |  |  |

| Noto      |           |      |      |  |  |

## Table 9.1. BGA112 Package Dimensions

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

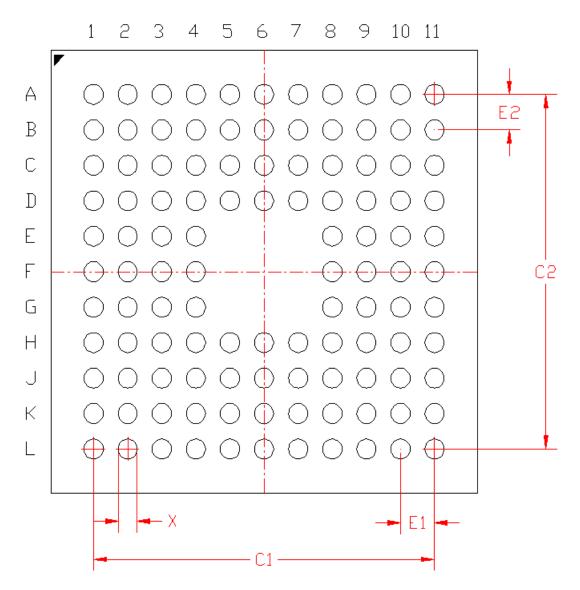

## 9.2 BGA112 PCB Land Pattern

Figure 9.2. BGA112 PCB Land Pattern Drawing