Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 72MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART  |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                              |

| Number of I/O              | 90                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 384K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                  |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 112-LFBGA                                                                    |

| Supplier Device Package    | 112-BGA (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b310f2048gl112-ar |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4.2 Internal and External Oscillators

The EFM32GG11 supports two crystal oscillators and fully integrates five RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 50 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxiliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC and the Serial Wire Viewer port with a wide frequency range.

- An integrated auxilliary high frequency RC oscillator (USHFRCO) is available for timing the USB, SDIO and QSPI peripherals. The USHFRCO can be syncronized to the host's USB clock to allow the USB to operate in device mode without the additional cost of an external crystal.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

#### 3.5 Counters/Timers and PWM

#### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

## 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER\_0 only.

#### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

#### 3.5.4 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of wave-forms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

#### 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

| Parameter                                       | Symbol                | Test Condition                                                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-----------------------|----------------------------------------------------------------|-----|-----|-----|------|

| Max load current                                | I <sub>LOAD_MAX</sub> | Low noise (LN) mode, Heavy Drive <sup>2</sup> , T $\leq$ 85 °C | _   | -   | 200 | mA   |

|                                                 |                       | Low noise (LN) mode, Heavy<br>Drive <sup>2</sup> , T > 85 °C   | _   | -   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Medium Drive <sup>2</sup>                 | _   | -   | 100 | mA   |

|                                                 |                       | Low noise (LN) mode, Light Drive <sup>2</sup>                  | _   | -   | 50  | mA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0         | _   | -   | 75  | μA   |

|                                                 |                       | Low power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3         | _   | -   | 10  | mA   |

| DCDC nominal output ca-<br>pacitor <sup>5</sup> | C <sub>DCDC</sub>     | 25% tolerance                                                  | 1   | 4.7 | 4.7 | μF   |

| DCDC nominal output induc-<br>tor               | L <sub>DCDC</sub>     | 20% tolerance                                                  | 4.7 | 4.7 | 4.7 | μH   |

| Resistance in Bypass mode                       | R <sub>BYP</sub>      |                                                                | -   | 1.2 | 2.5 | Ω    |

## Note:

1. Due to internal dropout, the DC-DC output will never be able to reach its input voltage, V<sub>VREGVDD</sub>.

- 2. Drive levels are defined by configuration of the PFETCNT and NFETCNT registers. Light Drive: PFETCNT=NFETCNT=3; Medium Drive: PFETCNT=NFETCNT=7; Heavy Drive: PFETCNT=15.

- 3. LPCMPBIASEMxx refers to either LPCMPBIASEM234H in the EMU\_DCDCMISCCTRL register or LPCMPBIASEM01 in the EMU\_DCDCLOEM01CFG register, depending on the energy mode.

4. LP mode controller is a hysteretic controller that maintains the output voltage within the specified limits.

5. Output voltage under/over-shoot and regulation are specified with C<sub>DCDC</sub> 4.7 μF. Different settings for DCDCLNCOMPCTRL must be used if C<sub>DCDC</sub> is lower than 4.7 μF. See Application Note AN0948 for details.

# 4.1.19 Operational Amplifier (OPAMP)

Unless otherwise indicated, specified conditions are: Non-inverting input configuration, VDD = 3.3 V, DRIVESTRENGTH = 2, MAIN-OUTEN = 1,  $C_{LOAD}$  = 75 pF with OUTSCALE = 0, or  $C_{LOAD}$  = 37.5 pF with OUTSCALE = 1. Unit gain buffer and 3X-gain connection as specified in table footnotes<sup>8 1</sup>.

| Parameter                     | Symbol            | Test Condition                                                                                                                                                                | Min              | Тур  | Max                   | Unit |

|-------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-----------------------|------|

| Supply voltage (from AVDD)    | V <sub>OPA</sub>  | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | 2                | _    | 3.8                   | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | 1.62             | _    | 3.8                   | V    |

| Input voltage                 | V <sub>IN</sub>   | HCMDIS = 0, Rail-to-rail input range                                                                                                                                          | V <sub>VSS</sub> | _    | V <sub>OPA</sub>      | V    |

|                               |                   | HCMDIS = 1                                                                                                                                                                    | V <sub>VSS</sub> |      | V <sub>OPA</sub> -1.2 | V    |

| Input impedance               | R <sub>IN</sub>   |                                                                                                                                                                               | 100              |      | _                     | MΩ   |

| Output voltage                | V <sub>OUT</sub>  |                                                                                                                                                                               | V <sub>VSS</sub> |      | V <sub>OPA</sub>      | V    |

| Load capacitance <sup>2</sup> | C <sub>LOAD</sub> | OUTSCALE = 0                                                                                                                                                                  | _                |      | 75                    | pF   |

|                               |                   | OUTSCALE = 1                                                                                                                                                                  | _                |      | 37.5                  | pF   |

| Output impedance              | R <sub>OUT</sub>  | DRIVESTRENGTH = 2 or 3, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -8 mA <<br>I <sub>OUT</sub> < 8 mA, Buffer connection,<br>Full supply range         | _                | 0.25 | -                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -400 µA $<$<br>I <sub>OUT</sub> $<$ 400 µA, Buffer connection,<br>Full supply range | _                | 0.6  | _                     | Ω    |

|                               |                   | DRIVESTRENGTH = 2 or 3, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -2 mA $<$<br>I <sub>OUT</sub> $<$ 2 mA, Buffer connection,<br>Full supply range     | _                | 0.4  | -                     | Ω    |

|                               |                   | DRIVESTRENGTH = 0 or 1, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -100 µA $<$<br>I <sub>OUT</sub> $<$ 100 µA, Buffer connection,<br>Full supply range | _                | 1    | _                     | Ω    |

| Internal closed-loop gain     | G <sub>CL</sub>   | Buffer connection                                                                                                                                                             | TBD              | 1    | TBD                   | -    |

|                               |                   | 3x Gain connection                                                                                                                                                            | TBD              | 2.99 | TBD                   | -    |

|                               |                   | 16x Gain connection                                                                                                                                                           | TBD              | 15.7 | TBD                   | -    |

| Active current <sup>4</sup>   | I <sub>OPA</sub>  | DRIVESTRENGTH = 3, OUT-<br>SCALE = 0                                                                                                                                          | _                | 580  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 2, OUT-<br>SCALE = 0                                                                                                                                          | _                | 176  | _                     | μA   |

|                               |                   | DRIVESTRENGTH = 1, OUT-<br>SCALE = 0                                                                                                                                          | _                | 13   | —                     | μA   |

|                               |                   | DRIVESTRENGTH = 0, OUT-<br>SCALE = 0                                                                                                                                          | _                | 4.7  | _                     | μA   |

# Table 4.27. Operational Amplifier (OPAMP)

| Parameter                             | Symbol           | Test Condition                                           | Min | Тур  | Max | Unit  |

|---------------------------------------|------------------|----------------------------------------------------------|-----|------|-----|-------|

| Open-loop gain                        | G <sub>OL</sub>  | DRIVESTRENGTH = 3                                        | _   | 135  | _   | dB    |

|                                       |                  | DRIVESTRENGTH = 2                                        | —   | 137  | _   | dB    |

|                                       |                  | DRIVESTRENGTH = 1                                        | _   | 121  | _   | dB    |

|                                       |                  | DRIVESTRENGTH = 0                                        | —   | 109  | _   | dB    |

| Loop unit-gain frequency <sup>7</sup> | UGF              | DRIVESTRENGTH = 3, Buffer connection                     | _   | 3.38 | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 2, Buffer connection                     | _   | 0.9  | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 1, Buffer connection                     | _   | 132  | _   | kHz   |

|                                       |                  | DRIVESTRENGTH = 0, Buffer connection                     | _   | 34   |     | kHz   |

|                                       |                  | DRIVESTRENGTH = 3, 3x Gain connection                    | _   | 2.57 | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 2, 3x Gain connection                    | _   | 0.71 | _   | MHz   |

|                                       |                  | DRIVESTRENGTH = 1, 3x Gain connection                    | _   | 113  | _   | kHz   |

|                                       |                  | DRIVESTRENGTH = 0, 3x Gain connection                    | _   | 28   | _   | kHz   |

| Phase margin                          | PM               | DRIVESTRENGTH = 3, Buffer connection                     |     | 67   | _   | 0     |

|                                       |                  | DRIVESTRENGTH = 2, Buffer connection                     | _   | 69   | _   | 0     |

|                                       |                  | DRIVESTRENGTH = 1, Buffer connection                     | _   | 63   | _   | 0     |

|                                       |                  | DRIVESTRENGTH = 0, Buffer connection                     | _   | 68   | _   | 0     |

| Output voltage noise                  | N <sub>OUT</sub> | DRIVESTRENGTH = 3, Buffer<br>connection, 10 Hz - 10 MHz  | _   | 146  | _   | µVrms |

|                                       |                  | DRIVESTRENGTH = 2, Buffer<br>connection, 10 Hz - 10 MHz  | _   | 163  | _   | µVrms |

|                                       |                  | DRIVESTRENGTH = 1, Buffer<br>connection, 10 Hz - 1 MHz   | _   | 170  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 0, Buffer<br>connection, 10 Hz - 1 MHz   | _   | 176  | _   | µVrms |

|                                       |                  | DRIVESTRENGTH = 3, 3x Gain<br>connection, 10 Hz - 10 MHz | _   | 313  | _   | µVrms |

|                                       |                  | DRIVESTRENGTH = 2, 3x Gain connection, 10 Hz - 10 MHz    | _   | 271  | _   | µVrms |

|                                       |                  | DRIVESTRENGTH = 1, 3x Gain<br>connection, 10 Hz - 1 MHz  | _   | 247  | _   | μVrms |

|                                       |                  | DRIVESTRENGTH = 0, 3x Gain connection, 10 Hz - 1 MHz     | -   | 245  | -   | μVrms |

## 4.1.21 Pulse Counter (PCNT)

## Table 4.29. Pulse Counter (PCNT)

| Parameter       | Symbol          | Test Condition                                | Min | Тур | Max | Unit |

|-----------------|-----------------|-----------------------------------------------|-----|-----|-----|------|

| Input frequency | F <sub>IN</sub> | Asynchronous Single and Quad-<br>rature Modes | —   | —   | 20  | MHz  |

|                 |                 | Sampled Modes with Debounce filter set to 0.  |     |     | 8   | kHz  |

## 4.1.22 Analog Port (APORT)

## Table 4.30. Analog Port (APORT)

| Parameter                     | Symbol             | Test Condition       | Min | Тур | Мах | Unit |

|-------------------------------|--------------------|----------------------|-----|-----|-----|------|

| Supply current <sup>2 1</sup> | I <sub>APORT</sub> | Operation in EM0/EM1 | —   | 7   | —   | μA   |

|                               |                    | Operation in EM2/EM3 | —   | 915 | _   | nA   |

# Note:

1. Specified current is for continuous APORT operation. In applications where the APORT is not requested continuously (e.g. periodic ACMP requests from LESENSE in EM2), the average current requirements can be estimated by mutiplying the duty cycle of the requests by the specified continuous current number.

2. Supply current increase that occurs when an analog peripheral requests access to APORT. This current is not included in reported module currents. Additional peripherals requesting access to APORT do not incur further current.

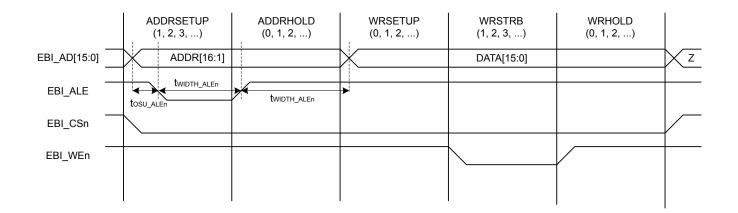

Figure 4.4. EBI Address Latch Enable Output Timing Diagram

# **RMII Receive Timing**

Timing is specified with 3.0 V  $\leq$  IOVDD  $\leq$  3.8 V, 25 pF external loading, and slew rate for all GPIO set to 6 unless otherwise indicated.

| Table 4.45. | Ethernet | RMII | Receive | Timing |

|-------------|----------|------|---------|--------|

|-------------|----------|------|---------|--------|

| Parameter                                                  | Symbol                | Test Condition            | Min | Тур | Max | Unit |

|------------------------------------------------------------|-----------------------|---------------------------|-----|-----|-----|------|

| REF_CLK frequency                                          | F <sub>REF_CLK</sub>  | Output slew rate set to 7 | —   | 50  | —   | MHz  |

| REF_CLK duty cycle                                         | DC <sub>REF_CLK</sub> |                           | 35  | —   | 65  | %    |

| Setup time, RXD[1:0],<br>CRS_DV, RX_ER valid to<br>REF_CLK | t <sub>SU</sub>       |                           | 4   | _   | _   | ns   |

| Hold time, REF_CLK to<br>RXD[1:0], CRS_DV, RX_ER<br>change | t <sub>HD</sub>       |                           | 2   | _   | _   | ns   |

Figure 4.12. Ethernet RMII Receive Timing

## SDIO MMC SDR Mode Timing at 1.8 V

Timing is specified for route location 0 at 1.8 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 20 pF on all pins.

| Parameter                                          | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|----------------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer               | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    | _    | 25  | MHz  |

|                                                    |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                     | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 18.1 | _    | _   | ns   |

|                                                    |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                                    | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 18.1 | _    | _   | ns   |

|                                                    |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                                    | t <sub>R</sub>      |                                   | 1.96 | 8.27 | _   | ns   |

| Clock fall time                                    | t <sub>F</sub>      |                                   | 1.67 | 6.90 | _   | ns   |

| Input setup time, CMD,<br>DAT[0:7] valid to SD_CLK | t <sub>ISU</sub>    |                                   | 5.3  | _    | _   | ns   |

| Input hold time, SD_CLK to CMD, DAT[0:7] change    | tiH                 |                                   | 2.5  | _    | _   | ns   |

| Output delay time, SD_CLK to CMD, DAT[0:7] valid   | t <sub>ODLY</sub>   |                                   | 0    | _    | 16  | ns   |

| Output hold time, SD_CLK to CMD, DAT[0:7] change   | t <sub>OH</sub>     |                                   | 3    | _    | _   | ns   |

# Table 4.50. SDIO MMC SDR Mode Timing (Location 0, 1.8V I/O)

## SDIO MMC SDR Mode Timing at 3.0 V

Timing is specified for route location 0 at 3.0 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 20 pF on all pins.

| Parameter                                           | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|-----------------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer                | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    | —    | 48  | MHz  |

|                                                     |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                      | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 9.4  | _    | _   | ns   |

|                                                     |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                                     | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 9.4  | _    | _   | ns   |

|                                                     |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                                     | t <sub>R</sub>      |                                   | 1.96 | 3.87 | _   | ns   |

| Clock fall time                                     | t <sub>F</sub>      |                                   | 1.67 | 3.31 | _   | ns   |

| Input setup time, CMD,<br>DAT[0:7] valid to SD_CLK  | t <sub>ISU</sub>    |                                   | 5.3  | -    | _   | ns   |

| Input hold time, SD_CLK to CMD, DAT[0:7] change     | tiH                 |                                   | 2.5  | -    | _   | ns   |

| Output delay time, SD_CLK<br>to CMD, DAT[0:7] valid | t <sub>ODLY</sub>   |                                   | 0    | -    | 16  | ns   |

| Output hold time, SD_CLK to CMD, DAT[0:7] change    | t <sub>OH</sub>     |                                   | 3    | -    | _   | ns   |

# Table 4.51. SDIO MMC SDR Mode Timing (Location 0, 3V I/O)

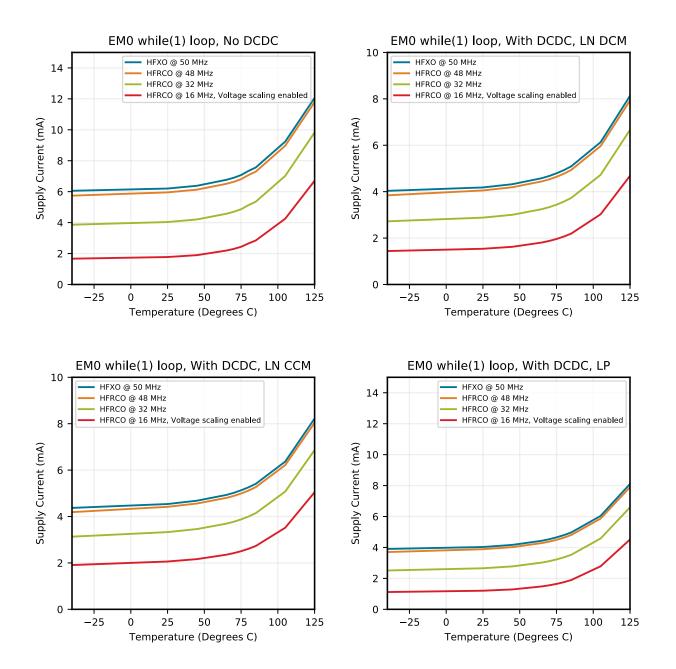

Figure 4.24. EM0 Active Mode Typical Supply Current vs. Temperature

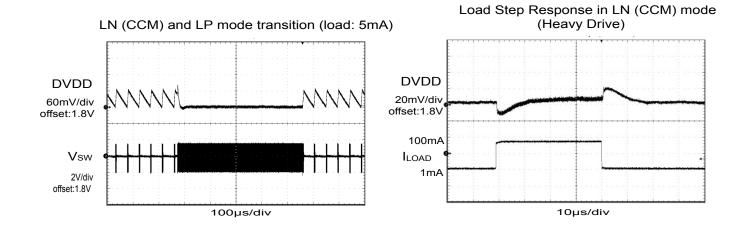

Figure 4.30. DC-DC Converter Transition Waveforms

| Pin Name | Pin(s)                                                    | Description                                           | Pin Name | Pin(s) | Description                                                                                                      |

|----------|-----------------------------------------------------------|-------------------------------------------------------|----------|--------|------------------------------------------------------------------------------------------------------------------|

| PE8      | B4                                                        | GPIO                                                  | PD11     | B5     | GPIO                                                                                                             |

| PF8      | B6                                                        | GPIO                                                  | PF6      | B7     | GPIO                                                                                                             |

| VBUS     | B8                                                        | USB VBUS signal and auxiliary input to 5 V regulator. | PE5      | В9     | GPIO                                                                                                             |

| VREGI    | B10                                                       | Input to 5 V regulator.                               | VREGO    | B11    | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs                 |

| PA1      | C1                                                        | GPIO                                                  | PA0      | C2     | GPIO                                                                                                             |

| PE10     | C3                                                        | GPIO                                                  | PD13     | C4     | GPIO (5V)                                                                                                        |

| PD12     | C5                                                        | GPIO                                                  | PF9      | C6     | GPIO                                                                                                             |

| VSS      | C7<br>D4<br>F9<br>G3<br>G9<br>H6<br>K4<br>K7<br>K10<br>L7 | Ground                                                | PF2      | C8     | GPIO                                                                                                             |

| PE6      | C9                                                        | GPIO                                                  | PC10     | C10    | GPIO (5V)                                                                                                        |

| PC11     | C11                                                       | GPIO (5V)                                             | PA3      | D1     | GPIO                                                                                                             |

| PA2      | D2                                                        | GPIO                                                  | PB15     | D3     | GPIO (5V)                                                                                                        |

| IOVDD1   | D5                                                        | Digital IO power supply 1.                            | PD9      | D6     | GPIO                                                                                                             |

| IOVDD0   | D7<br>G8<br>H7<br>L4                                      | Digital IO power supply 0.                            | PF1      | D8     | GPIO (5V)                                                                                                        |

| PE7      | D9                                                        | GPIO                                                  | PC8      | D10    | GPIO (5V)                                                                                                        |

| PC9      | D11                                                       | GPIO (5V)                                             | PA6      | E1     | GPIO                                                                                                             |

| PA5      | E2                                                        | GPIO                                                  | PA4      | E3     | GPIO                                                                                                             |

| PB0      | E4                                                        | GPIO                                                  | PF0      | E8     | GPIO (5V)                                                                                                        |

| PE0      | E9                                                        | GPIO (5V)                                             | PE1      | E10    | GPIO (5V)                                                                                                        |

| PE3      | E11                                                       | GPIO                                                  | PB1      | F1     | GPIO                                                                                                             |

| PB2      | F2                                                        | GPIO                                                  | PB3      | F3     | GPIO                                                                                                             |

| PB4      | F4                                                        | GPIO                                                  | DVDD     | F8     | Digital power supply.                                                                                            |

| PE2      | F10                                                       | GPIO                                                  | DECOUPLE | F11    | Decouple output for on-chip voltage<br>regulator. An external decoupling ca-<br>pacitor is required at this pin. |

| PB5      | G1                                                        | GPIO                                                  | PB6      | G2     | GPIO                                                                                                             |

| IOVDD2   | G4                                                        | Digital IO power supply 2.                            | PC6      | G10    | GPIO                                                                                                             |

| PC7      | G11                                                       | GPIO                                                  | PC0      | H1     | GPIO (5V)                                                                                                        |

| PC2      | H2                                                        | GPIO (5V)                                             | PD14     | H3     | GPIO (5V)                                                                                                        |

| PA7      | H4                                                        | GPIO                                                  | PA8      | H5     | GPIO                                                                                                             |

| Pin Name | Pin(s) | Description                                                                                                                                                                                                 | Pin Name | Pin(s)   | Description             |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------------------------|

| PB6      | 12     | GPIO                                                                                                                                                                                                        | PC4      | 13       | GPIO                    |

| PC5      | 14     | GPIO                                                                                                                                                                                                        | PB7      | 15       | GPIO                    |

| PB8      | 16     | GPIO                                                                                                                                                                                                        | PA12     | 17       | GPIO (5V)               |

| PA13     | 18     | GPIO (5V)                                                                                                                                                                                                   | PA14     | 19       | GPIO                    |

| RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB11     | 21       | GPIO                    |

| PB12     | 22     | GPIO                                                                                                                                                                                                        | AVDD     | 23<br>27 | Analog power supply.    |

| PB13     | 24     | GPIO                                                                                                                                                                                                        | PB14     | 25       | GPIO                    |

| PD0      | 28     | GPIO (5V)                                                                                                                                                                                                   | PD1      | 29       | GPIO                    |

| PD2      | 30     | GPIO (5V)                                                                                                                                                                                                   | PD3      | 31       | GPIO                    |

| PD4      | 32     | GPIO                                                                                                                                                                                                        | PD5      | 33       | GPIO                    |

| PD6      | 34     | GPIO                                                                                                                                                                                                        | PD7      | 35       | GPIO                    |

| PD8      | 36     | GPIO                                                                                                                                                                                                        | PC6      | 37       | GPIO                    |

| PC7      | 38     | GPIO                                                                                                                                                                                                        | DVDD     | 39       | Digital power supply.   |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    | PE4      | 41       | GPIO                    |

| PE5      | 42     | GPIO                                                                                                                                                                                                        | PE6      | 43       | GPIO                    |

| PE7      | 44     | GPIO                                                                                                                                                                                                        | VREGI    | 45       | Input to 5 V regulator. |

| VREGO    | 46     | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs                                                                                                            | PF10     | 47       | GPIO (5V)               |

| PF11     | 48     | GPIO (5V)                                                                                                                                                                                                   | PF0      | 49       | GPIO (5V)               |

| PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   | PF2      | 51       | GPIO                    |

| VBUS     | 52     | USB VBUS signal and auxiliary input to 5 V regulator.                                                                                                                                                       | PF12     | 53       | GPIO                    |

| PF5      | 54     | GPIO                                                                                                                                                                                                        | PE8      | 56       | GPIO                    |

| PE9      | 57     | GPIO                                                                                                                                                                                                        | PE10     | 58       | GPIO                    |

| PE11     | 59     | GPIO                                                                                                                                                                                                        | PE12     | 60       | GPIO                    |

| PE13     | 61     | GPIO                                                                                                                                                                                                        | PE14     | 62       | GPIO                    |

| PE15     | 63     | GPIO                                                                                                                                                                                                        | PA15     | 64       | GPIO                    |

1. GPIO with 5V tolerance are indicated by (5V).

#### 5.21 Alternate Functionality Overview

A wide selection of alternate functionality is available for multiplexing to various pins. The following table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings and the associated GPIO pin. Refer to 5.20 GPIO Functionality Table for a list of functions available on each GPIO pin.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     | LOCATION                                |                                        |                                                                         |  |

|---------------|-----------------------------------------|----------------------------------------|-------------------------------------------------------------------------|--|

| Functionality | 0 - 3                                   | 4 - 7                                  | Description                                                             |  |

| ACMP0_O       | 0: PE13<br>1: PE2<br>2: PD6<br>3: PB11  | 4: PA6<br>5: PB0<br>6: PB2<br>7: PB3   | Analog comparator ACMP0, digital output.                                |  |

| ACMP1_O       | 0: PF2<br>1: PE3<br>2: PD7<br>3: PA12   | 4: PA14<br>5: PB9<br>6: PB10<br>7: PA5 | Analog comparator ACMP1, digital output.                                |  |

| ACMP2_O       | 0: PD8<br>1: PE0<br>2: PE1<br>3: PI0    | 4: PI1<br>5: PI2                       | Analog comparator ACMP2, digital output.                                |  |

| ACMP3_O       | 0: PF0<br>1: PC15<br>2: PC14<br>3: PC13 | 4: PI4<br>5: PI5                       | Analog comparator ACMP3, digital output.                                |  |

| ADC0_EXTN     | 0: PD7                                  |                                        | Analog to digital converter ADC0 external reference input negative pin. |  |

| ADC0_EXTP     | 0: PD6                                  |                                        | Analog to digital converter ADC0 external reference input positive pin. |  |

| ADC1_EXTN     | 0: PD7                                  |                                        | Analog to digital converter ADC1 external reference input negative pin. |  |

| ADC1_EXTP     | 0: PD6                                  |                                        | Analog to digital converter ADC1 external reference input positive pin. |  |

| BOOT_RX       | 0: PF1                                  |                                        | Bootloader RX.                                                          |  |

| BOOT_TX       | 0: PF0                                  |                                        | Bootloader TX.                                                          |  |

## Table 5.21. Alternate Functionality Overview

| Alternate     | LOCATION                               |       |                                                                                                                                           |  |

|---------------|----------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Functionality | 0 - 3                                  | 4 - 7 | Description                                                                                                                               |  |

|               | 0: PF2                                 |       | Debug-interface Serial Wire viewer Output.                                                                                                |  |

| DBG_SWO       | 1: PC15<br>2: PD1<br>3: PD2            |       | Note that this function is not enabled after reset, and must be enabled by software to be used.                                           |  |

|               | 0: PF5                                 |       | Debug-interface JTAG Test Data In.                                                                                                        |  |

| DBG_TDI       |                                        |       | Note that this function becomes available after the first valid JTAG command is received, and has a built-in pull up when JTAG is active. |  |

|               | 0: PF2                                 |       | Debug-interface JTAG Test Data Out.                                                                                                       |  |

| DBG_TDO       |                                        |       | Note that this function becomes available after the first valid JTAG command is received.                                                 |  |

| EBI_A00       | 0: PA12<br>1: PB9<br>2: PE0<br>3: PC5  |       | External Bus Interface (EBI) address output pin 00.                                                                                       |  |

| EBI_A01       | 0: PA13<br>1: PB10<br>2: PE1<br>3: PA7 |       | External Bus Interface (EBI) address output pin 01.                                                                                       |  |

| EBI_A02       | 0: PA14<br>1: PB11<br>2: PI0<br>3: PA8 |       | External Bus Interface (EBI) address output pin 02.                                                                                       |  |

| EBI_A03       | 0: PB9<br>1: PB12<br>2: PI1<br>3: PA9  |       | External Bus Interface (EBI) address output pin 03.                                                                                       |  |

| EBI_A04       | 0: PB10<br>1: PD0<br>2: PI2<br>3: PA10 |       | External Bus Interface (EBI) address output pin 04.                                                                                       |  |

| EBI_A05       | 0: PC6<br>1: PD1<br>2: PI3<br>3: PA11  |       | External Bus Interface (EBI) address output pin 05.                                                                                       |  |

| EBI_A06       | 0: PC7<br>1: PD2<br>2: PI4<br>3: PA12  |       | External Bus Interface (EBI) address output pin 06.                                                                                       |  |

| EBI_A07       | 0: PE0<br>1: PD3<br>2: PI5<br>3: PA13  |       | External Bus Interface (EBI) address output pin 07.                                                                                       |  |

| EBI_A08       | 0: PE1<br>1: PD4<br>2: PC8<br>3: PA14  |       | External Bus Interface (EBI) address output pin 08.                                                                                       |  |

| EBI_A09       | 0: PE2<br>1: PD5<br>2: PC9<br>3: PB9   |       | External Bus Interface (EBI) address output pin 09.                                                                                       |  |

| Alternate     | LOCATION                               |                    |                                                                      |  |

|---------------|----------------------------------------|--------------------|----------------------------------------------------------------------|--|

| Functionality | 0 - 3                                  | 4 - 7              | Description                                                          |  |

| EBI_AD08      | 0: PA15<br>1: PC1<br>2: PG8            |                    | External Bus Interface (EBI) address and data input / output pin 08. |  |

| EBI_AD09      | 0: PA0<br>1: PC2<br>2: PG9             |                    | External Bus Interface (EBI) address and data input / output pin 09. |  |

| EBI_AD10      | 0: PA1<br>1: PC3<br>2: PG10            |                    | External Bus Interface (EBI) address and data input / output pin 10. |  |

| EBI_AD11      | 0: PA2<br>1: PC4<br>2: PG11            |                    | External Bus Interface (EBI) address and data input / output pin 11. |  |

| EBI_AD12      | 0: PA3<br>1: PC5<br>2: PG12            |                    | External Bus Interface (EBI) address and data input / output pin 12. |  |

| EBI_AD13      | 0: PA4<br>1: PA7<br>2: PG13            |                    | External Bus Interface (EBI) address and data input / output pin 13. |  |

| EBI_AD14      | 0: PA5<br>1: PA8<br>2: PG14            |                    | External Bus Interface (EBI) address and data input / output pin 14. |  |

| EBI_AD15      | 0: PA6<br>1: PA9<br>2: PG15            |                    | External Bus Interface (EBI) address and data input / output pin 15. |  |

| EBI_ALE       | 0: PF3<br>1: PB9<br>2: PC4<br>3: PB5   | 4: PC11<br>5: PC11 | External Bus Interface (EBI) Address Latch Enable output.            |  |

| EBI_ARDY      | 0: PF2<br>1: PD13<br>2: PB15<br>3: PB4 | 4: PC13<br>5: PF10 | External Bus Interface (EBI) Hardware Ready Control input.           |  |

| EBI_BL0       | 0: PF6<br>1: PF8<br>2: PB10<br>3: PC1  | 4: PF6<br>5: PF6   | External Bus Interface (EBI) Byte Lane/Enable pin 0.                 |  |

| EBI_BL1       | 0: PF7<br>1: PF9<br>2: PB11<br>3: PC3  | 4: PF7<br>5: PF7   | External Bus Interface (EBI) Byte Lane/Enable pin 1.                 |  |

| EBI_CS0       | 0: PD9<br>1: PA10<br>2: PC0<br>3: PB0  | 4: PE8             | External Bus Interface (EBI) Chip Select output 0.                   |  |

| Alternate LOCATION |                                          | ATION                                  |                                                      |  |

|--------------------|------------------------------------------|----------------------------------------|------------------------------------------------------|--|

| Functionality      | 0 - 3                                    | 4 - 7                                  | Description                                          |  |

| TIM2_CC1           | 0: PA9<br>1: PA13<br>2: PC9<br>3: PE12   | 4: PC0<br>5: PC3<br>6: PG9<br>7: PG6   | Timer 2 Capture Compare input / output channel 1.    |  |

| TIM2_CC2           | 0: PA10<br>1: PA14<br>2: PC10<br>3: PE13 | 4: PC1<br>5: PC4<br>6: PG10<br>7: PG7  | Timer 2 Capture Compare input / output channel 2.    |  |

| TIM2_CDTI0         | 0: PB0<br>1: PD13<br>2: PE8<br>3: PG0    |                                        | Timer 2 Complimentary Dead Time Insertion channel 0. |  |

| TIM2_CDTI1         | 0: PB1<br>1: PD14<br>2: PE14<br>3: PG1   |                                        | Timer 2 Complimentary Dead Time Insertion channel 1. |  |

| TIM2_CDTI2         | 0: PB2<br>1: PD15<br>2: PE15<br>3: PG2   |                                        | Timer 2 Complimentary Dead Time Insertion channel 2. |  |

| TIM3_CC0           | 0: PE14<br>1: PE0<br>2: PE3<br>3: PE5    | 4: PA0<br>5: PA3<br>6: PA6<br>7: PD15  | Timer 3 Capture Compare input / output channel 0.    |  |

| TIM3_CC1           | 0: PE15<br>1: PE1<br>2: PE4<br>3: PE6    | 4: PA1<br>5: PA4<br>6: PD13<br>7: PB15 | Timer 3 Capture Compare input / output channel 1.    |  |

| TIM3_CC2           | 0: PA15<br>1: PE2<br>2: PE5<br>3: PE7    | 4: PA2<br>5: PA5<br>6: PD14<br>7: PB0  | Timer 3 Capture Compare input / output channel 2.    |  |

| TIM4_CC0           | 0: PF3<br>1: PF13<br>2: PF5<br>3: PI8    | 4: PF6<br>5: PF9<br>6: PD11<br>7: PE9  | Timer 4 Capture Compare input / output channel 0.    |  |

| TIM4_CC1           | 0: PF4<br>1: PF14<br>2: PI6<br>3: PI9    | 4: PF7<br>5: PD9<br>6: PD12<br>7: PE10 | Timer 4 Capture Compare input / output channel 1.    |  |

| TIM4_CC2           | 0: PF12<br>1: PF15<br>2: PI7<br>3: PI10  | 4: PF8<br>5: PD10<br>6: PE8<br>7: PE11 | Timer 4 Capture Compare input / output channel 2.    |  |

| TIM4_CDTI0         | 0: PD0                                   |                                        | Timer 4 Complimentary Dead Time Insertion channel 0. |  |

| TIM4_CDTI1         | 0: PD1                                   |                                        | Timer 4 Complimentary Dead Time Insertion channel 1. |  |

Figure 6.3. BGA192 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.

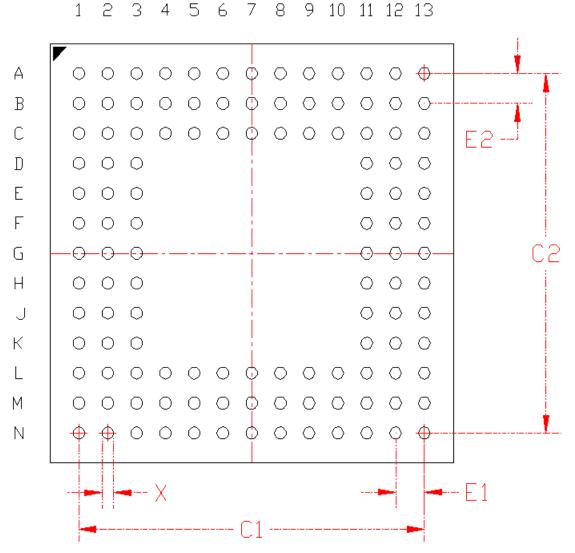

## 8.2 BGA120 PCB Land Pattern

Figure 8.2. BGA120 PCB Land Pattern Drawing

## Table 11.2. TQFP64 PCB Land Pattern Dimensions

| Dimension | Min      | Мах   |

|-----------|----------|-------|

| C1        | 11.30    | 11.40 |

| C2        | 11.30    | 11.40 |

| E         | 0.50 BSC |       |

| x         | 0.20     | 0.30  |

| Y         | 1.40     | 1.50  |

## Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

#### 11.3 TQFP64 Package Marking

Figure 11.3. TQFP64 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.