#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 72MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART  |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                              |

| Number of I/O              | 86                                                                           |

| Program Memory Size        | 2MB (2M × 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                  |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 100-TQFP                                                                     |

| Supplier Device Package    | 100-TQFP (14x14)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b320f2048gq100-br |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Feature List

The EFM32GG11 highlighted features are listed below.

- ARM Cortex-M4 CPU platform

- High performance 32-bit processor @ up to 72 MHz

- DSP instruction support and Floating Point Unit

- Memory Protection Unit

- Wake-up Interrupt Controller

- Flexible Energy Management System

- + 80  $\mu\text{A}/\text{MHz}$  in Active Mode (EM0)

- 2.1 µA EM2 Deep Sleep current (16 kB RAM retention and RTCC running from LFRCO)

- Integrated DC-DC buck converter

- Up to 2048 kB flash program memory

- · Dual-bank with read-while-write support

- Up to 512 kB RAM data memory

- 256 kB with ECC (SEC-DED)

- Octal/Quad-SPI Flash Memory Interface

- Supports 3 V and 1.8 V memories

- 1/2/4/8-bit data bus

- Quad-SPI Execute In Place (XIP)

- Communication Interfaces

- Low-energy Universal Serial Bus (USB) with Device and Host support

- Fully USB 2.0 compliant

- On-chip PHY and embedded 5V to 3.3V regulator

- Crystal-free Device mode operation

- Patent-pending Low-Energy Mode (LEM)

- SD/MMC/SDIO Host Controller

- SD v3.01, SDIO v3.0 and MMC v4.51

- 1/4/8-bit bus width

- 10/100 Ethernet MAC with MII/RMII interface

- IEEE1588-2008 precision time stamping

- Energy Efficient Ethernet (802.3az)

- Up to 2× CAN Bus Controller

- Version 2.0A and 2.0B up to 1 Mbps

- 6× Universal Synchronous/Asynchronous Receiver/ Transmitter

- UART/SPI/SmartCard (ISO 7816)/IrDA/I2S/LIN

- · Triple buffered full/half-duplex operation with flow control

- Ultra high speed (36 MHz) operation on one instance

- 2× Universal Asynchronous Receiver/ Transmitter

- 2× Low Energy UART

- · Autonomous operation with DMA in Deep Sleep Mode

- 3× I<sup>2</sup>C Interface with SMBus support

- Address recognition in EM3 Stop Mode

- Up to 144 General Purpose I/O Pins

- Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

- Configurable peripheral I/O locations

- 5 V tolerance on select pins

- Asynchronous external interrupts

- · Output state retention and wake-up from Shutoff Mode

- Up to 24 Channel DMA Controller

- Up to 24 Channel Peripheral Reflex System (PRS) for autonomous inter-peripheral signaling

- External Bus Interface for up to 4x256 MB of external memory mapped space

- TFT Controller with Direct Drive

- Per-pixel alpha-blending engine

- Hardware Cryptography

- AES 128/256-bit keys

- ECC B/K163, B/K233, P192, P224, P256

- SHA-1 and SHA-2 (SHA-224 and SHA-256)

- True Random Number Generator (TRNG)

- Hardware CRC engine

- Single-cycle computation with 8/16/32-bit data and 16-bit (programmable)/32-bit (fixed) polynomial

- Security Management Unit (SMU)

- · Fine-grained access control for on-chip peripherals

- Integrated Low-energy LCD Controller with up to 8×36 segments

- · Voltage boost, contrast and autonomous animation

- Patented low-energy LCD driver

- Backup Power Domain

- RTCC and retention registers in a separate power domain, available down to energy mode EM4H

- Operation from backup battery when main power absent/ insufficient

- Ultra Low-Power Precision Analog Peripherals

- 2× 12-bit 1 Msamples/s Analog to Digital Converter (ADC)

- · On-chip temperature sensor

- 2× 12-bit 500 ksamples/s Digital to Analog Converter (VDAC)

- Digital to Analog Current Converter (IDAC)

- Up to 4× Analog Comparator (ACMP)

- Up to 4× Operational Amplifier (OPAMP)

- Robust current-based capacitive sensing with up to 64 inputs and wake-on-touch (CSEN)

- Up to 108 GPIO pins are analog-capable. Flexible analog peripheral-to-pin routing via Analog Port (APORT)

- Supply Voltage Monitor

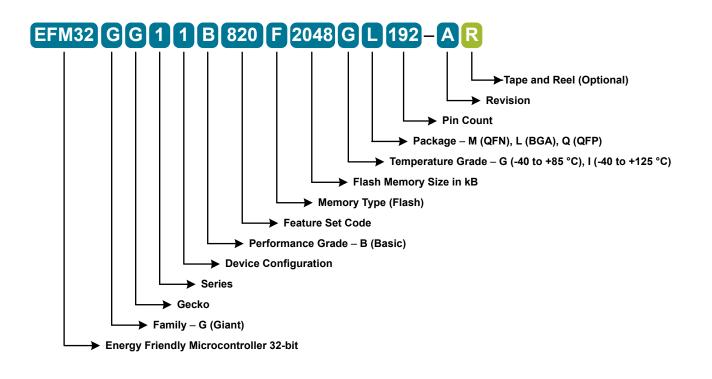

Figure 2.1. Ordering Code Key

## 4.1.10.2 High-Frequency Crystal Oscillator (HFXO)

| Parameter                                        | Symbol              | Test Condition                                 | Min | Тур   | Max  | Unit |

|--------------------------------------------------|---------------------|------------------------------------------------|-----|-------|------|------|

| Crystal frequency                                | f <sub>HFXO</sub>   | No clock doubling                              | 4   |       | 50   | MHz  |

|                                                  |                     | Clock doubler enabled                          | TBD |       | TBD  | MHz  |

| Supported crystal equivalent                     | ESR <sub>HFXO</sub> | 50 MHz crystal                                 |     |       | 50   | Ω    |

| series resistance (ESR)                          |                     | 24 MHz crystal                                 | _   |       | 150  | Ω    |

|                                                  |                     | 4 MHz crystal                                  | —   |       | 180  | Ω    |

| Nominal on-chip tuning cap<br>range <sup>1</sup> | C <sub>HFXO_T</sub> | On each of HFXTAL_N and HFXTAL_P pins          | 8.7 |       | 51.7 | pF   |

| On-chip tuning capacitance step                  | SS <sub>HFXO</sub>  |                                                | _   | 0.084 | _    | pF   |

| Startup time                                     | t <sub>HFXO</sub>   | 50 MHz crystal, ESR = 50 Ohm,<br>$C_L = 8 pF$  |     | 350   | _    | μs   |

|                                                  |                     | 24 MHz crystal, ESR = 150 Ohm,<br>$C_L = 6 pF$ |     | 700   | _    | μs   |

|                                                  |                     | 4 MHz crystal, ESR = 180 Ohm,<br>$C_L$ = 18 pF |     | 3     |      | ms   |

| Current consumption after                        | I <sub>HFXO</sub>   | 50 MHz crystal                                 | —   | 880   | _    | μA   |

| startup                                          |                     | 24 MHz crystal                                 |     | 420   | _    | μA   |

|                                                  |                     | 4 MHz crystal                                  | —   | 80    | _    | μA   |

### Table 4.13. High-Frequency Crystal Oscillator (HFXO)

## Note:

1. The effective load capacitance seen by the crystal will be C<sub>HFXO\_T</sub> /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

## 4.1.11 Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур  | Max | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|------|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _    | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | —    | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    | _    | _   | years  |

| Word (32-bit) programming time              | tw_prog              | Burst write, 128 words, average time per word | 20    | 26.2 | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68.7 | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 26.8 | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 26.9 | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | —     | 80.7 | 95  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 80.7 | 100 | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    |       | _    | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          |       | _    | 2.1 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | —     | _    | 3.9 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _    | 3.6 | V      |

### Table 4.19. Flash Memory Characteristics<sup>5</sup>

## Note:

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

6. Measured at 25 °C.

| Parameter                                         | Symbol                | Test Condition                                             | Min | Тур   | Мах | Unit   |

|---------------------------------------------------|-----------------------|------------------------------------------------------------|-----|-------|-----|--------|

| ADC clock frequency                               | f <sub>ADCCLK</sub>   |                                                            | —   | —     | 16  | MHz    |

| Throughput rate                                   | <b>f</b> ADCRATE      |                                                            | _   | _     | 1   | Msps   |

| Conversion time <sup>1</sup>                      | t <sub>ADCCONV</sub>  | 6 bit                                                      | —   | 7     | _   | cycles |

|                                                   |                       | 8 bit                                                      | _   | 9     | _   | cycles |

|                                                   |                       | 12 bit                                                     | —   | 13    |     | cycles |

| Startup time of reference generator and ADC core  | t <sub>ADCSTART</sub> | WARMUPMODE <sup>4</sup> = NORMAL                           | —   | _     | 5   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPIN-<br>STANDBY               | _   | _     | 2   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPINSLO-<br>WACC               | _   | _     | 1   | μs     |

| SNDR at 1Msps and f <sub>IN</sub> =<br>10kHz      | SNDR <sub>ADC</sub>   | Internal reference <sup>7</sup> , differential measurement | TBD | 67    | _   | dB     |

|                                                   |                       | External reference <sup>6</sup> , differential measurement | _   | 68    | _   | dB     |

| Spurious-free dynamic range<br>(SFDR)             | SFDR <sub>ADC</sub>   | 1 MSamples/s, 10 kHz full-scale sine wave                  | _   | 75    | _   | dB     |

| Differential non-linearity<br>(DNL)               | DNL <sub>ADC</sub>    | 12 bit resolution, No missing co-<br>des                   | TBD |       | TBD | LSB    |

| Integral non-linearity (INL),<br>End point method | INL <sub>ADC</sub>    | 12 bit resolution                                          | TBD |       | TBD | LSB    |

| Offset error                                      | VADCOFFSETERR         |                                                            | TBD | 0     | TBD | LSB    |

| Gain error in ADC                                 | VADCGAIN              | Using internal reference                                   | _   | -0.2  | TBD | %      |

|                                                   |                       | Using external reference                                   | _   | -1    | —   | %      |

| Temperature sensor slope                          | V <sub>TS_SLOPE</sub> |                                                            | _   | -1.84 | _   | mV/°C  |

Note:

1. Derived from ADCCLK.

2. PSRR is referenced to AVDD when ANASW=0 and to DVDD when ANASW=1 in EMU\_PWRCTRL.

3. In ADCn\_BIASPROG register.

4. In ADCn CNTL register.

5. The absolute voltage allowed at any ADC input is dictated by the power rail supplied to on-chip circuitry, and may be lower than the effective full scale voltage. All ADC inputs are limited to the ADC supply (AVDD or DVDD depending on EMU PWRCTRL ANASW). Any ADC input routed through the APORT will further be limited by the IOVDD supply to the pin.

6. External reference is 1.25 V applied externally to ADCnEXTREFP, with the selection CONF in the SINGLECTRL\_REF or SCANCTRL\_REF register field and VREFP in the SINGLECTRLX\_VREFSEL or SCANCTRLX\_VREFSEL field. The differential input range with this configuration is ± 1.25 V.

7. Internal reference option used corresponds to selection 2V5 in the SINGLECTRL\_REF or SCANCTRL\_REF register field. The differential input range with this configuration is ± 1.25 V. Typical value is characterized using full-scale sine wave input. Minimum value is production-tested using sine wave input at 1.5 dB lower than full scale.

## 4.1.15 Analog Comparator (ACMP)

| Parameter                                                           | Symbol              | Test Condition                                               | Min | Тур | Мах                         | Unit |

|---------------------------------------------------------------------|---------------------|--------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                                 | V <sub>ACMPIN</sub> | ACMPVDD =<br>ACMPn_CTRL_PWRSEL <sup>1</sup>                  |     | _   | V <sub>ACMPVDD</sub>        | V    |

| Supply voltage                                                      | VACMPVDD            | $BIASPROG^4 \le 0x10 \text{ or } FULL-BIAS^4 = 0$            | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                                     |                     | $0x10 < BIASPROG^4 \le 0x20$ and FULLBIAS <sup>4</sup> = 1   | 2.1 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Active current not including                                        | I <sub>ACMP</sub>   | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                          | _   | 50  | _                           | nA   |

| voltage reference <sup>2</sup>                                      |                     | $BIASPROG^4 = 0x10, FULLBIAS^4 = 0$                          | _   | 306 | —                           | nA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1   |     | 6.5 | _                           | μA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1   |     | 74  | TBD                         | μA   |

| Current consumption of inter-<br>nal voltage reference <sup>2</sup> | IACMPREF            | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V) |     | 50  | _                           | nA   |

|                                                                     |                     | VLP selected as input using VDD                              |     | 20  | _                           | nA   |

|                                                                     |                     | VBDIV selected as input using 1.25 V reference / 1           | _   | 4.1 | -                           | μA   |

|                                                                     |                     | VADIV selected as input using VDD/1                          | _   | 2.4 | —                           | μA   |

### Table 4.23. Analog Comparator (ACMP)

| Parameter                                 | Symbol                 | Test Condition                                             | Min | Тур      | Мах | Unit |

|-------------------------------------------|------------------------|------------------------------------------------------------|-----|----------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,     | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD | 0        | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-BIAS^4 = 1)$     |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 33       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 46       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 57       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 68       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 79       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 90       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD | 0        | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -33      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -45      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -57      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -67      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -78      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -88      | TBD | mV   |

| Comparator delay <sup>3</sup>             | t <sub>acmpdelay</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30       | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x10, FULLBIAS <sup>4</sup><br>= 0 |     | 3.7      | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 |     | 360      | _   | ns   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | _   | 35       | _   | ns   |

| Offset voltage                            | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _        | TBD | mV   |

| Reference voltage                         | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25     | TBD | V    |

|                                           |                        | Internal 2.5 V reference                                   | TBD | 2.5      | TBD | V    |

| Capacitive sense internal re-<br>sistance | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | _   | infinite | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 1                                  |     | 15       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 2                                  | —   | 27       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 3                                  | —   | 39       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 4                                  | —   | 51       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 5                                  | —   | 100      |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 6                                  | —   | 162      | -   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 7                                  | —   | 235      | -   | kΩ   |

## 4.1.23 I2C

## 4.1.23.1 I2C Standard-mode (Sm)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|-----|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0   | _   | 100  | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 4.7 | —   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 4   | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 250 | _   | _    | ns   |

| SDA hold time <sup>3</sup>                       | t <sub>HD_DAT</sub> |                | 100 | _   | 3450 | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 4.7 | _   | _    | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 4   | _   |      | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 4   | _   |      | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 4.7 | _   | _    | μs   |

## Table 4.31. I2C Standard-mode (Sm)<sup>1</sup>

### Note:

1. For CLHR set to 0 in the I2Cn\_CTRL register.

2. For the minimum HFPERCLK frequency required in Standard-mode, refer to the I2C chapter in the reference manual.

3. The maximum SDA hold time (t<sub>HD DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

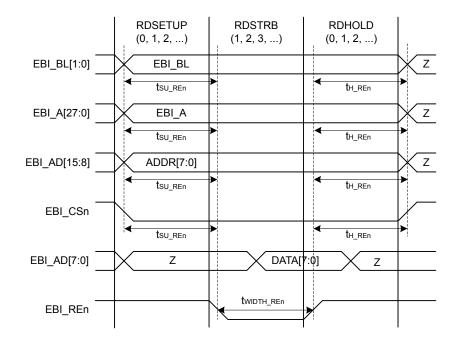

Figure 4.5. EBI Read Enable Output Timing Diagram

#### SDIO MMC SDR Mode Timing at 3.0 V

Timing is specified for route location 0 at 3.0 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 20 pF on all pins.

| Parameter                                          | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|----------------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer               | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    | —    | 48  | MHz  |

|                                                    |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                     | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 9.4  | _    | _   | ns   |

|                                                    |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                                    | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 9.4  | _    | _   | ns   |

|                                                    |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                                    | t <sub>R</sub>      |                                   | 1.96 | 3.87 | _   | ns   |

| Clock fall time                                    | t <sub>F</sub>      |                                   | 1.67 | 3.31 | _   | ns   |

| Input setup time, CMD,<br>DAT[0:7] valid to SD_CLK | t <sub>ISU</sub>    |                                   | 5.3  | -    | _   | ns   |

| Input hold time, SD_CLK to CMD, DAT[0:7] change    | tiH                 |                                   | 2.5  | -    | _   | ns   |

| Output delay time, SD_CLK to CMD, DAT[0:7] valid   | t <sub>ODLY</sub>   |                                   | 0    | -    | 16  | ns   |

| Output hold time, SD_CLK to CMD, DAT[0:7] change   | t <sub>OH</sub>     |                                   | 3    | -    | _   | ns   |

### Table 4.51. SDIO MMC SDR Mode Timing (Location 0, 3V I/O)

#### SDIO MMC DDR Mode Timing at 3.0 V

Timing is specified for route location 0 at 3.0 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 25 pF on all pins.

| Parameter                                     | Symbol              | Test Condition                    | Min  | Тур  | Мах      | Unit |

|-----------------------------------------------|---------------------|-----------------------------------|------|------|----------|------|

| Clock frequency during data transfer          | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    |      | 20       | MHz  |

|                                               |                     | Using HFXO                        | _    | _    | TBD      | MHz  |

| Clock low time                                | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 22.6 |      | _        | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _        | ns   |

| Clock high time                               | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 22.6 |      |          | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _        | ns   |

| Clock rise time                               | t <sub>R</sub>      |                                   | 1.13 | 2.37 | _        | ns   |

| Clock fall time                               | t <sub>F</sub>      |                                   | 1.01 | 2.02 | _        | ns   |

| Input setup time, CMD valid to SD_CLK         | t <sub>ISU</sub>    |                                   | 5.3  |      | _        | ns   |

| Input hold time, SD_CLK to CMD change         | t <sub>IH</sub>     |                                   | 2.5  |      |          | ns   |

| Output delay time, SD_CLK to CMD valid        | t <sub>ODLY</sub>   |                                   | 0    |      | 16       | ns   |

| Output hold time, SD_CLK to CMD change        | t <sub>OH</sub>     |                                   | 3    |      | _        | ns   |

| Input setup time, DAT[0:7]<br>valid to SD_CLK | t <sub>ISU2X</sub>  |                                   | 5.3  | _    | _        | ns   |

| Input hold time, SD_CLK to DAT[0:7] change    | t <sub>IH2X</sub>   |                                   | 2.5  | _    | _        | ns   |

| Output delay time, SD_CLK to DAT[0:7] valid   | t <sub>ODLY2X</sub> |                                   | 0    | _    | 16       | ns   |

| Output hold time, SD_CLK to DAT[0:7] change   | t <sub>OH2X</sub>   |                                   | 3    |      | <u> </u> | ns   |

### Table 4.53. SDIO MMC DDR Mode Timing (Location 0, 3V I/O)

## 4.1.28.2 QSPI DDR Mode

## **QSPI DDR Mode Timing (Location 0)**

Timing is specified with voltage scaling disabled, PHY-mode, route location 0 only, TX DLL = 35, RX DLL = 70, 20-25 pF loading per GPIO, and slew rate for all GPIO set to 6, DRIVESTRENGTH = STRONG.

## Table 4.56. QSPI DDR Mode Timing (Location 0)

| Parameter        | Symbol          | Test Condition           | Min                                   | Тур | Max       | Unit |

|------------------|-----------------|--------------------------|---------------------------------------|-----|-----------|------|

| Half SCLK period | T/2             | HFXO                     | (1/F <sub>SCLK</sub> ) *<br>0.4 - 0.4 | —   | -         | ns   |

|                  |                 | HFRCO, AUXHFRCO, USHFRCO | (1/F <sub>SCLK</sub> ) *<br>0.44      | —   | _         | ns   |

| Output valid     | t <sub>OV</sub> |                          | _                                     | _   | T/2 - 5.0 | ns   |

| Output hold      | t <sub>OH</sub> |                          | T/2 - 39.4                            | _   | —         | ns   |

| Input setup      | t <sub>SU</sub> |                          | 33.1                                  | _   | —         | ns   |

| Input hold       | t <sub>H</sub>  |                          | -0.9                                  |     | _         | ns   |

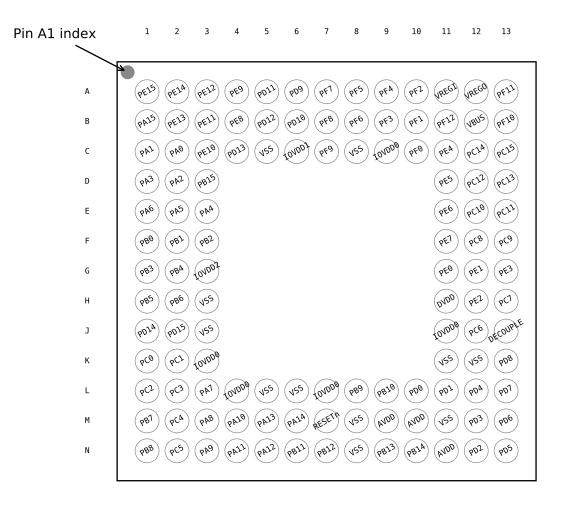

#### Figure 5.5. EFM32GG11B4xx in BGA120 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s) | Description             | Pin Name | Pin(s) | Description                                                                                      |

|----------|--------|-------------------------|----------|--------|--------------------------------------------------------------------------------------------------|

| PE15     | A1     | GPIO                    | PE14     | A2     | GPIO                                                                                             |

| PE12     | A3     | GPIO                    | PE9      | A4     | GPIO                                                                                             |

| PD11     | A5     | GPIO                    | PD9      | A6     | GPIO                                                                                             |

| PF7      | A7     | GPIO                    | PF5      | A8     | GPIO                                                                                             |

| PF4      | A9     | GPIO                    | PF2      | A10    | GPIO                                                                                             |

| VREGI    | A11    | Input to 5 V regulator. | VREGO    | A12    | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs |

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                                        |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                                        |

| PA8      | 17     | GPIO                                                                                                     | PA9      | 18       | GPIO                                                                                                                                                                                                        |

| PA10     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                                        |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                                        |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                                        |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                                        |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                                        |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                                        |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                                        |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                                       |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PC8      | 41       | GPIO (5V)                                                                                                                                                                                                   |

| PC9      | 42     | GPIO (5V)                                                                                                | PC10     | 43       | GPIO (5V)                                                                                                                                                                                                   |

| PC11     | 44     | GPIO (5V)                                                                                                | PC12     | 45       | GPIO (5V)                                                                                                                                                                                                   |

| PC13     | 46     | GPIO (5V)                                                                                                | PC14     | 47       | GPIO (5V)                                                                                                                                                                                                   |

| PC15     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                                   |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                                        |

| PF3      | 52     | GPIO                                                                                                     | PF4      | 53       | GPIO                                                                                                                                                                                                        |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                                        |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                                        |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                                        |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                                        |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                                             |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate     | LOCA                                   | TION  |                                                     |  |

|---------------|----------------------------------------|-------|-----------------------------------------------------|--|

| Functionality | 0 - 3                                  | 4 - 7 | Description                                         |  |

| EBI_A10       | 0: PE3<br>1: PD6<br>2: PC10<br>3: PB10 |       | External Bus Interface (EBI) address output pin 10. |  |

| EBI_A11       | 0: PE4<br>1: PD7<br>2: PI6<br>3: PB11  |       | External Bus Interface (EBI) address output pin 11. |  |

| EBI_A12       | 0: PE5<br>1: PD8<br>2: PI7<br>3: PB12  |       | External Bus Interface (EBI) address output pin 12. |  |

| EBI_A13       | 0: PE6<br>1: PC7<br>2: PI8<br>3: PD0   |       | External Bus Interface (EBI) address output pin 13. |  |

| EBI_A14       | 0: PE7<br>1: PE2<br>2: PI9<br>3: PD1   |       | External Bus Interface (EBI) address output pin 14. |  |

| EBI_A15       | 0: PC8<br>1: PE3<br>2: PI10<br>3: PD2  |       | External Bus Interface (EBI) address output pin 15. |  |

| EBI_A16       | 0: PB0<br>1: PE4<br>2: PH4<br>3: PD3   |       | External Bus Interface (EBI) address output pin 16. |  |

| EBI_A17       | 0: PB1<br>1: PE5<br>2: PH5<br>3: PD4   |       | External Bus Interface (EBI) address output pin 17. |  |

| EBI_A18       | 0: PB2<br>1: PE6<br>2: PH6<br>3: PD5   |       | External Bus Interface (EBI) address output pin 18. |  |

| EBI_A19       | 0: PB3<br>1: PE7<br>2: PH7<br>3: PD6   |       | External Bus Interface (EBI) address output pin 19. |  |

| EBI_A20       | 0: PB4<br>1: PC8<br>2: PH8<br>3: PD7   |       | External Bus Interface (EBI) address output pin 20. |  |

| EBI_A21       | 0: PB5<br>1: PC9<br>2: PH9<br>3: PC7   |       | External Bus Interface (EBI) address output pin 21. |  |

| EBI_A22       | 0: PB6<br>1: PC10<br>2: PH10<br>3: PE4 |       | External Bus Interface (EBI) address output pin 22. |  |

| Alternate LOCATION |                                        | ATION              |                                                                  |

|--------------------|----------------------------------------|--------------------|------------------------------------------------------------------|

| Functionality      | 0 - 3                                  | 4 - 7              | Description                                                      |

| EBI_CS1            | 0: PD10<br>1: PA11<br>2: PC1<br>3: PB1 | 4: PE9             | External Bus Interface (EBI) Chip Select output 1.               |

| EBI_CS2            | 0: PD11<br>1: PA12<br>2: PC2<br>3: PB2 | 4: PE10            | External Bus Interface (EBI) Chip Select output 2.               |

| EBI_CS3            | 0: PD12<br>1: PB15<br>2: PC3<br>3: PB3 | 4: PE11            | External Bus Interface (EBI) Chip Select output 3.               |

| EBI_CSTFT          | 0: PA7<br>1: PF6<br>2: PB12<br>3: PA0  |                    | External Bus Interface (EBI) Chip Select output TFT.             |

| EBI_DCLK           | 0: PA8<br>1: PF7<br>2: PH0<br>3: PA1   |                    | External Bus Interface (EBI) TFT Dot Clock pin.                  |

| EBI_DTEN           | 0: PA9<br>1: PD9<br>2: PH1<br>3: PA2   |                    | External Bus Interface (EBI) TFT Data Enable pin.                |

| EBI_HSNC           | 0: PA11<br>1: PD11<br>2: PH3<br>3: PA4 |                    | External Bus Interface (EBI) TFT Horizontal Synchronization pin. |

| EBI_NANDREn        | 0: PC3<br>1: PD15<br>2: PB9<br>3: PC4  | 4: PC15<br>5: PF12 | External Bus Interface (EBI) NAND Read Enable output.            |

| EBI_NANDWEn        | 0: PC5<br>1: PD14<br>2: PA13<br>3: PC2 | 4: PC14<br>5: PF11 | External Bus Interface (EBI) NAND Write Enable output.           |

| EBI_REn            | 0: PF5<br>1: PA14<br>2: PA12<br>3: PC0 | 4: PF9<br>5: PF5   | External Bus Interface (EBI) Read Enable output.                 |

| EBI_VSNC           | 0: PA10<br>1: PD10<br>2: PH2<br>3: PA3 |                    | External Bus Interface (EBI) TFT Vertical Synchronization pin.   |

| EBI_WEn            | 0: PF4<br>1: PA13<br>2: PC5<br>3: PB6  | 4: PF8<br>5: PF4   | External Bus Interface (EBI) Write Enable output.                |

| ETH_MDC            | 0: PB4<br>1: PD14<br>2: PC1<br>3: PA6  |                    | Ethernet Management Data Clock.                                  |

| Alternate<br>Functionality | LOC <i>A</i><br>0 - 3 | ATION<br>4 - 7 | Description          |

|----------------------------|-----------------------|----------------|----------------------|

| LCD_SEG7                   | 0: PE11               |                | LCD segment line 7.  |

| LCD_SEG8                   | 0: PE12               |                | LCD segment line 8.  |

| LCD_SEG9                   | 0: PE13               |                | LCD segment line 9.  |

| LCD_SEG10                  | 0: PE14               |                | LCD segment line 10. |

| LCD_SEG11                  | 0: PE15               |                | LCD segment line 11. |

| LCD_SEG12                  | 0: PA15               |                | LCD segment line 12. |

| LCD_SEG13                  | 0: PA0                |                | LCD segment line 13. |

| LCD_SEG14                  | 0: PA1                |                | LCD segment line 14. |

| LCD_SEG15                  | 0: PA2                |                | LCD segment line 15. |

| LCD_SEG16                  | 0: PA3                |                | LCD segment line 16. |

| LCD_SEG17                  | 0: PA4                |                | LCD segment line 17. |

| LCD_SEG18                  | 0: PA5                |                | LCD segment line 18. |

| LCD_SEG19                  | 0: PA6                |                | LCD segment line 19. |

| Alternate     | LOCA    | TION  |                                    |

|---------------|---------|-------|------------------------------------|

| Functionality | 0 - 3   | 4 - 7 | Description                        |

| LES_ALTEX6    | 0: PE12 |       | LESENSE alternate excite output 6. |

| LES_ALTEX7    | 0: PE13 |       | LESENSE alternate excite output 7. |

| LES_CH0       | 0: PC0  |       | LESENSE channel 0.                 |

| LES_CH1       | 0: PC1  |       | LESENSE channel 1.                 |

| LES_CH2       | 0: PC2  |       | LESENSE channel 2.                 |

| LES_CH3       | 0: PC3  |       | LESENSE channel 3.                 |

| LES_CH4       | 0: PC4  |       | LESENSE channel 4.                 |

| LES_CH5       | 0: PC5  |       | LESENSE channel 5.                 |

| LES_CH6       | 0: PC6  |       | LESENSE channel 6.                 |

| LES_CH7       | 0: PC7  |       | LESENSE channel 7.                 |

| LES_CH8       | 0: PC8  |       | LESENSE channel 8.                 |

| LES_CH9       | 0: PC9  |       | LESENSE channel 9.                 |

| LES_CH10      | 0: PC10 |       | LESENSE channel 10.                |

| Dimension | Min       | Тур  | Мах  |  |  |

|-----------|-----------|------|------|--|--|

| A         | 0.70      | 0.75 | 0.80 |  |  |

| A1        | 0.00      | _    | 0.05 |  |  |

| b         | 0.20      | 0.25 | 0.30 |  |  |

| A3        | 0.203 REF |      |      |  |  |

| D         | 9.00 BSC  |      |      |  |  |

| е         | 0.50 BSC  |      |      |  |  |

| E         | 9.00 BSC  |      |      |  |  |

| D2        | 7.10      | 7.20 | 7.30 |  |  |

| E2        | 7.10      | 7.20 | 7.30 |  |  |

| L         | 0.40      | 0.45 | 0.50 |  |  |

| L1        | 0.00      | _    | 0.10 |  |  |

| ааа       | 0.10      |      |      |  |  |

| bbb       | 0.10      |      |      |  |  |

| ссс       | 0.10      |      |      |  |  |

| ddd       | 0.05      |      |      |  |  |

| еее       | 0.08      |      |      |  |  |

| Note:     |           |      |      |  |  |

### Table 12.1. QFN64 Package Dimensions

### Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 13. Revision History

### **Revision 0.6**

March, 2018

- Removed "Confindential" watermark.

- Updated 4.1 Electrical Characteristics and 4.2 Typical Performance Curves with latest characterization data.

### Revision 0.2

October, 2017

- · Updated memory maps to latest formatting and to include all peripherals.

- Updated all electrical specifications tables with latest characterization results.

- Absolute Maximum Ratings Table:

- Removed redundant I<sub>VSSMAX</sub> line.

- Added footnote to clarify V<sub>DIGPIN</sub> specification for 5V tolerant GPIO.

- General Operating Conditions Table:

- Removed dV<sub>DD</sub> specification and redundant footnote about shorting VREGVDD and AVDD together.

- Added footnote about IOVDD voltage restriction when CSEN peripheral is used with chopping enabled.

- Flash Memory Characteristics Table: Added timing measurement clarification for Device Erase and Mass Erase.

- · Analog to Digital Converter (ADC) Table:

- · Added header text for general specification conditions.

- Added footnote for clarification of input voltage limits.

- · Minor typographical corrections, including capitalization, mis-spellings and punctuation marks, throughout document.

- Minor formatting and styling updates, including table formats, TOC location, and boilerplate information throughout document.

#### **Revision 0.1**

April 27th, 2017

Initial release.