Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                        |

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 93                                                                                                            |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 120-VFBGA                                                                                                     |

| Supplier Device Package    | 120-BGA (7x7)                                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b420f2048gl120-br                                  |

| 5. | . Pin Definitions                          |   | . 115 |

|----|--------------------------------------------|---|-------|

|    | 5.1 EFM32GG11B8xx in BGA192 Device Pinout  |   | 115   |

|    | 5.2 EFM32GG11B8xx in BGA152 Device Pinout  |   | 119   |

|    | 5.3 EFM32GG11B8xx in BGA120 Device Pinout  |   | 123   |

|    | 5.4 EFM32GG11B5xx in BGA120 Device Pinout  |   | 126   |

|    | 5.5 EFM32GG11B4xx in BGA120 Device Pinout  |   | 129   |

|    | 5.6 EFM32GG11B4xx in BGA112 Device Pinout  |   | 132   |

|    | 5.7 EFM32GG11B3xx in BGA112 Device Pinout  |   | 135   |

|    | 5.8 EFM32GG11B8xx in QFP100 Device Pinout  |   | 138   |

|    | 5.9 EFM32GG11B5xx in QFP100 Device Pinout  |   | 141   |

|    | 5.10 EFM32GG11B4xx in QFP100 Device Pinout |   | . 144 |

|    | 5.11 EFM32GG11B3xx in QFP100 Device Pinout |   | . 147 |

|    | 5.12 EFM32GG11B8xx in QFP64 Device Pinout  |   | 150   |

|    | 5.13 EFM32GG11B5xx in QFP64 Device Pinout  |   | 152   |

|    | 5.14 EFM32GG11B4xx in QFP64 Device Pinout  |   | 154   |

|    | 5.15 EFM32GG11B1xx in QFP64 Device Pinout  |   | 156   |

|    | 5.16 EFM32GG11B8xx in QFN64 Device Pinout  |   | 158   |

|    | 5.17 EFM32GG11B5xx in QFN64 Device Pinout  |   | 160   |

|    | 5.18 EFM32GG11B4xx in QFN64 Device Pinout  |   | 162   |

|    | 5.19 EFM32GG11B1xx in QFN64 Device Pinout  |   | 164   |

|    | 5.20 GPIO Functionality Table              |   | 166   |

|    | 5.21 Alternate Functionality Overview      |   | .178  |

|    | 5.22 Analog Port (APORT) Client Maps       |   | 211   |

| 6. | BGA192 Package Specifications              |   | .224  |

|    | 6.1 BGA192 Package Dimensions              |   | .224  |

|    | 6.2 BGA192 PCB Land Pattern                |   | 226   |

|    | 6.3 BGA192 Package Marking                 |   | 228   |

| 7. | . BGA152 Package Specifications            |   | .229  |

|    | 7.1 BGA152 Package Dimensions              |   | .229  |

|    | 7.2 BGA152 PCB Land Pattern                |   |       |

|    | 7.3 BGA152 Package Marking                 |   |       |

| 8. | BGA120 Package Specifications              |   | .234  |

| ٠. | 8.1 BGA120 Package Dimensions              |   | .234  |

|    | 8.2 BGA120 PCB Land Pattern                |   |       |

|    | 8.3 BGA120 Package Marking                 |   |       |

| ۵  | BGA112 Package Specifications              | • | .239  |

| J. | 9.1 BGA112 Package Dimensions              | • | .239  |

|    |                                            |   |       |

### 3.10.2 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the microcontroller. The flash memory is readable and writable from both the Cortex-M and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block, whereas the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in energy modes EM0 Active and EM1 Sleep.

### 3.10.3 Linked Direct Memory Access Controller (LDMA)

The Linked Direct Memory Access (LDMA) controller allows the system to perform memory operations independently of software. This reduces both energy consumption and software workload. The LDMA allows operations to be linked together and staged, enabling sophisticated operations to be implemented.

### 3.10.4 Bootloader

All devices come pre-programmed with a UART bootloader. This bootloader resides in flash and can be erased if it is not needed. More information about the bootloader protocol and usage can be found in *AN0003: UART Bootloader*. Application notes can be found on the Silicon Labs website (www.silabs.com/32bit-appnotes) or within Simplicity Studio in the [**Documentation**] area.

# 4.1.4 DC-DC Converter

Test conditions: L\_DCDC=4.7  $\mu$ H (Murata LQH3NPN4R7MM0L), C\_DCDC=4.7  $\mu$ F (Samsung CL10B475KQ8NQNC), V\_DCDC\_I=3.3 V, V\_DCDC\_O=1.8 V, I\_DCDC\_LOAD=50 mA, Heavy Drive configuration, F\_DCDC\_LN=7 MHz, unless otherwise indicated.

Table 4.4. DC-DC Converter

| Parameter                                           | Symbol              | Test Condition                                                                                                                           | Min | Тур | Max                         | Unit |

|-----------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                 | V <sub>DCDC_I</sub> | Bypass mode, I <sub>DCDC_LOAD</sub> = 50 mA                                                                                              | 1.8 | _   | V <sub>VREGVDD</sub> _      | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, I <sub>DCDC_LOAD</sub> = 100 mA, or Low power (LP) mode, 1.8 V output, I <sub>DCDC_LOAD</sub> = 10 mA | 2.4 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V output, I <sub>DCDC_LOAD</sub> = 200 mA                                                                       | 2.6 | _   | V <sub>VREGVDD</sub> _      | V    |

| Output voltage programma-<br>ble range <sup>1</sup> | V <sub>DCDC_O</sub> |                                                                                                                                          | 1.8 | _   | V <sub>VREGVDD</sub>        | V    |

| Regulation DC accuracy                              | ACC <sub>DC</sub>   | Low Noise (LN) mode, 1.8 V target output                                                                                                 | TBD | _   | TBD                         | V    |

| Regulation window <sup>4</sup>                      | WIN <sub>REG</sub>  | Low Power (LP) mode,<br>LPCMPBIASEMxx³ = 0, 1.8 V target output, I <sub>DCDC_LOAD</sub> ≤ 75 μA                                          | TBD | _   | TBD                         | V    |

|                                                     |                     | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3, 1.8 V target output, I <sub>DCDC_LOAD</sub> ≤ 10 mA                              | TBD | _   | TBD                         | V    |

| Steady-state output ripple                          | V <sub>R</sub>      |                                                                                                                                          | _   | 3   | _                           | mVpp |

| Output voltage under/over-<br>shoot                 | V <sub>OV</sub>     | CCM Mode (LNFORCECCM <sup>3</sup> = 1), Load changes between 0 mA and 100 mA                                                             | _   | 25  | TBD                         | mV   |

|                                                     |                     | DCM Mode (LNFORCECCM <sup>3</sup> = 0), Load changes between 0 mA and 10 mA                                                              | _   | 45  | TBD                         | mV   |

|                                                     |                     | Overshoot during LP to LN CCM/DCM mode transitions compared to DC level in LN mode                                                       | _   | 200 | _                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN CCM (LNFORCECCM <sup>3</sup> = 1) mode transitions compared to DC level in LN mode                        | _   | 40  | _                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN DCM (LNFORCECCM <sup>3</sup> = 0) mode transitions compared to DC level in LN mode                        | _   | 100 | _                           | mV   |

| DC line regulation                                  | V <sub>REG</sub>    | Input changes between V <sub>VREGVDD_MAX</sub> and 2.4 V                                                                                 | _   | 0.1 | _                           | %    |

| DC load regulation                                  | I <sub>REG</sub>    | Load changes between 0 mA and 100 mA in CCM mode                                                                                         | _   | 0.1 | _                           | %    |

### 4.1.7 Current Consumption

# 4.1.7.1 Current Consumption 3.3 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 3.3 V.  $T = 25 ^{\circ}C$ . DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at  $T = 25 ^{\circ}C$ .

Table 4.7. Current Consumption 3.3 V without DC-DC Converter

| Parameter                                                              | Symbol                 | Test Condition                                        | Min | Тур | Max | Unit   |

|------------------------------------------------------------------------|------------------------|-------------------------------------------------------|-----|-----|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE</sub>    | 72 MHz HFRCO, CPU running<br>Prime from flash         | _   | 120 | _   | μA/MHz |

| abled                                                                  |                        | 72 MHz HFRCO, CPU running while loop from flash       | _   | 120 | TBD | µA/MHz |

|                                                                        |                        | 72 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 140 | _   | µA/MHz |

|                                                                        |                        | 50 MHz crystal, CPU running while loop from flash     | _   | 123 | _   | μA/MHz |

|                                                                        |                        | 48 MHz HFRCO, CPU running while loop from flash       | _   | 122 | TBD | μA/MHz |

|                                                                        |                        | 32 MHz HFRCO, CPU running while loop from flash       | _   | 124 | _   | μA/MHz |

|                                                                        |                        | 26 MHz HFRCO, CPU running while loop from flash       | _   | 126 | TBD | μA/MHz |

|                                                                        |                        | 16 MHz HFRCO, CPU running while loop from flash       | _   | 131 | _   | μA/MHz |

|                                                                        |                        | 1 MHz HFRCO, CPU running while loop from flash        | _   | 319 | TBD | μA/MHz |

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE_VS</sub> | 19 MHz HFRCO, CPU running while loop from flash       | _   | 107 | _   | μA/MHz |

| abled and voltage scaling enabled                                      |                        | 1 MHz HFRCO, CPU running while loop from flash        | _   | 262 | _   | μA/MHz |

| Current consumption in EM1                                             | I <sub>EM1</sub>       | 72 MHz HFRCO                                          | _   | 57  | TBD | μΑ/MHz |

| mode with all peripherals disabled                                     |                        | 50 MHz crystal                                        | _   | 60  | _   | μΑ/MHz |

|                                                                        |                        | 48 MHz HFRCO                                          | _   | 59  | TBD | μΑ/MHz |

|                                                                        |                        | 32 MHz HFRCO                                          | _   | 61  | _   | μΑ/MHz |

|                                                                        |                        | 26 MHz HFRCO                                          | _   | 63  | TBD | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO                                          | _   | 68  | _   | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO                                           | _   | 255 | TBD | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub>    | 19 MHz HFRCO                                          | _   | 55  | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                        | 1 MHz HFRCO                                           | _   | 210 | _   | μΑ/MHz |

| Parameter                                                                      | Symbol               | Test Condition                                                                                          | Min | Тур  | Max | Unit |

|--------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Current consumption in EM2 mode, with voltage scaling                          | I <sub>EM2_VS</sub>  | Full 512 kB RAM retention and RTCC running from LFXO                                                    | _   | 3.9  | _   | μA   |

| enabled                                                                        |                      | Full 512 kB RAM retention and RTCC running from LFRCO                                                   | _   | 4.3  | _   | μA   |

|                                                                                |                      | 16 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup>                                   | _   | 2.8  | TBD | μA   |

| Current consumption in EM3 mode, with voltage scaling enabled                  | I <sub>EM3_VS</sub>  | Full 512 kB RAM retention and CRYOTIMER running from ULFR-CO                                            | _   | 3.6  | TBD | μА   |

| Current consumption in EM4H mode, with voltage                                 | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | _   | 1.08 | _   | μA   |

| scaling enabled                                                                |                      | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO                                              | _   | 0.69 | _   | μA   |

|                                                                                |                      | 128 byte RAM retention, no RTCC                                                                         | _   | 0.69 | TBD | μΑ   |

| Current consumption in EM4S mode                                               | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | _   | 0.16 | TBD | μA   |

| Current consumption of peripheral power domain 1, with voltage scaling enabled | I <sub>PD1_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _   | 0.68 | _   | μA   |

| Current consumption of peripheral power domain 2, with voltage scaling enabled | I <sub>PD2_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _   | 0.28 | _   | μA   |

- 1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.4 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

- 2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

# 4.1.7.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output. T = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

Table 4.8. Current Consumption 3.3 V using DC-DC Converter

| Parameter                                                 | Symbol                  | Test Condition                                        | Min | Тур  | Max | Unit   |

|-----------------------------------------------------------|-------------------------|-------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0 mode with all peripherals dis- | IACTIVE_DCM             | 72 MHz HFRCO, CPU running<br>Prime from flash         | _   | 80   | _   | μΑ/MHz |

| abled, DCDC in Low Noise DCM mode <sup>2</sup>            |                         | 72 MHz HFRCO, CPU running while loop from flash       | _   | 80   | _   | μA/MHz |

|                                                           |                         | 72 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 92   | _   | μΑ/MHz |

|                                                           |                         | 50 MHz crystal, CPU running while loop from flash     | _   | 84   | _   | μΑ/MHz |

|                                                           |                         | 48 MHz HFRCO, CPU running while loop from flash       | _   | 84   | _   | μA/MHz |

|                                                           |                         | 32 MHz HFRCO, CPU running while loop from flash       | _   | 90   | _   | μΑ/MHz |

|                                                           |                         | 26 MHz HFRCO, CPU running while loop from flash       | _   | 94   | _   | μΑ/MHz |

|                                                           |                         | 16 MHz HFRCO, CPU running while loop from flash       | _   | 109  | _   | μΑ/MHz |

|                                                           |                         | 1 MHz HFRCO, CPU running while loop from flash        | _   | 698  | _   | μΑ/MHz |

| Current consumption in EM0 mode with all peripherals dis- | I <sub>ACTIVE_CCM</sub> | 72 MHz HFRCO, CPU running<br>Prime from flash         | _   | 84   | _   | μΑ/MHz |

| abled, DCDC in Low Noise<br>CCM mode <sup>1</sup>         |                         | 72 MHz HFRCO, CPU running while loop from flash       | _   | 84   | _   | μA/MHz |

|                                                           |                         | 72 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 95   | _   | μΑ/MHz |

|                                                           |                         | 50 MHz crystal, CPU running while loop from flash     | _   | 91   | _   | μA/MHz |

|                                                           |                         | 48 MHz HFRCO, CPU running while loop from flash       | _   | 92   | _   | μΑ/MHz |

|                                                           |                         | 32 MHz HFRCO, CPU running while loop from flash       | _   | 104  | _   | μA/MHz |

|                                                           |                         | 26 MHz HFRCO, CPU running while loop from flash       | _   | 113  | _   | μΑ/MHz |

|                                                           |                         | 16 MHz HFRCO, CPU running while loop from flash       | _   | 142  | _   | μΑ/MHz |

|                                                           |                         | 1 MHz HFRCO, CPU running while loop from flash        | _   | 1264 | _   | μA/MHz |

# 4.1.10.2 High-Frequency Crystal Oscillator (HFXO)

Table 4.13. High-Frequency Crystal Oscillator (HFXO)

| Parameter                                     | Symbol              | Test Condition                                          | Min | Тур   | Max  | Unit |

|-----------------------------------------------|---------------------|---------------------------------------------------------|-----|-------|------|------|

| Crystal frequency                             | f <sub>HFXO</sub>   | No clock doubling                                       | 4   | _     | 50   | MHz  |

|                                               |                     | Clock doubler enabled                                   | TBD | _     | TBD  | MHz  |

| Supported crystal equivalent                  | ESR <sub>HFXO</sub> | 50 MHz crystal                                          | _   | _     | 50   | Ω    |

| series resistance (ESR)                       |                     | 24 MHz crystal                                          | _   | _     | 150  | Ω    |

|                                               |                     | 4 MHz crystal                                           | _   | _     | 180  | Ω    |

| Nominal on-chip tuning cap range <sup>1</sup> | C <sub>HFXO_T</sub> | On each of HFXTAL_N and HFXTAL_P pins                   | 8.7 | _     | 51.7 | pF   |

| On-chip tuning capacitance step               | SS <sub>HFXO</sub>  |                                                         | _   | 0.084 | _    | pF   |

| Startup time                                  | t <sub>HFXO</sub>   | 50 MHz crystal, ESR = 50 Ohm,<br>C <sub>L</sub> = 8 pF  | _   | 350   | _    | μs   |

|                                               |                     | 24 MHz crystal, ESR = 150 Ohm,<br>C <sub>L</sub> = 6 pF | _   | 700   | _    | μs   |

|                                               |                     | 4 MHz crystal, ESR = 180 Ohm,<br>C <sub>L</sub> = 18 pF | _   | 3     | _    | ms   |

| Current consumption after                     | I <sub>HFXO</sub>   | 50 MHz crystal                                          | _   | 880   | _    | μA   |

| startup                                       |                     | 24 MHz crystal                                          | _   | 420   | _    | μA   |

|                                               |                     | 4 MHz crystal                                           | _   | 80    | _    | μA   |

<sup>1.</sup> The effective load capacitance seen by the crystal will be  $C_{HFXO\_T}$  /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

# 4.1.12 General-Purpose I/O (GPIO)

Table 4.20. General-Purpose I/O (GPIO)

| Parameter                                                      | Symbol                 | Test Condition                                     | Min       | Тур      | Max       | Unit |

|----------------------------------------------------------------|------------------------|----------------------------------------------------|-----------|----------|-----------|------|

| Input low voltage                                              | V <sub>IL</sub>        | GPIO pins                                          | _         | _        | IOVDD*0.3 | V    |

| Input high voltage                                             | V <sub>IH</sub>        | GPIO pins                                          | IOVDD*0.7 | _        | _         | V    |

| Output high voltage relative                                   | V <sub>OH</sub>        | Sourcing 3 mA, IOVDD ≥ 3 V,                        | IOVDD*0.8 | _        | _         | V    |

| to IOVDD                                                       |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                  |           |          |           |      |

|                                                                |                        | Sourcing 1.2 mA, IOVDD ≥ 1.62 V,                   | IOVDD*0.6 | _        | _         | V    |

|                                                                |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                  |           |          |           |      |

|                                                                |                        | Sourcing 20 mA, IOVDD ≥ 3 V,                       | IOVDD*0.8 | _        | _         | V    |

|                                                                |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                |           |          |           |      |

|                                                                |                        | Sourcing 8 mA, IOVDD ≥ 1.62 V,                     | IOVDD*0.6 | _        | _         | V    |

|                                                                |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                |           |          |           |      |

| Output low voltage relative to                                 | V <sub>OL</sub>        | Sinking 3 mA, IOVDD ≥ 3 V,                         | _         | _        | IOVDD*0.2 | V    |

| IOVDD                                                          |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                  |           |          |           |      |

|                                                                |                        | Sinking 1.2 mA, IOVDD ≥ 1.62 V,                    | _         | _        | IOVDD*0.4 | V    |

|                                                                |                        | DRIVESTRENGTH <sup>1</sup> = WEAK                  |           |          |           |      |

|                                                                |                        | Sinking 20 mA, IOVDD ≥ 3 V,                        | _         | _        | IOVDD*0.2 | V    |

|                                                                |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                |           |          |           |      |

|                                                                |                        | Sinking 8 mA, IOVDD ≥ 1.62 V,                      | _         | _        | IOVDD*0.4 | V    |

|                                                                |                        | DRIVESTRENGTH <sup>1</sup> = STRONG                |           |          |           |      |

| Input leakage current                                          | I <sub>IOLEAK</sub>    | All GPIO except LFXO pins, GPIO ≤ IOVDD, T ≤ 85 °C | _         | 0.1      | TBD       | nA   |

|                                                                |                        | LFXO Pins, GPIO ≤ IOVDD, T ≤ 85 °C                 | _         | 0.1      | TBD       | nA   |

|                                                                |                        | All GPIO except LFXO pins, GPIO ≤ IOVDD, T > 85 °C | _         | <u>—</u> | TBD       | nA   |

|                                                                |                        | LFXO Pins, GPIO ≤ IOVDD, T > 85 °C                 | _         | _        | TBD       | nA   |

| Input leakage current on 5VTOL pads above IOVDD                | I <sub>5VTOLLEAK</sub> | IOVDD < GPIO ≤ IOVDD + 2 V                         | _         | 3.3      | TBD       | μΑ   |

| I/O pin pull-up/pull-down resistor                             | R <sub>PUD</sub>       |                                                    | TBD       | 40       | TBD       | kΩ   |

| Pulse width of pulses removed by the glitch suppression filter | t <sub>IOGLITCH</sub>  |                                                    | 15        | 25       | 35        | ns   |

| Parameter                                               | Symbol                   | Test Condition                                                                              | Min | Тур  | Max | Unit |

|---------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------|-----|------|-----|------|

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC</sub>      | 500 ksps, single-ended, internal 1.25V reference                                            | _   | 60.4 | _   | dB   |

| Noise band limited to 250 kHz                           |                          | 500 ksps, single-ended, internal 2.5V reference                                             | _   | 61.6 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                               | _   | 64.0 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 1.25V reference                                            | _   | 63.3 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 2.5V reference                                             | _   | 64.4 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                  | _   | 65.8 | _   | dB   |

| Signal to noise and distortion ratio (1 kHz sine wave), | SNDR <sub>DAC_BAND</sub> | 500 ksps, single-ended, internal 1.25V reference                                            | _   | 65.3 | _   | dB   |

| Noise band limited to 22 kHz                            |                          | 500 ksps, single-ended, internal 2.5V reference                                             | _   | 66.7 | _   | dB   |

|                                                         |                          | 500 ksps, differential, 3.3V VDD reference                                                  | _   | 68.5 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 1.25V reference                                            | _   | 67.8 | _   | dB   |

|                                                         |                          | 500 ksps, differential, internal 2.5V reference                                             | _   | 69.0 | _   | dB   |

|                                                         |                          | 500 ksps, single-ended, 3.3V<br>VDD reference                                               | _   | 70.0 | _   | dB   |

| Total harmonic distortion                               | THD                      |                                                                                             | _   | 70.2 | _   | dB   |

| Differential non-linearity <sup>3</sup>                 | DNL <sub>DAC</sub>       |                                                                                             | TBD | _    | TBD | LSB  |

| Intergral non-linearity                                 | INL <sub>DAC</sub>       |                                                                                             | TBD | _    | TBD | LSB  |

| Offset error <sup>5</sup>                               | V <sub>OFFSET</sub>      | T = 25 °C                                                                                   | TBD | _    | TBD | mV   |

|                                                         |                          | Across operating temperature range                                                          | TBD | _    | TBD | mV   |

| Gain error <sup>5</sup>                                 | $V_{GAIN}$               | T = 25 °C, Low-noise internal reference (REFSEL = 1V25LN or 2V5LN)                          | TBD | _    | TBD | %    |

|                                                         |                          | Across operating temperature range, Low-noise internal reference (REFSEL = 1V25LN or 2V5LN) | TBD | _    | TBD | %    |

| External load capactiance, OUTSCALE=0                   | C <sub>LOAD</sub>        |                                                                                             | _   | _    | 75  | pF   |

| Parameter | Symbol | Test Condition | Min | Tvp | Max | Unit |

|-----------|--------|----------------|-----|-----|-----|------|

|           |        |                |     | 7 F |     | 4    |

#### Note:

- 1. Specified configuration for 3X-Gain configuration is: INCBW = 1, HCMDIS = 1, RESINSEL = VSS, V<sub>INPUT</sub> = 0.5 V, V<sub>OUTPUT</sub> = 1.5 V. Nominal voltage gain is 3.

- 2. If the maximum C<sub>LOAD</sub> is exceeded, an isolation resistor is required for stability. See AN0038 for more information.

- 3. When INCBW is set to 1 the OPAMP bandwidth is increased. This is allowed only when the non-inverting close-loop gain is ≥ 3, or the OPAMP may not be stable.

- 4. Current into the load resistor is excluded. When the OPAMP is connected with closed-loop gain > 1, there will be extra current to drive the resistor feedback network. The internal resistor feedback network has total resistance of 143.5 kOhm, which will cause another ~10 μA current when the OPAMP drives 1.5 V between output and ground.

- 5. Step between 0.2V and V<sub>OPA</sub>-0.2V, 10%-90% rising/falling range.

- 6. From enable to output settled. In sample-and-off mode, RC network after OPAMP will contribute extra delay. Settling error < 1mV.

- 7. In unit gain connection, UGF is the gain-bandwidth product of the OPAMP. In 3x Gain connection, UGF is the gain-bandwidth product of the OPAMP and 1/3 attenuation of the feedback network.

- 8. Specified configuration for Unit gain buffer configuration is: INCBW = 0, HCMDIS = 0, RESINSEL = DISABLE.  $V_{INPUT}$  = 0.5 V,  $V_{OUTPUT}$  = 0.5 V.

- 9. When HCMDIS=1 and input common mode transitions the region from V<sub>OPA</sub>-1.4V to V<sub>OPA</sub>-1V, input offset will change. PSRR and CMRR specifications do not apply to this transition region.

### 4.1.20 LCD Driver

Table 4.28. LCD Driver

| Parameter                                   | Symbol                   | Test Condition                                 | Min | Тур  | Max                         | Unit |

|---------------------------------------------|--------------------------|------------------------------------------------|-----|------|-----------------------------|------|

| Frame rate                                  | f <sub>LCDFR</sub>       |                                                | TBD | _    | TBD                         | Hz   |

| LCD supply range <sup>2</sup>               | V <sub>LCDIN</sub>       |                                                | 1.8 | _    | 3.8                         | V    |

| LCD output voltage range                    | V <sub>LCD</sub>         | Current source mode, No external LCD capacitor | 2.0 | _    | V <sub>LCDIN</sub> -0.4     | V    |

|                                             |                          | Step-down mode with external LCD capacitor     | 2.0 | _    | V <sub>LCDIN</sub>          | V    |

|                                             |                          | Charge pump mode with external LCD capacitor   | 2.0 | _    | 1.9 *<br>V <sub>LCDIN</sub> | V    |

| Contrast control step size                  | STEP <sub>CONTRAST</sub> | Current source mode                            | _   | 64   | _                           | mV   |

|                                             |                          | Charge pump or Step-down mode                  | _   | 43   | _                           | mV   |

| Contrast control step accuracy <sup>1</sup> | ACC <sub>CONTRAST</sub>  |                                                | _   | +/-4 | _                           | %    |

- 1. Step size accuracy is measured relative to the typical step size, and typ value represents one standard deviation.

- 2. V<sub>LCDIN</sub> is selectable between the AVDD or DVDD supply pins, depending on EMU\_PWRCTRL\_ANASW.

# 4.1.23.3 I2C Fast-mode Plus (Fm+)<sup>1</sup>

Table 4.33. I2C Fast-mode Plus (Fm+)<sup>1</sup>

| Parameter                                        | Symbol              | Test Condition | Min  | Тур | Max  | Unit |

|--------------------------------------------------|---------------------|----------------|------|-----|------|------|

| SCL clock frequency <sup>2</sup>                 | f <sub>SCL</sub>    |                | 0    | _   | 1000 | kHz  |

| SCL clock low time                               | t <sub>LOW</sub>    |                | 0.5  | _   | _    | μs   |

| SCL clock high time                              | t <sub>HIGH</sub>   |                | 0.26 | _   | _    | μs   |

| SDA set-up time                                  | t <sub>SU_DAT</sub> |                | 50   | _   | _    | ns   |

| SDA hold time                                    | t <sub>HD_DAT</sub> |                | 100  | _   | _    | ns   |

| Repeated START condition set-up time             | t <sub>SU_STA</sub> |                | 0.26 | _   | _    | μs   |

| (Repeated) START condition hold time             | t <sub>HD_STA</sub> |                | 0.26 | _   | _    | μs   |

| STOP condition set-up time                       | t <sub>SU_STO</sub> |                | 0.26 | _   | _    | μs   |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                | 0.5  | _   | _    | μs   |

- 1. For CLHR set to 0 or 1 in the I2Cn\_CTRL register.

- 2. For the minimum HFPERCLK frequency required in Fast-mode Plus, refer to the I2C chapter in the reference manual.

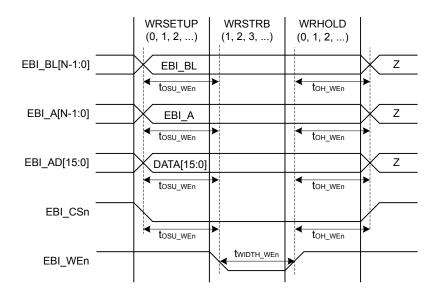

Figure 4.3. EBI Write Enable Output Timing Diagram

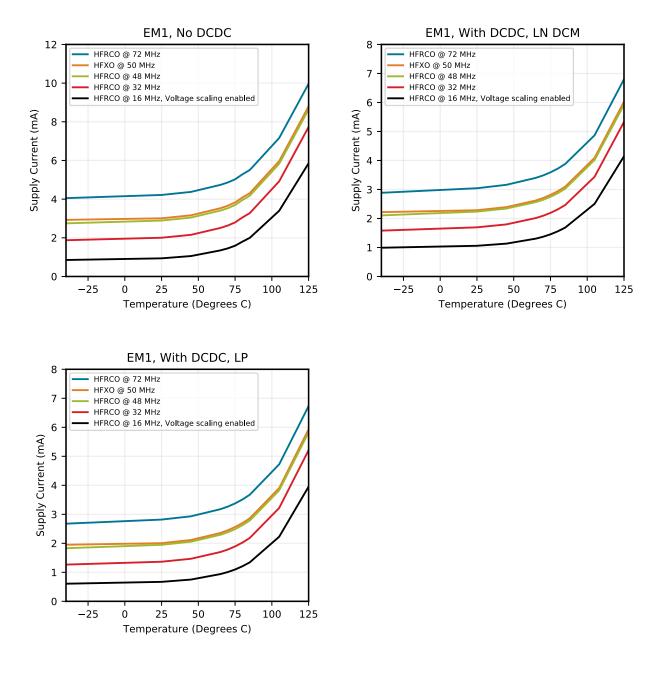

# 4.2 Typical Performance Curves

Typical performance curves indicate typical characterized performance under the stated conditions.

Figure 4.25. EM1 Sleep Mode Typical Supply Current vs. Temperature

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

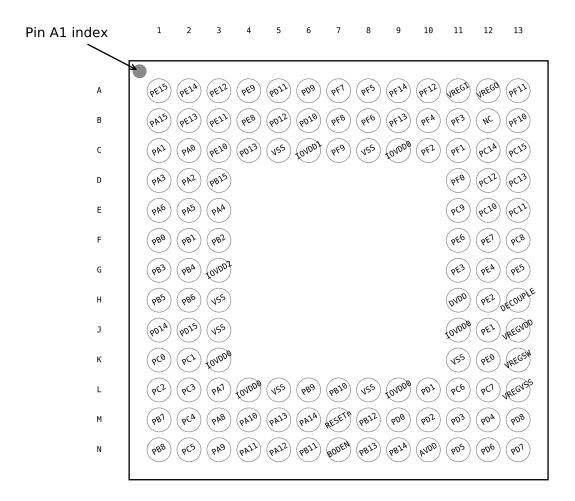

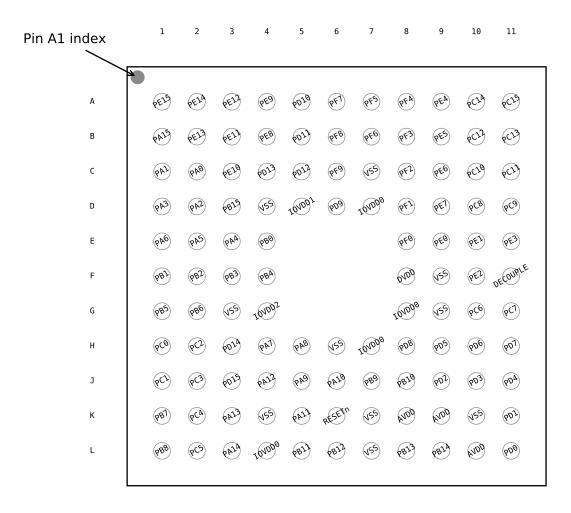

### 5.4 EFM32GG11B5xx in BGA120 Device Pinout

Figure 5.4. EFM32GG11B5xx in BGA120 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

Table 5.4. EFM32GG11B5xx in BGA120 Device Pinout

| Pin Name | Pin(s) | Description             | Pin Name | Pin(s) | Description                                                                              |

|----------|--------|-------------------------|----------|--------|------------------------------------------------------------------------------------------|

| PE15     | A1     | GPIO                    | PE14     | A2     | GPIO                                                                                     |

| PE12     | A3     | GPIO                    | PE9      | A4     | GPIO                                                                                     |

| PD11     | A5     | GPIO                    | PD9      | A6     | GPIO                                                                                     |

| PF7      | A7     | GPIO                    | PF5      | A8     | GPIO                                                                                     |

| PF14     | A9     | GPIO (5V)               | PF12     | A10    | GPIO                                                                                     |

| VREGI    | A11    | Input to 5 V regulator. | VREGO    | A12    | Decoupling for 5 V regulator and regulator output. Power for USB PHY in USB-enabled OPNs |

### 5.7 EFM32GG11B3xx in BGA112 Device Pinout

Figure 5.7. EFM32GG11B3xx in BGA112 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

Table 5.7. EFM32GG11B3xx in BGA112 Device Pinout

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description |

|----------|--------|-------------|----------|--------|-------------|

| PE15     | A1     | GPIO        | PE14     | A2     | GPIO        |

| PE12     | A3     | GPIO        | PE9      | A4     | GPIO        |

| PD10     | A5     | GPIO        | PF7      | A6     | GPIO        |

| PF5      | A7     | GPIO        | PF4      | A8     | GPIO        |

| PE4      | A9     | GPIO        | PC14     | A10    | GPIO (5V)   |

| PC15     | A11    | GPIO (5V)   | PA15     | B1     | GPIO        |

| PE13     | B2     | GPIO        | PE11     | В3     | GPIO        |

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                 |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                        |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                        |

| PA8      | 17     | GPIO                                                                                                     | PA9      | 18       | GPIO                                                                                                                                                                                        |

| PA10     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                        |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                        |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                        |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                        |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                        |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                        |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                        |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                       |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PC8      | 41       | GPIO (5V)                                                                                                                                                                                   |

| PC9      | 42     | GPIO (5V)                                                                                                | PC10     | 43       | GPIO (5V)                                                                                                                                                                                   |

| PC11     | 44     | GPIO (5V)                                                                                                | PC12     | 45       | GPIO (5V)                                                                                                                                                                                   |

| PC13     | 46     | GPIO (5V)                                                                                                | PC14     | 47       | GPIO (5V)                                                                                                                                                                                   |

| PC15     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                   |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                        |

| PF3      | 52     | GPIO                                                                                                     | PF4      | 53       | GPIO                                                                                                                                                                                        |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                        |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                        |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                        |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                        |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                             |

# Note:

1. GPIO with 5V tolerance are indicated by (5V).

| <b>GPIO Name</b> |                                                               | Pin Alter                  | nate Functionality / De                                                                       | escription                                                                                        |                                                    |

|------------------|---------------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------|

|                  | Analog                                                        | EBI                        | Timers                                                                                        | Communication                                                                                     | Other                                              |

| PD13             |                                                               | EBI_ARDY#1                 | TIM2_CDTI0 #1<br>TIM3_CC1 #6<br>WTIM0_CC1 #1                                                  | ETH_MDIO #1<br>US4_CTS #1<br>US5_CLK #1                                                           | ETM_TD1 #1                                         |

| PI15             |                                                               |                            |                                                                                               | CAN1_TX #7<br>US3_CS #5                                                                           |                                                    |

| PI14             |                                                               |                            |                                                                                               | CAN1_RX #7<br>US3_CLK #5                                                                          |                                                    |

| PI13             |                                                               |                            |                                                                                               | CAN0_TX #7<br>US3_RX #5                                                                           |                                                    |

| PI12             |                                                               |                            |                                                                                               | CAN0_RX #7<br>US3_TX #5                                                                           |                                                    |

| PI10             |                                                               | EBI_A15 #2                 | TIM4_CC2 #3                                                                                   | US4_CTS #3                                                                                        |                                                    |

| PI7              |                                                               | EBI_A12 #2                 | TIM1_CC1 #7<br>TIM4_CC2 #2<br>WTIM3_CC1 #5                                                    | US4_RX #3                                                                                         |                                                    |

| PF15             | BUSCY BUSDX                                                   |                            | TIM1_CC2 #6<br>TIM4_CC2 #1<br>WTIM3_CC2 #7                                                    | US5_TX #2<br>I2C2_SDA #5                                                                          |                                                    |

| PF12             | BUSDY BUSCX                                                   | EBI_NANDREn #5             | TIM4_CC2 #0<br>TIM1_CC3 #5<br>TIM5_CC0 #7<br>WTIM3_CC2 #6                                     | US5_CS #2<br>I2C2_SCL #3<br>USB_ID                                                                |                                                    |

| PF4              | BUSDY BUSCX<br>LCD_SEG2                                       | EBI_WEn #0<br>EBI_WEn #5   | TIM4_CC1 #0<br>TIM0_CDTI1 #2<br>TIM1_CC2 #5<br>WTIM3_CC1 #6                                   | US1_RTS #2<br>I2C2_SDA #3                                                                         | PRS_CH1 #1                                         |

| PC15             | VDAC0_OUT1ALT /<br>OPA1_OUTALT #3<br>BUSACMP1Y BU-<br>SACMP1X | EBI_NANDREn #4             | TIM0_CDTI2 #1<br>TIM1_CC2 #0<br>WTIM0_CC0 #4 LE-<br>TIM0_OUT1 #5                              | US0_CLK #3<br>US1_CLK #3<br>US3_RTS #3 U0_RX<br>#3 U1_RTS #0<br>LEU0_RX #5<br>I2C2_SCL #1         | LES_CH15<br>PRS_CH1 #2<br>ACMP3_O #1<br>DBG_SWO #1 |

| PC14             | VDAC0_OUT1ALT /<br>OPA1_OUTALT #2<br>BUSACMP1Y BU-<br>SACMP1X | EBI_NANDWEn #4             | TIM0_CDTI1 #1 TIM1_CC1 #0 TIM1_CC3 #4 TIM5_CC0 #6 WTIM3_CC0 #3 LE- TIM0_OUT0 #5 PCNT0_S1IN #0 | US0_CS #3 US1_CS<br>#3 US2_RTS #3<br>US3_CS #2 U0_TX<br>#3 U1_CTS #0<br>LEU0_TX #5<br>I2C2_SDA #1 | LES_CH14<br>PRS_CH0 #2<br>ACMP3_O #2               |

| PA2              | BUSBY BUSAX<br>LCD_SEG15                                      | EBI_AD11 #0<br>EBI_DTEN #3 | TIM0_CC2 #0<br>TIM3_CC2 #4                                                                    | ETH_RMIIRXD0 #0<br>ETH_MIITXD2 #0<br>SDIO_DAT2 #1<br>US1_RX #6<br>US3_CLK #0<br>QSPI0_DQ0 #1      | CMU_CLK0 #0<br>PRS_CH8 #1<br>ETM_TD0 #3            |

| PG0              | BUSACMP2Y BU-<br>SACMP2X                                      | EBI_AD00 #2                | TIM6_CC0 #0<br>TIM2_CDTI0 #3<br>WTIM0_CDTI1 #1<br>LETIM1_OUT0 #6                              | ETH_MIITXCLK #1<br>US3_TX #4<br>QSPI0_SCLK #2                                                     | CMU_CLK2 #3                                        |

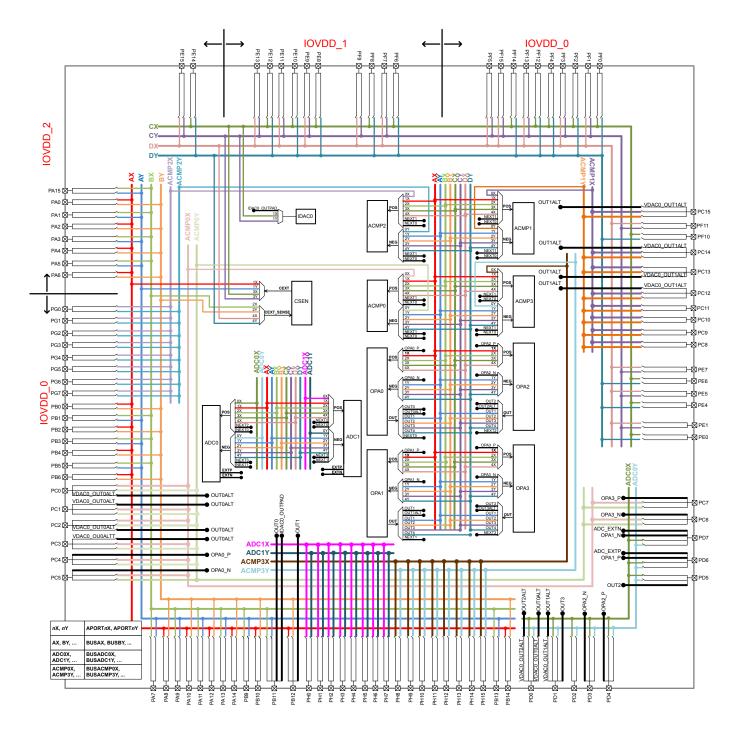

### 5.22 Analog Port (APORT) Client Maps

The Analog Port (APORT) is an infrastructure used to connect chip pins with on-chip analog clients such as analog comparators, ADCs, DACs, etc. The APORT consists of a set of shared buses, switches, and control logic needed to configurably implement the signal routing. Figure 5.20 APORT Connection Diagram on page 211 shows the APORT routing for this device family (note that available features may vary by part number). A complete description of APORT functionality can be found in the Reference Manual.

Figure 5.20. APORT Connection Diagram

Client maps for each analog circuit using the APORT are shown in the following tables. The maps are organized by bus, and show the peripheral's port connection, the shared bus, and the connection from specific bus channel numbers to GPIO pins.

In general, enumerations for the pin selection field in an analog peripheral's register can be determined by finding the desired pin connection in the table and then combining the value in the Port column (APORT\_\_), and the channel identifier (CH\_\_). For example, if pin PF7 is available on port APORT2X as CH23, the register field enumeration to connect to PF7 would be APORT2XCH23. The shared bus used by this connection is indicated in the Bus column.

Table 5.31. VDAC0 / OPA Bus and Pin Mapping

| Port    | Bus   | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СНЭ | СН8 | CH7 | СН6 | CH5 | CH4 | СНЗ | CH2 | CH1 | СНО |

|---------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| ОР      | A0_   | N    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y | BUSAY | PB15 |      | PB13 |      | PB11 |      | PB9  |      |      |      | PB5  |      | PB3  |      | PB1  |      | PA15 |      | PA13 |      | PA11 |      | PA9 |     | PA7 |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y | BUSBY |      | PB14 |      | PB12 |      | PB10 |      |      |      | PB6  |      | PB4  |      | PB2  |      | PB0  |      | PA14 |      | PA12 |      | PA10 |     | PA8 |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT3Y | BUSCY | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     | PE1 |     |

| APORT4Y | BUSDY |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     | PE0 |

| OF      | A0_   | Р    |      |      |      |      |      |      |      |      | ı    |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1X | BUSAX |      | PB14 |      | PB12 |      | PB10 |      |      |      | PB6  |      | PB4  |      | PB2  |      | PB0  |      | PA14 |      | PA12 |      | PA10 |     | PA8 |     | PA6 |     | PA4 |     | PA2 |     | PA0 |

| APORT2X | BUSBX | PB15 |      | PB13 |      | PB11 |      | PB9  |      |      |      | PB5  |      | PB3  |      | PB1  |      | PA15 |      | PA13 |      | PA11 |      | PA9 |     | PA7 |     | PA5 |     | PA3 |     | PA1 |     |

| APORT3X | BUSCX |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     | PE0 |

| APORT4X | BUSDX | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     | PE1 |     |