Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                                        |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 53                                                                                                            |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                                                          |

| Supplier Device Package    | 64-QFN (9x9)                                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b420f2048gm64-b                                    |

|                            |                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.11 Memory Map

The EFM32GG11 memory map is shown in the figures below. RAM and flash sizes are for the largest memory configuration.

|                                            | 8x£6166668               | ]   |                       |                          |

|--------------------------------------------|--------------------------|-----|-----------------------|--------------------------|

| CM4 Peripherals                            | 8xe88fffff               |     |                       |                          |

|                                            | 8×99999999               |     |                       |                          |

| QSPI0                                      | 8xcfffffff               |     |                       |                          |

|                                            | 8%888888888              |     |                       |                          |

| EBI Region 3                               | 8x8t6666666              |     |                       |                          |

| EBI Region 2                               | 8x886666666              |     |                       |                          |

| EBI Region 1                               | 8x84666666               | \   |                       | 0xe0100000               |

| EBI Region 0                               | 8x83ffffff               | \   | CM4 ROM Table         | 0xe00ff000               |

| Ebinegionio                                | 8×7fffffff               |     |                       | 0xe0042000               |

| Bit Set                                    | 0x460f0400<br>0x460f03ff | ,   | ETM                   | 0xe0041000               |

| (Peripherals / CRYPTO0)                    | 0×46000000               |     | TPIU                  | 0xe0040000               |

|                                            | 8×45555555               |     | Custom Control Concer | 0xe000f000               |

| Bit Clear                                  | 0x440f03ff               |     | System Control Space  | 0xe000e000               |

| (Peripherals / CRYPTO0)                    | 0×44000000               | \   | FPB                   | 0xe0003000               |

|                                            | 8x43£46666               | \ \ | DWT                   | 0xe0002000               |

| Bit-Band<br>(Peripherals / CRYPTO0 / SDIO) | 0x43e3ffff<br>0x42000000 | Λ.  | ITM                   | 0xe0001000               |

| (relipitedas) extri roci (spio)            | 8×41ffffff               | 1   | 119                   | 0xe0000000               |

| USB                                        | 8×40135555               |     |                       |                          |

| 038                                        | 0×40100000<br>8×488f2fff |     |                       | 0x10080000               |

| SDIQ                                       |                          |     | RAM2<br>(code space)  | 0,10000000               |

| SDIO                                       | 8×48811666               |     | RAM1                  | 0×10040000               |

|                                            | 8×48818455               |     | (code space)          | 010020000                |

| CRYPTO0                                    | 8×488f8355               | /   | RAMO                  | 0x10020000               |

| Peripherals 1                              | 8×48845555               | /   | (code space)          | 0×10000000               |

| Peripherals 0                              | 8×48835555               | /   | Chip config           | 0x0fe09000               |

|                                            | 8x3fffffff               | /   |                       | 0x0fe08000<br>0x0fe05000 |

| SRAM (bit-band)                            | 8×33222222               |     | Lock bits             | 0x0fe04000               |

|                                            | 8×21ffffff               |     | User Data             | 0x0fe01000               |

| RAM2 (data space)                          | 8×28846666               |     |                       | 0x0fe00000               |

| RAM1 (data space)                          | 8×28835555               |     | QSPI0                 | 0x0c000000<br>0x04000000 |

| RAM0 (data space)                          | 8×2881ffff               | 1   |                       | 0x00200000               |

|                                            | 0x1fffffff               | 1   |                       |                          |

| Code                                       |                          |     | Flash (2048 KB)       |                          |

|                                            | 0×00000000               |     |                       | 0x00000000               |

Figure 3.2. EFM32GG11 Memory Map — Core Peripherals and Code Space

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbol             | Test Condition                                                                | Min           | Тур              | Мах             | Unit      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------|---------------|------------------|-----------------|-----------|

| Note:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                                                               |               |                  |                 |           |

| 1. The minimum voltage req<br>other loads can be calcula                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | node is calculated using $R_{BYP}$ from the $h^+I_{LOAD} * R_{BYP_max}$ .     | e DCDC spec   | cification table | e. Requiremer   | nts for   |

| 2. VREGVDD must be tied t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | o AVDD. Both VR    | EGVDD and AVDD minimum voltage                                                | es must be sa | tisfied for the  | part to operat  | te.       |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    | aracteristic specs of the capacitor use<br>s temperature and DC bias.         | ed on DECOL   | JPLE to ensu     | re its capacita | ince val- |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dependent on the   | nsitions occur at a rate of 10 mV / use<br>e value of the DECOUPLE output cap |               |                  |                 |           |

| 5. When the CSEN peripher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | al is used with ch | opping enabled (CSEN_CTRL_CHO                                                 | PEN = ENABI   | LE), IOVDD m     | nust be equal   | to AVDD.  |

| <ol> <li>5. When the CSEN peripheral is used with chopping enabled (CSEN_CTRL_CHOPEN = ENABLE), IOVDD must be equal to AVDD.</li> <li>6. The maximum limit on T<sub>A</sub> may be lower due to device self-heating, which depends on the power dissipation of the specific application. T<sub>A</sub> (max) = T<sub>J</sub> (max) - (THETA<sub>JA</sub> x PowerDissipation). Refer to the Absolute Maximum Ratings table and the Thermal Characteristics table for T<sub>J</sub> and THETA<sub>JA</sub>.</li> </ol> |                    |                                                                               |               |                  |                 |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    |                                                                               |               |                  |                 |           |

# 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                          | Test Condition                    | Min | Тур  | Max | Unit |

|----------------------------|---------------------------------|-----------------------------------|-----|------|-----|------|

| Thermal resistance, QFN64  | THETAJA_QFN64                   | 4-Layer PCB, Air velocity = 0 m/s | _   | 17.8 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 15.4 |     | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 13.8 |     | °C/W |

| Thermal resistance, TQFP64 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 33.9 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP64</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 32.1 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 30.1 | _   | °C/W |

| Thermal resistance,        | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _   | °C/W |

| TQFP100 Package            | TA <sub>JA_TQFP100</sub>        | 4-Layer PCB, Air velocity = 1 m/s | _   | 37.7 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 35.5 | _   | °C/W |

| Thermal resistance, BGA112 | THE-<br>TA <sub>JA_BGA112</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 42.0 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 37.0 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 35.3 | _   | °C/W |

| Thermal resistance, BGA120 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 47.9 | _   | °C/W |

| Package                    | TA <sub>JA_BGA120</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 41.8 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 39.6 | _   | °C/W |

| Thermal resistance, BGA152 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 35.7 | _   | °C/W |

| Package                    | TA <sub>JA_BGA152</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 31.0 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 29.5 | _   | °C/W |

| Thermal resistance, BGA192 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 47.9 | _   | °C/W |

| Package                    | TA <sub>JA_BGA192</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 41.8 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 39.6 | _   | °C/W |

# Table 4.3. Thermal Characteristics

## 4.1.4 DC-DC Converter

Test conditions: L\_DCDC=4.7 µH (Murata LQH3NPN4R7MM0L), C\_DCDC=4.7 µF (Samsung CL10B475KQ8NQNC), V\_DCDC\_I=3.3 V, V\_DCDC\_O=1.8 V, I\_DCDC\_LOAD=50 mA, Heavy Drive configuration, F\_DCDC\_LN=7 MHz, unless otherwise indicated.

### Table 4.4. DC-DC Converter

| Parameter                                           | Symbol              | Test Condition                                                                                                                            | Min | Тур | Max                         | Unit |

|-----------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                 | V <sub>DCDC_I</sub> | Bypass mode, I <sub>DCDC_LOAD</sub> = 50<br>mA                                                                                            | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V out-<br>put, $I_{DCDC\_LOAD} = 100$ mA, or<br>Low power (LP) mode, 1.8 V out-<br>put, $I_{DCDC\_LOAD} = 10$ mA | 2.4 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                     |                     | Low noise (LN) mode, 1.8 V out-<br>put, I <sub>DCDC_LOAD</sub> = 200 mA                                                                   | 2.6 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Output voltage programma-<br>ble range <sup>1</sup> | V <sub>DCDC_O</sub> |                                                                                                                                           | 1.8 | _   | V <sub>VREGVDD</sub>        | V    |

| Regulation DC accuracy                              | ACC <sub>DC</sub>   | Low Noise (LN) mode, 1.8 V tar-<br>get output                                                                                             | TBD | _   | TBD                         | V    |

| Regulation window <sup>4</sup>                      | WIN <sub>REG</sub>  | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 0, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 75 µA                          | TBD | _   | TBD                         | V    |

|                                                     |                     | Low Power (LP) mode,<br>LPCMPBIASEMxx <sup>3</sup> = 3, 1.8 V tar-<br>get output, I <sub>DCDC_LOAD</sub> ≤ 10 mA                          | TBD | _   | TBD                         | V    |

| Steady-state output ripple                          | V <sub>R</sub>      |                                                                                                                                           | _   | 3   | _                           | mVpp |

| Output voltage under/over-<br>shoot                 | Vov                 | CCM Mode (LNFORCECCM <sup>3</sup> = 1), Load changes between 0 mA and 100 mA                                                              | _   | 25  | TBD                         | mV   |

|                                                     |                     | DCM Mode (LNFORCECCM <sup>3</sup> = 0), Load changes between 0 mA and 10 mA                                                               | _   | 45  | TBD                         | mV   |

|                                                     |                     | Overshoot during LP to LN<br>CCM/DCM mode transitions com-<br>pared to DC level in LN mode                                                | _   | 200 | -                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>CCM (LNFORCECCM <sup>3</sup> = 1) mode<br>transitions compared to DC level<br>in LN mode                | _   | 40  | _                           | mV   |

|                                                     |                     | Undershoot during BYP/LP to LN<br>DCM (LNFORCECCM <sup>3</sup> = 0) mode<br>transitions compared to DC level<br>in LN mode                | _   | 100 | _                           | mV   |

| DC line regulation                                  | V <sub>REG</sub>    | Input changes between V <sub>VREGVDD_MAX</sub> and 2.4 V                                                                                  | _   | 0.1 | -                           | %    |

| DC load regulation                                  | I <sub>REG</sub>    | Load changes between 0 mA and 100 mA in CCM mode                                                                                          | _   | 0.1 | -                           | %    |

# 4.1.10.2 High-Frequency Crystal Oscillator (HFXO)

| Parameter                                        | Symbol              | Test Condition                                          | Min | Тур   | Max  | Unit |

|--------------------------------------------------|---------------------|---------------------------------------------------------|-----|-------|------|------|

| Crystal frequency                                | f <sub>HFXO</sub>   | No clock doubling                                       | 4   |       | 50   | MHz  |

|                                                  |                     | Clock doubler enabled                                   | TBD |       | TBD  | MHz  |

| Supported crystal equivalent                     | ESR <sub>HFXO</sub> | 50 MHz crystal                                          |     |       | 50   | Ω    |

| series resistance (ESR)                          |                     | 24 MHz crystal                                          | _   |       | 150  | Ω    |

|                                                  |                     | 4 MHz crystal                                           | —   |       | 180  | Ω    |

| Nominal on-chip tuning cap<br>range <sup>1</sup> | C <sub>HFXO_T</sub> | On each of HFXTAL_N and HFXTAL_P pins                   | 8.7 |       | 51.7 | pF   |

| On-chip tuning capacitance step                  | SS <sub>HFXO</sub>  |                                                         | _   | 0.084 | _    | pF   |

| Startup time                                     | t <sub>HFXO</sub>   | 50 MHz crystal, ESR = 50 Ohm,<br>$C_L = 8 pF$           |     | 350   | _    | μs   |

|                                                  |                     | 24 MHz crystal, ESR = 150 Ohm,<br>C <sub>L</sub> = 6 pF |     | 700   | _    | μs   |

|                                                  |                     | 4 MHz crystal, ESR = 180 Ohm,<br>$C_L$ = 18 pF          |     | 3     |      | ms   |

| Current consumption after                        | I <sub>HFXO</sub>   | 50 MHz crystal                                          | —   | 880   | _    | μA   |

| startup                                          |                     | 24 MHz crystal                                          |     | 420   | _    | μA   |

|                                                  |                     | 4 MHz crystal                                           | —   | 80    | _    | μA   |

## Table 4.13. High-Frequency Crystal Oscillator (HFXO)

# Note:

1. The effective load capacitance seen by the crystal will be C<sub>HFXO\_T</sub> /2. This is because each XTAL pin has a tuning cap and the two caps will be seen in series by the crystal.

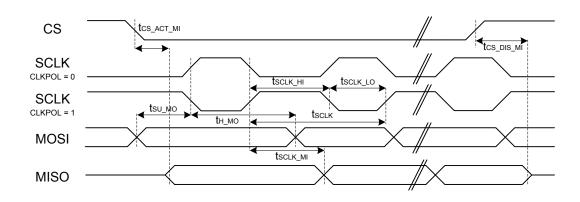

| Parameter                         | Symbol                 | Test Condition | Min                                 | Тур | Мах                                 | Unit |

|-----------------------------------|------------------------|----------------|-------------------------------------|-----|-------------------------------------|------|

| SCLK period <sup>1 3 2</sup>      | t <sub>SCLK</sub>      |                | 6 *<br><sup>t</sup> HFPERCLK        | _   | —                                   | ns   |

| SCLK high time <sup>1 3 2</sup>   | t <sub>SCLK_HI</sub>   |                | 2.5 *<br><sup>t</sup> HFPERCLK      | —   | _                                   | ns   |

| SCLK low time <sup>1 3 2</sup>    | t <sub>SCLK_LO</sub>   |                | 2.5 *<br><sup>t</sup> HFPERCLK      | —   | _                                   | ns   |

| CS active to MISO <sup>1 3</sup>  | t <sub>cs_аст_мі</sub> |                | 24                                  | —   | 69                                  | ns   |

| CS disable to MISO <sup>1 3</sup> | t <sub>CS_DIS_MI</sub> |                | 19                                  | _   | 175                                 | ns   |

| MOSI setup time <sup>1 3</sup>    | t <sub>SU_MO</sub>     |                | 7                                   | —   | —                                   | ns   |

| MOSI hold time <sup>1 3 2</sup>   | t <sub>H_MO</sub>      |                | 6                                   | _   | —                                   | ns   |

| SCLK to MISO <sup>1 3 2</sup>     | t <sub>SCLK_MI</sub>   |                | 16 + 1.5 *<br><sup>t</sup> HFPERCLK | _   | 43 + 2.5 *<br>t <sub>HFPERCLK</sub> | ns   |

# Table 4.35. SPI Slave Timing

## Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2.  $t_{\text{HFPERCLK}}$  is one period of the selected HFPERCLK.

3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ ).

Figure 4.2. SPI Slave Timing Diagram

#### EBI Address Latch Enable Output Timing

Timing applies to multiplexed addressing modes D8A24ALE and D16A16ALE for both polarities. All numbers are based on route locations 0,1,2 only (with all EBI alternate functions using the same location at the same time). Timing is specified at 10% and 90% of IOVDD, 25 pF external loading, and slew rate for all GPIO set to 6.

| Parameter                                                                             | Symbol                | Test Condition | Min                                                                    | Тур | Max | Unit |

|---------------------------------------------------------------------------------------|-----------------------|----------------|------------------------------------------------------------------------|-----|-----|------|

| Output hold time, from trail-<br>ing EBI_ALE edge to<br>EBI_AD invalid <sup>1 2</sup> | edge to               |                | -22 +<br>(ADDR-<br>HOLD *<br><sup>t</sup> HFCOR-<br>ECLK)              | _   | _   | ns   |

|                                                                                       |                       | IOVDD ≥ 3.0 V  | -11 +<br>(ADDR-<br>HOLD *<br><sup>t</sup> HFCOR-<br>ECLK)              | _   | _   | ns   |

| Output setup time, from                                                               | t <sub>OSU_ALEn</sub> | IOVDD ≥ 1.62 V | -12                                                                    | —   | —   | ns   |

| EBI_AD valid to leading<br>EBI_ALE edge                                               |                       | IOVDD ≥ 3.0 V  | -9                                                                     | —   | _   | ns   |

| EBI_ALEn pulse width <sup>1</sup>                                                     | twidth_Alen           | IOVDD ≥ 1.62 V | -4 +<br>((ADDR-<br>SETUP +<br>1) *<br>t{ <sub>}HFCOR-</sub><br>ECLK{}) | _   | _   | ns   |

|                                                                                       |                       | IOVDD ≥ 3.0 V  | -3 +<br>((ADDR-<br>SETUP +<br>1) *<br>t{ <sub>}HFCOR-</sub><br>ECLK{}) | _   | _   | ns   |

### Table 4.37. EBI Address Latch Enable Output Timing

#### Note:

1. The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFALE=0. The trailing edge of EBI\_ALEn can be moved to the left by setting HALFALE=1. This decreases the length of t<sub>WIDTH\_ALEn</sub> and increases the length of t<sub>OSU\_ALEn</sub> by t<sub>HFCORECLK</sub> - 1/2 \* t<sub>HFCLKNODIV</sub>.

2. The figure shows a write operation. For a multiplexed read operation the address hold time is controlled via the RDSETUP state instead of via the ADDRHOLD state.

## SDIO DDR Mode Timing

Timing is specified for route location 0 at 1.8 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 6, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 30 pF on all pins.

| Parameter                                     | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|-----------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer          | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    |      | 20  | MHz  |

|                                               |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 22.6 | —    | _   | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                               | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 22.6 | _    | _   | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                               | t <sub>R</sub>      |                                   | 1.69 | 6.52 | —   | ns   |

| Clock fall time                               | t <sub>F</sub>      |                                   | 1.42 | 4.96 | _   | ns   |

| Input setup time, CMD valid to SD_CLK         | t <sub>ISU</sub>    |                                   | 6    |      | _   | ns   |

| Input hold time, SD_CLK to CMD change         | t <sub>IH</sub>     |                                   | 1.8  |      | _   | ns   |

| Output delay time, SD_CLK to CMD valid        | t <sub>ODLY</sub>   |                                   | 0    |      | 16  | ns   |

| Output hold time, SD_CLK to CMD change        | t <sub>OH</sub>     |                                   | 0.8  | _    | _   | ns   |

| Input setup time, DAT[0:3]<br>valid to SD_CLK | t <sub>ISU2X</sub>  |                                   | 6    | _    | _   | ns   |

| Input hold time, SD_CLK to DAT[0:3] change    | t <sub>IH2X</sub>   |                                   | 1.5  | _    | _   | ns   |

| Output delay time, SD_CLK to DAT[0:3] valid   | t <sub>ODLY2X</sub> |                                   | 0    | _    | 16  | ns   |

| Output hold time, SD_CLK to DAT[0:3] change   | t <sub>OH2X</sub>   |                                   | 0.8  |      | —   | ns   |

## Table 4.49. SDIO DS Mode Timing (Location 0)

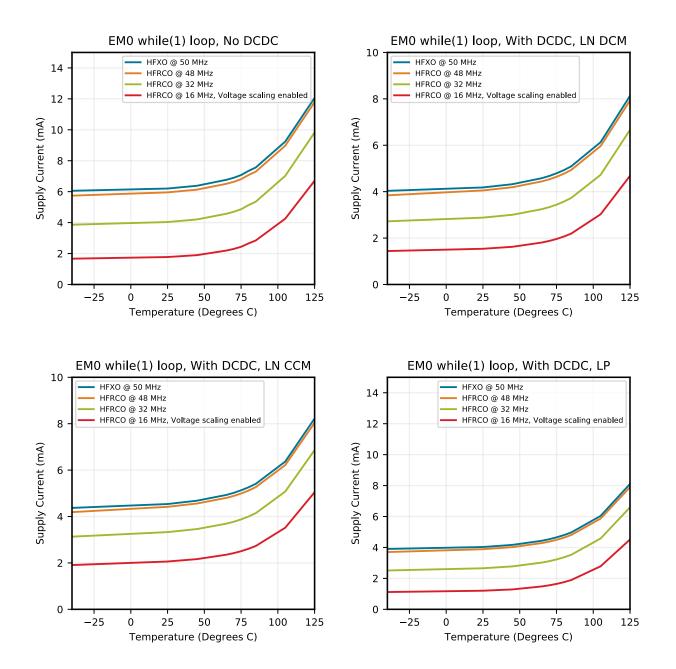

Figure 4.24. EM0 Active Mode Typical Supply Current vs. Temperature

| Pin Name                                                                                                                                                                                           | Pin(s)    | Description                | Pin Name | Pin(s) | Description |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------|----------|--------|-------------|--|--|--|--|

| Note:                                                                                                                                                                                              | Note:     |                            |          |        |             |  |  |  |  |

| 1. GPIO with                                                                                                                                                                                       | 5V tolera | nce are indicated by (5V). |          |        |             |  |  |  |  |

| 2. The pins PD13, PD14, and PD15 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hard-<br>ware compatibility, do not use these pins with 5V domains. |           |                            |          |        |             |  |  |  |  |

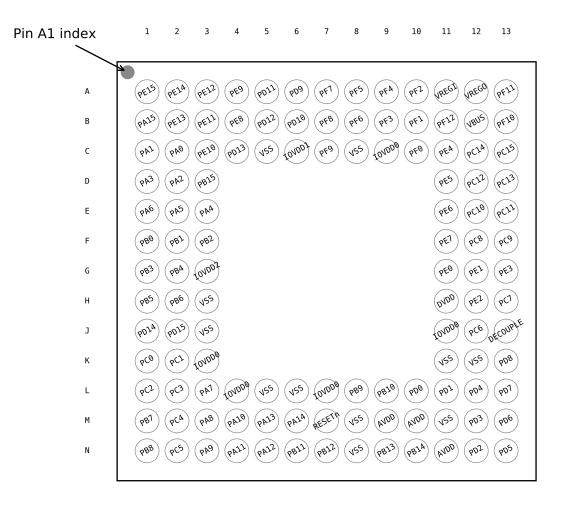

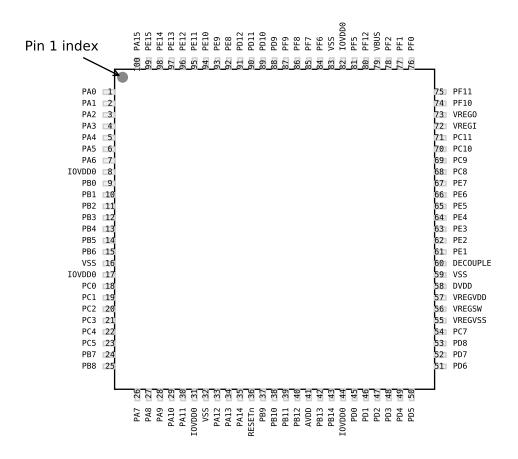

#### Figure 5.5. EFM32GG11B4xx in BGA120 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s) | Description             | Pin Name | Pin(s) | Description                                                                                      |

|----------|--------|-------------------------|----------|--------|--------------------------------------------------------------------------------------------------|

| PE15     | A1     | GPIO                    | PE14     | A2     | GPIO                                                                                             |

| PE12     | A3     | GPIO                    | PE9      | A4     | GPIO                                                                                             |

| PD11     | A5     | GPIO                    | PD9      | A6     | GPIO                                                                                             |

| PF7      | A7     | GPIO                    | PF5      | A8     | GPIO                                                                                             |

| PF4      | A9     | GPIO                    | PF2      | A10    | GPIO                                                                                             |

| VREGI    | A11    | Input to 5 V regulator. | VREGO    | A12    | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs |

#### Figure 5.8. EFM32GG11B8xx in QFP100 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Table 5.8. | EFM32GG11B8xx in QFP100 Device Pinout |

|------------|---------------------------------------|

|------------|---------------------------------------|

| Pin Name | Pin(s) | Description | Pin Name | Pin(s)                    | Description                |

|----------|--------|-------------|----------|---------------------------|----------------------------|

| PA0      | 1      | GPIO        | PA1      | 2                         | GPIO                       |

| PA2      | 3      | GPIO        | PA3      | 4                         | GPIO                       |

| PA4      | 5      | GPIO        | PA5      | 6                         | GPIO                       |

| PA6      | 7      | GPIO        | IOVDD0   | 8<br>17<br>31<br>44<br>82 | Digital IO power supply 0. |

| PB0      | 9      | GPIO        | PB1      | 10                        | GPIO                       |

| Pin Name | Pin(s) | Description                                                                                                                                                                                                 | Pin Name | Pin(s)               | Description                                                                                      |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|--------------------------------------------------------------------------------------------------|

| PB2      | 11     | GPIO                                                                                                                                                                                                        | PB3      | 12                   | GPIO                                                                                             |

| PB4      | 13     | GPIO                                                                                                                                                                                                        | PB5      | 14                   | GPIO                                                                                             |

| PB6      | 15     | GPIO                                                                                                                                                                                                        | VSS      | 16<br>32<br>59<br>83 | Ground                                                                                           |

| PC0      | 18     | GPIO (5V)                                                                                                                                                                                                   | PC1      | 19                   | GPIO (5V)                                                                                        |

| PC2      | 20     | GPIO (5V)                                                                                                                                                                                                   | PC3      | 21                   | GPIO (5V)                                                                                        |

| PC4      | 22     | GPIO                                                                                                                                                                                                        | PC5      | 23                   | GPIO                                                                                             |

| PB7      | 24     | GPIO                                                                                                                                                                                                        | PB8      | 25                   | GPIO                                                                                             |

| PA7      | 26     | GPIO                                                                                                                                                                                                        | PA8      | 27                   | GPIO                                                                                             |

| PA9      | 28     | GPIO                                                                                                                                                                                                        | PA10     | 29                   | GPIO                                                                                             |

| PA11     | 30     | GPIO                                                                                                                                                                                                        | PA12     | 33                   | GPIO (5V)                                                                                        |

| PA13     | 34     | GPIO (5V)                                                                                                                                                                                                   | PA14     | 35                   | GPIO                                                                                             |

| RESETn   | 36     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB9      | 37                   | GPIO (5V)                                                                                        |

| PB10     | 38     | GPIO (5V)                                                                                                                                                                                                   | PB11     | 39                   | GPIO                                                                                             |

| PB12     | 40     | GPIO                                                                                                                                                                                                        | AVDD     | 41                   | Analog power supply.                                                                             |

| PB13     | 42     | GPIO                                                                                                                                                                                                        | PB14     | 43                   | GPIO                                                                                             |

| PD0      | 45     | GPIO (5V)                                                                                                                                                                                                   | PD1      | 46                   | GPIO                                                                                             |

| PD2      | 47     | GPIO (5V)                                                                                                                                                                                                   | PD3      | 48                   | GPIO                                                                                             |

| PD4      | 49     | GPIO                                                                                                                                                                                                        | PD5      | 50                   | GPIO                                                                                             |

| PD6      | 51     | GPIO                                                                                                                                                                                                        | PD7      | 52                   | GPIO                                                                                             |

| PD8      | 53     | GPIO                                                                                                                                                                                                        | PC7      | 54                   | GPIO                                                                                             |

| VREGVSS  | 55     | Voltage regulator VSS                                                                                                                                                                                       | VREGSW   | 56                   | DCDC regulator switching node                                                                    |

| VREGVDD  | 57     | Voltage regulator VDD input                                                                                                                                                                                 | DVDD     | 58                   | Digital power supply.                                                                            |

| DECOUPLE | 60     | Decouple output for on-chip voltage<br>regulator. An external decoupling ca-<br>pacitor is required at this pin.                                                                                            | PE1      | 61                   | GPIO (5V)                                                                                        |

| PE2      | 62     | GPIO                                                                                                                                                                                                        | PE3      | 63                   | GPIO                                                                                             |

| PE4      | 64     | GPIO                                                                                                                                                                                                        | PE5      | 65                   | GPIO                                                                                             |

| PE6      | 66     | GPIO                                                                                                                                                                                                        | PE7      | 67                   | GPIO                                                                                             |

| PC8      | 68     | GPIO (5V)                                                                                                                                                                                                   | PC9      | 69                   | GPIO (5V)                                                                                        |

| PC10     | 70     | GPIO (5V)                                                                                                                                                                                                   | PC11     | 71                   | GPIO (5V)                                                                                        |

| VREGI    | 72     | Input to 5 V regulator.                                                                                                                                                                                     | VREGO    | 73                   | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs |

| PF10     | 74     | GPIO (5V)                                                                                                                                                                                                   | PF11     | 75                   | GPIO (5V)                                                                                        |

| PF0      | 76     | GPIO (5V)                                                                                                                                                                                                   | PF1      | 77                   | GPIO (5V)                                                                                        |

| GPIO Name | Pin Alternate Functionality / Description |                             |                                                            |                                                                                                                             |                                                        |  |

|-----------|-------------------------------------------|-----------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

|           | Analog                                    | EBI                         | Timers                                                     | Communication                                                                                                               | Other                                                  |  |

| PF14      | BUSDY BUSCX                               |                             | TIM1_CC1 #6<br>TIM4_CC1 #1<br>TIM5_CC2 #7<br>WTIM3_CC1 #7  | 12C2_SCL #4                                                                                                                 |                                                        |  |

| PF11      | BUSCY BUSDX                               | EBI_NANDWEn #5              | TIM5_CC2 #6<br>WTIM3_CC2 #3<br>PCNT2_S1IN #3               | US5_CTS #2 U1_RX<br>#1 I2C2_SCL #2<br>USB_DP                                                                                |                                                        |  |

| PF10      | BUSDY BUSCX                               | EBI_ARDY #5                 | TIM5_CC1 #6<br>WTIM3_CC1 #3<br>PCNT2_S0IN #3               | US5_RTS #2 U1_TX<br>#1 I2C2_SDA #2<br>USB_DM                                                                                |                                                        |  |

| PF0       | BUSDY BUSCX                               | EBI_A24 #1                  | TIM0_CC0 #4<br>WTIM0_CC1 #4 LE-<br>TIM0_OUT0 #2            | US2_TX #5<br>CAN0_RX #1<br>US1_CLK #2<br>LEU0_TX #3<br>I2C0_SDA #5                                                          | PRS_CH15 #2<br>ACMP3_O #0<br>DBG_SWCLKTCK<br>BOOT_TX   |  |

| PA0       | BUSBY BUSAX<br>LCD_SEG13                  | EBI_AD09 #0<br>EBI_CSTFT #3 | TIM0_CC0 #0<br>TIM0_CC1 #7<br>TIM3_CC0 #4<br>PCNT0_S0IN #4 | ETH_RMIITXEN #0<br>ETH_MIITXCLK #0<br>SDIO_DAT0 #1<br>US1_RX #5 US3_TX<br>#0 QSPI0_CS0 #1<br>LEU0_RX #4<br>I2C0_SDA #0      | CMU_CLK2 #0<br>PRS_CH0 #0<br>PRS_CH3 #3<br>GPIO_EM4WU0 |  |

| PD11      | LCD_SEG30                                 | EBI_CS2 #0<br>EBI_HSNC #1   | TIM4_CC0 #6<br>WTIM3_CC2 #0                                | ETH_RMIICRSDV #1<br>SDIO_DAT5 #0<br>QSPI0_DQ2 #0<br>ETH_MIIRXD3 #2<br>US4_CLK #1                                            |                                                        |  |

| PD10      | LCD_SEG29                                 | EBI_CS1 #0<br>EBI_VSNC #1   | TIM4_CC2 #5<br>WTIM3_CC1 #0                                | ETH_RMIIREFCLK<br>#1 SDIO_DAT6 #0<br>QSPI0_DQ1 #0<br>ETH_MIIRXD2 #2<br>US4_RX #1                                            | CMU_CLK2 #5<br>CMU_CLKI0 #5                            |  |

| PD9       | LCD_SEG28                                 | EBI_CS0 #0<br>EBI_DTEN #1   | TIM4_CC1 #5<br>WTIM3_CC0 #0                                | ETH_RMIIRXD0 #1<br>SDIO_DAT7 #0<br>QSPI0_DQ0 #0<br>ETH_MIIRXD1 #2<br>US4_TX #1                                              |                                                        |  |

| PF9       | BUSCY BUSDX<br>LCD_SEG27                  | EBI_REn #4<br>EBI_BL1 #1    | TIM4_CC0 #5                                                | ETH_RMIIRXD1 #1<br>US2_CS #4<br>QSPI0_DQS #0<br>ETH_MIIRXD0 #2<br>ETH_TSUTMRTOG<br>#3 SDIO_WP #0<br>U0_RTS #0 U1_CTS<br>#1  | ETM_TD0 #1                                             |  |

| PF8       | BUSDY BUSCX<br>LCD_SEG26                  | EBI_WEn #4<br>EBI_BL0 #1    | TIM0_CC2 #1<br>TIM4_CC2 #4                                 | ETH_RMIITXEN #1<br>US2_CLK #4<br>QSPI0_CS1 #0<br>ETH_MIIRXDV #2<br>ETH_TSUEXTCLK<br>#3 SDIO_CD #0<br>U0_CTS #0 U1_RTS<br>#1 | ETM_TCLK #1<br>GPIO_EM4WU8                             |  |

| Alternate LOCATION |                                       | ATION                                    |                                                                                                                                                                       |  |  |

|--------------------|---------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Functionality      | 0 - 3                                 | 4 - 7                                    | Description                                                                                                                                                           |  |  |

| BU_STAT            | 0: PE3                                |                                          | Backup Power Domain status, whether or not the system is in backup mode.                                                                                              |  |  |

| BU_VIN             | 0: PD8                                |                                          | Battery input for Backup Power Domain.                                                                                                                                |  |  |

| BU_VOUT            | 0: PE2                                |                                          | Power output for Backup Power Domain.                                                                                                                                 |  |  |

| CAN0_RX            | 0: PC0<br>1: PF0<br>2: PD0<br>3: PB9  | 4: PG8<br>5: PD14<br>6: PE0<br>7: PI12   | CAN0 RX.                                                                                                                                                              |  |  |

| CAN0_TX            | 0: PC1<br>1: PF2<br>2: PD1<br>3: PB10 | 4: PG9<br>5: PD15<br>6: PE1<br>7: PI13   | CAN0 TX.                                                                                                                                                              |  |  |

| CAN1_RX            | 0: PC2<br>1: PF1<br>2: PD3<br>3: PC9  | 4: PC12<br>5: PA12<br>6: PG10<br>7: PI14 | CAN1 RX.                                                                                                                                                              |  |  |

| CAN1_TX            | 0: PC3<br>1: PF3<br>2: PD4<br>3: PC10 | 4: PC11<br>5: PA13<br>6: PG11<br>7: PI15 | CAN1 TX.                                                                                                                                                              |  |  |

| CMU_CLK0           | 0: PA2<br>1: PC12<br>2: PD7<br>3: PG2 | 4: PF2<br>5: PA12                        | Clock Management Unit, clock output number 0.                                                                                                                         |  |  |

| CMU_CLK1           | 0: PA1<br>1: PD8<br>2: PE12<br>3: PG1 | 4: PF3<br>5: PB11                        | Clock Management Unit, clock output number 1.                                                                                                                         |  |  |

| CMU_CLK2           | 0: PA0<br>1: PA3<br>2: PD6<br>3: PG0  | 4: PA3<br>5: PD10                        | Clock Management Unit, clock output number 2.                                                                                                                         |  |  |

| CMU_CLKI0          | 0: PD4<br>1: PA3<br>2: PB8<br>3: PB13 | 4: PE1<br>5: PD10<br>6: PE12<br>7: PB11  | Clock Management Unit, clock input number 0.                                                                                                                          |  |  |

| DBG_SWCLKTCK       | 0: PF0                                |                                          | Debug-interface Serial Wire clock input and JTAG Test Clock.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull down.             |  |  |

| DBG_SWDIOTMS       | 0: PF1                                |                                          | Debug-interface Serial Wire data input / output and JTAG Test Mode Select.<br>Note that this function is enabled to the pin out of reset, and has a built-in pull up. |  |  |

| Alternate     | LOCA                                   | TION  |                                                     |  |

|---------------|----------------------------------------|-------|-----------------------------------------------------|--|

| Functionality | 0 - 3                                  | 4 - 7 | Description                                         |  |

| EBI_A10       | 0: PE3<br>1: PD6<br>2: PC10<br>3: PB10 |       | External Bus Interface (EBI) address output pin 10. |  |

| EBI_A11       | 0: PE4<br>1: PD7<br>2: PI6<br>3: PB11  |       | External Bus Interface (EBI) address output pin 11. |  |

| EBI_A12       | 0: PE5<br>1: PD8<br>2: PI7<br>3: PB12  |       | External Bus Interface (EBI) address output pin 12. |  |

| EBI_A13       | 0: PE6<br>1: PC7<br>2: PI8<br>3: PD0   |       | External Bus Interface (EBI) address output pin 13. |  |

| EBI_A14       | 0: PE7<br>1: PE2<br>2: PI9<br>3: PD1   |       | External Bus Interface (EBI) address output pin 14. |  |

| EBI_A15       | 0: PC8<br>1: PE3<br>2: PI10<br>3: PD2  |       | External Bus Interface (EBI) address output pin 15. |  |

| EBI_A16       | 0: PB0<br>1: PE4<br>2: PH4<br>3: PD3   |       | External Bus Interface (EBI) address output pin 16. |  |

| EBI_A17       | 0: PB1<br>1: PE5<br>2: PH5<br>3: PD4   |       | External Bus Interface (EBI) address output pin 17. |  |

| EBI_A18       | 0: PB2<br>1: PE6<br>2: PH6<br>3: PD5   |       | External Bus Interface (EBI) address output pin 18. |  |

| EBI_A19       | 0: PB3<br>1: PE7<br>2: PH7<br>3: PD6   |       | External Bus Interface (EBI) address output pin 19. |  |

| EBI_A20       | 0: PB4<br>1: PC8<br>2: PH8<br>3: PD7   |       | External Bus Interface (EBI) address output pin 20. |  |

| EBI_A21       | 0: PB5<br>1: PC9<br>2: PH9<br>3: PC7   |       | External Bus Interface (EBI) address output pin 21. |  |

| EBI_A22       | 0: PB6<br>1: PC10<br>2: PH10<br>3: PE4 |       | External Bus Interface (EBI) address output pin 22. |  |

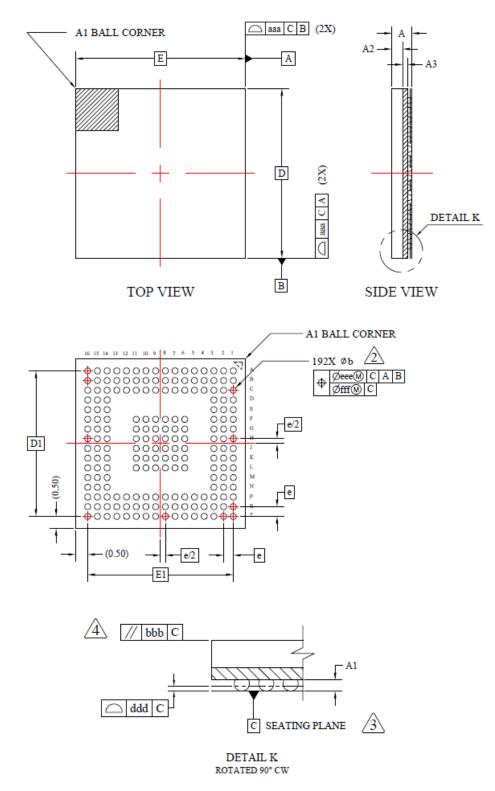

# 6. BGA192 Package Specifications

## 6.1 BGA192 Package Dimensions

Figure 6.1. BGA192 Package Drawing

| Dimension | Min            | Тур      | Мах  |  |  |

|-----------|----------------|----------|------|--|--|

| A         | 0.77           | 0.83     | 0.89 |  |  |

| A1        | 0.13           | 0.18     | 0.23 |  |  |

| A3        | 0.16 0.20 0.24 |          |      |  |  |

| A2        |                | 0.45 REF |      |  |  |

| D         |                | 7.00 BSC |      |  |  |

| е         |                | 0.40 BSC |      |  |  |

| E         | 7.00 BSC       |          |      |  |  |

| D1        | 6.00 BSC       |          |      |  |  |

| E1        | 6.00 BSC       |          |      |  |  |

| b         | 0.20 0.25 0.30 |          |      |  |  |

| ааа       | 0.10           |          |      |  |  |

| bbb       | 0.10           |          |      |  |  |

| ddd       | 0.08           |          |      |  |  |

| eee       | 0.15           |          |      |  |  |

| fff       | 0.05           |          |      |  |  |

| Noto      |                |          |      |  |  |

### Table 6.1. BGA192 Package Dimensions

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

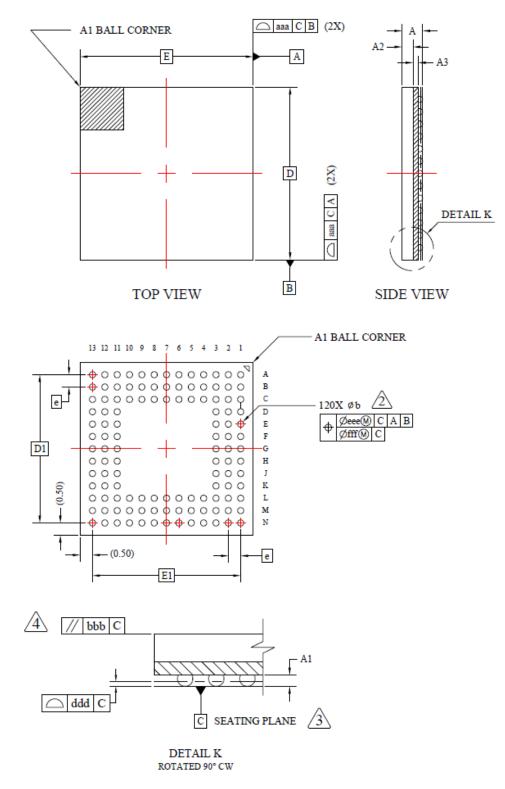

# 8. BGA120 Package Specifications

## 8.1 BGA120 Package Dimensions

Figure 8.1. BGA120 Package Drawing

| Dimension | Min       | Тур       | Мах  |  |  |

|-----------|-----------|-----------|------|--|--|

| A         | -         | -         | 1.30 |  |  |

| A1        | 0.55      | 0.60      | 0.65 |  |  |

| A2        |           | 0.21 BSC  |      |  |  |

| A3        | 0.30      | 0.35 0.40 |      |  |  |

| d         | 0.43      | 0.48      | 0.53 |  |  |

| D         | 10.00 BSC |           |      |  |  |

| D1        | 8.00 BSC  |           |      |  |  |

| E         | 10.00 BSC |           |      |  |  |

| E1        | 8.00 BSC  |           |      |  |  |

| e1        | 0.80 BSC  |           |      |  |  |

| e2        | 0.80 BSC  |           |      |  |  |

| L1        | 1.00 REF  |           |      |  |  |

| L2        | 1.00 REF  |           |      |  |  |

| Noto      |           |           |      |  |  |

### Table 9.1. BGA112 Package Dimensions

Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

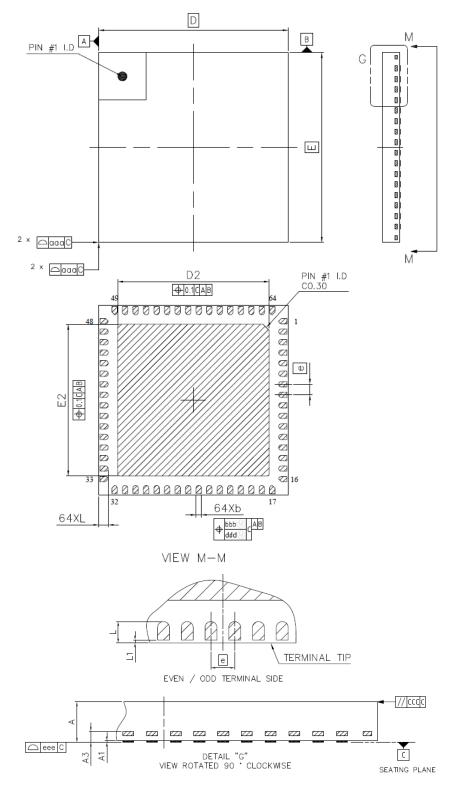

# 12. QFN64 Package Specifications

## 12.1 QFN64 Package Dimensions

Figure 12.1. QFN64 Package Drawing