Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Active                                                                                                        |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 53                                                                                                            |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 64-VFQFN Exposed Pad                                                                                          |

| Supplier Device Package    | 64-QFN (9x9)                                                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b420f2048gm64-br                                   |

|                            |                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2.4 EM2 and EM3 Power Domains

The EFM32GG11 has three independent peripheral power domains for use in EM2 and EM3. Two of these domains are dynamic and can be shut down to save energy. Peripherals associated with the two dynamic power domains are listed in Table 3.1 EM2 and EM3 Peripheral Power Subdomains on page 13. If all of the peripherals in a peripheral power domain are unused, the power domain for that group will be powered off in EM2 and EM3, reducing the overall current consumption of the device. Other EM2, EM3, and EM4-capable peripherals and functions not listed in the table below reside on the primary power domain, which is always on in EM2 and EM3.

| Peripheral Power Domain 1 | Peripheral Power Domain 2 |

|---------------------------|---------------------------|

| ACMP0                     | ACMP1                     |

| PCNT0                     | PCNT1                     |

| ADC0                      | PCNT2                     |

| LETIMER0                  | CSEN                      |

| LESENSE                   | VDAC0                     |

| APORT                     | LEUART0                   |

| -                         | LEUART1                   |

| -                         | LETIMER1                  |

| -                         | 12C0                      |

| -                         | 12C1                      |

| -                         | 12C2                      |

| -                         | IDAC                      |

| -                         | ADC1                      |

| -                         | ACMP2                     |

| -                         | ACMP3                     |

| -                         | LCD                       |

| -                         | RTC                       |

### Table 3.1. EM2 and EM3 Peripheral Power Subdomains

### 3.3 General Purpose Input/Output (GPIO)

EFM32GG11 has up to 144 General Purpose Input/Output pins. GPIO are organized on three independent supply rails, allowing for interface to multiple logic levels in the system simultaneously. Each GPIO pin can be individually configured as either an output or input. More advanced configurations including open-drain, open-source, and glitch-filtering can be configured for each individual GPIO pin. The GPIO pins can be overridden by peripheral connections, like SPI communication. Each peripheral connection can be routed to several GPIO pins on the device. The input value of a GPIO pin can be routed through the Peripheral Reflex System to other peripherals. The GPIO subsystem supports asynchronous external pin interrupts.

### 3.4 Clocking

## 3.4.1 Clock Management Unit (CMU)

The Clock Management Unit controls oscillators and clocks in the EFM32GG11. Individual enabling and disabling of clocks to all peripheral modules is performed by the CMU. The CMU also controls enabling and configuration of the oscillators. A high degree of flexibility allows software to optimize energy consumption in any specific application by minimizing power dissipation in unused peripherals and oscillators.

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Symbol                                                                                                                                                                                                                                                                                         | Test Condition                                                        | Min           | Тур             | Мах             | Unit      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|-----------------|-----------------|-----------|--|--|--|

| Note:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                |                                                                       |               |                 |                 |           |  |  |  |

| U 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol> <li>The minimum voltage required in bypass mode is calculated using R<sub>BYP</sub> from the DCDC specification table. Requirements for<br/>other loads can be calculated as V<sub>DVDD min</sub>+I<sub>LOAD</sub> * R<sub>BYP max</sub>.</li> </ol>                                      |                                                                       |               |                 |                 |           |  |  |  |

| 2. VREGVDD must be tied t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | o AVDD. Both VR                                                                                                                                                                                                                                                                                | EGVDD and AVDD minimum voltage                                        | es must be sa | tisfied for the | part to operat  | te.       |  |  |  |

| , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                | aracteristic specs of the capacitor use<br>s temperature and DC bias. | ed on DECOL   | JPLE to ensu    | re its capacita | ince val- |  |  |  |

| tion, peak currents will be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4. VSCALE0 to VSCALE2 voltage change transitions occur at a rate of 10 mV / usec for approximately 20 usec. During this transi-<br>tion, peak currents will be dependent on the value of the DECOUPLE output capacitor, from 35 mA (with a 1 μF capacitor) to 70 mA (with a 2.7 μF capacitor). |                                                                       |               |                 |                 |           |  |  |  |

| 5. When the CSEN peripher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | al is used with ch                                                                                                                                                                                                                                                                             | opping enabled (CSEN_CTRL_CHO                                         | PEN = ENABI   | LE), IOVDD m    | nust be equal   | to AVDD.  |  |  |  |

| <ol> <li>5. When the CSEN peripheral is used with chopping enabled (CSEN_CTRL_CHOPEN = ENABLE), IOVDD must be equal to AVDD.</li> <li>6. The maximum limit on T<sub>A</sub> may be lower due to device self-heating, which depends on the power dissipation of the specific application. T<sub>A</sub> (max) = T<sub>J</sub> (max) - (THETA<sub>JA</sub> x PowerDissipation). Refer to the Absolute Maximum Ratings table and the Thermal Characteristics table for T<sub>J</sub> and THETA<sub>JA</sub>.</li> </ol> |                                                                                                                                                                                                                                                                                                |                                                                       |               |                 |                 |           |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                |                                                                       |               |                 |                 |           |  |  |  |

# 4.1.3 Thermal Characteristics

| Parameter                  | Symbol                          | Test Condition                    | Min | Тур  | Max | Unit |

|----------------------------|---------------------------------|-----------------------------------|-----|------|-----|------|

| Thermal resistance, QFN64  | THETAJA_QFN64                   | 4-Layer PCB, Air velocity = 0 m/s | _   | 17.8 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 15.4 |     | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 13.8 |     | °C/W |

| Thermal resistance, TQFP64 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 33.9 | _   | °C/W |

| Package                    | TA <sub>JA_TQFP64</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 32.1 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 30.1 | _   | °C/W |

| Thermal resistance,        | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 44.1 | _   | °C/W |

| TQFP100 Package            | TA <sub>JA_TQFP100</sub>        | 4-Layer PCB, Air velocity = 1 m/s | _   | 37.7 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 35.5 | _   | °C/W |

| Thermal resistance, BGA112 | THE-<br>TA <sub>JA_BGA112</sub> | 4-Layer PCB, Air velocity = 0 m/s | _   | 42.0 | _   | °C/W |

| Package                    |                                 | 4-Layer PCB, Air velocity = 1 m/s | _   | 37.0 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 35.3 | _   | °C/W |

| Thermal resistance, BGA120 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 47.9 | _   | °C/W |

| Package                    | TA <sub>JA_BGA120</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 41.8 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 39.6 | _   | °C/W |

| Thermal resistance, BGA152 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 35.7 | _   | °C/W |

| Package                    | TA <sub>JA_BGA152</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 31.0 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 29.5 | _   | °C/W |

| Thermal resistance, BGA192 | THE-                            | 4-Layer PCB, Air velocity = 0 m/s | _   | 47.9 | _   | °C/W |

| Package                    | TA <sub>JA_BGA192</sub>         | 4-Layer PCB, Air velocity = 1 m/s | _   | 41.8 | _   | °C/W |

|                            |                                 | 4-Layer PCB, Air velocity = 2 m/s | _   | 39.6 | _   | °C/W |

# Table 4.3. Thermal Characteristics

| Parameter                                                                                                          | Symbol                  | Test Condition                                                        | Min | Тур  | Max | Unit   |

|--------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------|-----|------|-----|--------|

| Current consumption in EM0<br>mode with all peripherals dis-                                                       | IACTIVE_LPM             | 32 MHz HFRCO, CPU running while loop from flash                       | _   | 82   | _   | µA/MHz |

| abled, DCDC in LP mode <sup>3</sup>                                                                                |                         | 26 MHz HFRCO, CPU running while loop from flash                       | —   | 83   | _   | µA/MHz |

|                                                                                                                    |                         | 16 MHz HFRCO, CPU running while loop from flash                       | _   | 88   | _   | µA/MHz |

|                                                                                                                    |                         | 1 MHz HFRCO, CPU running while loop from flash                        | —   | 257  | _   | µA/MHz |

| Current consumption in EM0 mode with all peripherals dis-                                                          | IACTIVE_CCM_VS          | 19 MHz HFRCO, CPU running while loop from flash                       | _   | 117  | _   | µA/MHz |

| abled and voltage scaling<br>enabled, DCDC in Low<br>Noise CCM mode <sup>1</sup>                                   |                         | 1 MHz HFRCO, CPU running while loop from flash                        | _   | 1231 | _   | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis-                                                       | IACTIVE_LPM_VS          | 19 MHz HFRCO, CPU running while loop from flash                       | —   | 72   |     | µA/MHz |

| abled and voltage scaling enabled, DCDC in LP mode <sup>3</sup>                                                    |                         | 1 MHz HFRCO, CPU running while loop from flash                        | —   | 219  |     | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_DCM</sub>    | 72 MHz HFRCO                                                          | —   | 42   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled, DCDC in Low Noise                                                         |                         | 50 MHz crystal                                                        | —   | 46   | _   | µA/MHz |

| DCM mode <sup>2</sup>                                                                                              |                         | 48 MHz HFRCO                                                          | —   | 46   | _   | µA/MHz |

|                                                                                                                    |                         | 32 MHz HFRCO                                                          | —   | 53   | _   | µA/MHz |

|                                                                                                                    |                         | 26 MHz HFRCO                                                          | —   | 57   | _   | µA/MHz |

|                                                                                                                    |                         | 16 MHz HFRCO                                                          | —   | 72   | _   | µA/MHz |

|                                                                                                                    |                         | 1 MHz HFRCO                                                           | —   | 663  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_LPM</sub>    | 32 MHz HFRCO                                                          | —   | 42   | —   | µA/MHz |

| mode with all peripherals dis-<br>abled, DCDC in Low Power                                                         |                         | 26 MHz HFRCO                                                          | —   | 43   | —   | µA/MHz |

| mode <sup>3</sup>                                                                                                  |                         | 16 MHz HFRCO                                                          | —   | 48   | _   | µA/MHz |

|                                                                                                                    |                         | 1 MHz HFRCO                                                           | _   | 219  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_DCM_VS</sub> | 19 MHz HFRCO                                                          | —   | 60   | —   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled, DCDC in Low<br>Noise DCM mode <sup>2</sup> |                         | 1 MHz HFRCO                                                           | _   | 637  | _   | µA/MHz |

| Current consumption in EM1                                                                                         | I <sub>EM1_LPM_VS</sub> | 19 MHz HFRCO                                                          | _   | 39   | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled. DCDC in LP mode <sup>3</sup>               |                         | 1 MHz HFRCO                                                           | —   | 190  | _   | µA/MHz |

| Current consumption in EM2<br>mode, with voltage scaling                                                           | I <sub>EM2_VS</sub>     | Full 512 kB RAM retention and RTCC running from LFXO                  | _   | 2.8  | _   | μΑ     |

| enabled, DCDC in LP mode <sup>3</sup>                                                                              |                         | Full 512 kB RAM retention and RTCC running from LFRCO                 | —   | 3.1  | _   | μΑ     |

|                                                                                                                    |                         | 16 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>5</sup> | —   | 2.1  | _   | μΑ     |

| Current consumption in EM3 mode, with voltage scaling enabled                                                      | I <sub>EM3_VS</sub>     | Full 512 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO   | _   | 2.4  | _   | μA     |

# 4.1.11 Flash Memory Characteristics<sup>5</sup>

| Parameter                                   | Symbol               | Test Condition                                | Min   | Тур  | Max | Unit   |

|---------------------------------------------|----------------------|-----------------------------------------------|-------|------|-----|--------|

| Flash erase cycles before failure           | EC <sub>FLASH</sub>  |                                               | 10000 | _    | _   | cycles |

| Flash data retention                        | RET <sub>FLASH</sub> | T ≤ 85 °C                                     | 10    | —    | _   | years  |

|                                             |                      | T ≤ 125 °C                                    | 10    | _    | _   | years  |

| Word (32-bit) programming time              | tw_prog              | Burst write, 128 words, average time per word | 20    | 26.2 | 32  | μs     |

|                                             |                      | Single word                                   | 59    | 68.7 | 83  | μs     |

| Page erase time <sup>4</sup>                | t <sub>PERASE</sub>  |                                               | 20    | 26.8 | 35  | ms     |

| Mass erase time <sup>1</sup>                | t <sub>MERASE</sub>  |                                               | 20    | 26.9 | 35  | ms     |

| Device erase time <sup>2 3</sup>            | t <sub>DERASE</sub>  | T ≤ 85 °C                                     | —     | 80.7 | 95  | ms     |

|                                             |                      | T ≤ 125 °C                                    | _     | 80.7 | 100 | ms     |

| Erase current <sup>6</sup>                  | I <sub>ERASE</sub>   | Page Erase                                    |       | _    | 1.7 | mA     |

|                                             |                      | Mass or Device Erase                          |       | _    | 2.1 | mA     |

| Write current <sup>6</sup>                  | I <sub>WRITE</sub>   |                                               | —     | _    | 3.9 | mA     |

| Supply voltage during flash erase and write | V <sub>FLASH</sub>   |                                               | 1.62  | _    | 3.6 | V      |

## Table 4.19. Flash Memory Characteristics<sup>5</sup>

# Note:

- 1. Mass erase is issued by the CPU and erases all flash.

- 2. Device erase is issued over the AAP interface and erases all flash, SRAM, the Lock Bit (LB) page, and the User data page Lock Word (ULW).

- 3. From setting the DEVICEERASE bit in AAP\_CMD to 1 until the ERASEBUSY bit in AAP\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 4. From setting the ERASEPAGE bit in MSC\_WRITECMD to 1 until the BUSY bit in MSC\_STATUS is cleared to 0. Internal setup and hold times for flash control signals are included.

- 5. Flash data retention information is published in the Quarterly Quality and Reliability Report.

6. Measured at 25 °C.

| Parameter                                         | Symbol                | Test Condition                                             | Min | Тур   | Мах | Unit   |

|---------------------------------------------------|-----------------------|------------------------------------------------------------|-----|-------|-----|--------|

| ADC clock frequency                               | f <sub>ADCCLK</sub>   |                                                            | —   | —     | 16  | MHz    |

| Throughput rate                                   | <b>f</b> ADCRATE      |                                                            | —   | _     | 1   | Msps   |

| Conversion time <sup>1</sup>                      | t <sub>ADCCONV</sub>  | 6 bit                                                      | —   | 7     | _   | cycles |

|                                                   |                       | 8 bit                                                      | _   | 9     | _   | cycles |

|                                                   |                       | 12 bit                                                     | —   | 13    |     | cycles |

| Startup time of reference generator and ADC core  | t <sub>ADCSTART</sub> | WARMUPMODE <sup>4</sup> = NORMAL                           | —   | _     | 5   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPIN-<br>STANDBY               | _   | _     | 2   | μs     |

|                                                   |                       | WARMUPMODE <sup>4</sup> = KEEPINSLO-<br>WACC               | _   | _     | 1   | μs     |

| SNDR at 1Msps and f <sub>IN</sub> = 10kHz         | SNDR <sub>ADC</sub>   | Internal reference <sup>7</sup> , differential measurement | TBD | 67    | _   | dB     |

|                                                   |                       | External reference <sup>6</sup> , differential measurement | _   | 68    | _   | dB     |

| Spurious-free dynamic range<br>(SFDR)             | SFDR <sub>ADC</sub>   | 1 MSamples/s, 10 kHz full-scale sine wave                  | _   | 75    | _   | dB     |

| Differential non-linearity<br>(DNL)               | DNL <sub>ADC</sub>    | 12 bit resolution, No missing co-<br>des                   | TBD |       | TBD | LSB    |

| Integral non-linearity (INL),<br>End point method | INL <sub>ADC</sub>    | 12 bit resolution                                          | TBD |       | TBD | LSB    |

| Offset error                                      | VADCOFFSETERR         |                                                            | TBD | 0     | TBD | LSB    |

| Gain error in ADC                                 | VADCGAIN              | Using internal reference                                   | _   | -0.2  | TBD | %      |

|                                                   |                       | Using external reference                                   | _   | -1    | —   | %      |

| Temperature sensor slope                          | V <sub>TS_SLOPE</sub> |                                                            | _   | -1.84 | _   | mV/°C  |

Note:

1. Derived from ADCCLK.

2. PSRR is referenced to AVDD when ANASW=0 and to DVDD when ANASW=1 in EMU\_PWRCTRL.

3. In ADCn\_BIASPROG register.

4. In ADCn CNTL register.

5. The absolute voltage allowed at any ADC input is dictated by the power rail supplied to on-chip circuitry, and may be lower than the effective full scale voltage. All ADC inputs are limited to the ADC supply (AVDD or DVDD depending on EMU PWRCTRL ANASW). Any ADC input routed through the APORT will further be limited by the IOVDD supply to the pin.

6. External reference is 1.25 V applied externally to ADCnEXTREFP, with the selection CONF in the SINGLECTRL\_REF or SCANCTRL\_REF register field and VREFP in the SINGLECTRLX\_VREFSEL or SCANCTRLX\_VREFSEL field. The differential input range with this configuration is ± 1.25 V.

7. Internal reference option used corresponds to selection 2V5 in the SINGLECTRL\_REF or SCANCTRL\_REF register field. The differential input range with this configuration is ± 1.25 V. Typical value is characterized using full-scale sine wave input. Minimum value is production-tested using sine wave input at 1.5 dB lower than full scale.

# 4.1.15 Analog Comparator (ACMP)

| Parameter                                                           | Symbol              | Test Condition                                               | Min | Тур | Мах                         | Unit |

|---------------------------------------------------------------------|---------------------|--------------------------------------------------------------|-----|-----|-----------------------------|------|

| Input voltage range                                                 | V <sub>ACMPIN</sub> | ACMPVDD =<br>ACMPn_CTRL_PWRSEL <sup>1</sup>                  |     | _   | V <sub>ACMPVDD</sub>        | V    |

| Supply voltage                                                      | VACMPVDD            | $BIASPROG^4 \le 0x10 \text{ or } FULL-BIAS^4 = 0$            | 1.8 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

|                                                                     |                     | $0x10 < BIASPROG^4 \le 0x20$ and FULLBIAS <sup>4</sup> = 1   | 2.1 | _   | V <sub>VREGVDD</sub><br>MAX | V    |

| Active current not including                                        | I <sub>ACMP</sub>   | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                          | _   | 50  | _                           | nA   |

| voltage reference <sup>2</sup>                                      |                     | $BIASPROG^4 = 0x10, FULLBIAS^4 = 0$                          | _   | 306 | —                           | nA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1   |     | 6.5 | _                           | μA   |

|                                                                     |                     | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1   |     | 74  | TBD                         | μA   |

| Current consumption of inter-<br>nal voltage reference <sup>2</sup> | IACMPREF            | VLP selected as input using 2.5 V<br>Reference / 4 (0.625 V) |     | 50  | _                           | nA   |

|                                                                     |                     | VLP selected as input using VDD                              |     | 20  | _                           | nA   |

|                                                                     |                     | VBDIV selected as input using 1.25 V reference / 1           | _   | 4.1 | -                           | μA   |

|                                                                     |                     | VADIV selected as input using VDD/1                          | _   | 2.4 | —                           | μA   |

# Table 4.23. Analog Comparator (ACMP)

| Parameter | Symbol                                                              | Test Condition                                             | Min | Тур | Max | Unit    |

|-----------|---------------------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|---------|

|           | rrent is the sum of th<br>al drive.<br>egister.<br>RESIS registers. | etting in ACMPn_CTRL_PWRS<br>e contributions from the ACMF |     |     |     | IACMP + |

| Parameter                                                               | Symbol         | Test Condition                                                                                     | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Supply current, continuous<br>conversions, WARMUP-<br>MODE=KEEPCSENWARM | ICSEN_ACTIVE   | SAR or Delta Modulation conver-<br>sions of 33 pF capacitor,<br>CS0CG=0 (Gain = 10x), always<br>on | _   | 90.5 | _   | μA     |

| HFPERCLK supply current                                                 | ICSEN_HFPERCLK | Current contribution from<br>HFPERCLK when clock to CSEN<br>block is enabled.                      |     | 2.25 | _   | µA/MHz |

# Note:

Current is specified with a total external capacitance of 33 pF per channel. Average current is dependent on how long the module is actively sampling channels within the scan period, and scales with the number of samples acquired. Supply current for a specific application can be estimated by multiplying the current per sample by the total number of samples per period (total\_current = single\_sample\_current \* (number\_of\_channels \* accumulation)).

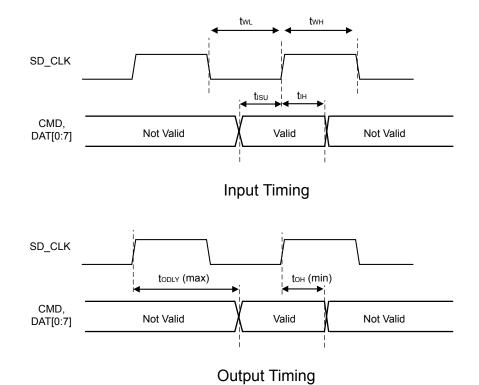

Figure 4.18. SDIO MMC SDR Mode Timing

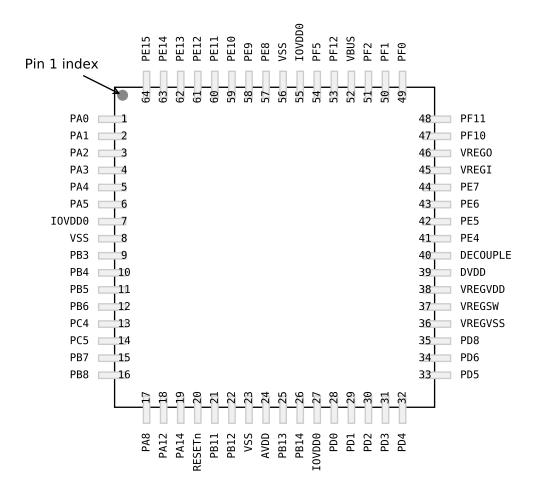

## Figure 5.12. EFM32GG11B8xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Table 5.12. EFM32GG11B8xx in QFP64 Device Pinou | Table 5.12. | 2GG11B8xx in QFP64 Device Pinout |

|-------------------------------------------------|-------------|----------------------------------|

|-------------------------------------------------|-------------|----------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>27<br>55 | Digital IO power supply 0. | VSS      | 8<br>23<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

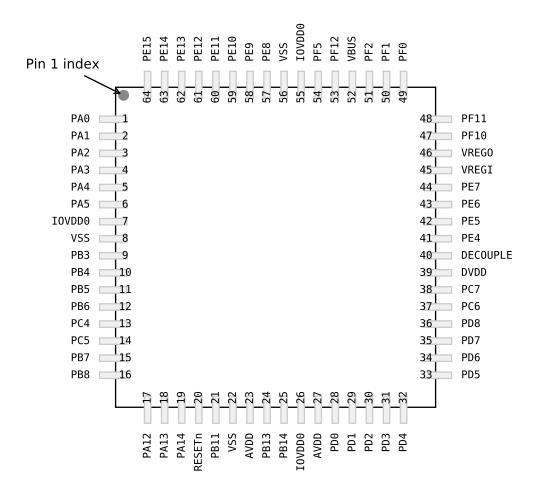

## Figure 5.14. EFM32GG11B4xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>26<br>55 | Digital IO power supply 0. | VSS      | 8<br>22<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

| GPIO Name | Pin Alternate Functionality / Description |                                     |                                                                             |                                                                       |                                           |  |  |  |  |  |  |

|-----------|-------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|--|

|           | Analog                                    | EBI                                 | Timers                                                                      | Communication                                                         | Other                                     |  |  |  |  |  |  |

| PE6       | BUSDY BUSCX<br>LCD_COM2                   | EBI_A13 #0 EBI_A18<br>#1 EBI_A24 #3 | TIM3_CC1 #3<br>TIM5_CC2 #0<br>TIM6_CDTI2 #2<br>WTIM0_CC2 #0<br>WTIM1_CC3 #4 | US0_RX #1 US3_TX<br>#1                                                | PRS_CH6 #2                                |  |  |  |  |  |  |

| PE7       | BUSCY BUSDX<br>LCD_COM3                   | EBI_A14 #0 EBI_A19<br>#1 EBI_A25 #3 | TIM3_CC2 #3<br>TIM5_CC0 #1<br>WTIM1_CC0 #5                                  | US0_TX #1 US3_RX<br>#1                                                | PRS_CH7 #2                                |  |  |  |  |  |  |

| PG11      |                                           | EBI_AD11 #2                         | TIM6_CDTI2 #1<br>WTIM0_CDTI0 #3                                             | ETH_MIIRXD0 #1<br>CAN1_TX #6<br>US3_RTS #5<br>QSPI0_DQS #2            | ETM_TD3 #5                                |  |  |  |  |  |  |

| PG10      |                                           | EBI_AD10 #2                         | TIM2_CC2 #6<br>TIM6_CDTI1 #1<br>WTIM0_CC2 #3                                | ETH_MIIRXD1 #1<br>CAN1_RX #6<br>US3_CTS #3<br>QSPI0_CS1 #2            |                                           |  |  |  |  |  |  |

| PG9       |                                           | EBI_AD09 #2                         | TIM2_CC1 #6<br>TIM6_CDTI0 #1<br>WTIM0_CC1 #3                                | ETH_MIIRXD2 #1<br>CAN0_TX #4<br>US3_CTS #5<br>QSPI0_CS0 #2            |                                           |  |  |  |  |  |  |

| PE3       | BU_STAT                                   | EBI_A10 #0 EBI_A15<br>#1            | TIM3_CC0 #2<br>WTIM1_CC0 #4                                                 | US0_CTS #1<br>U0_RTS #1 U1_RX<br>#3                                   | ACMP1_O #1                                |  |  |  |  |  |  |

| PE4       | BUSDY BUSCX<br>LCD_COM0                   | EBI_A11 #0 EBI_A16<br>#1 EBI_A22 #3 | TIM3_CC1 #2<br>TIM5_CC0 #0<br>TIM6_CDTI0 #2<br>WTIM0_CC0 #0<br>WTIM1_CC1 #4 | US0_CS #1 US1_CS<br>#5 US3_CS #1<br>U0_RX #6 U1_CTS<br>#3 I2C0_SDA #7 | PRS_CH16 #2                               |  |  |  |  |  |  |

| PG14      |                                           | EBI_AD14 #2                         | TIM6_CC2 #2<br>WTIM2_CC0 #4<br>PCNT1_S0IN #7                                | ETH_MIICRS #1<br>US0_CLK #6                                           | ETM_TD0 #5                                |  |  |  |  |  |  |

| PG13      |                                           | EBI_AD13 #2                         | TIM6_CC1 #2<br>WTIM0_CDTI2 #3<br>WTIM2_CC2 #3                               | ETH_MIIRXER #1<br>US0_RX #6                                           | ETM_TD1 #5                                |  |  |  |  |  |  |

| PG12      |                                           | EBI_AD12 #2                         | TIM6_CC0 #2<br>WTIM0_CDTI1 #3<br>WTIM2_CC1 #3                               | ETH_MIIRXDV #1<br>US0_TX #6                                           | ETM_TD2 #5                                |  |  |  |  |  |  |

| PE1       | BUSCY BUSDX                               | EBI_A01 #2 EBI_A08<br>#0            | TIM3_CC1 #1<br>WTIM1_CC2 #3<br>PCNT0_S1IN #1                                | CAN0_TX #6 U0_RX<br>#1 I2C1_SCL #2                                    | CMU_CLKI0 #4<br>PRS_CH23 #1<br>ACMP2_O #2 |  |  |  |  |  |  |

| PE2       | BU_VOUT                                   | EBI_A09 #0 EBI_A14<br>#1            | TIM3_CC2 #1<br>WTIM1_CC3 #3                                                 | US0_RTS #1<br>U0_CTS #1 U1_TX<br>#3                                   | PRS_CH20 #2<br>ACMP0_O #1                 |  |  |  |  |  |  |

| PG15      |                                           | EBI_AD15 #2                         | WTIM2_CC1 #4<br>PCNT1_S1IN #7                                               | ETH_MIICOL #1<br>US0_CS #6                                            | ETM_TCLK #5                               |  |  |  |  |  |  |

| PB15      | BUSAY BUSBX                               | EBI_CS3 #1 EBI_AR-<br>DY #2         | TIM3_CC1 #7                                                                 | ETH_TSUTMRTOG<br>#1 SDIO_WP #2<br>US2_RTS #1<br>US5_RTS #1            | PRS_CH17 #1<br>ETM_TD2 #1                 |  |  |  |  |  |  |

| GPIO Name |                                                            | Pin Alteri                                                | nate Functionality / De                                                                            | escription                                                                      |                                                                         |  |

|-----------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

|           | Analog                                                     | EBI                                                       | Timers                                                                                             | Communication                                                                   | Other                                                                   |  |

| PH14      | BUSACMP3Y BU-<br>SACMP3X                                   | EBI_A26 #2                                                | TIM5_CC1 #2<br>WTIM1_CC2 #7<br>PCNT2_S0IN #7                                                       | US5_CTS #3<br>U1_RTS #5<br>I2C1_SCL #6                                          |                                                                         |  |

| PH15      | BUSACMP3Y BU-<br>SACMP3X                                   | EBI_A27 #2                                                | TIM5_CC2 #2<br>WTIM1_CC3 #7<br>PCNT2_S1IN #6                                                       | US5_RTS #3                                                                      |                                                                         |  |

| PD2       | BUSADC0Y BU-<br>SADC0X                                     | EBI_A06 #1 EBI_A15<br>#3 EBI_A27 #0                       | TIM0_CC1 #2<br>TIM6_CC1 #6<br>WTIM1_CC0 #1                                                         | US1_CLK #1<br>LEU1_TX #2                                                        | DBG_SWO #3                                                              |  |

| PD7       | BUSADC0Y BU-<br>SADC0X<br>ADC0_EXTN<br>ADC1_EXTN<br>OPA1_N | EBI_A11 #1 EBI_A20<br>#3                                  | TIM1_CC1 #4<br>WTIM1_CC1 #2 LE-<br>TIM0_OUT1 #0<br>PCNT0_S1IN #3                                   | US1_TX #2<br>US3_CLK #1 U0_TX<br>#6 I2C0_SCL #1                                 | CMU_CLK0 #2<br>LES_ALTEX1<br>ACMP1_O #2<br>ETM_TCLK #0                  |  |

| PB8       | LFXTAL_N                                                   |                                                           | TIM0_CDTI1 #4<br>TIM1_CC1 #3                                                                       | US0_RX #4 US1_CS<br>#0 US4_RX #0<br>U0_RTS #4                                   | CMU_CLKI0 #2<br>PRS_CH23 #0                                             |  |

| PC4       | BUSACMP0Y BU-<br>SACMP0X OPA0_P                            | EBI_AD11 #1<br>EBI_ALE #2<br>EBI_NANDREn #3<br>EBI_A26 #0 | TIM0_CC0 #5<br>TIM0_CDTI2 #3<br>TIM2_CC2 #5 LE-<br>TIM0_OUT0 #3<br>PCNT1_S0IN #3                   | SDIO_CD #1<br>US2_CLK #0<br>US4_CLK #0 U0_TX<br>#4 U1_CTS #4<br>I2C1_SDA #0     | LES_CH4<br>PRS_CH18 #2<br>GPIO_EM4WU6                                   |  |

| PA7       | BUSAY BUSBX<br>LCD_SEG35                                   | EBI_AD13 #1<br>EBI_A01 #3<br>EBI_CSTFT #0                 | TIM0_CC2 #5 LE-<br>TIM1_OUT0 #0<br>PCNT1_S0IN #4                                                   | US2_TX #2<br>US4_CTS #0<br>US5_RX #1                                            | PRS_CH7 #1                                                              |  |

| PA10      | BUSBY BUSAX<br>LCD_SEG38                                   | EBI_CS0 #1<br>EBI_A04 #3<br>EBI_VSNC #0                   | TIM2_CC2 #0<br>TIM0_CC2 #6<br>WTIM2_CC1 #0                                                         | US2_CS #2                                                                       | PRS_CH10 #0                                                             |  |

| PA12      | BUSBY BUSAX                                                | EBI_CS2 #1<br>EBI_REn #2<br>EBI_A00 #0 EBI_A06<br>#3      | TIM2_CC0 #1<br>WTIM0_CDTI0 #2<br>WTIM2_CC0 #1 LE-<br>TIM1_OUT0 #2<br>PCNT1_S0IN #5                 | CAN1_RX #5<br>US0_CLK #5<br>US2_RTS #2                                          | CMU_CLK0 #5<br>PRS_CH12 #0<br>ACMP1_O #3                                |  |

| PA14      | BUSBY BUSAX<br>LCD_BEXT                                    | EBI_REn #1<br>EBI_A02 #0 EBI_A08<br>#3                    | TIM2_CC2 #1<br>WTIM0_CDTI2 #2<br>WTIM2_CC2 #1 LE-<br>TIM1_OUT1 #2                                  | US1_TX #6 US2_RX<br>#3 US3_RTS #2                                               | PRS_CH14 #0<br>ACMP1_O #4                                               |  |

| PB11      | BUSAY BUSBX<br>VDAC0_OUT0 /<br>OPA0_OUT<br>IDAC0_OUT       | EBI_BL1 #2 EBI_A02<br>#1 EBI_A11 #3                       | TIM0_CDTI2 #4<br>TIM1_CC2 #3<br>WTIM2_CC2 #2 LE-<br>TIM0_OUT0 #1<br>PCNT0_S1IN #7<br>PCNT1_S0IN #6 | US0_CTS #5<br>US1_CLK #5<br>US2_CS #3<br>US5_CLK #0<br>U1_CTS #2<br>I2C1_SDA #1 | CMU_CLK1 #5<br>CMU_CLKI0 #7<br>PRS_CH21 #2<br>ACMP0_O #3<br>GPIO_EM4WU7 |  |

| PH1       | BUSADC1Y BU-<br>SADC1X                                     | EBI_DTEN #2                                               |                                                                                                    | US0_RTS #6<br>LEU1_RX #5                                                        |                                                                         |  |

| PH4       | BUSADC1Y BU-<br>SADC1X                                     | EBI_A16 #2                                                | TIM6_CC2 #3<br>WTIM2_CC0 #6                                                                        | US4_TX #4                                                                       |                                                                         |  |

| PH7       | BUSADC1Y BU-<br>SADC1X                                     | EBI_A19 #2                                                | TIM6_CDTI2 #3<br>WTIM2_CC0 #7                                                                      | US4_CS #4                                                                       |                                                                         |  |

| PH10      | BUSACMP3Y BU-<br>SACMP3X                                   | EBI_A22 #2                                                | TIM6_CC2 #4<br>WTIM1_CC2 #6                                                                        | US5_TX #3                                                                       |                                                                         |  |

| GPIO Name | Pin Alternate Functionality / Description                               |                          |                                                                                                   |                                                                                 |                                                                     |  |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|--|

|           | Analog                                                                  | EBI                      | Timers                                                                                            | Communication                                                                   | Other                                                               |  |  |  |  |  |  |

| PB13      | BUSAY BUSBX<br>HFXTAL_P                                                 |                          | TIM6_CC0 #5<br>WTIM1_CC0 #0<br>PCNT2_S0IN #2                                                      | US0_CLK #4<br>US1_CTS #5<br>US5_CS #0<br>LEU0_TX #1                             | CMU_CLKI0 #3<br>PRS_CH7 #0                                          |  |  |  |  |  |  |

| PB14      | BUSBY BUSAX<br>HFXTAL_N                                                 |                          | TIM6_CC1 #5<br>WTIM1_CC1 #0<br>PCNT2_S1IN #2                                                      | US0_CS #4<br>US1_RTS #5<br>US5_CTS #0<br>LEU0_RX #1                             | PRS_CH6 #1                                                          |  |  |  |  |  |  |

| PD1       | VDAC0_OUT1ALT /<br>OPA1_OUTALT #4<br>BUSADC0Y BU-<br>SADC0X OPA3_OUT    | EBI_A05 #1 EBI_A14<br>#3 | TIM4_CDTI1<br>TIM0_CC0 #2<br>TIM6_CC0 #6<br>WTIM1_CC3 #0<br>PCNT2_S1IN #0                         | CAN0_TX #2<br>US1_RX #1                                                         | DBG_SWO #2                                                          |  |  |  |  |  |  |

| PD6       | BUSADC0Y BU-<br>SADC0X<br>ADC0_EXTP<br>VDAC0_EXT<br>ADC1_EXTP<br>OPA1_P | EBI_A10 #1 EBI_A19<br>#3 | TIM1_CC0 #4<br>TIM6_CC2 #7<br>WTIM0_CDTI2 #4<br>WTIM1_CC0 #2 LE-<br>TIM0_OUT0 #0<br>PCNT0_S0IN #3 | US0_RTS #5<br>US1_RX #2<br>US2_CTS #5<br>US3_CTS #2<br>U0_RTS #5<br>I2C0_SDA #1 | CMU_CLK2 #2<br>LES_ALTEX0<br>PRS_CH5 #2<br>ACMP0_O #2<br>ETM_TD0 #0 |  |  |  |  |  |  |

| Alternate     | LOCA                                   | TION  |                                   |

|---------------|----------------------------------------|-------|-----------------------------------|

| Functionality | 0 - 3                                  | 4 - 7 | Description                       |

| ETH_MDIO      | 0: PB3<br>1: PD13<br>2: PC0<br>3: PA15 |       | Ethernet Management Data I/O.     |

| ETH_MIICOL    | 0: PB2<br>1: PG15<br>2: PB4            |       | Ethernet MII Collision Detect.    |

| ETH_MIICRS    | 0: PB1<br>1: PG14<br>2: PB3            |       | Ethernet MII Carrier Sense.       |

| ETH_MIIRXCLK  | 0: PA15<br>1: PG7<br>2: PD12           |       | Ethernet MII Receive Clock.       |

| ETH_MIIRXD0   | 0: PE12<br>1: PG11<br>2: PF9           |       | Ethernet MII Receive Data Bit 0.  |

| ETH_MIIRXD1   | 0: PE13<br>1: PG10<br>2: PD9           |       | Ethernet MII Receive Data Bit 1.  |

| ETH_MIIRXD2   | 0: PE14<br>1: PG9<br>2: PD10           |       | Ethernet MII Receive Data Bit 2.  |

| ETH_MIIRXD3   | 0: PE15<br>1: PG8<br>2: PD11           |       | Ethernet MII Receive Data Bit 3.  |

| ETH_MIIRXDV   | 0: PE11<br>1: PG12<br>2: PF8           |       | Ethernet MII Receive Data Valid.  |

| ETH_MIIRXER   | 0: PE10<br>1: PG13<br>2: PF7           |       | Ethernet MII Receive Error.       |

| ETH_MIITXCLK  | 0: PA0<br>1: PG0                       |       | Ethernet MII Transmit Clock.      |

| ETH_MIITXD0   | 0: PA4<br>1: PG4                       |       | Ethernet MII Transmit Data Bit 0. |

| ETH_MIITXD1   | 0: PA3<br>1: PG3                       |       | Ethernet MII Transmit Data Bit 1. |

| Alternate<br>Functionality | LOC <i>A</i><br>0 - 3 | ATION<br>4 - 7 | Description          |

|----------------------------|-----------------------|----------------|----------------------|

| LCD_SEG7                   | 0: PE11               |                | LCD segment line 7.  |

| LCD_SEG8                   | 0: PE12               |                | LCD segment line 8.  |

| LCD_SEG9                   | 0: PE13               |                | LCD segment line 9.  |

| LCD_SEG10                  | 0: PE14               |                | LCD segment line 10. |

| LCD_SEG11                  | 0: PE15               |                | LCD segment line 11. |

| LCD_SEG12                  | 0: PA15               |                | LCD segment line 12. |

| LCD_SEG13                  | 0: PA0                |                | LCD segment line 13. |

| LCD_SEG14                  | 0: PA1                |                | LCD segment line 14. |

| LCD_SEG15                  | 0: PA2                |                | LCD segment line 15. |

| LCD_SEG16                  | 0: PA3                |                | LCD segment line 16. |

| LCD_SEG17                  | 0: PA4                |                | LCD segment line 17. |

| LCD_SEG18                  | 0: PA5                |                | LCD segment line 18. |

| LCD_SEG19                  | 0: PA6                |                | LCD segment line 19. |

| Alternate     | LOC                                      | ATION             |                                                                                                                                                            |  |  |  |

|---------------|------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Functionality | 0 - 3                                    | 4 - 7             | Description                                                                                                                                                |  |  |  |

| US3_RTS       | 0: PA5<br>1: PC1<br>2: PA14<br>3: PC15   | 4: PG5<br>5: PG11 | USART3 Request To Send hardware flow control output.                                                                                                       |  |  |  |

| US3_RX        | 0: PA1<br>1: PE7<br>2: PB7<br>3: PG7     | 4: PG1<br>5: PI13 | USART3 Asynchronous Receive.<br>USART3 Synchronous mode Master Input / Slave Output (MISO).                                                                |  |  |  |

| US3_TX        | 0: PA0<br>1: PE6<br>2: PB3<br>3: PG6     | 4: PG0<br>5: PI12 | USART3 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART3 Synchronous mode Master Output / Slave Input (MOSI). |  |  |  |

| US4_CLK       | 0: PC4<br>1: PD11<br>2: Pl2<br>3: Pl8    | 4: PH6            | USART4 clock input / output.                                                                                                                               |  |  |  |

| US4_CS        | 0: PC5<br>1: PD12<br>2: Pl3<br>3: Pl9    | 4: PH7            | USART4 chip select input / output.                                                                                                                         |  |  |  |

| US4_CTS       | 0: PA7<br>1: PD13<br>2: Pl4<br>3: Pl10   | 4: PH8            | USART4 Clear To Send hardware flow control input.                                                                                                          |  |  |  |

| US4_RTS       | 0: PA8<br>1: PD14<br>2: PI5<br>3: PI11   | 4: PH9            | USART4 Request To Send hardware flow control output.                                                                                                       |  |  |  |

| US4_RX        | 0: PB8<br>1: PD10<br>2: PI1<br>3: PI7    | 4: PH5            | USART4 Asynchronous Receive.<br>USART4 Synchronous mode Master Input / Slave Output (MISO).                                                                |  |  |  |

| US4_TX        | 0: PB7<br>1: PD9<br>2: PI0<br>3: PI6     | 4: PH4            | USART4 Asynchronous Transmit. Also used as receive input in half duplex communica-<br>tion.<br>USART4 Synchronous mode Master Output / Slave Input (MOSI). |  |  |  |

| US5_CLK       | 0: PB11<br>1: PD13<br>2: PF13<br>3: PH12 |                   | USART5 clock input / output.                                                                                                                               |  |  |  |

| US5_CS        | 0: PB13<br>1: PD14<br>2: PF12<br>3: PH13 |                   | USART5 chip select input / output.                                                                                                                         |  |  |  |

| US5_CTS       | 0: PB14<br>1: PD15<br>2: PF11<br>3: PH14 |                   | USART5 Clear To Send hardware flow control input.                                                                                                          |  |  |  |

| US5_RTS       | 0: PB12<br>1: PB15<br>2: PF10<br>3: PH15 |                   | USART5 Request To Send hardware flow control output.                                                                                                       |  |  |  |

# EFM32GG11 Family Data Sheet Pin Definitions

| Port           | Bus                  | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СН9 | CH8 | CH7 | CH6 | CH5 | CH4 | СНЗ | CH2 | CH1 | CH0 |

|----------------|----------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| VD             | DAC0_OUT1 / OPA1_OUT |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     |     |     |     |     |     |     |     |     |

| APORT1Y        | BUSAY                | PB15 |      | PB13 |      | PB11 |      | PB9  |      |      |      | PB5  |      | PB3  |      | PB1  |      | PA15 |      | PA13 |      | PA11 |      | PA9 |     | PA7 |     | PA5 |     | PA3 |     | PA1 |     |

| APORT2Y        | BUSBY                |      | PB14 |      | PB12 |      | PB10 |      |      |      | PB6  |      | PB4  |      | PB2  |      | PB0  |      | PA14 |      | PA12 |      | PA10 |     | PA8 |     | PA6 |     | PA4 |     | PA2 |     | PAO |

| <b>APORT3Y</b> | BUSCY                | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7 |     | PE5 |     |     |     | PE1 |     |

| APORT4Y        | BUSDY                |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |     | PE6 |     | PE4 |     |     |     | PEO |

| Dimension | Min      | Тур      | Мах  |  |  |  |  |  |  |

|-----------|----------|----------|------|--|--|--|--|--|--|

| A         | 0.78     | 0.84     | 0.90 |  |  |  |  |  |  |

| A1        | 0.13     | 0.18     | 0.23 |  |  |  |  |  |  |

| A3        | 0.16     | 0.20     | 0.24 |  |  |  |  |  |  |

| A2        |          | 0.45 REF |      |  |  |  |  |  |  |

| D         |          | 8.00 BSC |      |  |  |  |  |  |  |

| е         |          | 0.50 BSC |      |  |  |  |  |  |  |

| E         | 8.00 BSC |          |      |  |  |  |  |  |  |

| D1        | 6.50 BSC |          |      |  |  |  |  |  |  |

| E1        |          | 6.50 BSC |      |  |  |  |  |  |  |

| b         | 0.20     | 0.25     | 0.30 |  |  |  |  |  |  |

| ааа       |          | 0.10     |      |  |  |  |  |  |  |

| bbb       |          | 0.10     |      |  |  |  |  |  |  |

| ddd       |          | 0.08     |      |  |  |  |  |  |  |

| eee       | 0.15     |          |      |  |  |  |  |  |  |

| fff       | 0.05     |          |      |  |  |  |  |  |  |

| Noto      | 1        |          |      |  |  |  |  |  |  |

## Table 7.1. BGA152 Package Dimensions

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## Table 10.2. TQFP100 PCB Land Pattern Dimensions

| Min | Min Nom Max |                                  |  |  |  |  |  |  |  |

|-----|-------------|----------------------------------|--|--|--|--|--|--|--|

|     | 15.4        |                                  |  |  |  |  |  |  |  |

|     | 15.4        |                                  |  |  |  |  |  |  |  |

|     | 0.50 BSC    |                                  |  |  |  |  |  |  |  |

|     | 0.30        |                                  |  |  |  |  |  |  |  |

|     | 1.50        |                                  |  |  |  |  |  |  |  |

|     | Min         | 15.4<br>15.4<br>0.50 BSC<br>0.30 |  |  |  |  |  |  |  |

### Note:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release. 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

### 10.3 TQFP100 Package Marking

Figure 10.3. TQFP100 Package Marking

The package marking consists of:

- PPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- · WW The 2-digit workweek when the device was assembled.