Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                        |

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 50                                                                                                            |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 64-TQFP                                                                                                       |

| Supplier Device Package    | 64-TQFP (10x10)                                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b420f2048gq64-b                                    |

|                            |                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Timers/Counters

- 7× 16-bit Timer/Counter

- 3 + 4 Compare/Capture/PWM channels (4 + 4 on one timer instance)

- Dead-Time Insertion on several timer instances

- 4× 32-bit Timer/Counter

- 32-bit Real Time Counter and Calendar (RTCC)

- 24-bit Real Time Counter (RTC)

- 32-bit Ultra Low Energy CRYOTIMER for periodic wakeup from any Energy Mode

- 2× 16-bit Low Energy Timer for waveform generation

- 3× 16-bit Pulse Counter with asynchronous operation

- 2× Watchdog Timer with dedicated RC oscillator

# Low Energy Sensor Interface (LESENSE)

- Autonomous sensor monitoring in Deep Sleep Mode

- Wide range of sensors supported, including LC sensors and capacitive buttons

- Up to 16 inputs

- Ultra efficient Power-on Reset and Brown-Out Detector

- Debug Interface

- 2-pin Serial Wire Debug interface

- 1-pin Serial Wire Viewer

- 4-pin JTAG interface

- Embedded Trace Macrocell (ETM)

Pre-Programmed USB/UART Bootloader

# Wide Operating Range

- 1.8 V to 3.8 V single power supply

- Integrated DC-DC, down to 1.8 V output with up to 200 mA load current for system

- Standard (-40  $^\circ C$  to 85  $^\circ C$   $T_{AMB})$  and Extended (-40  $^\circ C$  to 125  $^\circ C$   $T_J)$  temperature grades available

- Packages

- QFN64 (9x9 mm)

- TQFP64 (10x10 mm)

- TQFP100 (14x14 mm)

- BGA112 (10x10 mm)

- BGA120 (7x7 mm)

- BGA152 (8x8 mm)

- BGA192 (7x7mm)

#### 3.4.2 Internal and External Oscillators

The EFM32GG11 supports two crystal oscillators and fully integrates five RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 50 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxiliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC and the Serial Wire Viewer port with a wide frequency range.

- An integrated auxilliary high frequency RC oscillator (USHFRCO) is available for timing the USB, SDIO and QSPI peripherals. The USHFRCO can be syncronized to the host's USB clock to allow the USB to operate in device mode without the additional cost of an external crystal.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

#### 3.5 Counters/Timers and PWM

#### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

#### 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER\_0 only.

#### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

#### 3.5.4 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of wave-forms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

#### 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

### 4.1.6 Backup Supply Domain

| Parameter                                                   | Symbol               | Test Condition                                  | Min  | Тур  | Max  | Unit |

|-------------------------------------------------------------|----------------------|-------------------------------------------------|------|------|------|------|

| Backup supply voltage range                                 | V <sub>BU_VIN</sub>  |                                                 | 1.8  | —    | 3.8  | V    |

| PWRRES resistor                                             | R <sub>PWRRES</sub>  | EMU_BUCTRL_PWRRES =<br>RES0                     | 3400 | 3900 | 4400 | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES1                     | 1450 | 1800 | 2150 | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES2                     | 1000 | 1350 | 1700 | Ω    |

|                                                             |                      | EMU_BUCTRL_PWRRES =<br>RES3                     | 525  | 815  | 1100 | Ω    |

| Output impedance between<br>BU_VIN and BU_VOUT <sup>2</sup> | R <sub>BU_VOUT</sub> | EMU_BUCTRL_VOUTRES =<br>STRONG                  | 35   | 110  | 185  | Ω    |

|                                                             |                      | EMU_BUCTRL_VOUTRES =<br>MED                     | 475  | 775  | 1075 | Ω    |

|                                                             |                      | EMU_BUCTRL_VOUTRES =<br>WEAK                    | 5600 | 6500 | 7400 | Ω    |

| Supply current                                              | I <sub>BU_VIN</sub>  | BU_VIN not powering backup do-<br>main          | _    | 11   | TBD  | nA   |

|                                                             |                      | BU_VIN powering backup do-<br>main <sup>1</sup> |      | 550  | TBD  | nA   |

### Table 4.6. Backup Supply Domain

# Note:

1. Additional current required by backup circuitry when backup is active. Includes supply current of backup switches and backup regulator. Does not include supply current required for backed-up circuitry.

2. BU\_VOUT and BU\_STAT signals are not available in all package configurations. Check the device pinout for availability.

#### 4.1.7 Current Consumption

# 4.1.7.1 Current Consumption 3.3 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 3.3 V. T = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

## Table 4.7. Current Consumption 3.3 V without DC-DC Converter

| Parameter                                                              | Symbol                 | Test Condition                                     | Min | Тур | Max | Unit   |

|------------------------------------------------------------------------|------------------------|----------------------------------------------------|-----|-----|-----|--------|

| Current consumption in EM0 mode with all peripherals dis-              | I <sub>ACTIVE</sub>    | 72 MHz HFRCO, CPU running<br>Prime from flash      | _   | 120 | _   | µA/MHz |

| abled                                                                  |                        | 72 MHz HFRCO, CPU running while loop from flash    | _   | 120 | TBD | µA/MHz |

|                                                                        |                        | 72 MHz HFRCO, CPU running CoreMark loop from flash | _   | 140 |     | µA/MHz |

|                                                                        |                        | 50 MHz crystal, CPU running while loop from flash  | _   | 123 | _   | µA/MHz |

|                                                                        |                        | 48 MHz HFRCO, CPU running while loop from flash    | _   | 122 | TBD | µA/MHz |

|                                                                        |                        | 32 MHz HFRCO, CPU running while loop from flash    | _   | 124 | _   | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO, CPU running while loop from flash    | _   | 126 | TBD | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO, CPU running while loop from flash    | _   | 131 | _   | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO, CPU running while loop from flash     | _   | 319 | TBD | µA/MHz |

| Current consumption in EM0<br>mode with all peripherals dis-           | I <sub>ACTIVE_VS</sub> | 19 MHz HFRCO, CPU running while loop from flash    | _   | 107 | _   | µA/MHz |

| abled and voltage scaling enabled                                      |                        | 1 MHz HFRCO, CPU running while loop from flash     | _   | 262 | _   | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1</sub>       | 72 MHz HFRCO                                       | —   | 57  | TBD | µA/MHz |

| mode with all peripherals disabled                                     |                        | 50 MHz crystal                                     | _   | 60  | _   | µA/MHz |

|                                                                        |                        | 48 MHz HFRCO                                       | _   | 59  | TBD | µA/MHz |

|                                                                        |                        | 32 MHz HFRCO                                       | _   | 61  |     | µA/MHz |

|                                                                        |                        | 26 MHz HFRCO                                       |     | 63  | TBD | µA/MHz |

|                                                                        |                        | 16 MHz HFRCO                                       |     | 68  | _   | µA/MHz |

|                                                                        |                        | 1 MHz HFRCO                                        | _   | 255 | TBD | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub>    | 19 MHz HFRCO                                       | _   | 55  | _   | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                        | 1 MHz HFRCO                                        | _   | 210 | _   | µA/MHz |

| Parameter                                                                              | Symbol               | Test Condition                                                                                          | Min                                                        | Тур  | Мах  | Unit |

|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------|------|

| Current consumption in EM2 mode, with voltage scaling                                  | I <sub>EM2_VS</sub>  | Full 512 kB RAM retention and RTCC running from LFXO                                                    | _                                                          | 3.9  | _    | μA   |

| enabled                                                                                |                      | Full 512 kB RAM retention and RTCC running from LFRCO                                                   | —                                                          | 4.3  | _    | μA   |

|                                                                                        |                      | 16 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup>                                   | _                                                          | 2.8  | TBD  | μA   |

| Current consumption in EM3<br>mode, with voltage scaling<br>enabled                    | I <sub>EM3_VS</sub>  | Full 512 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO                                     | _                                                          | 3.6  | TBD  | μA   |

| Current consumption in<br>EM4H mode, with voltage                                      | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | _                                                          | 1.08 | _    | μA   |

| scaling enabled                                                                        |                      |                                                                                                         | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO | —    | 0.69 | _    |

|                                                                                        |                      | 128 byte RAM retention, no RTCC                                                                         | _                                                          | 0.69 | TBD  | μA   |

| Current consumption in EM4S mode                                                       | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | _                                                          | 0.16 | TBD  | μA   |

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled | I <sub>PD1_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _                                                          | 0.68 | _    | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled | I <sub>PD2_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _                                                          | 0.28 | _    | μA   |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.4 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

| Parameter                                 | Symbol                 | Test Condition                                             | Min | Тур      | Мах | Unit |

|-------------------------------------------|------------------------|------------------------------------------------------------|-----|----------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,     | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD | 0        | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-BIAS^4 = 1)$     |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 33       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 46       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 57       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 68       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 79       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 90       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD | 0        | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -33      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -45      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -57      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -67      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -78      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -88      | TBD | mV   |

| Comparator delay <sup>3</sup>             | t <sub>acmpdelay</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30       | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x10, FULLBIAS <sup>4</sup><br>= 0 |     | 3.7      | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 |     | 360      | _   | ns   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | _   | 35       | _   | ns   |

| Offset voltage                            | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _        | TBD | mV   |

| Reference voltage                         | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25     | TBD | V    |

|                                           |                        | Internal 2.5 V reference                                   | TBD | 2.5      | TBD | V    |

| Capacitive sense internal re-<br>sistance | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | _   | infinite | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 1                                  |     | 15       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 2                                  | —   | 27       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 3                                  | —   | 39       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 4                                  | —   | 51       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 5                                  | —   | 100      |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 6                                  | —   | 162      | -   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 7                                  | —   | 235      | -   | kΩ   |

# 4.1.17 Current Digital to Analog Converter (IDAC)

| Parameter                                   | Symbol                   | Test Condition                                                                      | Min  | Тур  | Max | Unit   |

|---------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|------|------|-----|--------|

| Number of ranges                            | N <sub>IDAC_RANGES</sub> |                                                                                     | _    | 4    | _   | ranges |

| Output current                              | I <sub>IDAC_OUT</sub>    | RANGSEL <sup>1</sup> = RANGE0                                                       | 0.05 | _    | 1.6 | μA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE1                                                       | 1.6  | _    | 4.7 | μA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE2                                                       | 0.5  | _    | 16  | μA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE3                                                       | 2    | _    | 64  | μA     |

| Linear steps within each range              | N <sub>IDAC_STEPS</sub>  |                                                                                     | _    | 32   | _   | steps  |

| Step size                                   | SS <sub>IDAC</sub>       | RANGSEL <sup>1</sup> = RANGE0                                                       | _    | 50   | _   | nA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE1                                                       | _    | 100  | _   | nA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE2                                                       | _    | 500  | _   | nA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE3                                                       | _    | 2    | _   | μA     |

| Total accuracy, STEPSEL <sup>1</sup> = 0x10 | ACCIDAC                  | EM0 or EM1, AVDD=3.3 V, T = 25<br>°C                                                | TBD  | _    | TBD | %      |

|                                             |                          | EM0 or EM1, Across operating temperature range                                      | TBD  | _    | TBD | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE0,<br>AVDD=3.3 V, T = 25 °C | _    | -2.7 | _   | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE1,<br>AVDD=3.3 V, T = 25 °C | _    | -2.5 | _   | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE2,<br>AVDD=3.3 V, T = 25 °C | _    | -1.5 | _   | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE3,<br>AVDD=3.3 V, T = 25 °C | _    | -1.0 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE0, AVDD=3.3 V, T<br>= 25 °C | _    | -1.1 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE1, AVDD=3.3 V, T<br>= 25 °C | _    | -1.1 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE2, AVDD=3.3 V, T<br>= 25 °C | _    | -0.9 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE3, AVDD=3.3 V, T<br>= 25 °C | _    | -0.9 | -   | %      |

# Table 4.25. Current Digital to Analog Converter (IDAC)

#### 4.1.25 External Bus Interface (EBI)

#### **EBI Write Enable Output Timing**

Timing applies to both EBI\_WEn and EBI\_NANDWEn for all addressing modes and both polarities. All numbers are based on route locations 0,1,2 only (with all EBI alternate functions using the same location at the same time). Timing is specified at 10% and 90% of IOVDD, 25 pF external loading, and slew rate for all GPIO set to 6.

### Table 4.36. EBI Write Enable Timing

| Parameter                                                                                                                    | Symbol              | Test Condition | Min                                                          | Тур | Мах | Unit |

|------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|--------------------------------------------------------------|-----|-----|------|

| Output hold time, from trail-<br>ing EBI_WEn / EBI_NAND-<br>WEn edge to EBI_AD,<br>EBI_A, EBI_CSn, EBI_BLn<br>invalid        | t <sub>OH_WEn</sub> | IOVDD ≥ 1.62 V | -22 +<br>(WRHOLD<br>* t{ <sub>}HFCOR-<br/>ECLK{</sub> )      | -   | _   | ns   |

|                                                                                                                              |                     | IOVDD ≥ 3.0 V  | -13 +<br>(WRHOLD<br><sup>* t</sup> HFCOR-<br>ECLK)           | _   | _   | ns   |

| Output setup time, from<br>EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading<br>EBI_WEn / EBI_NANDWEn<br>edge <sup>1</sup> | tosu_wen            | IOVDD ≥ 1.62 V | -12 +<br>(WRSET-<br>UP *<br>t <sub>HFCOR-</sub><br>ECLK)     | _   |     | ns   |

|                                                                                                                              |                     | IOVDD ≥ 3.0 V  | -10 +<br>(WRSET-<br>UP *<br>t <sub>HFCOR-</sub><br>ЕСLК)     |     |     | ns   |

| EBI_WEn / EBI_NANDWEn pulse width <sup>1</sup>                                                                               | twidth_wen          | IOVDD ≥ 1.62 V | -6 +<br>(MAX(1,<br>WRSTRB)<br><sup>* t</sup> HFCOR-<br>ECLK) |     |     | ns   |

|                                                                                                                              |                     | IOVDD ≥ 3.0 V  | -5 +<br>(MAX(1,<br>WRSTRB)<br><sup>* t</sup> HFCOR-<br>ECLK) | _   | -   | ns   |

Note:

1. The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFWE=0. The leading edge of EBI\_WEn can be moved to the right by setting HALFWE=1. This decreases the length of t<sub>WIDTH\_WEn</sub> and increases the length of t<sub>OSU\_WEn</sub> by 1/2 \* t<sub>HFCLKNODIV</sub>.

## SDIO DDR Mode Timing

Timing is specified for route location 0 at 1.8 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 6, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 30 pF on all pins.

| Parameter                                     | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|-----------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer          | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    |      | 20  | MHz  |

|                                               |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 22.6 | —    | _   | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                               | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 22.6 | _    | _   | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                               | t <sub>R</sub>      |                                   | 1.69 | 6.52 | —   | ns   |

| Clock fall time                               | t <sub>F</sub>      |                                   | 1.42 | 4.96 | _   | ns   |

| Input setup time, CMD valid to SD_CLK         | t <sub>ISU</sub>    |                                   | 6    |      | _   | ns   |

| Input hold time, SD_CLK to CMD change         | t <sub>IH</sub>     |                                   | 1.8  |      | _   | ns   |

| Output delay time, SD_CLK to CMD valid        | t <sub>ODLY</sub>   |                                   | 0    |      | 16  | ns   |

| Output hold time, SD_CLK to CMD change        | t <sub>OH</sub>     |                                   | 0.8  | _    | _   | ns   |

| Input setup time, DAT[0:3]<br>valid to SD_CLK | t <sub>ISU2X</sub>  |                                   | 6    | _    | _   | ns   |

| Input hold time, SD_CLK to DAT[0:3] change    | t <sub>IH2X</sub>   |                                   | 1.5  | _    | _   | ns   |

| Output delay time, SD_CLK to DAT[0:3] valid   | t <sub>ODLY2X</sub> |                                   | 0    | _    | 16  | ns   |

| Output hold time, SD_CLK to DAT[0:3] change   | t <sub>OH2X</sub>   |                                   | 0.8  |      | —   | ns   |

# Table 4.49. SDIO DS Mode Timing (Location 0)

#### SDIO MMC SDR Mode Timing at 1.8 V

Timing is specified for route location 0 at 1.8 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 20 pF on all pins.

| Parameter                                          | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|----------------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer               | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    | _    | 25  | MHz  |

|                                                    |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                     | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 18.1 | _    | _   | ns   |

|                                                    |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                                    | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 18.1 | _    | _   | ns   |

|                                                    |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                                    | t <sub>R</sub>      |                                   | 1.96 | 8.27 | _   | ns   |

| Clock fall time                                    | t <sub>F</sub>      |                                   | 1.67 | 6.90 | _   | ns   |

| Input setup time, CMD,<br>DAT[0:7] valid to SD_CLK | t <sub>ISU</sub>    |                                   | 5.3  | _    | _   | ns   |

| Input hold time, SD_CLK to CMD, DAT[0:7] change    | tiH                 |                                   | 2.5  | _    | _   | ns   |

| Output delay time, SD_CLK to CMD, DAT[0:7] valid   | t <sub>ODLY</sub>   |                                   | 0    | _    | 16  | ns   |

| Output hold time, SD_CLK to CMD, DAT[0:7] change   | t <sub>OH</sub>     |                                   | 3    | _    | _   | ns   |

### Table 4.50. SDIO MMC SDR Mode Timing (Location 0, 1.8V I/O)

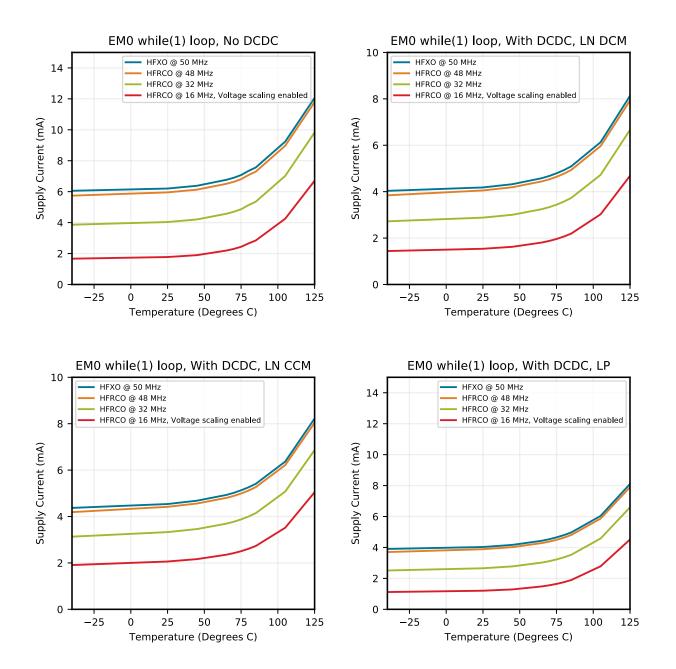

Figure 4.24. EM0 Active Mode Typical Supply Current vs. Temperature

| Pin Name | Pin(s)          | Description          | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|-----------------|----------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD8      | H8              | GPIO                 | PD5      | H9     | GPIO                                                                                                                                                                                                        |

| PD6      | H10             | GPIO                 | PD7      | H11    | GPIO                                                                                                                                                                                                        |

| PC1      | J1              | GPIO (5V)            | PC3      | J2     | GPIO (5V)                                                                                                                                                                                                   |

| PD15     | J3              | GPIO (5V)            | PA12     | J4     | GPIO (5V)                                                                                                                                                                                                   |

| PA9      | J5              | GPIO                 | PA10     | J6     | GPIO                                                                                                                                                                                                        |

| PB9      | J7              | GPIO (5V)            | PB10     | J8     | GPIO (5V)                                                                                                                                                                                                   |

| PD2      | J9              | GPIO (5V)            | PD3      | J10    | GPIO                                                                                                                                                                                                        |

| PD4      | J11             | GPIO                 | PB7      | K1     | GPIO                                                                                                                                                                                                        |

| PC4      | K2              | GPIO                 | PA13     | K3     | GPIO (5V)                                                                                                                                                                                                   |

| PA11     | К5              | GPIO                 | RESETn   | K6     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| AVDD     | K8<br>K9<br>L10 | Analog power supply. | PD1      | K11    | GPIO                                                                                                                                                                                                        |

| PB8      | L1              | GPIO                 | PC5      | L2     | GPIO                                                                                                                                                                                                        |

| PA14     | L3              | GPIO                 | PB11     | L5     | GPIO                                                                                                                                                                                                        |

| PB12     | L6              | GPIO                 | PB13     | L8     | GPIO                                                                                                                                                                                                        |

| PB14     | L9              | GPIO                 | PD0      | L11    | GPIO (5V)                                                                                                                                                                                                   |

### Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PD13, PD14, and PD15 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description |

|----------|--------|-------------|----------|--------|-------------|

| PF2      | 78     | GPIO        | NC       | 79     | No Connect. |

| PF12     | 80     | GPIO        | PF5      | 81     | GPIO        |

| PF6      | 84     | GPIO        | PF7      | 85     | GPIO        |

| PF8      | 86     | GPIO        | PF9      | 87     | GPIO        |

| PD9      | 88     | GPIO        | PD10     | 89     | GPIO        |

| PD11     | 90     | GPIO        | PD12     | 91     | GPIO        |

| PE8      | 92     | GPIO        | PE9      | 93     | GPIO        |

| PE10     | 94     | GPIO        | PE11     | 95     | GPIO        |

| PE12     | 96     | GPIO        | PE13     | 97     | GPIO        |

| PE14     | 98     | GPIO        | PE15     | 99     | GPIO        |

| PA15     | 100    | GPIO        |          |        |             |

| Note:    |        | · ]         |          |        |             |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate      | LOCA                                  | TION  |                                             |

|----------------|---------------------------------------|-------|---------------------------------------------|

| Functionality  | 0 - 3                                 | 4 - 7 | Description                                 |

| ETH_MIITXD2    | 0: PA2<br>1: PG2                      |       | Ethernet MII Transmit Data Bit 2.           |

| ETH_MIITXD3    | 0: PA1<br>1: PG1                      |       | Ethernet MII Transmit Data Bit 3.           |

| ETH_MIITXEN    | 0: PA5<br>1: PG5                      |       | Ethernet MII Transmit Enable.               |

| ETH_MIITXER    | 0: PA6<br>1: PG6                      |       | Ethernet MII Transmit Error.                |

| ETH_RMIICRSDV  | 0: PA4<br>1: PD11                     |       | Ethernet RMII Carrier Sense / Data Valid.   |

| ETH_RMIIREFCLK | 0: PA3<br>1: PD10                     |       | Ethernet RMII Reference Clock.              |

| ETH_RMIIRXD0   | 0: PA2<br>1: PD9                      |       | Ethernet RMII Receive Data Bit 0.           |

| ETH_RMIIRXD1   | 0: PA1<br>1: PF9                      |       | Ethernet RMII Receive Data Bit 1.           |

| ETH_RMIIRXER   | 0: PA5<br>1: PD12                     |       | Ethernet RMII Receive Error.                |

| ETH_RMIITXD0   | 0: PE15<br>1: PF7                     |       | Ethernet RMII Transmit Data Bit 0.          |

| ETH_RMIITXD1   | 0: PE14<br>1: PF6                     |       | Ethernet RMII Transmit Data Bit 1.          |

| ETH_RMIITXEN   | 0: PA0<br>1: PF8                      |       | Ethernet RMII Transmit Enable.              |

| ETH_TSUEXTCLK  | 0: PB5<br>1: PD15<br>2: PC2<br>3: PF8 |       | Ethernet IEEE1588 External Reference Clock. |

| Alternate          | LOCATION                              |                    |                                                |  |

|--------------------|---------------------------------------|--------------------|------------------------------------------------|--|

| Functionality      | 0 - 3                                 | 4 - 7              | Description                                    |  |

| ETH_TSUTMR-<br>TOG | 0: PB6<br>1: PB15<br>2: PC3<br>3: PF9 |                    | Ethernet IEEE1588 Timer Toggle.                |  |

| ETM_TCLK           | 0: PD7<br>1: PF8<br>2: PC6<br>3: PA6  | 4: PE11<br>5: PG15 | Embedded Trace Module ETM clock .              |  |

| ETM_TD0            | 0: PD6<br>1: PF9<br>2: PC7<br>3: PA2  | 4: PE12<br>5: PG14 | Embedded Trace Module ETM data 0.              |  |

| ETM_TD1            | 0: PD3<br>1: PD13<br>2: PD3<br>3: PA3 | 4: PE13<br>5: PG13 | Embedded Trace Module ETM data 1.              |  |

| ETM_TD2            | 0: PD4<br>1: PB15<br>2: PD4<br>3: PA4 | 4: PE14<br>5: PG12 | Embedded Trace Module ETM data 2.              |  |

| ETM_TD3            | 0: PD5<br>1: PF3<br>2: PD5<br>3: PA5  | 4: PE15<br>5: PG11 | Embedded Trace Module ETM data 3.              |  |

| GPIO_EM4WU0        | 0: PA0                                |                    | Pin can be used to wake the system up from EM4 |  |

| GPIO_EM4WU1        | 0: PA6                                |                    | Pin can be used to wake the system up from EM4 |  |

| GPIO_EM4WU2        | 0: PC9                                |                    | Pin can be used to wake the system up from EM4 |  |

| GPIO_EM4WU3        | 0: PF1                                |                    | Pin can be used to wake the system up from EM4 |  |

| GPIO_EM4WU4        | 0: PF2                                |                    | Pin can be used to wake the system up from EM4 |  |

| GPIO_EM4WU5        | 0: PE13                               |                    | Pin can be used to wake the system up from EM4 |  |

| GPIO_EM4WU6        | 0: PC4                                |                    | Pin can be used to wake the system up from EM4 |  |

| Alternate     | LOCA                                  | TION  |                          |

|---------------|---------------------------------------|-------|--------------------------|

| Functionality | 0 - 3                                 | 4 - 7 | Description              |

| QSPI0_DQ7     | 0: PE11<br>1: PB6<br>2: PG8           |       | Quad SPI 0 Data 7.       |

| QSPI0_DQS     | 0: PF9<br>1: PE15<br>2: PG11          |       | Quad SPI 0 Data S.       |

| QSPI0_SCLK    | 0: PF6<br>1: PE14<br>2: PG0           |       | Quad SPI 0 Serial Clock. |

| SDIO_CD       | 0: PF8<br>1: PC4<br>2: PA6<br>3: PB10 |       | SDIO Card Detect.        |

| SDIO_CLK      | 0: PE13<br>1: PE14                    |       | SDIO Serial Clock.       |

| SDIO_CMD      | 0: PE12<br>1: PE15                    |       | SDIO Command.            |

| SDIO_DAT0     | 0: PE11<br>1: PA0                     |       | SDIO Data 0.             |

| SDIO_DAT1     | 0: PE10<br>1: PA1                     |       | SDIO Data 1.             |

| SDIO_DAT2     | 0: PE9<br>1: PA2                      |       | SDIO Data 2.             |

| SDIO_DAT3     | 0: PE8<br>1: PA3                      |       | SDIO Data 3.             |

| SDIO_DAT4     | 0: PD12<br>1: PA4                     |       | SDIO Data 4.             |

| SDIO_DAT5     | 0: PD11<br>1: PA5                     |       | SDIO Data 5.             |

| SDIO_DAT6     | 0: PD10<br>1: PB3                     |       | SDIO Data 6.             |

| Alternate     | LOCATION                                 |                                        |                                                           |

|---------------|------------------------------------------|----------------------------------------|-----------------------------------------------------------|

| Functionality | 0 - 3                                    | 4 - 7                                  | Description                                               |

| WTIM0_CC2     | 0: PE6<br>1: PD14<br>2: PG4<br>3: PG10   | 4: PF1<br>5: PB2<br>6: PB5<br>7: PC3   | Wide timer 0 Capture Compare input / output channel 2.    |

| WTIM0_CDTI0   | 0: PE10<br>1: PD15<br>2: PA12<br>3: PG11 | 4: PD4                                 | Wide timer 0 Complimentary Dead Time Insertion channel 0. |

| WTIM0_CDTI1   | 0: PE11<br>1: PG0<br>2: PA13<br>3: PG12  | 4: PD5                                 | Wide timer 0 Complimentary Dead Time Insertion channel 1. |

| WTIM0_CDTI2   | 0: PE12<br>1: PG1<br>2: PA14<br>3: PG13  | 4: PD6                                 | Wide timer 0 Complimentary Dead Time Insertion channel 2. |

| WTIM1_CC0     | 0: PB13<br>1: PD2<br>2: PD6<br>3: PC7    | 4: PE3<br>5: PE7<br>6: PH8<br>7: PH12  | Wide timer 1 Capture Compare input / output channel 0.    |

| WTIM1_CC1     | 0: PB14<br>1: PD3<br>2: PD7<br>3: PE0    | 4: PE4<br>5: PI0<br>6: PH9<br>7: PH13  | Wide timer 1 Capture Compare input / output channel 1.    |

| WTIM1_CC2     | 0: PD0<br>1: PD4<br>2: PD8<br>3: PE1     | 4: PE5<br>5: PI1<br>6: PH10<br>7: PH14 | Wide timer 1 Capture Compare input / output channel 2.    |

| WTIM1_CC3     | 0: PD1<br>1: PD5<br>2: PC6<br>3: PE2     | 4: PE6<br>5: PI2<br>6: PH11<br>7: PH15 | Wide timer 1 Capture Compare input / output channel 3.    |

| WTIM2_CC0     | 0: PA9<br>1: PA12<br>2: PB9<br>3: PB12   | 4: PG14<br>5: PD3<br>6: PH4<br>7: PH7  | Wide timer 2 Capture Compare input / output channel 0.    |

| WTIM2_CC1     | 0: PA10<br>1: PA13<br>2: PB10<br>3: PG12 | 4: PG15<br>5: PD4<br>6: PH5<br>7: PH8  | Wide timer 2 Capture Compare input / output channel 1.    |

| WTIM2_CC2     | 0: PA11<br>1: PA14<br>2: PB11<br>3: PG13 | 4: PH0<br>5: PD5<br>6: PH6<br>7: PH9   | Wide timer 2 Capture Compare input / output channel 2.    |

| WTIM3_CC0     | 0: PD9<br>1: PC8<br>2: PC11<br>3: PC14   | 4: PI3<br>5: PI6<br>6: PB6<br>7: PF13  | Wide timer 3 Capture Compare input / output channel 0.    |

| WTIM3_CC1     | 0: PD10<br>1: PC9<br>2: PC12<br>3: PF10  | 4: Pl4<br>5: Pl7<br>6: PF4<br>7: PF14  | Wide timer 3 Capture Compare input / output channel 1.    |

| Alternate     | LOCATION                                 |                                        |                                                        |

|---------------|------------------------------------------|----------------------------------------|--------------------------------------------------------|

| Functionality | 0 - 3                                    | 4 - 7                                  | Description                                            |

| WTIM3_CC2     | 0: PD11<br>1: PC10<br>2: PC13<br>3: PF11 | 4: PI5<br>5: PF6<br>6: PF12<br>7: PF15 | Wide timer 3 Capture Compare input / output channel 2. |

Certain alternate function locations may have non-interference priority. These locations will take precedence over any other functions selected on that pin (i.e. another alternate function enabled to the same pin inadvertently).

Some alternate functions may also have high speed priority on certain locations. These locations ensure the fastest possible paths to the pins for timing-critical signals.

The following table lists the alternate functions and locations with special priority.

## Table 5.22. Alternate Functionality Priority

| Alternate Functionality | Location          | Priority                 |

|-------------------------|-------------------|--------------------------|

| CMU_CLK2                | 1: PA3<br>5: PD10 | High Speed<br>High Speed |

| CMU_CLKI0               | 1: PA3<br>5: PD10 | High Speed<br>High Speed |

| ETH_RMIICRSDV           | 0: PA4<br>1: PD11 | High Speed<br>High Speed |

| ETH_RMIIREFCLK          | 0: PA3<br>1: PD10 | High Speed<br>High Speed |

| ETH_RMIIRXD0            | 0: PA2<br>1: PD9  | High Speed<br>High Speed |

| ETH_RMIIRXD1            | 0: PA1<br>1: PF9  | High Speed<br>High Speed |

| ETH_RMIIRXER            | 0: PA5<br>1: PD12 | High Speed<br>High Speed |

| ETH_RMIITXD0            | 0: PE15<br>1: PF7 | High Speed<br>High Speed |

| ETH_RMIITXD1            | 0: PE14<br>1: PF6 | High Speed<br>High Speed |

| ETH_RMIITXEN            | 0: PA0<br>1: PF8  | High Speed<br>High Speed |

| QSPI0_CS0               | 0: PF7            | High Speed               |

| QSPI0_CS1               | 0: PF8            | High Speed               |

| QSPI0_DQ0               | 0: PD9            | High Speed               |

| QSPI0_DQ1               | 0: PD10           | High Speed               |

| QSPI0_DQ2               | 0: PD11           | High Speed               |

| QSPI0_DQ3               | 0: PD12           | High Speed               |

| QSPI0_DQ4               | 0: PE8            | High Speed               |

| QSPI0_DQ5               | 0: PE9            | High Speed               |

| QSPI0_DQ6               | 0: PE10           | High Speed               |

| QSPI0_DQ7               | 0: PE11           | High Speed               |

|                         |                   |                          |

| Alternate Functionality | Location | Priority         |

|-------------------------|----------|------------------|

| QSPI0_DQS               | 0: PF9   | High Speed       |

| QSPI0_SCLK              | 0: PF6   | High Speed       |

| SDIO_CLK                | 0: PE13  | High Speed       |

| SDIO_CMD                | 0: PE12  | High Speed       |

| SDIO_DAT0               | 0: PE11  | High Speed       |

| SDIO_DAT1               | 0: PE10  | High Speed       |

| SDIO_DAT2               | 0: PE9   | High Speed       |

| SDIO_DAT3               | 0: PE8   | High Speed       |

| SDIO_DAT4               | 0: PD12  | High Speed       |

| SDIO_DAT5               | 0: PD11  | High Speed       |

| SDIO_DAT6               | 0: PD10  | High Speed       |

| SDIO_DAT7               | 0: PD9   | High Speed       |

| TIM0_CC0                | 3: PB6   | Non-interference |

| TIM0_CC1                | 3: PC0   | Non-interference |

| TIM0_CC2                | 3: PC1   | Non-interference |

| TIM0_CDTI0              | 1: PC13  | Non-interference |

| TIM0_CDTI1              | 1: PC14  | Non-interference |

| TIM0_CDTI2              | 1: PC15  | Non-interference |

| TIM2_CC0                | 0: PA8   | Non-interference |

| TIM2_CC1                | 0: PA9   | Non-interference |

| TIM2_CC2                | 0: PA10  | Non-interference |

| TIM2_CDTI0              | 0: PB0   | Non-interference |

| TIM2_CDTI1              | 0: PB1   | Non-interference |

| TIM2_CDTI2              | 0: PB2   | Non-interference |

| TIM4_CC0                | 0: PF3   | Non-interference |

| TIM4_CC1                | 0: PF4   | Non-interference |

| TIM4_CC2                | 0: PF12  | Non-interference |

| TIM4_CDTI0              | 0: PD0   | Non-interference |

| TIM4_CDTI1              | 0: PD1   | Non-interference |

| TIM4_CDTI2              | 0: PD3   | Non-interference |

| TIM6_CC0                | 0: PG0   | Non-interference |

| TIM6_CC1                | 0: PG1   | Non-interference |

| TIM6_CC2                | 0: PG2   | Non-interference |

| TIM6_CDTI0              | 0: PG3   | Non-interference |

| TIM6_CDTI1              | 0: PG4   | Non-interference |

| TIM6_CDTI2              | 0: PG5   | Non-interference |

# 13. Revision History

## **Revision 0.6**

March, 2018

- Removed "Confindential" watermark.

- Updated 4.1 Electrical Characteristics and 4.2 Typical Performance Curves with latest characterization data.

### Revision 0.2

October, 2017

- · Updated memory maps to latest formatting and to include all peripherals.

- Updated all electrical specifications tables with latest characterization results.

- Absolute Maximum Ratings Table:

- Removed redundant I<sub>VSSMAX</sub> line.

- Added footnote to clarify V<sub>DIGPIN</sub> specification for 5V tolerant GPIO.

- General Operating Conditions Table:

- Removed dV<sub>DD</sub> specification and redundant footnote about shorting VREGVDD and AVDD together.

- Added footnote about IOVDD voltage restriction when CSEN peripheral is used with chopping enabled.

- Flash Memory Characteristics Table: Added timing measurement clarification for Device Erase and Mass Erase.

- · Analog to Digital Converter (ADC) Table:

- · Added header text for general specification conditions.

- Added footnote for clarification of input voltage limits.

- · Minor typographical corrections, including capitalization, mis-spellings and punctuation marks, throughout document.

- Minor formatting and styling updates, including table formats, TOC location, and boilerplate information throughout document.

#### **Revision 0.1**

April 27th, 2017

Initial release.