Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E-XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                              |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 72MHz                                                                        |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART  |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                              |

| Number of I/O              | 95                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                  |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 120-VFBGA                                                                    |

| Supplier Device Package    | 120-BGA (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b520f2048il120-br |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4.2 Internal and External Oscillators

The EFM32GG11 supports two crystal oscillators and fully integrates five RC oscillators, listed below.

- A high frequency crystal oscillator (HFXO) with integrated load capacitors, tunable in small steps, provides a precise timing reference for the MCU. Crystal frequencies in the range from 4 to 50 MHz are supported. An external clock source such as a TCXO can also be applied to the HFXO input for improved accuracy over temperature.

- A 32.768 kHz crystal oscillator (LFXO) provides an accurate timing reference for low energy modes.

- An integrated high frequency RC oscillator (HFRCO) is available for the MCU system. The HFRCO employs fast startup at minimal energy consumption combined with a wide frequency range. When crystal accuracy is not required, it can be operated in free-running mode at a number of factory-calibrated frequencies. A digital phase-locked loop (DPLL) feature allows the HFRCO to achieve higher accuracy and stability by referencing other available clock sources such as LFXO and HFXO.

- An integrated auxiliary high frequency RC oscillator (AUXHFRCO) is available for timing the general-purpose ADC and the Serial Wire Viewer port with a wide frequency range.

- An integrated auxilliary high frequency RC oscillator (USHFRCO) is available for timing the USB, SDIO and QSPI peripherals. The USHFRCO can be syncronized to the host's USB clock to allow the USB to operate in device mode without the additional cost of an external crystal.

- An integrated low frequency 32.768 kHz RC oscillator (LFRCO) can be used as a timing reference in low energy modes, when crystal accuracy is not required.

- An integrated ultra-low frequency 1 kHz RC oscillator (ULFRCO) is available to provide a timing reference at the lowest energy consumption in low energy modes.

### 3.5 Counters/Timers and PWM

### 3.5.1 Timer/Counter (TIMER)

TIMER peripherals keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each TIMER is a 16-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the TIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit TIMER\_0 only.

## 3.5.2 Wide Timer/Counter (WTIMER)

WTIMER peripherals function just as TIMER peripherals, but are 32 bits wide. They keep track of timing, count events, generate PWM outputs and trigger timed actions in other peripherals through the PRS system. The core of each WTIMER is a 32-bit counter with up to 4 compare/capture channels. Each channel is configurable in one of three modes. In capture mode, the counter state is stored in a buffer at a selected input event. In compare mode, the channel output reflects the comparison of the counter to a programmed threshold value. In PWM mode, the WTIMER supports generation of pulse-width modulation (PWM) outputs of arbitrary waveforms defined by the sequence of values written to the compare registers, with optional dead-time insertion available in timer unit WTIMER\_0 only.

### 3.5.3 Real Time Counter and Calendar (RTCC)

The Real Time Counter and Calendar (RTCC) is a 32-bit counter providing timekeeping in all energy modes. The RTCC includes a Binary Coded Decimal (BCD) calendar mode for easy time and date keeping. The RTCC can be clocked by any of the on-board oscillators with the exception of the AUXHFRCO, and it is capable of providing system wake-up at user defined instances. The RTCC includes 128 bytes of general purpose data retention, allowing easy and convenient data storage in all energy modes down to EM4H.

### 3.5.4 Low Energy Timer (LETIMER)

The unique LETIMER is a 16-bit timer that is available in energy mode EM2 Deep Sleep in addition to EM1 Sleep and EM0 Active. This allows it to be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of wave-forms with minimal software intervention. The LETIMER is connected to the Real Time Counter and Calendar (RTCC), and can be configured to start counting on compare matches from the RTCC.

#### 3.5.5 Ultra Low Power Wake-up Timer (CRYOTIMER)

The CRYOTIMER is a 32-bit counter that is capable of running in all energy modes. It can be clocked by either the 32.768 kHz crystal oscillator (LFXO), the 32.768 kHz RC oscillator (LFRCO), or the 1 kHz RC oscillator (ULFRCO). It can provide periodic Wakeup events and PRS signals which can be used to wake up peripherals from any energy mode. The CRYOTIMER provides a wide range of interrupt periods, facilitating flexible ultra-low energy operation.

| 0x40024000               | ETH     | Ņ   |                                      | 8xe0100008               | /            | PRS                | 0x400e6000               |

|--------------------------|---------|-----|--------------------------------------|--------------------------|--------------|--------------------|--------------------------|

| 0x40022400               |         | 1   | CM4 Peripherals                      | 8xe88fffff               | ,            | RMU                | 0x400e5400               |

| 0x40022000               | USB     |     |                                      |                          | 1            | KMIO               | 0x400e5000               |

| 0x40020400               |         | 1   |                                      | 8xdfffffff               |              | СМИ                | 0x400e4400               |

| 0x40020000               | SMU     |     | QSPI0                                | 8xcfffffff               |              | 0.10               | 0x400e4000               |

| 0x4001d400               |         |     |                                      | 8×955555555              |              | EMU                | 0x400e3400               |

| 0x4001d000               | TRNG0   | [ \ | 5010 1 0                             |                          | 1            |                    | 0x400e3000<br>0x4008f400 |

| 0x4001c800               |         |     | EBI Region 3                         | 8x8c666666               |              | CRYOTIMER          | 0x4008f000               |

| 0x4001c400               | QSPI0   |     | EBI Region 2                         | 8x88999999               | ,            |                    | 0x4008e400               |

| 0x4001c000               | GPCRC   |     | EBI Region 1                         | 8x87ffffff               | 1            | CSEN               | 0x4008e000               |

| 0x4001b000               |         |     | EBI Region 0                         | 8×83ffffff               |              | 2C2                | 0x40089c00               |

| 0x4001ac00               | WTIMER3 |     | EBI Region 0                         |                          | 1            | 1202               | 0x40089800               |

| 0x4001a800               | WTIMER2 | 1   |                                      | 8x366f6466               | 1            | 2C0                | 0x40089400               |

| 0x4001a400               | WTIMER1 | 1   | Bit Set                              | 0x460f03ff               |              | GPIO               | 0x40089000               |

| 0x4001a000               | WTIMER0 |     | (Peripherals / CRYPTO0)              | 0×46000000               | /            |                    | 0x40088000               |

| 0x40019c00               |         | 1   |                                      | 8×455f6466               | /            | VDAC0              | 0x40086400<br>0x40086000 |

| 0x40019800               | TIMER6  |     |                                      | 0x44010400<br>0x440f03ff |              |                    | 0x40086000               |

| 0x40019400               | TIMER5  | ( · | Bit Clear<br>(Peripherals / CRYPTO0) |                          | 1            | DAC0               | 0x40084000               |

| 0x40019000               | TIMER4  | ۱ ۱ | (renpherals / ettir roo)             | 0x44000000               |              |                    | 0x40082800               |

| 0x40018c00               | TIMER3  |     |                                      | 8x43£46666               |              | ADC1               | 0x40082400               |

| 0x40018800               | TIMER2  | 1   | Bit-Band                             | 0x43e3ffff               | 1            | ADC0               | 0x40082000               |

| 0x40018800               | TIMER1  | ] \ | (Peripherals / CRYPTO0 / SDI         | O) <sub>0×42000000</sub> |              | ACMP3              | 0x40081000               |

| 0x40018400               | TIMERO  |     |                                      | 8×40146666               | ' '          | ACMP2              | 0x40080c00               |

| 0x40018000               |         | ) \ | USB                                  | 8×48135555               | 1            | ACMP1              | 0x40080800               |

| 0x40014800<br>0x40014400 | UART1   | 1 \ | 058                                  |                          |              | ACMP0              | 0x40080400               |

| 0x40014400<br>0x40014000 | UART0   |     |                                      | 8×488‡£555               | '            |                    | 0x40080000               |

| 0x40014000<br>0x40011800 |         | 1 \ | SDIO                                 | 8×488f1666               | 1            | PCNT2              | 0x4006ec00<br>0x4006e800 |

|                          | USART5  | 1 \ |                                      |                          | 1            | PCNT1              | 0x4006e400               |

| 0x40011400<br>0x40011000 | USART4  | 1   |                                      | 8×488f8455               | /            | PCNT0              | 0x4006e000               |

|                          | USART3  | 1 \ | CRYPTO0                              | 8×488‡8355               | /            |                    | 0x4006a800               |

| 0x40010c00               | USART2  | 1   | Peripherals 1                        | 8×48845555               |              | LEUART1<br>LEUART0 | 0x4006a400               |

| 0x40010800               | USART1  |     | Desigh and a O                       |                          |              | LEUARTO            | 0x4006a000               |

| 0x40010400               | USART0  | 1   | Peripherals 0                        | 8×48835555               | 1            | LETIMER1           | 0x40066800               |

| 0x40010000               |         | 1   |                                      | 8×36666666               |              | LETIMERO           | 0x40066400               |

| 0x4000b400               | EBI     | 1 / | SRAM (bit-band)                      | 8x22666666               | <b>`</b>     |                    | 0×40066000               |

| 0x4000b000               |         | 1 / |                                      |                          | Λ.           | RTCC               | 0x40062400<br>0x40062000 |

| 0x40004800               | CAN1    |     |                                      | 8x21ffffff               | \<br>\       |                    | 0x40062000               |

| 0x40004400               | CAN0    |     | RAM2 (data space)                    | 8x28846666               | `            | RTC                | 0x40060000               |

| 0x40004000               |         | 1 / | RAM1 (data space)                    | 8×28835555               | \            |                    | 0x40055400               |

| 0x40003000               | LDMA    |     |                                      |                          | $\mathbf{i}$ | LESENSE            | 0x40055000               |

| 0x40002000               |         |     | RAM0 (data space)                    | 8x28816666               | N.           | LCD                | 0x40054400               |

| 0x40001400               | FPUEH   | 1 / |                                      | 0x1fffffff               | \            |                    | 0x40054000               |

| 0x40001000               |         | 1 / | Code                                 |                          | Λ.           | WDOG1              | 0x40052800               |

| 0×40000800               | MSC     | /   |                                      | 0×00000000               | \<br>\       | WDOG1<br>WDOG0     | 0x40052400               |

| 0x40000000               |         | r   |                                      |                          | i '          |                    | 0x40052000               |

Figure 3.3. EFM32GG11 Memory Map — Peripherals

## 4.1.7.2 Current Consumption 3.3 V using DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = IOVDD = 3.3 V, DVDD = 1.8 V DC-DC output. T = 25 °C. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

| Table 4.8. | <b>Current Consumption 3.3</b> | V using DC-DC Converter |

|------------|--------------------------------|-------------------------|

|------------|--------------------------------|-------------------------|

| Parameter                                                 | Symbol      | Test Condition                                        | Min | Тур  | Мах | Unit   |

|-----------------------------------------------------------|-------------|-------------------------------------------------------|-----|------|-----|--------|

| mode with all peripherals dis-                            | IACTIVE_DCM | 72 MHz HFRCO, CPU running<br>Prime from flash         | _   | 80   | -   | µA/MHz |

| abled, DCDC in Low Noise<br>DCM mode <sup>2</sup>         |             | 72 MHz HFRCO, CPU running while loop from flash       | _   | 80   | _   | µA/MHz |

|                                                           |             | 72 MHz HFRCO, CPU running CoreMark loop from flash    | _   | 92   | _   | µA/MHz |

|                                                           |             | 50 MHz crystal, CPU running while loop from flash     | _   | 84   | _   | µA/MHz |

|                                                           |             | 48 MHz HFRCO, CPU running while loop from flash       | _   | 84   | _   | µA/MHz |

|                                                           |             | 32 MHz HFRCO, CPU running while loop from flash       | _   | 90   | -   | µA/MHz |

|                                                           |             | 26 MHz HFRCO, CPU running while loop from flash       | _   | 94   | _   | µA/MHz |

|                                                           |             | 16 MHz HFRCO, CPU running while loop from flash       | _   | 109  | _   | µA/MHz |

|                                                           |             | 1 MHz HFRCO, CPU running while loop from flash        | _   | 698  | _   | µA/MHz |

| Current consumption in EM0 mode with all peripherals dis- | IACTIVE_CCM | 72 MHz HFRCO, CPU running<br>Prime from flash         | _   | 84   | _   | µA/MHz |

| abled, DCDC in Low Noise<br>CCM mode <sup>1</sup>         |             | 72 MHz HFRCO, CPU running while loop from flash       | _   | 84   | -   | µA/MHz |

|                                                           |             | 72 MHz HFRCO, CPU running<br>CoreMark loop from flash | _   | 95   | _   | µA/MHz |

|                                                           |             | 50 MHz crystal, CPU running while loop from flash     | _   | 91   | _   | µA/MHz |

|                                                           |             | 48 MHz HFRCO, CPU running while loop from flash       | _   | 92   | _   | µA/MHz |

|                                                           |             | 32 MHz HFRCO, CPU running while loop from flash       | _   | 104  | _   | µA/MHz |

|                                                           |             | 26 MHz HFRCO, CPU running while loop from flash       | _   | 113  | _   | µA/MHz |

|                                                           |             | 16 MHz HFRCO, CPU running while loop from flash       | _   | 142  | _   | µA/MHz |

|                                                           |             | 1 MHz HFRCO, CPU running while loop from flash        | _   | 1264 | _   | µA/MHz |

## 4.1.7.3 Current Consumption 1.8 V without DC-DC Converter

Unless otherwise indicated, typical conditions are: VREGVDD = AVDD = DVDD = 1.8 V. T = 25 °C. DCDC is off. Minimum and maximum values in this table represent the worst conditions across supply voltage and process variation at T = 25 °C.

# Table 4.9. Current Consumption 1.8 V without DC-DC Converter

| Parameter                                                              | Symbol              | Test Condition                                                        | Min | Тур | Max | Unit   |

|------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------|-----|-----|-----|--------|

| mode with all peripherals dis-                                         | I <sub>ACTIVE</sub> | 72 MHz HFRCO, CPU running<br>Prime from flash                         | _   | 120 | _   | µA/MHz |

| abled                                                                  |                     | 72 MHz HFRCO, CPU running while loop from flash                       | _   | 120 | _   | µA/MHz |

|                                                                        |                     | 72 MHz HFRCO, CPU running<br>CoreMark loop from flash                 | _   | 140 | _   | µA/MHz |

|                                                                        |                     | 50 MHz crystal, CPU running while loop from flash                     | —   | 122 | _   | µA/MHz |

|                                                                        |                     | 48 MHz HFRCO, CPU running while loop from flash                       | _   | 122 | _   | µA/MHz |

|                                                                        |                     | 32 MHz HFRCO, CPU running while loop from flash                       | _   | 124 | _   | µA/MHz |

|                                                                        |                     | 26 MHz HFRCO, CPU running while loop from flash                       | _   | 126 | _   | µA/MHz |

|                                                                        |                     | 16 MHz HFRCO, CPU running while loop from flash                       | _   | 131 | _   | µA/MHz |

|                                                                        |                     | 1 MHz HFRCO, CPU running while loop from flash                        | —   | 315 | _   | µA/MHz |

| Current consumption in EM0 mode with all peripherals dis-              | IACTIVE_VS          | 19 MHz HFRCO, CPU running while loop from flash                       | —   | 107 | _   | µA/MHz |

| abled and voltage scaling enabled                                      |                     | 1 MHz HFRCO, CPU running while loop from flash                        | _   | 259 | _   | µA/MHz |

| Current consumption in EM1                                             | IEM1                | 72 MHz HFRCO                                                          | _   | 57  |     | µA/MHz |

| mode with all peripherals disabled                                     |                     | 50 MHz crystal                                                        | _   | 59  |     | µA/MHz |

|                                                                        |                     | 48 MHz HFRCO                                                          | _   | 59  |     | µA/MHz |

|                                                                        |                     | 32 MHz HFRCO                                                          | _   | 61  |     | µA/MHz |

|                                                                        |                     | 26 MHz HFRCO                                                          | _   | 63  |     | µA/MHz |

|                                                                        |                     | 16 MHz HFRCO                                                          | _   | 68  | _   | µA/MHz |

|                                                                        |                     | 1 MHz HFRCO                                                           | _   | 252 |     | µA/MHz |

| Current consumption in EM1                                             | I <sub>EM1_VS</sub> | 19 MHz HFRCO                                                          | _   | 55  |     | µA/MHz |

| mode with all peripherals dis-<br>abled and voltage scaling<br>enabled |                     | 1 MHz HFRCO                                                           | _   | 207 | _   | µA/MHz |

| Current consumption in EM2 mode, with voltage scaling                  | I <sub>EM2_VS</sub> | Full 512 kB RAM retention and RTCC running from LFXO                  | _   | 3.7 | _   | μΑ     |

| enabled                                                                |                     | Full 512 kB RAM retention and RTCC running from LFRCO                 | _   | 4.0 | _   | μΑ     |

|                                                                        |                     | 16 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup> | —   | 2.5 | _   | μΑ     |

| Parameter                                 | Symbol                 | Test Condition                                             | Min | Тур      | Мах | Unit |

|-------------------------------------------|------------------------|------------------------------------------------------------|-----|----------|-----|------|

| Hysteresis (V <sub>CM</sub> = 1.25 V,     | V <sub>ACMPHYST</sub>  | HYSTSEL <sup>5</sup> = HYST0                               | TBD | 0        | TBD | mV   |

| $BIASPROG^4 = 0x10, FULL-BIAS^4 = 1)$     |                        | HYSTSEL <sup>5</sup> = HYST1                               | TBD | 18       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST2                               | TBD | 33       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST3                               | TBD | 46       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST4                               | TBD | 57       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST5                               | TBD | 68       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST6                               | TBD | 79       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST7                               | TBD | 90       | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST8                               | TBD | 0        | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST9                               | TBD | -18      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST10                              | TBD | -33      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST11                              | TBD | -45      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST12                              | TBD | -57      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST13                              | TBD | -67      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST14                              | TBD | -78      | TBD | mV   |

|                                           |                        | HYSTSEL <sup>5</sup> = HYST15                              | TBD | -88      | TBD | mV   |

| Comparator delay <sup>3</sup>             | t <sub>ACMPDELAY</sub> | $BIASPROG^4 = 1$ , $FULLBIAS^4 = 0$                        | _   | 30       | _   | μs   |

|                                           |                        | $BIASPROG^4 = 0x10, FULLBIAS^4 = 0$                        |     | 3.7      | _   | μs   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x02, FULLBIAS <sup>4</sup><br>= 1 |     | 360      | _   | ns   |

|                                           |                        | BIASPROG <sup>4</sup> = 0x20, FULLBIAS <sup>4</sup><br>= 1 | _   | 35       | _   | ns   |

| Offset voltage                            | VACMPOFFSET            | BIASPROG <sup>4</sup> =0x10, FULLBIAS <sup>4</sup><br>= 1  | TBD | _        | TBD | mV   |

| Reference voltage                         | V <sub>ACMPREF</sub>   | Internal 1.25 V reference                                  | TBD | 1.25     | TBD | V    |

|                                           |                        | Internal 2.5 V reference                                   | TBD | 2.5      | TBD | V    |

| Capacitive sense internal re-<br>sistance | R <sub>CSRES</sub>     | CSRESSEL <sup>6</sup> = 0                                  | _   | infinite | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 1                                  |     | 15       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 2                                  | —   | 27       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 3                                  | —   | 39       | _   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 4                                  | —   | 51       |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 5                                  | —   | 100      |     | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 6                                  | —   | 162      | -   | kΩ   |

|                                           |                        | CSRESSEL <sup>6</sup> = 7                                  | —   | 235      | -   | kΩ   |

# 4.1.16 Digital to Analog Converter (VDAC)

DRIVESTRENGTH = 2 unless otherwise specified. Primary VDAC output.

| Table 4.24. | Digital to | Analog | Converter | (VDAC) |

|-------------|------------|--------|-----------|--------|

|-------------|------------|--------|-----------|--------|

| Parameter                                                               | Symbol                  | Test Condition                                                                                                                                                                 | Min                | Тур  | Max               | Unit   |

|-------------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------------------|--------|

| Output voltage                                                          | V <sub>DACOUT</sub>     | Single-Ended                                                                                                                                                                   | 0                  | _    | V <sub>VREF</sub> | V      |

|                                                                         |                         | Differential <sup>2</sup>                                                                                                                                                      | -V <sub>VREF</sub> | _    | V <sub>VREF</sub> | V      |

| Current consumption includ-<br>ing references (2 channels) <sup>1</sup> | IDAC                    | 500 ksps, 12-bit, DRIVES-<br>TRENGTH = 2, REFSEL = 4                                                                                                                           | _                  | 402  | _                 | μA     |

|                                                                         |                         | 44.1 ksps, 12-bit, DRIVES-<br>TRENGTH = 1, REFSEL = 4                                                                                                                          | —                  | 88   | -                 | μA     |

|                                                                         |                         | 200 Hz refresh rate, 12-bit Sam-<br>ple-Off mode in EM2, DRIVES-<br>TRENGTH = 2, BGRREQTIME =<br>1, EM2REFENTIME = 9, REFSEL<br>= 4, SETTLETIME = 0x0A, WAR-<br>MUPTIME = 0x02 |                    | 2    | _                 | μΑ     |

| Current from HFPERCLK <sup>4</sup>                                      | IDAC_CLK                |                                                                                                                                                                                | —                  | 5.25 | _                 | µA/MHz |

| Sample rate                                                             | SR <sub>DAC</sub>       |                                                                                                                                                                                | —                  | _    | 500               | ksps   |

| DAC clock frequency                                                     | f <sub>DAC</sub>        |                                                                                                                                                                                | _                  | _    | 1                 | MHz    |

| Conversion time                                                         | t <sub>DACCONV</sub>    | f <sub>DAC</sub> = 1MHz                                                                                                                                                        | 2                  | _    | _                 | μs     |

| Settling time                                                           | t <sub>DACSETTLE</sub>  | 50% fs step settling to 5 LSB                                                                                                                                                  | —                  | 2.5  | —                 | μs     |

| Startup time                                                            | t <sub>DACSTARTUP</sub> | Enable to 90% fs output, settling to 10 LSB                                                                                                                                    | _                  | _    | 12                | μs     |

| Output impedance                                                        | R <sub>OUT</sub>        | $\label{eq:DRIVESTRENGTH} \begin{array}{l} DRIVESTRENGTH = 2,0.4V \leq \\ V_{OUT} \leq V_{OPA} - 0.4V,-8mA < \\ I_{OUT} < 8mA,Full supply range \end{array}$                   | _                  | 2    | _                 | Ω      |

|                                                                         |                         | DRIVESTRENGTH = 0 or 1, 0.4 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.4 V, -400 µA $<$<br>I <sub>OUT</sub> $<$ 400 µA, Full supply range                        | _                  | 2    | _                 | Ω      |

|                                                                         |                         | $\label{eq:DRIVESTRENGTH} \begin{array}{l} DRIVESTRENGTH = 2, 0.1 V \leq \\ V_{OUT} \leq V_{OPA} - 0.1 V, -2 mA < \\ I_{OUT} < 2 mA, Full \text{ supply range} \end{array}$    | _                  | 2    | _                 | Ω      |

|                                                                         |                         | DRIVESTRENGTH = 0 or 1, 0.1 V<br>$\leq$ V <sub>OUT</sub> $\leq$ V <sub>OPA</sub> - 0.1 V, -100 µA $<$<br>I <sub>OUT</sub> $<$ 100 µA, Full supply range                        | _                  | 2    | -                 | Ω      |

| Power supply rejection ratio <sup>6</sup>                               | PSRR                    | Vout = 50% fs. DC                                                                                                                                                              | _                  | 65.5 | _                 | dB     |

# 4.1.17 Current Digital to Analog Converter (IDAC)

| Parameter                                   | Symbol                   | Test Condition                                                                      | Min  | Тур  | Max | Unit   |

|---------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|------|------|-----|--------|

| Number of ranges                            | N <sub>IDAC_RANGES</sub> |                                                                                     | _    | 4    | _   | ranges |

| Output current                              | I <sub>IDAC_OUT</sub>    | RANGSEL <sup>1</sup> = RANGE0                                                       | 0.05 | _    | 1.6 | μA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE1                                                       | 1.6  | _    | 4.7 | μA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE2                                                       | 0.5  | _    | 16  | μA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE3                                                       | 2    | _    | 64  | μA     |

| Linear steps within each range              | N <sub>IDAC_STEPS</sub>  |                                                                                     | _    | 32   | _   | steps  |

| Step size                                   | SS <sub>IDAC</sub>       | RANGSEL <sup>1</sup> = RANGE0                                                       | _    | 50   | _   | nA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE1                                                       | _    | 100  | _   | nA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE2                                                       | _    | 500  | _   | nA     |

|                                             |                          | RANGSEL <sup>1</sup> = RANGE3                                                       | _    | 2    | _   | μA     |

| Total accuracy, STEPSEL <sup>1</sup> = 0x10 | ACCIDAC                  | EM0 or EM1, AVDD=3.3 V, T = 25<br>°C                                                | TBD  | _    | TBD | %      |

|                                             |                          | EM0 or EM1, Across operating temperature range                                      | TBD  | _    | TBD | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE0,<br>AVDD=3.3 V, T = 25 °C | _    | -2.7 | _   | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE1,<br>AVDD=3.3 V, T = 25 °C | _    | -2.5 | _   | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE2,<br>AVDD=3.3 V, T = 25 °C | _    | -1.5 | _   | %      |

|                                             |                          | EM2 or EM3, Source mode,<br>RANGSEL <sup>1</sup> = RANGE3,<br>AVDD=3.3 V, T = 25 °C | _    | -1.0 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE0, AVDD=3.3 V, T<br>= 25 °C | _    | -1.1 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE1, AVDD=3.3 V, T<br>= 25 °C | _    | -1.1 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE2, AVDD=3.3 V, T<br>= 25 °C | _    | -0.9 | _   | %      |

|                                             |                          | EM2 or EM3, Sink mode, RANG-<br>SEL <sup>1</sup> = RANGE3, AVDD=3.3 V, T<br>= 25 °C | _    | -0.9 | -   | %      |

# Table 4.25. Current Digital to Analog Converter (IDAC)

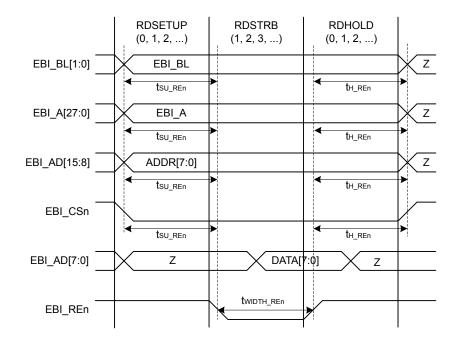

Figure 4.5. EBI Read Enable Output Timing Diagram

# SDIO MMC DDR Mode Timing at 1.8 V

Timing is specified for route location 0 at 1.8 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 25 pF on all pins.

| Parameter                                     | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|-----------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer          | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    | _    | 18  | MHz  |

|                                               |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 25.1 | —    |     | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                               | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 25.1 |      |     | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                               | t <sub>R</sub>      |                                   | 1.13 | 5.21 | _   | ns   |

| Clock fall time                               | t <sub>F</sub>      |                                   | 1.01 | 4.10 | _   | ns   |

| Input setup time, CMD valid to SD_CLK         | t <sub>ISU</sub>    |                                   | 5.3  |      |     | ns   |

| Input hold time, SD_CLK to CMD change         | t <sub>IH</sub>     |                                   | 2.5  |      | _   | ns   |

| Output delay time, SD_CLK to CMD valid        | t <sub>ODLY</sub>   |                                   | 0    |      | 16  | ns   |

| Output hold time, SD_CLK to CMD change        | t <sub>OH</sub>     |                                   | 3    |      |     | ns   |

| Input setup time, DAT[0:7]<br>valid to SD_CLK | t <sub>ISU2X</sub>  |                                   | 5.3  |      |     | ns   |

| Input hold time, SD_CLK to DAT[0:7] change    | t <sub>IH2X</sub>   |                                   | 2.5  |      |     | ns   |

| Output delay time, SD_CLK to DAT[0:7] valid   | t <sub>ODLY2X</sub> |                                   | 0    | _    | 16  | ns   |

| Output hold time, SD_CLK to DAT[0:7] change   | t <sub>OH2X</sub>   |                                   | 3    | —    | —   | ns   |

# Table 4.52. SDIO MMC DDR Mode Timing (Location 0, 1.8V I/O)

# 4.2.1 Supply Current

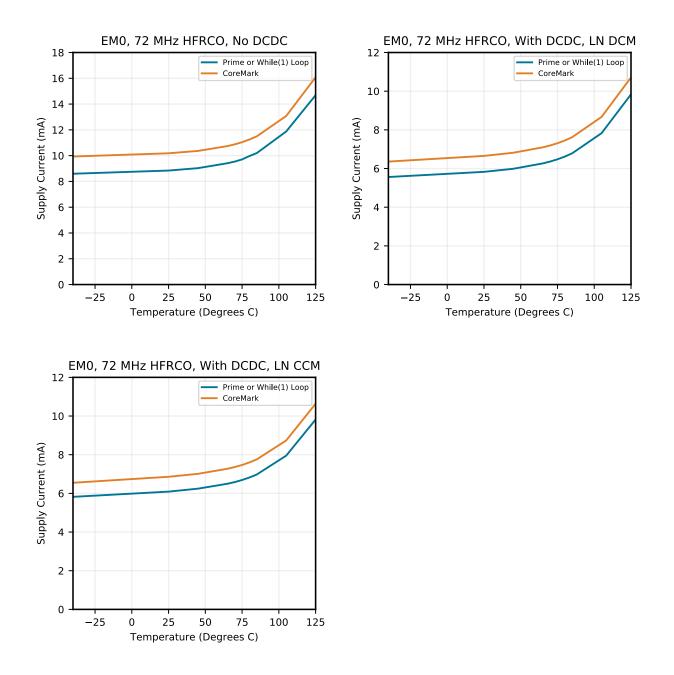

Figure 4.23. EM0 Full Speed Active Mode Typical Supply Current vs. Temperature

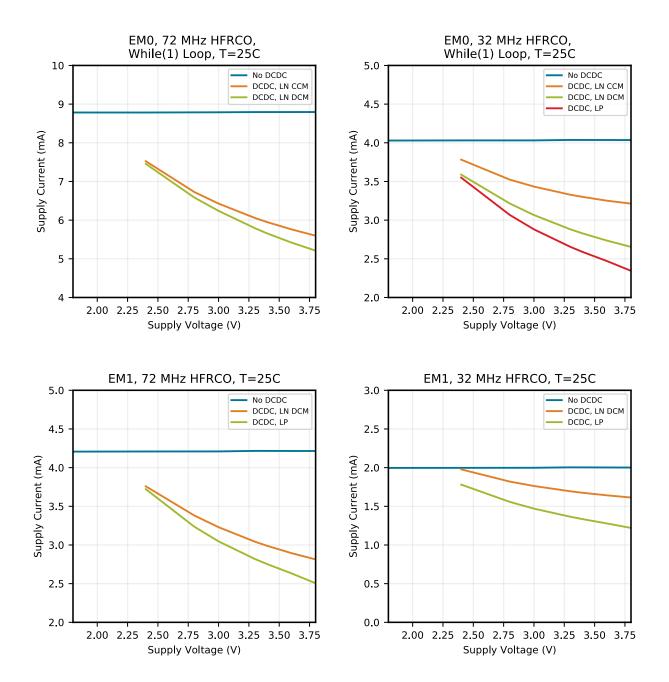

Figure 4.27. EM0 and EM1 Mode Typical Supply Current vs. Supply

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

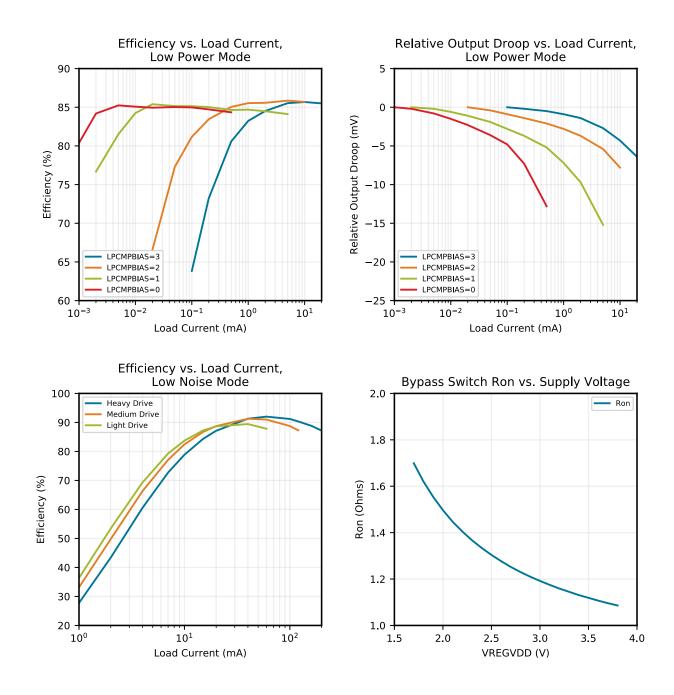

## 4.2.2 DC-DC Converter

Default test conditions: CCM mode, LDCDC = 4.7 µH, CDCDC = 4.7 µF, VDCDC\_I = 3.3 V, VDCDC\_O = 1.8 V, FDCDC\_LN = 7 MHz

Figure 4.29. DC-DC Converter Typical Performance Characteristics

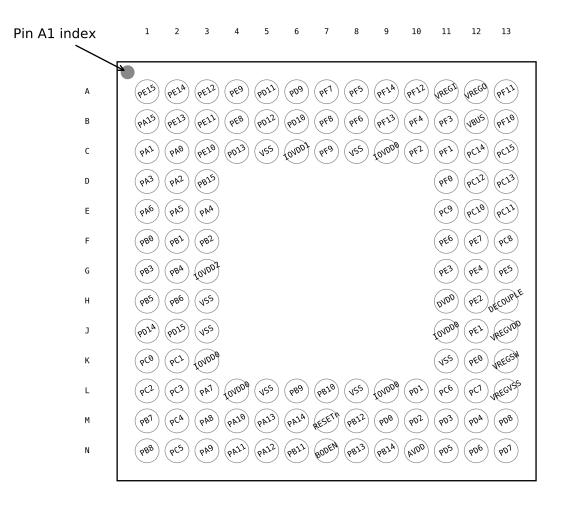

### Figure 5.3. EFM32GG11B8xx in BGA120 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Table 5.3. EFM32GG11B8xx in BGA120 Device Pinout |

|--------------------------------------------------|

|--------------------------------------------------|

| Pin Name | Pin(s) | Description             | Pin Name | Pin(s) | Description                                                                                      |

|----------|--------|-------------------------|----------|--------|--------------------------------------------------------------------------------------------------|

| PE15     | A1     | GPIO                    | PE14     | A2     | GPIO                                                                                             |

| PE12     | A3     | GPIO                    | PE9      | A4     | GPIO                                                                                             |

| PD11     | A5     | GPIO                    | PD9      | A6     | GPIO                                                                                             |

| PF7      | A7     | GPIO                    | PF5      | A8     | GPIO                                                                                             |

| PF14     | A9     | GPIO (5V)               | PF12     | A10    | GPIO                                                                                             |

| VREGI    | A11    | Input to 5 V regulator. | VREGO    | A12    | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs |

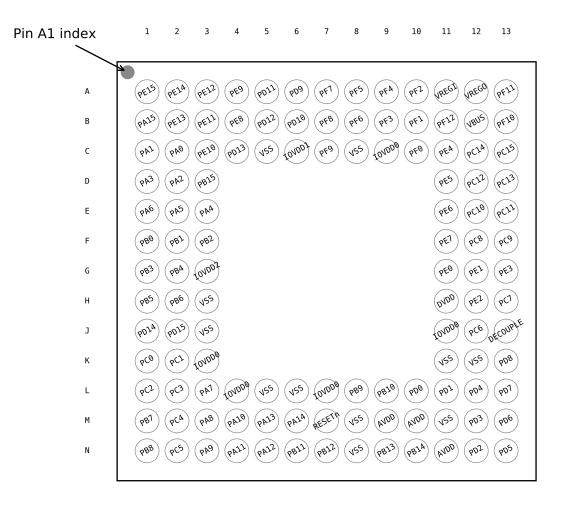

### Figure 5.5. EFM32GG11B4xx in BGA120 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s) | Description             | Pin Name | Pin(s) | Description                                                                                      |

|----------|--------|-------------------------|----------|--------|--------------------------------------------------------------------------------------------------|

| PE15     | A1     | GPIO                    | PE14     | A2     | GPIO                                                                                             |

| PE12     | A3     | GPIO                    | PE9      | A4     | GPIO                                                                                             |

| PD11     | A5     | GPIO                    | PD9      | A6     | GPIO                                                                                             |

| PF7      | A7     | GPIO                    | PF5      | A8     | GPIO                                                                                             |

| PF4      | A9     | GPIO                    | PF2      | A10    | GPIO                                                                                             |

| VREGI    | A11    | Input to 5 V regulator. | VREGO    | A12    | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs |

| Pin Name | Pin(s) | Description                                                                                              | Pin Name | Pin(s)   | Description                                                                                                                                                                                                 |  |

|----------|--------|----------------------------------------------------------------------------------------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PC4      | 13     | GPIO                                                                                                     | PC5      | 14       | GPIO                                                                                                                                                                                                        |  |

| PB7      | 15     | GPIO                                                                                                     | PB8      | 16       | GPIO                                                                                                                                                                                                        |  |

| PA12     | 17     | GPIO (5V)                                                                                                | PA13     | 18       | GPIO (5V)                                                                                                                                                                                                   |  |

| PA14     | 19     | GPIO                                                                                                     | RESETn   | 20       | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |  |

| PB11     | 21     | GPIO                                                                                                     | AVDD     | 23<br>27 | Analog power supply.                                                                                                                                                                                        |  |

| PB13     | 24     | GPIO                                                                                                     | PB14     | 25       | GPIO                                                                                                                                                                                                        |  |

| PD0      | 28     | GPIO (5V)                                                                                                | PD1      | 29       | GPIO                                                                                                                                                                                                        |  |

| PD2      | 30     | GPIO (5V)                                                                                                | PD3      | 31       | GPIO                                                                                                                                                                                                        |  |

| PD4      | 32     | GPIO                                                                                                     | PD5      | 33       | GPIO                                                                                                                                                                                                        |  |

| PD6      | 34     | GPIO                                                                                                     | PD7      | 35       | GPIO                                                                                                                                                                                                        |  |

| PD8      | 36     | GPIO                                                                                                     | PC6      | 37       | GPIO                                                                                                                                                                                                        |  |

| PC7      | 38     | GPIO                                                                                                     | DVDD     | 39       | Digital power supply.                                                                                                                                                                                       |  |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin. | PE4      | 41       | GPIO                                                                                                                                                                                                        |  |

| PE5      | 42     | GPIO                                                                                                     | PE6      | 43       | GPIO                                                                                                                                                                                                        |  |

| PE7      | 44     | GPIO                                                                                                     | VREGI    | 45       | Input to 5 V regulator.                                                                                                                                                                                     |  |

| VREGO    | 46     | Decoupling for 5 V regulator and regu-<br>lator output. Power for USB PHY in<br>USB-enabled OPNs         | PF10     | 47       | GPIO (5V)                                                                                                                                                                                                   |  |

| PF11     | 48     | GPIO (5V)                                                                                                | PF0      | 49       | GPIO (5V)                                                                                                                                                                                                   |  |

| PF1      | 50     | GPIO (5V)                                                                                                | PF2      | 51       | GPIO                                                                                                                                                                                                        |  |

| VBUS     | 52     | USB VBUS signal and auxiliary input to 5 V regulator.                                                    | PF12     | 53       | GPIO                                                                                                                                                                                                        |  |

| PF5      | 54     | GPIO                                                                                                     | PE8      | 57       | GPIO                                                                                                                                                                                                        |  |

| PE9      | 58     | GPIO                                                                                                     | PE10     | 59       | GPIO                                                                                                                                                                                                        |  |

| PE11     | 60     | GPIO                                                                                                     | PE12     | 61       | GPIO                                                                                                                                                                                                        |  |

| PE13     | 62     | GPIO                                                                                                     | PE14     | 63       | GPIO                                                                                                                                                                                                        |  |

| PE15     | 64     | GPIO                                                                                                     |          |          |                                                                                                                                                                                                             |  |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate     | LOCA                                   | TION  |                                   |

|---------------|----------------------------------------|-------|-----------------------------------|

| Functionality | 0 - 3                                  | 4 - 7 | Description                       |

| ETH_MDIO      | 0: PB3<br>1: PD13<br>2: PC0<br>3: PA15 |       | Ethernet Management Data I/O.     |

| ETH_MIICOL    | 0: PB2<br>1: PG15<br>2: PB4            |       | Ethernet MII Collision Detect.    |

| ETH_MIICRS    | 0: PB1<br>1: PG14<br>2: PB3            |       | Ethernet MII Carrier Sense.       |

| ETH_MIIRXCLK  | 0: PA15<br>1: PG7<br>2: PD12           |       | Ethernet MII Receive Clock.       |

| ETH_MIIRXD0   | 0: PE12<br>1: PG11<br>2: PF9           |       | Ethernet MII Receive Data Bit 0.  |

| ETH_MIIRXD1   | 0: PE13<br>1: PG10<br>2: PD9           |       | Ethernet MII Receive Data Bit 1.  |

| ETH_MIIRXD2   | 0: PE14<br>1: PG9<br>2: PD10           |       | Ethernet MII Receive Data Bit 2.  |

| ETH_MIIRXD3   | 0: PE15<br>1: PG8<br>2: PD11           |       | Ethernet MII Receive Data Bit 3.  |

| ETH_MIIRXDV   | 0: PE11<br>1: PG12<br>2: PF8           |       | Ethernet MII Receive Data Valid.  |

| ETH_MIIRXER   | 0: PE10<br>1: PG13<br>2: PF7           |       | Ethernet MII Receive Error.       |

| ETH_MIITXCLK  | 0: PA0<br>1: PG0                       |       | Ethernet MII Transmit Clock.      |

| ETH_MIITXD0   | 0: PA4<br>1: PG4                       |       | Ethernet MII Transmit Data Bit 0. |

| ETH_MIITXD1   | 0: PA3<br>1: PG3                       |       | Ethernet MII Transmit Data Bit 1. |

| Alternate LOCA <sup>-</sup> |                                         | ATION                                  |                                                      |  |  |

|-----------------------------|-----------------------------------------|----------------------------------------|------------------------------------------------------|--|--|

| Functionality               | 0 - 3                                   | 4 - 7                                  | Description                                          |  |  |

| SDIO_DAT7                   | 0: PD9<br>1: PB4                        |                                        | SDIO Data 7.                                         |  |  |

| SDIO_WP                     | 0: PF9<br>1: PC5<br>2: PB15<br>3: PB9   |                                        | SDIO Write Protect.                                  |  |  |

| TIM0_CC0                    | 0: PA0<br>1: PF6<br>2: PD1<br>3: PB6    | 4: PF0<br>5: PC4<br>6: PA8<br>7: PA1   | Timer 0 Capture Compare input / output channel 0.    |  |  |

| TIM0_CC1                    | 0: PA1<br>1: PF7<br>2: PD2<br>3: PC0    | 4: PF1<br>5: PC5<br>6: PA9<br>7: PA0   | Timer 0 Capture Compare input / output channel 1.    |  |  |

| TIM0_CC2                    | 0: PA2<br>1: PF8<br>2: PD3<br>3: PC1    | 4: PF2<br>5: PA7<br>6: PA10<br>7: PA13 | Timer 0 Capture Compare input / output channel 2.    |  |  |

| TIM0_CDTI0                  | 0: PA3<br>1: PC13<br>2: PF3<br>3: PC2   | 4: PB7                                 | Timer 0 Complimentary Dead Time Insertion channel 0. |  |  |

| TIM0_CDTI1                  | 0: PA4<br>1: PC14<br>2: PF4<br>3: PC3   | 4: PB8                                 | Timer 0 Complimentary Dead Time Insertion channel 1. |  |  |

| TIM0_CDTI2                  | 0: PA5<br>1: PC15<br>2: PF5<br>3: PC4   | 4: PB11                                | Timer 0 Complimentary Dead Time Insertion channel 2. |  |  |

| TIM1_CC0                    | 0: PC13<br>1: PE10<br>2: PB0<br>3: PB7  | 4: PD6<br>5: PF2<br>6: PF13<br>7: PI6  | Timer 1 Capture Compare input / output channel 0.    |  |  |

| TIM1_CC1                    | 0: PC14<br>1: PE11<br>2: PB1<br>3: PB8  | 4: PD7<br>5: PF3<br>6: PF14<br>7: PI7  | Timer 1 Capture Compare input / output channel 1.    |  |  |

| TIM1_CC2                    | 0: PC15<br>1: PE12<br>2: PB2<br>3: PB11 | 4: PC13<br>5: PF4<br>6: PF15<br>7: PI8 | Timer 1 Capture Compare input / output channel 2.    |  |  |

| TIM1_CC3                    | 0: PC12<br>1: PE13<br>2: PB3<br>3: PB12 | 4: PC14<br>5: PF12<br>6: PF5<br>7: PI9 | Timer 1 Capture Compare input / output channel 3.    |  |  |

| TIM2_CC0                    | 0: PA8<br>1: PA12<br>2: PC8<br>3: PF2   | 4: PB6<br>5: PC2<br>6: PG8<br>7: PG5   | Timer 2 Capture Compare input / output channel 0.    |  |  |

| Alternate LOCATION |                                          | ATION                                  |                                                      |  |  |

|--------------------|------------------------------------------|----------------------------------------|------------------------------------------------------|--|--|

| Functionality      | 0 - 3                                    | 4 - 7                                  | Description                                          |  |  |

| TIM2_CC1           | 0: PA9<br>1: PA13<br>2: PC9<br>3: PE12   | 4: PC0<br>5: PC3<br>6: PG9<br>7: PG6   | Timer 2 Capture Compare input / output channel 1.    |  |  |

| TIM2_CC2           | 0: PA10<br>1: PA14<br>2: PC10<br>3: PE13 | 4: PC1<br>5: PC4<br>6: PG10<br>7: PG7  | Timer 2 Capture Compare input / output channel 2.    |  |  |

| TIM2_CDTI0         | 0: PB0<br>1: PD13<br>2: PE8<br>3: PG0    |                                        | Timer 2 Complimentary Dead Time Insertion channel 0. |  |  |

| TIM2_CDTI1         | 0: PB1<br>1: PD14<br>2: PE14<br>3: PG1   |                                        | Timer 2 Complimentary Dead Time Insertion channel 1. |  |  |

| TIM2_CDTI2         | 0: PB2<br>1: PD15<br>2: PE15<br>3: PG2   |                                        | Timer 2 Complimentary Dead Time Insertion channel 2. |  |  |

| TIM3_CC0           | 0: PE14<br>1: PE0<br>2: PE3<br>3: PE5    | 4: PA0<br>5: PA3<br>6: PA6<br>7: PD15  | Timer 3 Capture Compare input / output channel 0.    |  |  |

| TIM3_CC1           | 0: PE15<br>1: PE1<br>2: PE4<br>3: PE6    | 4: PA1<br>5: PA4<br>6: PD13<br>7: PB15 | Timer 3 Capture Compare input / output channel 1.    |  |  |

| TIM3_CC2           | 0: PA15<br>1: PE2<br>2: PE5<br>3: PE7    | 4: PA2<br>5: PA5<br>6: PD14<br>7: PB0  | Timer 3 Capture Compare input / output channel 2.    |  |  |

| TIM4_CC0           | 0: PF3<br>1: PF13<br>2: PF5<br>3: PI8    | 4: PF6<br>5: PF9<br>6: PD11<br>7: PE9  | Timer 4 Capture Compare input / output channel 0.    |  |  |

| TIM4_CC1           | 0: PF4<br>1: PF14<br>2: PI6<br>3: PI9    | 4: PF7<br>5: PD9<br>6: PD12<br>7: PE10 | Timer 4 Capture Compare input / output channel 1.    |  |  |

| TIM4_CC2           | 0: PF12<br>1: PF15<br>2: PI7<br>3: PI10  | 4: PF8<br>5: PD10<br>6: PE8<br>7: PE11 | Timer 4 Capture Compare input / output channel 2.    |  |  |

| TIM4_CDTI0         | 0: PD0                                   |                                        | Timer 4 Complimentary Dead Time Insertion channel 0. |  |  |

| TIM4_CDTI1         | 0: PD1                                   |                                        | Timer 4 Complimentary Dead Time Insertion channel 1. |  |  |

| Alternate     | LOCA                                     | ATION                                  |                                                           |  |  |

|---------------|------------------------------------------|----------------------------------------|-----------------------------------------------------------|--|--|

| Functionality | 0 - 3                                    | 4 - 7                                  | Description                                               |  |  |

| WTIM0_CC2     | 0: PE6<br>1: PD14<br>2: PG4<br>3: PG10   | 4: PF1<br>5: PB2<br>6: PB5<br>7: PC3   | Wide timer 0 Capture Compare input / output channel 2.    |  |  |

| WTIM0_CDTI0   | 0: PE10<br>1: PD15<br>2: PA12<br>3: PG11 | 4: PD4                                 | Wide timer 0 Complimentary Dead Time Insertion channel 0. |  |  |

| WTIM0_CDTI1   | 0: PE11<br>1: PG0<br>2: PA13<br>3: PG12  | 4: PD5                                 | Wide timer 0 Complimentary Dead Time Insertion channel 1. |  |  |

| WTIM0_CDTI2   | 0: PE12<br>1: PG1<br>2: PA14<br>3: PG13  | 4: PD6                                 | Wide timer 0 Complimentary Dead Time Insertion channel 2. |  |  |

| WTIM1_CC0     | 0: PB13<br>1: PD2<br>2: PD6<br>3: PC7    | 4: PE3<br>5: PE7<br>6: PH8<br>7: PH12  | Wide timer 1 Capture Compare input / output channel 0.    |  |  |

| WTIM1_CC1     | 0: PB14<br>1: PD3<br>2: PD7<br>3: PE0    | 4: PE4<br>5: PI0<br>6: PH9<br>7: PH13  | Wide timer 1 Capture Compare input / output channel 1.    |  |  |

| WTIM1_CC2     | 0: PD0<br>1: PD4<br>2: PD8<br>3: PE1     | 4: PE5<br>5: PI1<br>6: PH10<br>7: PH14 | Wide timer 1 Capture Compare input / output channel 2.    |  |  |

| WTIM1_CC3     | 0: PD1<br>1: PD5<br>2: PC6<br>3: PE2     | 4: PE6<br>5: PI2<br>6: PH11<br>7: PH15 | Wide timer 1 Capture Compare input / output channel 3.    |  |  |

| WTIM2_CC0     | 0: PA9<br>1: PA12<br>2: PB9<br>3: PB12   | 4: PG14<br>5: PD3<br>6: PH4<br>7: PH7  | Wide timer 2 Capture Compare input / output channel 0.    |  |  |

| WTIM2_CC1     | 0: PA10<br>1: PA13<br>2: PB10<br>3: PG12 | 4: PG15<br>5: PD4<br>6: PH5<br>7: PH8  | Wide timer 2 Capture Compare input / output channel 1.    |  |  |

| WTIM2_CC2     | 0: PA11<br>1: PA14<br>2: PB11<br>3: PG13 | 4: PH0<br>5: PD5<br>6: PH6<br>7: PH9   | Wide timer 2 Capture Compare input / output channel 2.    |  |  |

| WTIM3_CC0     | 0: PD9<br>1: PC8<br>2: PC11<br>3: PC14   | 4: PI3<br>5: PI6<br>6: PB6<br>7: PF13  | Wide timer 3 Capture Compare input / output channel 0.    |  |  |

| WTIM3_CC1     | 0: PD10<br>1: PC9<br>2: PC12<br>3: PF10  | 4: PI4<br>5: PI7<br>6: PF4<br>7: PF14  | Wide timer 3 Capture Compare input / output channel 1.    |  |  |

| Dimension | Min            | Тур      | Мах  |  |  |  |  |

|-----------|----------------|----------|------|--|--|--|--|

| A         | 0.77           | 0.83     | 0.89 |  |  |  |  |

| A1        | 0.13           | 0.18     | 0.23 |  |  |  |  |

| A3        | 0.16 0.20 0.24 |          |      |  |  |  |  |

| A2        | 0.45 REF       |          |      |  |  |  |  |

| D         | 7.00 BSC       |          |      |  |  |  |  |

| е         |                | 0.40 BSC |      |  |  |  |  |

| E         | 7.00 BSC       |          |      |  |  |  |  |

| D1        | 6.00 BSC       |          |      |  |  |  |  |

| E1        | 6.00 BSC       |          |      |  |  |  |  |

| b         | 0.20 0.25 0.30 |          |      |  |  |  |  |

| ааа       | 0.10           |          |      |  |  |  |  |

| bbb       | 0.10           |          |      |  |  |  |  |

| ddd       | 0.08           |          |      |  |  |  |  |

| eee       | 0.15           |          |      |  |  |  |  |

| fff       | 0.05           |          |      |  |  |  |  |

| Noto      |                |          |      |  |  |  |  |

## Table 6.1. BGA192 Package Dimensions

# Note:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.