Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                                      |

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 144                                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 192-VFBGA                                                                                                     |

| Supplier Device Package    | 192-BGA (7x7)                                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b820f2048gl192-ar                                  |

|                            |                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 5. | Pin Definitions                            | 115  |

|----|--------------------------------------------|------|

|    | 5.1 EFM32GG11B8xx in BGA192 Device Pinout  | .115 |

|    | 5.2 EFM32GG11B8xx in BGA152 Device Pinout  | .119 |

|    | 5.3 EFM32GG11B8xx in BGA120 Device Pinout  | .123 |

|    | 5.4 EFM32GG11B5xx in BGA120 Device Pinout  | .126 |

|    | 5.5 EFM32GG11B4xx in BGA120 Device Pinout  | 129  |

|    | 5.6 EFM32GG11B4xx in BGA112 Device Pinout  | .132 |

|    | 5.7 EFM32GG11B3xx in BGA112 Device Pinout  | .135 |

|    | 5.8 EFM32GG11B8xx in QFP100 Device Pinout  | 138  |

|    | 5.9 EFM32GG11B5xx in QFP100 Device Pinout  | 141  |

|    | 5.10 EFM32GG11B4xx in QFP100 Device Pinout | 144  |

|    | 5.11 EFM32GG11B3xx in QFP100 Device Pinout | 147  |

|    | 5.12 EFM32GG11B8xx in QFP64 Device Pinout  | 150  |

|    | 5.13 EFM32GG11B5xx in QFP64 Device Pinout  | 152  |

|    | 5.14 EFM32GG11B4xx in QFP64 Device Pinout  | 154  |

|    | 5.15 EFM32GG11B1xx in QFP64 Device Pinout  | 156  |

|    | 5.16 EFM32GG11B8xx in QFN64 Device Pinout  | 158  |

|    | 5.17 EFM32GG11B5xx in QFN64 Device Pinout  | .160 |

|    | 5.18 EFM32GG11B4xx in QFN64 Device Pinout  | .162 |

|    | 5.19 EFM32GG11B1xx in QFN64 Device Pinout  | 164  |

|    | 5.20 GPIO Functionality Table              | 166  |

|    | 5.21 Alternate Functionality Overview      | 178  |

|    | 5.22 Analog Port (APORT) Client Maps       | 211  |

| 6. | BGA192 Package Specifications              | 224  |

|    | 6.1 BGA192 Package Dimensions              | .224 |

|    | 6.2 BGA192 PCB Land Pattern                | 226  |

|    | 6.3 BGA192 Package Marking                 | 228  |

| 7. | BGA152 Package Specifications              | 229  |

|    | 7.1 BGA152 Package Dimensions              | .229 |

|    | 7.2 BGA152 PCB Land Pattern                | 231  |

|    | 7.3 BGA152 Package Marking                 | 233  |

| 8. | BGA120 Package Specifications              | 234  |

|    | 8.1 BGA120 Package Dimensions              | .234 |

|    |                                            | 236  |

|    |                                            | 238  |

| 9. | BGA112 Package Specifications              | 239  |

|    |                                            | .239 |

#### 3.2 Power

The EFM32GG11 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. A 5 V regulator is available on some OPNs, allowing the device to be powered directly from 5 V power sources, such as USB. An optional integrated DC-DC buck regulator can be utilized to further reduce the current consumption. The DC-DC regulator requires one external inductor and one external capacitor.

The EFM32GG11 device family includes support for internal supply voltage scaling, as well as two different power domain groups for peripherals. These enhancements allow for further supply current reductions and lower overall power consumption.

AVDD and VREGVDD need to be 1.8 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the DC-DC to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

#### 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

#### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

#### 3.2.3 5 V Regulator

A 5 V input regulator is available, allowing the device to be powered directly from 5 V power sources such as the USB VBUS line. The regulator is available in all energy modes, and outputs 3.3 V to be used to power the USB PHY and other 3.3 V systems. Two inputs to the regulator allow for seamless switching between local and external power sources.

## 4.1.10.3 Low-Frequency RC Oscillator (LFRCO)

| Parameter                        | Symbol             | Test Condition                     | Min | Тур    | Мах | Unit |

|----------------------------------|--------------------|------------------------------------|-----|--------|-----|------|

| Oscillation frequency            | f <sub>LFRCO</sub> | ENVREF <sup>2</sup> = 1            | TBD | 32.768 | TBD | kHz  |

|                                  |                    | ENVREF <sup>2</sup> = 1, T > 85 °C | TBD | 32.768 | TBD | kHz  |

|                                  |                    | ENVREF <sup>2</sup> = 0            | TBD | 32.768 | TBD | kHz  |

| Startup time                     | t <sub>LFRCO</sub> |                                    | _   | 500    | _   | μs   |

| Current consumption <sup>1</sup> | I <sub>LFRCO</sub> | ENVREF = 1 in<br>CMU_LFRCOCTRL     | _   | 370    | _   | nA   |

|                                  |                    | ENVREF = 0 in<br>CMU_LFRCOCTRL     | -   | 520    |     | nA   |

| Note:                            | 1                  | I.                                 | 1   | 1      | 1   | 1    |

# Table 4.14. Low-Frequency RC Oscillator (LFRCO)

1. Block is supplied by AVDD if ANASW = 0, or DVDD if ANASW=1 in EMU\_PWRCTRL register.

2. In CMU\_LFRCOCTRL register.

| Parameter                     | Symbol                                         | Test Condition                                                           | Min                   | Тур             | Max            | Unit      |

|-------------------------------|------------------------------------------------|--------------------------------------------------------------------------|-----------------------|-----------------|----------------|-----------|

| Note:                         |                                                |                                                                          | l                     |                 |                |           |

| 1. Supply current s the load. | specifications are for VD                      | AC circuitry operating with static o                                     | output only and do n  | not include cur | rent required  | to drive  |

|                               | ode, the output is define<br>ngle-ended range. | d as the difference between two s                                        | ingle-ended outputs   | s. Absolute vol | tage on each   | output is |

| 3. Entire range is r          | monotonic and has no m                         | issing codes.                                                            |                       |                 |                |           |

|                               | PERCLK is dependent<br>DAC module is enabled   | on HFPERCLK frequency. This cuint in the CMU.                            | urrent contributes to | the total supp  | ly current use | ed when   |

|                               | , U I                                          | be from 10% to 90% of full scale.<br>It 10% of full scale with the measu |                       | by comparing    | actual VDAC    | output a  |

|                               |                                                | ΔV <sub>OUT</sub> ), VDAC output at 90% of f                             |                       |                 |                |           |

## 4.1.18 Capacitive Sense (CSEN)

| Parameter                                                                           | Symbol              | Test Condition                                                                                                                                                   | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Single conversion time (1x                                                          | t <sub>CNV</sub>    | 12-bit SAR Conversions                                                                                                                                           | _   | 20.2 | _   | μs   |

| accumulation)                                                                       |                     | 16-bit SAR Conversions                                                                                                                                           | _   | 26.4 | _   | μs   |

|                                                                                     |                     | Delta Modulation Conversion (sin-<br>gle comparison)                                                                                                             | _   | 1.55 |     | μs   |

| Maximum external capacitive load                                                    | C <sub>EXTMAX</sub> | CS0CG=7 (Gain = 1x), including routing parasitics                                                                                                                | _   | 68   | -   | pF   |

|                                                                                     |                     | CS0CG=0 (Gain = 10x), including routing parasitics                                                                                                               | —   | 680  | _   | pF   |

| Maximum external series impedance                                                   | R <sub>EXTMAX</sub> |                                                                                                                                                                  | —   | 1    | -   | kΩ   |

| Supply current, EM2 bonded<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-<br>MUPCNT=0 | ICSEN_BOND          | 12-bit SAR conversions, 20 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                       | _   | 326  | _   | nA   |

|                                                                                     |                     | Delta Modulation conversions, 20<br>ms conversion rate, CS0CG=7<br>(Gain = 1x), 10 channels bonded<br>(total capacitance of 330 pF) <sup>1</sup>                 | _   | 226  | _   | nA   |

|                                                                                     |                     | 12-bit SAR conversions, 200 ms<br>conversion rate, CS0CG=7 (Gain<br>= 1x), 10 channels bonded (total<br>capacitance of 330 pF) <sup>1</sup>                      | —   | 33   | _   | nA   |

|                                                                                     |                     | Delta Modulation conversions,<br>200 ms conversion rate,<br>CS0CG=7 (Gain = 1x), 10 chan-<br>nels bonded (total capacitance of<br>330 pF) <sup>1</sup>           | _   | 25   | _   | nA   |

| Supply current, EM2 scan<br>conversions, WARMUP-<br>MODE=NORMAL, WAR-               | ICSEN_EM2           | 12-bit SAR conversions, 20 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                             | _   | 690  | _   | nA   |

| MUPCNT=0                                                                            |                     | Delta Modulation conversions, 20<br>ms scan rate, 8 comparisons per<br>sample (DMCR = 1, DMR = 2),<br>CS0CG=0 (Gain = 10x), 8 sam-<br>ples per scan <sup>1</sup> | _   | 515  | _   | nA   |

|                                                                                     |                     | 12-bit SAR conversions, 200 ms<br>scan rate, CS0CG=0 (Gain =<br>10x), 8 samples per scan <sup>1</sup>                                                            | _   | 79   | _   | nA   |

|                                                                                     |                     | Delta Modulation conversions,<br>200 ms scan rate, 8 comparisons<br>per sample (DMCR = 1, DMR =<br>2), CS0CG=0 (Gain = 10x), 8<br>samples per scan <sup>1</sup>  | _   | 57   | _   | nA   |

# Table 4.26. Capacitive Sense (CSEN)

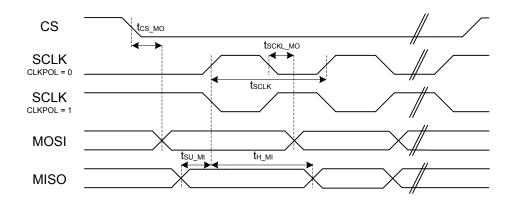

# 4.1.24 USART SPI

# SPI Master Timing

# Table 4.34. SPI Master Timing

| Parameter                      | Symbol             | Test Condition                                   | Min                           | Тур | Мах | Unit |

|--------------------------------|--------------------|--------------------------------------------------|-------------------------------|-----|-----|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>  | All USARTs except USART2                         | 2 *<br>t <sub>HFPERCLK</sub>  | _   | _   | ns   |

|                                |                    | USART2                                           | 2 *<br>t <sub>HFPERBCLK</sub> | _   | _   | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub> | USART2, location 4, IOVDD = 1.8<br>V             | -3.2                          | _   | 6.8 | ns   |

|                                |                    | USART2, location 4, IOVDD = 3.0<br>V             | -2.3                          | _   | 6.0 | ns   |

|                                |                    | USART2, location 5, IOVDD = 1.8<br>V             | -8.1                          | —   | 6.3 | ns   |

|                                |                    | USART2, location 5, IOVDD = 3.0<br>V             | -7.3                          | _   | 4.4 | ns   |

|                                |                    | All other USARTs and locations,<br>IOVDD = 1.8 V | -15                           | —   | 13  | ns   |

|                                |                    | All other USARTs and locations,<br>IOVDD = 3.0 V | -13                           | —   | 11  | ns   |

| SCLK to MOSI <sup>1 3</sup>    | tsclk_mo           | USART2, location 4, IOVDD = 1.8<br>V             | -0.3                          | _   | 9.2 | ns   |

|                                |                    | USART2, location 4, IOVDD = 3.0<br>V             | -0.3                          | —   | 8.6 | ns   |

|                                |                    | USART2, location 5, IOVDD = 1.8<br>V             | -3.6                          | —   | 5.0 | ns   |

|                                |                    | USART2, location 5, IOVDD = 3.0<br>V             | -3.4                          | _   | 3.2 | ns   |

|                                |                    | All other USARTs and locations,<br>IOVDD = 1.8 V | -10                           | _   | 11  | ns   |

|                                |                    | All other USARTs and locations,<br>IOVDD = 3.0 V | -9                            | _   | 11  | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>SU_MI</sub> | USART2, location 4, IOVDD = 1.8<br>V             | 39.7                          | —   | -   | ns   |

|                                |                    | USART2, location 4, IOVDD = 3.0<br>V             | 22.4                          | —   | -   | ns   |

|                                |                    | USART2, location 5, IOVDD = 1.8<br>V             | 49.2                          | _   | -   | ns   |

|                                |                    | USART2, location 5, IOVDD = 3.0<br>V             | 30.0                          | _   | _   | ns   |

|                                |                    | All other USARTs and locations,<br>IOVDD = 1.8 V | 55                            | _   | _   | ns   |

|                                |                    | All other USARTs and locations,<br>IOVDD = 3.0 V | 36                            | _   | -   | ns   |

| Parameter                     | Symbol            | Test Condition                                   | Min   | Тур | Max | Unit |

|-------------------------------|-------------------|--------------------------------------------------|-------|-----|-----|------|

| MISO hold time <sup>1 3</sup> | t <sub>H_MI</sub> | USART2, location 4, IOVDD = 1.8<br>V             | -11.6 | _   | —   | ns   |

|                               |                   | USART2, location 4, IOVDD = 3.0<br>V             | -11.6 | _   | —   | ns   |

|                               |                   | USART2, location 5, IOVDD = 1.8<br>V             | -9.1  | _   | _   | ns   |

|                               |                   | USART2, location 5, IOVDD = 3.0<br>V             | -9.1  | _   | _   | ns   |

|                               |                   | All other USARTs and locations,<br>IOVDD = 1.8 V | -8    |     | _   | ns   |

|                               |                   | All other USARTs and locations,<br>IOVDD = 3.0 V | -8    |     | _   | ns   |

Note:

1. Applies for both CLKPHA = 0 and CLKPHA = 1 (figure only shows CLKPHA = 0).

2.  $t_{\mbox{\scriptsize HFPERCLK}}$  is one period of the selected  $\mbox{\scriptsize HFPERCLK}.$

3. Measurement done with 8 pF output loading at 10% and 90% of  $V_{DD}$  (figure shows 50% of  $V_{DD}$ ).

Figure 4.1. SPI Master Timing Diagram

#### 4.1.25 External Bus Interface (EBI)

#### **EBI Write Enable Output Timing**

Timing applies to both EBI\_WEn and EBI\_NANDWEn for all addressing modes and both polarities. All numbers are based on route locations 0,1,2 only (with all EBI alternate functions using the same location at the same time). Timing is specified at 10% and 90% of IOVDD, 25 pF external loading, and slew rate for all GPIO set to 6.

## Table 4.36. EBI Write Enable Timing

| Parameter                                                                                                                    | Symbol              | Test Condition | Min                                                          | Тур | Мах | Unit |

|------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|--------------------------------------------------------------|-----|-----|------|

| Output hold time, from trail-<br>ing EBI_WEn / EBI_NAND-<br>WEn edge to EBI_AD,<br>EBI_A, EBI_CSn, EBI_BLn<br>invalid        | t <sub>OH_WEn</sub> | IOVDD ≥ 1.62 V | -22 +<br>(WRHOLD<br>* t{ <sub>}HFCOR-<br/>ECLK{</sub> )      | -   | _   | ns   |

|                                                                                                                              |                     | IOVDD ≥ 3.0 V  | -13 +<br>(WRHOLD<br><sup>* t</sup> HFCOR-<br>ECLK)           | _   | _   | ns   |

| Output setup time, from<br>EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading<br>EBI_WEn / EBI_NANDWEn<br>edge <sup>1</sup> | tosu_wen            | IOVDD ≥ 1.62 V | -12 +<br>(WRSET-<br>UP *<br>t <sub>HFCOR-</sub><br>ECLK)     | _   |     | ns   |

|                                                                                                                              |                     | IOVDD ≥ 3.0 V  | -10 +<br>(WRSET-<br>UP *<br>t <sub>HFCOR-</sub><br>ЕСLК)     |     |     | ns   |

| EBI_WEn / EBI_NANDWEn pulse width <sup>1</sup>                                                                               | twidth_wen          | IOVDD ≥ 1.62 V | -6 +<br>(MAX(1,<br>WRSTRB)<br><sup>* t</sup> HFCOR-<br>ECLK) |     |     | ns   |

|                                                                                                                              |                     | IOVDD ≥ 3.0 V  | -5 +<br>(MAX(1,<br>WRSTRB)<br><sup>* t</sup> HFCOR-<br>ECLK) | _   | -   | ns   |

Note:

1. The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFWE=0. The leading edge of EBI\_WEn can be moved to the right by setting HALFWE=1. This decreases the length of t<sub>WIDTH\_WEn</sub> and increases the length of t<sub>OSU\_WEn</sub> by 1/2 \* t<sub>HFCLKNODIV</sub>.

#### EBI Address Latch Enable Output Timing

Timing applies to multiplexed addressing modes D8A24ALE and D16A16ALE for both polarities. All numbers are based on route locations 0,1,2 only (with all EBI alternate functions using the same location at the same time). Timing is specified at 10% and 90% of IOVDD, 25 pF external loading, and slew rate for all GPIO set to 6.

| Parameter                                                                             | Symbol                  | Test Condition | Min                                                                    | Тур | Max | Unit |

|---------------------------------------------------------------------------------------|-------------------------|----------------|------------------------------------------------------------------------|-----|-----|------|

| Output hold time, from trail-<br>ing EBI_ALE edge to<br>EBI_AD invalid <sup>1 2</sup> | t <sub>OH_ALEn</sub>    | IOVDD ≥ 1.62 V | -22 +<br>(ADDR-<br>HOLD *<br><sup>t</sup> HFCOR-<br>ECLK)              | _   | _   | ns   |

|                                                                                       |                         | IOVDD ≥ 3.0 V  | -11 +<br>(ADDR-<br>HOLD *<br><sup>t</sup> HFCOR-<br>ECLK)              | _   | _   | ns   |

| Output setup time, from                                                               | t <sub>OSU_ALEn</sub>   | IOVDD ≥ 1.62 V | -12                                                                    | —   | —   | ns   |

| EBI_AD valid to leading<br>EBI_ALE edge                                               |                         | IOVDD ≥ 3.0 V  | -9                                                                     | —   | _   | ns   |

| EBI_ALEn pulse width <sup>1</sup>                                                     | <sup>t</sup> WIDTH_ALEn | IOVDD ≥ 1.62 V | -4 +<br>((ADDR-<br>SETUP +<br>1) *<br>t{ <sub>}HFCOR-</sub><br>ECLK{}) | _   | _   | ns   |

|                                                                                       |                         | IOVDD ≥ 3.0 V  | -3 +<br>((ADDR-<br>SETUP +<br>1) *<br>t{ <sub>}HFCOR-</sub><br>ECLK{}) | _   | _   | ns   |

## Table 4.37. EBI Address Latch Enable Output Timing

#### Note:

1. The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFALE=0. The trailing edge of EBI\_ALEn can be moved to the left by setting HALFALE=1. This decreases the length of t<sub>WIDTH\_ALEn</sub> and increases the length of t<sub>OSU\_ALEn</sub> by t<sub>HFCORECLK</sub> - 1/2 \* t<sub>HFCLKNODIV</sub>.

2. The figure shows a write operation. For a multiplexed read operation the address hold time is controlled via the RDSETUP state instead of via the ADDRHOLD state.

#### **EBI Read Enable Output Timing**

Timing applies to both EBI\_REn and EBI\_NANDREn for all addressing modes and both polarities. Output timing for EBI\_AD applies only to multiplexed addressing modes D8A24ALE and D16A16ALE. All numbers are based on route locations 0,1,2 only (with all EBI alternate functions using the same location at the same time). Timing is specified at 10% and 90% of IOVDD, 25 pF external loading, and slew rate for all GPIO set to 6.

| Parameter                                                                                               | Symbol               | Test Condition | Min                                                          | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------------------|----------------------|----------------|--------------------------------------------------------------|-----|-----|------|

| EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading                                                     | t <sub>OH_REn</sub>  | IOVDD ≥ 1.62 V | -23 +<br>(RDHOLD *<br><sup>t</sup> HFCOR-<br>ECLK)           | _   | _   | ns   |

|                                                                                                         |                      | IOVDD ≥ 3.0 V  | -13 +<br>(RDHOLD *<br><sup>t</sup> HFCOR-<br>ECLK)           | _   | _   | ns   |

| Output setup time, from<br>EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading<br>EBI_REn / EBI_NANDREn | t <sub>OSU_REn</sub> | IOVDD ≥ 1.62 V | -12 +<br>(RDSETUP<br>* t <sub>HFCOR-</sub><br>ECLK)          | _   | _   | ns   |

| euge ·                                                                                                  |                      | IOVDD ≥ 3.0 V  | -11 +<br>(RDSETUP<br><sup>* t</sup> HFCOR-<br>ECLK)          | _   | _   | ns   |

| EBI_REn pulse width <sup>1 2</sup>                                                                      | twiDTH_REn           | IOVDD ≥ 1.62 V | -6 +<br>(MAX(1,<br>RDSTRB) *<br>t <sub>HFCOR-</sub><br>ECLK) | _   | _   | ns   |

|                                                                                                         |                      | IOVDD ≥ 3.0 V  | -4 +<br>(MAX(1,<br>RDSTRB) *<br>t <sub>HFCOR-</sub><br>ECLK) | —   | _   | ns   |

## Table 4.38. EBI Read Enable Output Timing

#### Note:

1. The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFRE=0. The leading edge of EBI\_REn can be moved to the right by setting HALFRE=1. This decreases the length of t<sub>WIDTH\_REn</sub> and increases the length of t<sub>OSU\_REn</sub> by 1/2 \* t<sub>HFCLKNODIV</sub>.

2. When page mode is used, RDSTRB is replaced by RDPA for page hits.

# SDIO MMC DDR Mode Timing at 1.8 V

Timing is specified for route location 0 at 1.8 V IOVDD with voltage scaling disabled. Slew rate for SD\_CLK set to 7, all other GPIO set to 6, DRIVESTRENGTH = STRONG for all pins. SDIO\_CTRL\_TXDLYMUXSEL = 1. Loading between 5 and 10 pF on all pins or between 10 and 25 pF on all pins.

| Parameter                                     | Symbol              | Test Condition                    | Min  | Тур  | Мах | Unit |

|-----------------------------------------------|---------------------|-----------------------------------|------|------|-----|------|

| Clock frequency during data transfer          | F <sub>SD_CLK</sub> | Using HFRCO, AUXHFRCO, or USHFRCO | _    | _    | 18  | MHz  |

|                                               |                     | Using HFXO                        | _    | _    | TBD | MHz  |

| Clock low time                                | t <sub>WL</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 25.1 | —    |     | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock high time                               | t <sub>WH</sub>     | Using HFRCO, AUXHFRCO, or USHFRCO | 25.1 |      |     | ns   |

|                                               |                     | Using HFXO                        | TBD  | _    | _   | ns   |

| Clock rise time                               | t <sub>R</sub>      |                                   | 1.13 | 5.21 | _   | ns   |

| Clock fall time                               | t <sub>F</sub>      |                                   | 1.01 | 4.10 | _   | ns   |

| Input setup time, CMD valid to SD_CLK         | t <sub>ISU</sub>    |                                   | 5.3  |      |     | ns   |

| Input hold time, SD_CLK to CMD change         | t <sub>IH</sub>     |                                   | 2.5  |      | _   | ns   |

| Output delay time, SD_CLK to CMD valid        | t <sub>ODLY</sub>   |                                   | 0    |      | 16  | ns   |

| Output hold time, SD_CLK to CMD change        | t <sub>OH</sub>     |                                   | 3    |      |     | ns   |

| Input setup time, DAT[0:7]<br>valid to SD_CLK | t <sub>ISU2X</sub>  |                                   | 5.3  |      |     | ns   |

| Input hold time, SD_CLK to DAT[0:7] change    | t <sub>IH2X</sub>   |                                   | 2.5  |      |     | ns   |

| Output delay time, SD_CLK to DAT[0:7] valid   | t <sub>ODLY2X</sub> |                                   | 0    | _    | 16  | ns   |

| Output hold time, SD_CLK to DAT[0:7] change   | t <sub>OH2X</sub>   |                                   | 3    | —    | —   | ns   |

# Table 4.52. SDIO MMC DDR Mode Timing (Location 0, 1.8V I/O)

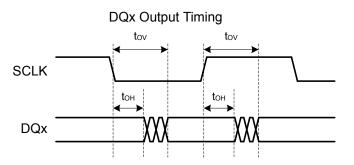

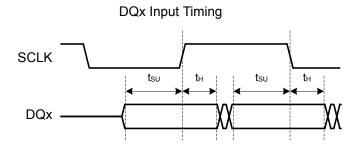

# **QSPI DDR Mode Timing (Locations 1, 2)**

Timing is specified with voltage scaling disabled, PHY-mode, route locations other than 0, TX DLL = 53, RX DLL = 88, 20-25 pF loading per GPIO, and slew rate for all GPIO set to 6, DRIVESTRENGTH = STRONG.

| Parameter        | Symbol          | Test Condition           | Min                                   | Тур | Мах       | Unit |

|------------------|-----------------|--------------------------|---------------------------------------|-----|-----------|------|

| Half SCLK period | T/2             | HFXO                     | (1/F <sub>SCLK</sub> ) *<br>0.4 - 0.4 | —   | _         | ns   |

|                  |                 | HFRCO, AUXHFRCO, USHFRCO | (1/F <sub>SCLK</sub> ) *<br>0.44      | —   | _         | ns   |

| Output valid     | t <sub>OV</sub> |                          | —                                     | —   | T/2 - 6.6 | ns   |

| Output hold      | t <sub>OH</sub> |                          | T/2 - 52.2                            | —   | —         | ns   |

| Input setup      | t <sub>SU</sub> |                          | 44.8                                  | —   | _         | ns   |

| Input hold       | t <sub>H</sub>  |                          | -2.4                                  | _   | _         | ns   |

Figure 4.22. QSPI DDR Timing Diagrams

# **QSPI DDR Flash Timing Example**

This example uses timing values for location 0 (DDR mode) to demonstrate the calculation of allowable flash timing using the QSPI in DDR mode.

- Using a configured SCLK frequency ( $\mathrm{F}_{\mathrm{SCLK}}$ ) of 8 MHz from the HFXO clock source:

- The resulting minimum half-period, T/2(min) = (1/F<sub>SCLK</sub>) \* 0.4 0.4 = 49.6 ns.

- Flash will see a minimum setup time of T/2  $t_{OV}$  = T/2 (T/2 5.0) = 5.0 ns.

- Flash will see a minimum hold time of  $t_{OH}$  = T/2 39.4 = 49.6 39.4 = 10.2 ns.

- Flash can have a maximum output valid time of T/2  $t_{SU}$  = T/2 33.1 = 49.6 33.1 = 16.5 ns.

- Flash can have a minimum output hold time of  $t_{\rm H}$  = 0.9 ns.

# 5. Pin Definitions

# 5.1 EFM32GG11B8xx in BGA192 Device Pinout

| Pin A1 index | 1           | 2    | 3        | 4           | 5     | 6          | 7            | 8                     | 9                   | 10        | 11       | 12          | 13      | 14   | 15               | 16              |

|--------------|-------------|------|----------|-------------|-------|------------|--------------|-----------------------|---------------------|-----------|----------|-------------|---------|------|------------------|-----------------|

|              | *           |      |          |             |       |            |              |                       |                     |           |          |             |         |      |                  |                 |

| А            | PALS        | PE15 | PE14     | PE13        | PE12  | PE1        | PE10         | PE9                   | PE8                 | 619       | 610      | PE14        | BUS     | PET] | PE70             | PF0             |

| В            | PAG         | 101  | 1010     | 609         | PF9   | <b>PF8</b> | PFT          | 640                   | PII)                | 618       | PF5      | PF13        | PF3     | PF2  | PF1              | VREGO           |

| С            | (Ag         | 1012 | 1014     | 1013        | PI13  | PI14       | PI13         | PI12                  | PI19                | (TI)      | PF15     | PF12        | PFA     | PC15 | PC14             | VREGI           |

| D            | PAZ         | 609  | 1015     |             |       |            |              |                       |                     |           |          |             |         | PC13 | ¢C12             | PC17            |

| E            | PA3         | 602  | pGI      |             |       |            |              |                       |                     |           |          |             |         | PC70 | 609              | e <sup>C8</sup> |

| F            | PA9         | pGA  | PG3      |             |       | TONDS;     | I OVDD'      | 159                   | (NC).               | LOVDDC    | tovobe   | )           |         | 619  | PIA              | P13             |

| G            | PAS         | 609  | 605      |             |       |            |              |                       |                     | LOVODE    |          |             |         | 612  | PIL              | P10             |

| н            | PAG         | PG8  | PGT      |             |       | (159)      | 159<br>(159) | (155)                 | (159)               | (159)     | (159)    |             |         | PES  | PEO              | PET             |

| J            | pG1}        | PG19 | PG9      |             |       | (155)      | 155          | (155)                 | (155)               | 159       | (159)    |             |         | PE3  | PEA.             | ECOUPLE         |

| к            | pG14        | pG13 | PG13     |             |       | TONDOG     | Lovopo       | (159)                 | (15 <sup>5</sup> ). | LOVDDe    | LOVDDe   | )           |         | PEL  | PE2              | ende            |

| L            | 613         | BIJ  | ,<br>p80 |             |       | TONDOG.    | revoge       | (59)                  | (159).              | rovode.   | ronde    | <b>)</b>    |         | PEO  | ( <sup>1</sup> ) | REGUDD          |

| м            | PB1         | 682  | PB3      |             |       | \$C        | <b>y</b>     | $\bigcirc$            | $\bigcirc$          | <b>y</b>  | <b>y</b> |             |         | 609  | FOVS             | REGSW           |

| Ν            | pBA)        | PB5  | P89      |             |       |            |              |                       |                     |           |          |             |         | 605  | pDA.             | TEGNES          |

| Р            | ()<br>(0)q  | 603  | 603      | 849         | 627   | 6213       | 689          | B12                   | 642                 | PHS       | PH8      | 0H1]        | PH13    | 009  | 603              | 1908)<br>141-   |

| R            | ()<br>(PBT) | 63   | (C)      | ()<br>(PA9) | RODEN | ET CET     | 6819         | 640                   | (H3)                | 6H6       | PH9      | 6417        | 6H14    | PH15 | 602              | (TOG)           |

| т            | 683         | 60   | (FAG     | P.<br>PAL   | BOP . | RES 14     | pB1          | PHJ                   | pHA                 | PH)       | e.       | 10.<br>1813 | 100 B14 | ku b | 603              | 609             |

| ,            | 60          | 60   | (h)      | PK-         | PK-   | PK-        | 60.          | <b>W</b> <sup>1</sup> | <u>N</u>            | <u>en</u> | 642      | 60.         | 60.     | Pur  | 60               | 60              |

## Figure 5.1. EFM32GG11B8xx in BGA192 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description |

|----------|--------|-------------|----------|--------|-------------|

| PA15     | A1     | GPIO        | PE15     | A2     | GPIO        |

| PE14     | A3     | GPIO        | PE13     | A4     | GPIO        |

| PE12     | A5     | GPIO        | PE11     | A6     | GPIO        |

| PE10     | A7     | GPIO        | PE9      | A8     | GPIO        |

| PE8      | A9     | GPIO        | PI9      | A10    | GPIO (5V)   |

| PI6      | A11    | GPIO (5V)   | PF14     | A12    | GPIO (5V)   |

| Pin Name | Pin(s) | Description                                                                         | Pin Name | Pin(s)     | Description                                                                                                                                                                                                 |

|----------|--------|-------------------------------------------------------------------------------------|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB2      | M2     | GPIO                                                                                | PB3      | M3         | GPIO                                                                                                                                                                                                        |

| PC6      | M14    | GPIO                                                                                | VREGVSS  | M15<br>N16 | Voltage regulator VSS                                                                                                                                                                                       |

| VREGSW   | M16    | DCDC regulator switching node                                                       | PB4      | N1         | GPIO                                                                                                                                                                                                        |

| PB5      | N2     | GPIO                                                                                | PB6      | N3         | GPIO                                                                                                                                                                                                        |

| PD5      | N14    | GPIO                                                                                | PD4      | N15        | GPIO                                                                                                                                                                                                        |

| PC0      | P1     | GPIO (5V)                                                                           | PC1      | P2         | GPIO (5V)                                                                                                                                                                                                   |

| PC2      | P3     | GPIO (5V)                                                                           | PA8      | P4         | GPIO                                                                                                                                                                                                        |

| PA11     | P5     | GPIO                                                                                | PA13     | P6         | GPIO (5V)                                                                                                                                                                                                   |

| PB9      | P7     | GPIO (5V)                                                                           | PB12     | P8         | GPIO                                                                                                                                                                                                        |

| PH2      | P9     | GPIO (5V)                                                                           | PH5      | P10        | GPIO                                                                                                                                                                                                        |

| PH8      | P11    | GPIO (5V)                                                                           | PH11     | P12        | GPIO (5V)                                                                                                                                                                                                   |

| PH13     | P13    | GPIO (5V)                                                                           | PD0      | P14        | GPIO (5V)                                                                                                                                                                                                   |

| PD3      | P15    | GPIO                                                                                | PD8      | P16        | GPIO                                                                                                                                                                                                        |

| PB7      | R1     | GPIO                                                                                | PC3      | R2         | GPIO (5V)                                                                                                                                                                                                   |

| PC5      | R3     | GPIO                                                                                | PA9      | R4         | GPIO                                                                                                                                                                                                        |

| BODEN    | R5     | Brown-Out Detector Enable. This pin<br>may be left disconnected or tied to<br>AVDD. | RESETn   | R6         | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB10     | R7     | GPIO (5V)                                                                           | PH0      | R8         | GPIO (5V)                                                                                                                                                                                                   |

| PH3      | R9     | GPIO (5V)                                                                           | PH6      | R10        | GPIO                                                                                                                                                                                                        |

| PH9      | R11    | GPIO (5V)                                                                           | PH12     | R12        | GPIO (5V)                                                                                                                                                                                                   |

| PH14     | R13    | GPIO (5V)                                                                           | PH15     | R14        | GPIO (5V)                                                                                                                                                                                                   |

| PD2      | R15    | GPIO (5V)                                                                           | PD7      | R16        | GPIO                                                                                                                                                                                                        |

| PB8      | T1     | GPIO                                                                                | PC4      | T2         | GPIO                                                                                                                                                                                                        |

| PA7      | Т3     | GPIO                                                                                | PA10     | T4         | GPIO                                                                                                                                                                                                        |

| PA12     | T5     | GPIO (5V)                                                                           | PA14     | Т6         | GPIO                                                                                                                                                                                                        |

| PB11     | T7     | GPIO                                                                                | PH1      | Т8         | GPIO (5V)                                                                                                                                                                                                   |

| PH4      | Т9     | GPIO                                                                                | PH7      | T10        | GPIO (5V)                                                                                                                                                                                                   |

| PH10     | T11    | GPIO (5V)                                                                           | PB13     | T12        | GPIO                                                                                                                                                                                                        |

| PB14     | T13    | GPIO                                                                                | AVDD     | T14        | Analog power supply.                                                                                                                                                                                        |

| PD1      | T15    | GPIO                                                                                | PD6      | T16        | GPIO                                                                                                                                                                                                        |

Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PD13, PD14, and PD15 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

| Pin Name | Pin(s) | Description                                                                                                                                                                                                 | Pin Name | Pin(s)               | Description           |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|-----------------------|

| PB2      | 11     | GPIO                                                                                                                                                                                                        | PB3      | 12                   | GPIO                  |

| PB4      | 13     | GPIO                                                                                                                                                                                                        | PB5      | 14                   | GPIO                  |

| PB6      | 15     | GPIO                                                                                                                                                                                                        | VSS      | 16<br>32<br>58<br>83 | Ground                |

| PC0      | 18     | GPIO (5V)                                                                                                                                                                                                   | PC1      | 19                   | GPIO (5V)             |

| PC2      | 20     | GPIO (5V)                                                                                                                                                                                                   | PC3      | 21                   | GPIO (5V)             |

| PC4      | 22     | GPIO                                                                                                                                                                                                        | PC5      | 23                   | GPIO                  |

| PB7      | 24     | GPIO                                                                                                                                                                                                        | PB8      | 25                   | GPIO                  |

| PA7      | 26     | GPIO                                                                                                                                                                                                        | PA8      | 27                   | GPIO                  |

| PA9      | 28     | GPIO                                                                                                                                                                                                        | PA10     | 29                   | GPIO                  |

| PA11     | 30     | GPIO                                                                                                                                                                                                        | PA12     | 33                   | GPIO (5V)             |

| PA13     | 34     | GPIO (5V)                                                                                                                                                                                                   | PA14     | 35                   | GPIO                  |

| RESETn   | 36     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. | PB9      | 37                   | GPIO (5V)             |

| PB10     | 38     | GPIO (5V)                                                                                                                                                                                                   | PB11     | 39                   | GPIO                  |

| PB12     | 40     | GPIO                                                                                                                                                                                                        | AVDD     | 41<br>45             | Analog power supply.  |

| PB13     | 42     | GPIO                                                                                                                                                                                                        | PB14     | 43                   | GPIO                  |

| PD0      | 46     | GPIO (5V)                                                                                                                                                                                                   | PD1      | 47                   | GPIO                  |

| PD2      | 48     | GPIO (5V)                                                                                                                                                                                                   | PD3      | 49                   | GPIO                  |

| PD4      | 50     | GPIO                                                                                                                                                                                                        | PD5      | 51                   | GPIO                  |

| PD6      | 52     | GPIO                                                                                                                                                                                                        | PD7      | 53                   | GPIO                  |

| PD8      | 54     | GPIO                                                                                                                                                                                                        | PC6      | 55                   | GPIO                  |

| PC7      | 56     | GPIO                                                                                                                                                                                                        | DVDD     | 57                   | Digital power supply. |

| DECOUPLE | 59     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    | PE0      | 60                   | GPIO (5V)             |

| PE1      | 61     | GPIO (5V)                                                                                                                                                                                                   | PE2      | 62                   | GPIO                  |

| PE3      | 63     | GPIO                                                                                                                                                                                                        | PE4      | 64                   | GPIO                  |

| PE5      | 65     | GPIO                                                                                                                                                                                                        | PE6      | 66                   | GPIO                  |

| PE7      | 67     | GPIO                                                                                                                                                                                                        | PC8      | 68                   | GPIO (5V)             |

| PC9      | 69     | GPIO (5V)                                                                                                                                                                                                   | PC10     | 70                   | GPIO (5V)             |

| PC11     | 71     | GPIO (5V)                                                                                                                                                                                                   | PC12     | 72                   | GPIO (5V)             |

| PC13     | 73     | GPIO (5V)                                                                                                                                                                                                   | PC14     | 74                   | GPIO (5V)             |

| PC15     | 75     | GPIO (5V)                                                                                                                                                                                                   | PF0      | 76                   | GPIO (5V)             |

| PF1      | 77     | GPIO (5V)                                                                                                                                                                                                   | PF2      | 78                   | GPIO                  |

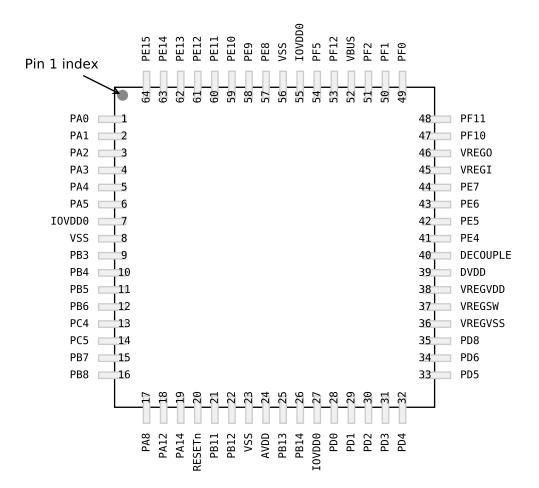

## Figure 5.12. EFM32GG11B8xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Table 5.12. EFM32GG11B8xx in QFP64 Device Pinou | Table 5.12. | 2GG11B8xx in QFP64 Device Pinout |

|-------------------------------------------------|-------------|----------------------------------|

|-------------------------------------------------|-------------|----------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>27<br>55 | Digital IO power supply 0. | VSS      | 8<br>23<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

| GPIO Name |                          | Pin Alter                   | nate Functionality / De                                    | escription                                                                                                                  |                                                        |

|-----------|--------------------------|-----------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

|           | Analog                   | EBI                         | Timers                                                     | Communication                                                                                                               | Other                                                  |

| PF14      | BUSDY BUSCX              |                             | TIM1_CC1 #6<br>TIM4_CC1 #1<br>TIM5_CC2 #7<br>WTIM3_CC1 #7  | 12C2_SCL #4                                                                                                                 |                                                        |

| PF11      | BUSCY BUSDX              | EBI_NANDWEn #5              | TIM5_CC2 #6<br>WTIM3_CC2 #3<br>PCNT2_S1IN #3               | US5_CTS #2 U1_RX<br>#1 I2C2_SCL #2<br>USB_DP                                                                                |                                                        |

| PF10      | BUSDY BUSCX              | EBI_ARDY #5                 | TIM5_CC1 #6<br>WTIM3_CC1 #3<br>PCNT2_S0IN #3               | US5_RTS #2 U1_TX<br>#1 I2C2_SDA #2<br>USB_DM                                                                                |                                                        |

| PF0       | BUSDY BUSCX              | EBI_A24 #1                  | TIM0_CC0 #4<br>WTIM0_CC1 #4 LE-<br>TIM0_OUT0 #2            | US2_TX #5<br>CAN0_RX #1<br>US1_CLK #2<br>LEU0_TX #3<br>I2C0_SDA #5                                                          | PRS_CH15 #2<br>ACMP3_O #0<br>DBG_SWCLKTCK<br>BOOT_TX   |

| PA0       | BUSBY BUSAX<br>LCD_SEG13 | EBI_AD09 #0<br>EBI_CSTFT #3 | TIM0_CC0 #0<br>TIM0_CC1 #7<br>TIM3_CC0 #4<br>PCNT0_S0IN #4 | ETH_RMIITXEN #0<br>ETH_MIITXCLK #0<br>SDIO_DAT0 #1<br>US1_RX #5 US3_TX<br>#0 QSPI0_CS0 #1<br>LEU0_RX #4<br>I2C0_SDA #0      | CMU_CLK2 #0<br>PRS_CH0 #0<br>PRS_CH3 #3<br>GPIO_EM4WU0 |

| PD11      | LCD_SEG30                | EBI_CS2 #0<br>EBI_HSNC #1   | TIM4_CC0 #6<br>WTIM3_CC2 #0                                | ETH_RMIICRSDV #1<br>SDIO_DAT5 #0<br>QSPI0_DQ2 #0<br>ETH_MIIRXD3 #2<br>US4_CLK #1                                            |                                                        |

| PD10      | LCD_SEG29                | EBI_CS1 #0<br>EBI_VSNC #1   | TIM4_CC2 #5<br>WTIM3_CC1 #0                                | ETH_RMIIREFCLK<br>#1 SDIO_DAT6 #0<br>QSPI0_DQ1 #0<br>ETH_MIIRXD2 #2<br>US4_RX #1                                            | CMU_CLK2 #5<br>CMU_CLKI0 #5                            |

| PD9       | LCD_SEG28                | EBI_CS0 #0<br>EBI_DTEN #1   | TIM4_CC1 #5<br>WTIM3_CC0 #0                                | ETH_RMIIRXD0 #1<br>SDIO_DAT7 #0<br>QSPI0_DQ0 #0<br>ETH_MIIRXD1 #2<br>US4_TX #1                                              |                                                        |

| PF9       | BUSCY BUSDX<br>LCD_SEG27 | EBI_REn #4<br>EBI_BL1 #1    | TIM4_CC0 #5                                                | ETH_RMIIRXD1 #1<br>US2_CS #4<br>QSPI0_DQS #0<br>ETH_MIIRXD0 #2<br>ETH_TSUTMRTOG<br>#3 SDIO_WP #0<br>U0_RTS #0 U1_CTS<br>#1  | ETM_TD0 #1                                             |

| PF8       | BUSDY BUSCX<br>LCD_SEG26 | EBI_WEn #4<br>EBI_BL0 #1    | TIM0_CC2 #1<br>TIM4_CC2 #4                                 | ETH_RMIITXEN #1<br>US2_CLK #4<br>QSPI0_CS1 #0<br>ETH_MIIRXDV #2<br>ETH_TSUEXTCLK<br>#3 SDIO_CD #0<br>U0_CTS #0 U1_RTS<br>#1 | ETM_TCLK #1<br>GPIO_EM4WU8                             |

| Alternate     | LOCA   | TION  |                                                                                                                    |

|---------------|--------|-------|--------------------------------------------------------------------------------------------------------------------|

| Functionality | 0 - 3  | 4 - 7 | Description                                                                                                        |

| LFXTAL_N      | 0: PB8 |       | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional ex-<br>ternal clock input pin. |

| LFXTAL_P      | 0: PB7 |       | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                         |

| OPA0_N        | 0: PC5 |       | Operational Amplifier 0 external negative input.                                                                   |

| OPA0_P        | 0: PC4 |       | Operational Amplifier 0 external positive input.                                                                   |

| OPA1_N        | 0: PD7 |       | Operational Amplifier 1 external negative input.                                                                   |

| OPA1_P        | 0: PD6 |       | Operational Amplifier 1 external positive input.                                                                   |

| OPA2_N        | 0: PD3 |       | Operational Amplifier 2 external negative input.                                                                   |

| OPA2_OUT      | 0: PD5 |       | Operational Amplifier 2 output.                                                                                    |

| OPA2_OUTALT   | 0: PD0 |       | Operational Amplifier 2 alternative output.                                                                        |

| OPA2_P        | 0: PD4 |       | Operational Amplifier 2 external positive input.                                                                   |

| OPA3_N        | 0: PC7 |       | Operational Amplifier 3 external negative input.                                                                   |

| OPA3_OUT      | 0: PD1 |       | Operational Amplifier 3 output.                                                                                    |

| OPA3_P        | 0: PC6 |       | Operational Amplifier 3 external positive input.                                                                   |

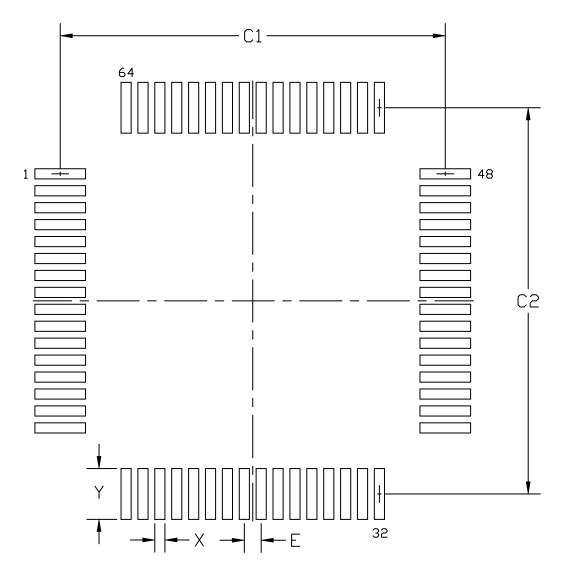

## 11.2 TQFP64 PCB Land Pattern

Figure 11.2. TQFP64 PCB Land Pattern Drawing

# 13. Revision History

## **Revision 0.6**

March, 2018

- Removed "Confindential" watermark.

- Updated 4.1 Electrical Characteristics and 4.2 Typical Performance Curves with latest characterization data.

## Revision 0.2

October, 2017

- · Updated memory maps to latest formatting and to include all peripherals.

- Updated all electrical specifications tables with latest characterization results.

- Absolute Maximum Ratings Table:

- Removed redundant I<sub>VSSMAX</sub> line.

- Added footnote to clarify V<sub>DIGPIN</sub> specification for 5V tolerant GPIO.

- General Operating Conditions Table:

- Removed dV<sub>DD</sub> specification and redundant footnote about shorting VREGVDD and AVDD together.

- Added footnote about IOVDD voltage restriction when CSEN peripheral is used with chopping enabled.

- Flash Memory Characteristics Table: Added timing measurement clarification for Device Erase and Mass Erase.

- · Analog to Digital Converter (ADC) Table:

- · Added header text for general specification conditions.

- Added footnote for clarification of input voltage limits.

- · Minor typographical corrections, including capitalization, mis-spellings and punctuation marks, throughout document.

- Minor formatting and styling updates, including table formats, TOC location, and boilerplate information throughout document.

#### **Revision 0.1**

April 27th, 2017

Initial release.