Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                        |

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 144                                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                             |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 192-VFBGA                                                                                                     |

| Supplier Device Package    | 192-BGA (7x7)                                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b820f2048gl192-br                                  |

### 3.2 Power

The EFM32GG11 has an Energy Management Unit (EMU) and efficient integrated regulators to generate internal supply voltages. Only a single external supply voltage is required, from which all internal voltages are created. A 5 V regulator is available on some OPNs, allowing the device to be powered directly from 5 V power sources, such as USB. An optional integrated DC-DC buck regulator can be utilized to further reduce the current consumption. The DC-DC regulator requires one external inductor and one external capacitor.

The EFM32GG11 device family includes support for internal supply voltage scaling, as well as two different power domain groups for peripherals. These enhancements allow for further supply current reductions and lower overall power consumption.

AVDD and VREGVDD need to be 1.8 V or higher for the MCU to operate across all conditions; however the rest of the system will operate down to 1.62 V, including the digital supply and I/O. This means that the device is fully compatible with 1.8 V components. Running from a sufficiently high supply, the device can use the DC-DC to regulate voltage not only for itself, but also for other PCB components, supplying up to a total of 200 mA.

### 3.2.1 Energy Management Unit (EMU)

The Energy Management Unit manages transitions of energy modes in the device. Each energy mode defines which peripherals and features are available and the amount of current the device consumes. The EMU can also be used to turn off the power to unused RAM blocks, and it contains control registers for the DC-DC regulator and the Voltage Monitor (VMON). The VMON is used to monitor multiple supply voltages. It has multiple channels which can be programmed individually by the user to determine if a sensed supply has fallen below a chosen threshold.

### 3.2.2 DC-DC Converter

The DC-DC buck converter covers a wide range of load currents and provides up to 90% efficiency in energy modes EM0, EM1, EM2 and EM3, and can supply up to 200 mA to the device and surrounding PCB components. Protection features include programmable current limiting, short-circuit protection, and dead-time protection. The DC-DC converter may also enter bypass mode when the input voltage is too low for efficient operation. In bypass mode, the DC-DC input supply is internally connected directly to its output through a low resistance switch. Bypass mode also supports in-rush current limiting to prevent input supply voltage droops due to excessive output current transients.

### 3.2.3 5 V Regulator

A 5 V input regulator is available, allowing the device to be powered directly from 5 V power sources such as the USB VBUS line. The regulator is available in all energy modes, and outputs 3.3 V to be used to power the USB PHY and other 3.3 V systems. Two inputs to the regulator allow for seamless switching between local and external power sources.

## 4.1.2 Operating Conditions

When assigning supply sources, the following requirements must be observed:

- VREGVDD must be greater than or equal to AVDD, DVDD and all IOVDD supplies.

- VREGVDD = AVDD

- DVDD ≤ AVDD

- IOVDD ≤ AVDD

## **4.1.24 USART SPI**

# **SPI Master Timing**

Table 4.34. SPI Master Timing

| Parameter                      | Symbol               | Test Condition                                | Min                                         | Тур          | Max | Unit |

|--------------------------------|----------------------|-----------------------------------------------|---------------------------------------------|--------------|-----|------|

| SCLK period <sup>1 3 2</sup>   | t <sub>SCLK</sub>    | All USARTs except USART2                      | 2 * the | _            | _   | ns   |

|                                |                      | USART2                                        | 2 * t <sub>HFPERBCLK</sub>                  | _            | _   | ns   |

| CS to MOSI <sup>1 3</sup>      | t <sub>CS_MO</sub>   | USART2, location 4, IOVDD = 1.8 V             | -3.2                                        | _            | 6.8 | ns   |

|                                |                      | USART2, location 4, IOVDD = 3.0 V             | -2.3                                        | _            | 6.0 | ns   |

|                                |                      | USART2, location 5, IOVDD = 1.8 V             | -8.1                                        | <del>_</del> | 6.3 | ns   |

|                                |                      | USART2, location 5, IOVDD = 3.0 V             | -7.3                                        | _            | 4.4 | ns   |

|                                |                      | All other USARTs and locations, IOVDD = 1.8 V | -15                                         | _            | 13  | ns   |

|                                |                      | All other USARTs and locations, IOVDD = 3.0 V | -13                                         | _            | 11  | ns   |

| SCLK to MOSI <sup>13</sup>     | t <sub>SCLK_MO</sub> | USART2, location 4, IOVDD = 1.8 V             | -0.3                                        | _            | 9.2 | ns   |

|                                |                      | USART2, location 4, IOVDD = 3.0 V             | -0.3                                        | _            | 8.6 | ns   |

|                                |                      | USART2, location 5, IOVDD = 1.8 V             | -3.6                                        | _            | 5.0 | ns   |

|                                |                      | USART2, location 5, IOVDD = 3.0 V             | -3.4                                        | _            | 3.2 | ns   |

|                                |                      | All other USARTs and locations, IOVDD = 1.8 V | -10                                         | _            | 11  | ns   |

|                                |                      | All other USARTs and locations, IOVDD = 3.0 V | -9                                          | _            | 11  | ns   |

| MISO setup time <sup>1 3</sup> | t <sub>SU_MI</sub>   | USART2, location 4, IOVDD = 1.8 V             | 39.7                                        | _            | _   | ns   |

|                                |                      | USART2, location 4, IOVDD = 3.0 V             | 22.4                                        | _            | _   | ns   |

|                                |                      | USART2, location 5, IOVDD = 1.8 V             | 49.2                                        | _            | _   | ns   |

|                                |                      | USART2, location 5, IOVDD = 3.0 V             | 30.0                                        | _            | _   | ns   |

|                                |                      | All other USARTs and locations, IOVDD = 1.8 V | 55                                          | _            | _   | ns   |

|                                |                      | All other USARTs and locations, IOVDD = 3.0 V | 36                                          | _            | _   | ns   |

### 4.1.25 External Bus Interface (EBI)

### **EBI Write Enable Output Timing**

Timing applies to both EBI\_WEn and EBI\_NANDWEn for all addressing modes and both polarities. All numbers are based on route locations 0,1,2 only (with all EBI alternate functions using the same location at the same time). Timing is specified at 10% and 90% of IOVDD, 25 pF external loading, and slew rate for all GPIO set to 6.

Table 4.36. EBI Write Enable Timing

| Parameter                                                                                                                    | Symbol               | Test Condition | Min                                                          | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|--------------------------------------------------------------|-----|-----|------|

| Output hold time, from trailing EBI_WEn / EBI_NAND-WEn edge to EBI_AD, EBI_A, EBI_CSn, EBI_BLn invalid                       | t <sub>OH_WEn</sub>  | IOVDD ≥ 1.62 V | -22 +<br>(WRHOLD<br>* t{}HFCOR-<br>ECLK{})                   | _   | _   | ns   |

| invalid                                                                                                                      |                      | IOVDD ≥ 3.0 V  | -13 +<br>(WRHOLD<br>* thecor-<br>eclk)                       | _   | _   | ns   |

| Output setup time, from<br>EBI_AD, EBI_A, EBI_CSn,<br>EBI_BLn valid to leading<br>EBI_WEn / EBI_NANDWEn<br>edge <sup>1</sup> | t <sub>OSU_WEn</sub> | IOVDD ≥ 1.62 V | -12 +<br>(WRSET-<br>UP *<br>t <sub>HFCOR-</sub><br>ECLK)     | _   | _   | ns   |

|                                                                                                                              |                      | IOVDD ≥ 3.0 V  | -10 +<br>(WRSET-<br>UP *<br>t <sub>HFCOR-</sub><br>ECLK)     | _   | _   | ns   |

| EBI_WEn / EBI_NANDWEn pulse width <sup>1</sup>                                                                               | twidth_wen           | IOVDD ≥ 1.62 V | -6 +<br>(MAX(1,<br>WRSTRB)<br>* t <sub>HFCOR-</sub><br>ECLK) | _   | _   | ns   |

|                                                                                                                              |                      | IOVDD ≥ 3.0 V  | -5 +<br>(MAX(1,<br>WRSTRB)<br>* tHFCOR-<br>ECLK)             | _   | _   | ns   |

<sup>1.</sup> The figure shows the timing for the case that the half strobe length functionality is not used, i.e. HALFWE=0. The leading edge of EBI\_WEn can be moved to the right by setting HALFWE=1. This decreases the length of t<sub>WIDTH\_WEn</sub> and increases the length of t<sub>OSU\_WEn</sub> by 1/2 \* t<sub>HFCLKNODIV</sub>.

## 4.1.28.2 QSPI DDR Mode

## **QSPI DDR Mode Timing (Location 0)**

Timing is specified with voltage scaling disabled, PHY-mode, route location 0 only, TX DLL = 35, RX DLL = 70, 20-25 pF loading per GPIO, and slew rate for all GPIO set to 6, DRIVESTRENGTH = STRONG.

Table 4.56. QSPI DDR Mode Timing (Location 0)

| Parameter        | Symbol          | Test Condition           | Min                                   | Тур | Max       | Unit |

|------------------|-----------------|--------------------------|---------------------------------------|-----|-----------|------|

| Half SCLK period | T/2             | HFXO                     | (1/F <sub>SCLK</sub> ) *<br>0.4 - 0.4 | _   | _         | ns   |

|                  |                 | HFRCO, AUXHFRCO, USHFRCO | (1/F <sub>SCLK</sub> ) *<br>0.44      | _   | _         | ns   |

| Output valid     | t <sub>OV</sub> |                          | _                                     | _   | T/2 - 5.0 | ns   |

| Output hold      | t <sub>OH</sub> |                          | T/2 - 39.4                            | _   | _         | ns   |

| Input setup      | t <sub>SU</sub> |                          | 33.1                                  | _   | _         | ns   |

| Input hold       | t <sub>H</sub>  |                          | -0.9                                  | _   | _         | ns   |

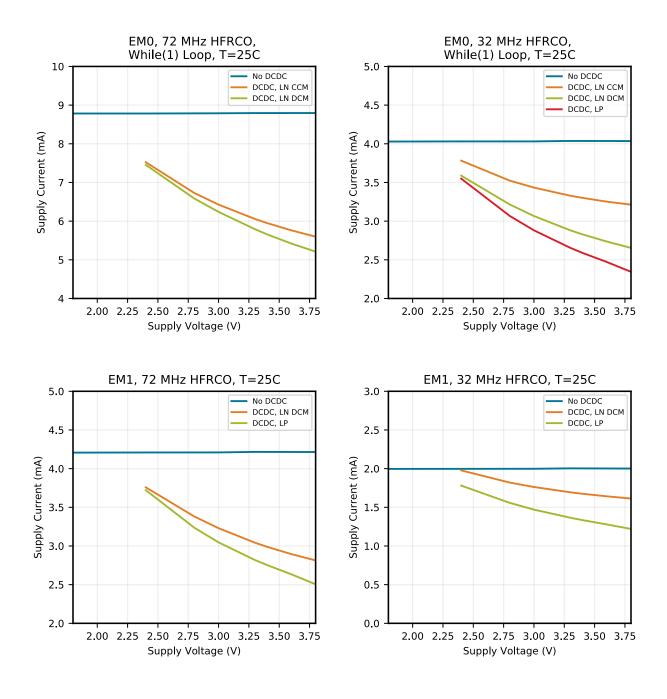

Figure 4.27. EM0 and EM1 Mode Typical Supply Current vs. Supply

Typical supply current for EM2, EM3 and EM4H using standard software libraries from Silicon Laboratories.

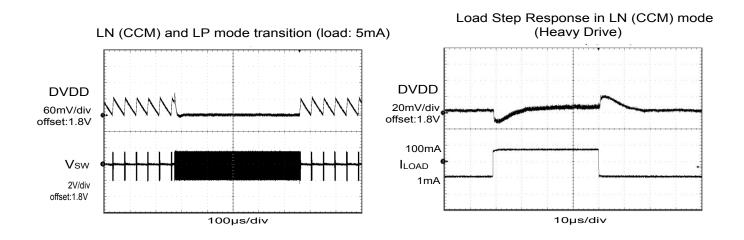

Figure 4.30. DC-DC Converter Transition Waveforms

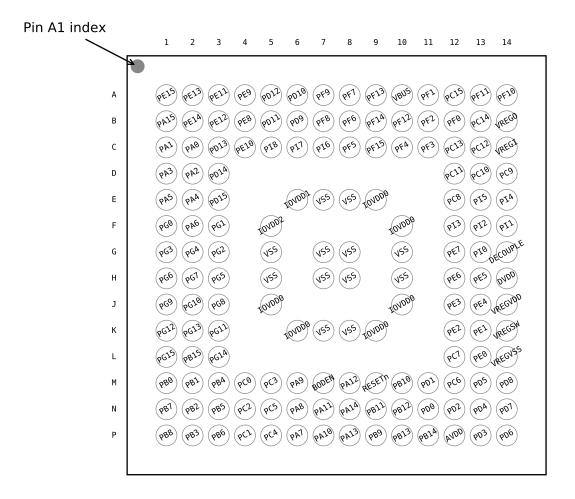

### 5.2 EFM32GG11B8xx in BGA152 Device Pinout

Figure 5.2. EFM32GG11B8xx in BGA152 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

Table 5.2. EFM32GG11B8xx in BGA152 Device Pinout

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description                                           |

|----------|--------|-------------|----------|--------|-------------------------------------------------------|

| PE15     | A1     | GPIO        | PE13     | A2     | GPIO                                                  |

| PE11     | А3     | GPIO        | PE9      | A4     | GPIO                                                  |

| PD12     | A5     | GPIO        | PD10     | A6     | GPIO                                                  |

| PF9      | A7     | GPIO        | PF7      | A8     | GPIO                                                  |

| PF13     | A9     | GPIO (5V)   | VBUS     | A10    | USB VBUS signal and auxiliary input to 5 V regulator. |

| PF1      | A11    | GPIO (5V)   | PC15     | A12    | GPIO (5V)                                             |

| PF11     | A13    | GPIO (5V)   | PF10     | A14    | GPIO (5V)                                             |

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description                                           |

|----------|--------|-------------|----------|--------|-------------------------------------------------------|

| PF2      | 78     | GPIO        | VBUS     | 79     | USB VBUS signal and auxiliary input to 5 V regulator. |

| PF12     | 80     | GPIO        | PF5      | 81     | GPIO                                                  |

| PF6      | 84     | GPIO        | PF7      | 85     | GPIO                                                  |

| PF8      | 86     | GPIO        | PF9      | 87     | GPIO                                                  |

| PD9      | 88     | GPIO        | PD10     | 89     | GPIO                                                  |

| PD11     | 90     | GPIO        | PD12     | 91     | GPIO                                                  |

| PE8      | 92     | GPIO        | PE9      | 93     | GPIO                                                  |

| PE10     | 94     | GPIO        | PE11     | 95     | GPIO                                                  |

| PE12     | 96     | GPIO        | PE13     | 97     | GPIO                                                  |

| PE14     | 98     | GPIO        | PE15     | 99     | GPIO                                                  |

| PA15     | 100    | GPIO        |          |        |                                                       |

<sup>1.</sup> GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s) | Description | Pin Name | Pin(s) | Description |

|----------|--------|-------------|----------|--------|-------------|

| PF2      | 78     | GPIO        | NC       | 79     | No Connect. |

| PF12     | 80     | GPIO        | PF5      | 81     | GPIO        |

| PF6      | 84     | GPIO        | PF7      | 85     | GPIO        |

| PF8      | 86     | GPIO        | PF9      | 87     | GPIO        |

| PD9      | 88     | GPIO        | PD10     | 89     | GPIO        |

| PD11     | 90     | GPIO        | PD12     | 91     | GPIO        |

| PE8      | 92     | GPIO        | PE9      | 93     | GPIO        |

| PE10     | 94     | GPIO        | PE11     | 95     | GPIO        |

| PE12     | 96     | GPIO        | PE13     | 97     | GPIO        |

| PE14     | 98     | GPIO        | PE15     | 99     | GPIO        |

| PA15     | 100    | GPIO        |          |        |             |

1. GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s) | Description                                           | Pin Name | Pin(s) | Description |

|----------|--------|-------------------------------------------------------|----------|--------|-------------|

| PF1      | 77     | GPIO (5V)                                             | PF2      | 78     | GPIO        |

| VBUS     | 79     | USB VBUS signal and auxiliary input to 5 V regulator. | PF12     | 80     | GPIO        |

| PF5      | 81     | GPIO                                                  | PF6      | 84     | GPIO        |

| PF7      | 85     | GPIO                                                  | PF8      | 86     | GPIO        |

| PF9      | 87     | GPIO                                                  | PD9      | 88     | GPIO        |

| PD10     | 89     | GPIO                                                  | PD11     | 90     | GPIO        |

| PD12     | 91     | GPIO                                                  | PE8      | 92     | GPIO        |

| PE9      | 93     | GPIO                                                  | PE10     | 94     | GPIO        |

| PE11     | 95     | GPIO                                                  | PE12     | 96     | GPIO        |

| PE13     | 97     | GPIO                                                  | PE14     | 98     | GPIO        |

| PE15     | 99     | GPIO                                                  | PA15     | 100    | GPIO        |

<sup>1.</sup> GPIO with 5V tolerance are indicated by (5V).

| Pin Name | Pin(s) | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                 |

|----------|--------|-------------------------------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                          | PC5      | 14     | GPIO                                                                                                                                                                                        |

| PB7      | 15     | GPIO                          | PB8      | 16     | GPIO                                                                                                                                                                                        |

| PA8      | 17     | GPIO                          | PA12     | 18     | GPIO (5V)                                                                                                                                                                                   |

| PA14     | 19     | GPIO                          | RESETn   | 20     | Reset input, active low. To apply an external reset source to this pin, it is required to only drive this pin low during reset, and let the internal pull-up ensure that reset is released. |

| PB11     | 21     | GPIO                          | PB12     | 22     | GPIO                                                                                                                                                                                        |

| AVDD     | 24     | Analog power supply.          | PB13     | 25     | GPIO                                                                                                                                                                                        |

| PB14     | 26     | GPIO                          | PD0      | 28     | GPIO (5V)                                                                                                                                                                                   |

| PD1      | 29     | GPIO                          | PD2      | 30     | GPIO (5V)                                                                                                                                                                                   |

| PD3      | 31     | GPIO                          | PD4      | 32     | GPIO                                                                                                                                                                                        |

| PD5      | 33     | GPIO                          | PD6      | 34     | GPIO                                                                                                                                                                                        |

| PD7      | 35     | GPIO                          | PD8      | 36     | GPIO                                                                                                                                                                                        |

| PC7      | 37     | GPIO                          | VREGVSS  | 38     | Voltage regulator VSS                                                                                                                                                                       |

| VREGSW   | 39     | DCDC regulator switching node | VREGVDD  | 40     | Voltage regulator VDD input                                                                                                                                                                 |

| DVDD     | 41     | Digital power supply.         | DECOUPLE | 42     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                    |

| PE4      | 43     | GPIO                          | PE5      | 44     | GPIO                                                                                                                                                                                        |

| PE6      | 45     | GPIO                          | PE7      | 46     | GPIO                                                                                                                                                                                        |

| PC12     | 47     | GPIO (5V)                     | PC13     | 48     | GPIO (5V)                                                                                                                                                                                   |

| PF0      | 49     | GPIO (5V)                     | PF1      | 50     | GPIO (5V)                                                                                                                                                                                   |

| PF2      | 51     | GPIO                          | PF3      | 52     | GPIO                                                                                                                                                                                        |

| PF4      | 53     | GPIO                          | PF5      | 54     | GPIO                                                                                                                                                                                        |

| PE8      | 57     | GPIO                          | PE9      | 58     | GPIO                                                                                                                                                                                        |

| PE10     | 59     | GPIO                          | PE11     | 60     | GPIO                                                                                                                                                                                        |

| PE12     | 61     | GPIO                          | PE13     | 62     | GPIO                                                                                                                                                                                        |

| PE14     | 63     | GPIO                          | PE15     | 64     | GPIO                                                                                                                                                                                        |

<sup>1.</sup> GPIO with 5V tolerance are indicated by (5V).

| GPIO Name |                                                               | Pin Alteri                                                          | nate Functionality / De                                                            | escription                                                                                              |                                                         |

|-----------|---------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

|           | Analog                                                        | EBI                                                                 | Timers                                                                             | Communication                                                                                           | Other                                                   |

| PD4       | BUSADC0Y BU-<br>SADC0X OPA2_P                                 | EBI_A08 #1 EBI_A17<br>#3                                            | TIM6_CC0 #7<br>WTIM0_CDTI0 #4<br>WTIM1_CC2 #1<br>WTIM2_CC1 #5                      | CAN1_TX #2<br>US1_CTS #1<br>US3_CLK #2<br>LEU0_TX #0<br>I2C1_SDA #3                                     | CMU_CLKI0 #0<br>PRS_CH10 #2<br>ETM_TD2 #0<br>ETM_TD2 #2 |

| PC0       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #0<br>BUSACMP0Y BU-<br>SACMP0X | EBI_AD07 #1<br>EBI_CS0 #2<br>EBI_REn #3<br>EBI_A23 #0               | TIM0_CC1 #3<br>TIM2_CC1 #4<br>PCNT0_S0IN #2                                        | ETH_MDIO #2<br>CAN0_RX #0<br>US0_TX #5 US1_TX<br>#0 US1_CS #4<br>US2_RTS #0<br>US3_CS #3<br>I2C0_SDA #4 | LES_CH0 PRS_CH2<br>#0                                   |

| PC1       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #1<br>BUSACMP0Y BU-<br>SACMP0X | EBI_AD08 #1<br>EBI_CS1 #2<br>EBI_BL0 #3 EBI_A24<br>#0               | TIM0_CC2 #3<br>TIM2_CC2 #4<br>WTIM0_CC0 #7<br>PCNT0_S1IN #2                        | ETH_MDC #2<br>CAN0_TX #0<br>US0_RX #5 US1_TX<br>#4 US1_RX #0<br>US2_CTS #0<br>US3_RTS #1<br>I2C0_SCL #4 | LES_CH1 PRS_CH3<br>#0                                   |

| PC2       | VDAC0_OUT0ALT /<br>OPA0_OUTALT #2<br>BUSACMP0Y BU-<br>SACMP0X | EBI_AD09 #1<br>EBI_CS2 #2<br>EBI_NANDWEn #3<br>EBI_A25 #0           | TIM0_CDTI0 #3<br>TIM2_CC0 #5<br>WTIM0_CC1 #7 LE-<br>TIM1_OUT0 #3                   | ETH_TSUEXTCLK<br>#2 CAN1_RX #0<br>US1_RX #4 US2_TX<br>#0                                                | LES_CH2<br>PRS_CH10 #1                                  |

| PA8       | BUSBY BUSAX<br>LCD_SEG36                                      | EBI_AD14 #1<br>EBI_A02 #3<br>EBI_DCLK #0                            | TIM2_CC0 #0<br>TIM0_CC0 #6 LE-<br>TIM0_OUT0 #6<br>PCNT1_S1IN #4                    | US2_RX #2<br>US4_RTS #0                                                                                 | PRS_CH8 #0                                              |

| PA11      | BUSAY BUSBX<br>LCD_SEG39                                      | EBI_CS1 #1<br>EBI_A05 #3<br>EBI_HSNC #0                             | WTIM2_CC2 #0 LE-<br>TIM1_OUT0 #1                                                   | US2_CTS #2                                                                                              | PRS_CH11 #0                                             |

| PA13      | BUSAY BUSBX                                                   | EBI_WEn #1<br>EBI_NANDWEn #2<br>EBI_A01 #0 EBI_A07<br>#3            | TIM0_CC2 #7 TIM2_CC1 #1 WTIM0_CDTI1 #2 WTIM2_CC1 #1 LE- TIM1_OUT1 #1 PCNT1_S1IN #5 | CAN1_TX #5<br>US0_CS #5 US2_TX<br>#3                                                                    | PRS_CH13 #0                                             |

| PB9       | BUSAY BUSBX                                                   | EBI_ALE #1<br>EBI_NANDREn #2<br>EBI_A00 #1 EBI_A03<br>#0 EBI_A09 #3 | WTIM2_CC0 #2 LE-<br>TIM0_OUT0 #7                                                   | SDIO_WP #3<br>CAN0_RX #3<br>US1_CTS #0 U1_TX<br>#2                                                      | PRS_CH13 #1<br>ACMP1_O #5                               |

| PB12      | BUSBY BUSAX<br>VDAC0_OUT1 /<br>OPA1_OUT                       | EBI_A03 #1 EBI_A12<br>#3 EBI_CSTFT #2                               | TIM1_CC3 #3<br>WTIM2_CC0 #3 LE-<br>TIM0_OUT1 #1<br>PCNT0_S0IN #7<br>PCNT1_S1IN #6  | US2_CTS #1<br>US5_RTS #0<br>U1_RTS #2<br>I2C1_SCL #1                                                    | PRS_CH16 #1                                             |

| PH2       | BUSADC1Y BU-<br>SADC1X                                        | EBI_VSNC #2                                                         | TIM6_CC0 #3                                                                        | US1_CTS #6                                                                                              |                                                         |

| PH5       | BUSADC1Y BU-<br>SADC1X                                        | EBI_A17 #2                                                          | TIM6_CDTI0 #3<br>WTIM2_CC1 #6                                                      | US4_RX #4                                                                                               |                                                         |

| PH8       | BUSACMP3Y BU-<br>SACMP3X                                      | EBI_A20 #2                                                          | TIM6_CC0 #4<br>WTIM1_CC0 #6<br>WTIM2_CC1 #7                                        | US4_CTS #4                                                                                              |                                                         |

| Alternate     | LOCA    | ATION |                                    |

|---------------|---------|-------|------------------------------------|

| Functionality | 0 - 3   | 4 - 7 | Description                        |

| LCD_SEG33     | 0: PB1  |       | LCD segment line 33.               |

| LCD_SEG34     | 0: PB2  |       | LCD segment line 34.               |

| LCD_SEG35     | 0: PA7  |       | LCD segment line 35.               |

| LCD_SEG36     | 0: PA8  |       | LCD segment line 36.               |

| LCD_SEG37     | 0: PA9  |       | LCD segment line 37.               |

| LCD_SEG38     | 0: PA10 |       | LCD segment line 38.               |

| LCD_SEG39     | 0: PA11 |       | LCD segment line 39.               |

| LES_ALTEX0    | 0: PD6  |       | LESENSE alternate excite output 0. |

| LES_ALTEX1    | 0: PD7  |       | LESENSE alternate excite output 1. |

| LES_ALTEX2    | 0: PA3  |       | LESENSE alternate excite output 2. |

| LES_ALTEX3    | 0: PA4  |       | LESENSE alternate excite output 3. |

| LES_ALTEX4    | 0: PA5  |       | LESENSE alternate excite output 4. |

| LES_ALTEX5    | 0: PE11 |       | LESENSE alternate excite output 5. |

# Table 5.26. ACMP3 Bus and Pin Mapping

| Port    | Bus       | CH31 | CH30 | CH29 | CH28 | CH27 | CH26 | CH25 | CH24 | CH23 | CH22 | CH21 | CH20 | CH19 | CH18 | CH17 | CH16 | CH15 | CH14 | CH13 | CH12 | CH11 | CH10 | СНЭ | СН8 | CH7  | СН6  | СН5  | CH4  | СНЗ  | CH2  | CH1 | СНО |

|---------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|-----|-----|

| APORT0X | BUSACMP3X |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PH15 | PH14 | PH13 | PH12 | PH11 | PH10 | PH9 | PH8 |

| APORT0Y | BUSACMP3Y |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |     |     | PH15 | PH14 | PH13 | PH12 | PH11 | PH10 | 6НА | PH8 |

| APORT1X | BUSAX     |      | PB14 |      | PB12 |      | PB10 |      |      |      | PB6  |      | PB4  |      | PB2  |      | PB0  |      | PA14 |      | PA12 |      | PA10 |     | PA8 |      | PA6  |      | PA4  |      | PA2  |     | PA0 |

| APORT1Y | BUSAY     | PB15 |      | PB13 |      | PB11 |      | PB9  |      |      |      | PB5  |      | PB3  |      | PB1  |      | PA15 |      | PA13 |      | PA11 |      | PA9 |     | PA7  |      | PA5  |      | PA3  |      | PA1 |     |

| APORT2X | BUSBX     | PB15 |      | PB13 |      | PB11 |      | PB9  |      |      |      | PB5  |      | PB3  |      | PB1  |      | PA15 |      | PA13 |      | PA11 |      | PA9 |     | PA7  |      | PA5  |      | PA3  |      | PA1 |     |

| APORT2Y | BUSBY     |      | PB14 |      | PB12 |      | PB10 |      |      |      | PB6  |      | PB4  |      | PB2  |      | PB0  |      | PA14 |      | PA12 |      | PA10 |     | PA8 |      | PA6  |      | PA4  |      | PA2  |     | PA0 |

| APORT3X | BUSCX     |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |      | PE6  |      | PE4  |      |      |     | PE0 |

| APORT3Y | BUSCY     | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7  |      | PE5  |      |      |      | PE1 |     |

| APORT4X | BUSDX     | PF15 |      | PF13 |      | PF11 |      | PF9  |      | PF7  |      | PF5  |      | PF3  |      | PF1  |      | PE15 |      | PE13 |      | PE11 |      | PE9 |     | PE7  |      | PE5  |      |      |      | PE1 |     |

| APORT4Y | BUSDY     |      | PF14 |      | PF12 |      | PF10 |      | PF8  |      | PF6  |      | PF4  |      | PF2  |      | PF0  |      | PE14 |      | PE12 |      | PE10 |     | PE8 |      | PE6  |      | PE4  |      |      |     | PE0 |

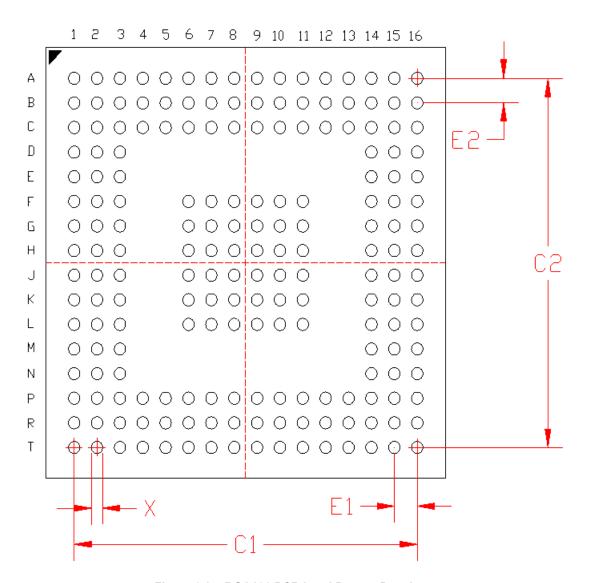

### 6.2 BGA192 PCB Land Pattern

Figure 6.2. BGA192 PCB Land Pattern Drawing

Table 7.2. BGA152 PCB Land Pattern Dimensions

| Dimension | Min  | Nom | Max |

|-----------|------|-----|-----|

| X         | 0.20 |     |     |

| C1        | 6.50 |     |     |

| C2        | 6.50 |     |     |

| E1        | 0.5  |     |     |

| E2        | 0.5  |     |     |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

- 5. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 6. The stencil thickness should be 0.125 mm (5 mils).

- 7. The ratio of stencil aperture to land pad size should be 1:1.

- 8. A No-Clean, Type-3 solder paste is recommended.

- 9. The recommended card reflow profile is per the JEDEC/IPC J-STD-020C specification for Small Body Components.

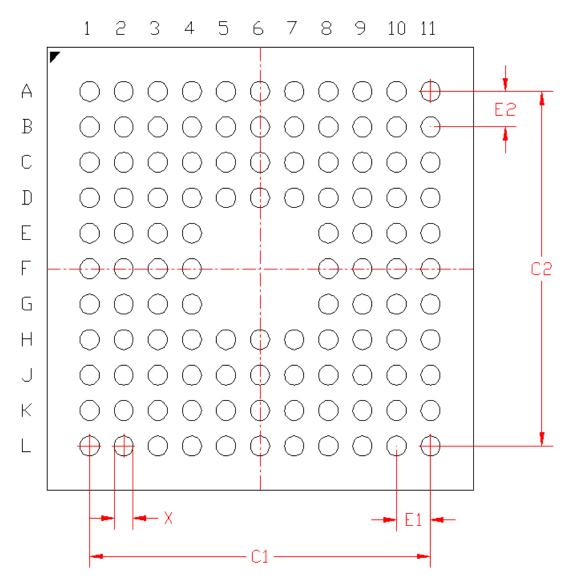

Table 9.1. BGA112 Package Dimensions

| Min       | Тур               | Max  |

|-----------|-------------------|------|

| -         | -                 | 1.30 |

| 0.55      | 0.60              | 0.65 |

| 0.21 BSC  |                   |      |

| 0.30      | 0.35              | 0.40 |

| 0.43      | 0.48              | 0.53 |

| 10.00 BSC |                   |      |

| 8.00 BSC  |                   |      |

| 10.00 BSC |                   |      |

| 8.00 BSC  |                   |      |

| 0.80 BSC  |                   |      |

| 0.80 BSC  |                   |      |

| 1.00 REF  |                   |      |

| 1.00 REF  |                   |      |

|           | -<br>0.55<br>0.30 |      |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 9.2 BGA112 PCB Land Pattern

Figure 9.2. BGA112 PCB Land Pattern Drawing

Table 11.2. TQFP64 PCB Land Pattern Dimensions

| Dimension | Min      | Max   |  |

|-----------|----------|-------|--|

| C1        | 11.30    | 11.40 |  |

| C2        | 11.30    | 11.40 |  |

| E         | 0.50 BSC |       |  |

| Х         | 0.20     | 0.30  |  |

| Y         | 1.40     | 1.50  |  |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 μm minimum, all the way around the pad.

- 4. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size can be 1:1 for all pads.

- 7. A No-Clean, Type-3 solder paste is recommended.

- 8. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

### 11.3 TQFP64 Package Marking

Figure 11.3. TQFP64 Package Marking

The package marking consists of:

- PPPPPPPPP The part number designation.

- TTTTTT A trace or manufacturing code. The first letter is the device revision.

- YY The last 2 digits of the assembly year.

- WW The 2-digit workweek when the device was assembled.