Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Betuno                     |                                                                                                               |

|----------------------------|---------------------------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                                      |

| Core Processor             | ARM® Cortex®-M4                                                                                               |

| Core Size                  | 32-Bit Single-Core                                                                                            |

| Speed                      | 72MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SmartCard, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                                                               |

| Number of I/O              | 121                                                                                                           |

| Program Memory Size        | 2MB (2M x 8)                                                                                                  |

| Program Memory Type        | FLASH                                                                                                         |

| EEPROM Size                | -                                                                                                             |

| RAM Size                   | 512K x 8                                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.8V                                                                                                   |

| Data Converters            | A/D 16x12b SAR; D/A 2x12b                                                                                     |

| Oscillator Type            | Internal                                                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                                            |

| Mounting Type              | Surface Mount                                                                                                 |

| Package / Case             | 152-VFBGA                                                                                                     |

| Supplier Device Package    | 152-BGA (8x8)                                                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32gg11b820f2048il152-ar                                  |

|                            |                                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ordering Code             | Flash<br>(kB) | RAM<br>(kB) | DC-DC Converter | USB | Ethernet | QSPI | SDIO | LCD | GPIO | Package | Temp Range    |

|---------------------------|---------------|-------------|-----------------|-----|----------|------|------|-----|------|---------|---------------|

| EFM32GG11B520F2048GQ64-A  | 2048          | 512         | Yes             | No  | No       | No   | No   | Yes | 50   | QFP64   | -40 to +85°C  |

| EFM32GG11B510F2048GQ64-A  | 2048          | 384         | Yes             | No  | No       | No   | No   | Yes | 50   | QFP64   | -40 to +85°C  |

| EFM32GG11B520F2048GM64-A  | 2048          | 512         | Yes             | No  | No       | No   | No   | Yes | 53   | QFN64   | -40 to +85°C  |

| EFM32GG11B510F2048GM64-A  | 2048          | 384         | Yes             | No  | No       | No   | No   | Yes | 53   | QFN64   | -40 to +85°C  |

| EFM32GG11B520F2048IQ64-A  | 2048          | 512         | Yes             | No  | No       | No   | No   | Yes | 50   | QFP64   | -40 to +125°C |

| EFM32GG11B510F2048IQ64-A  | 2048          | 384         | Yes             | No  | No       | No   | No   | Yes | 50   | QFP64   | -40 to +125°C |

| EFM32GG11B520F2048IM64-A  | 2048          | 512         | Yes             | No  | No       | No   | No   | Yes | 53   | QFN64   | -40 to +125°C |

| EFM32GG11B510F2048IM64-A  | 2048          | 384         | Yes             | No  | No       | No   | No   | Yes | 53   | QFN64   | -40 to +125°C |

| EFM32GG11B420F2048GL120-A | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 93   | BGA120  | -40 to +85°C  |

| EFM32GG11B420F2048IL120-A | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 93   | BGA120  | -40 to +125°C |

| EFM32GG11B420F2048GL112-A | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 87   | BGA112  | -40 to +85°C  |

| EFM32GG11B420F2048IL112-A | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 87   | BGA112  | -40 to +125°C |

| EFM32GG11B420F2048GQ100-A | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 83   | QFP100  | -40 to +85°C  |

| EFM32GG11B420F2048IQ100-A | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 83   | QFP100  | -40 to +125°C |

| EFM32GG11B420F2048GQ64-A  | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 50   | QFP64   | -40 to +85°C  |

| EFM32GG11B420F2048GM64-A  | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 53   | QFN64   | -40 to +85°C  |

| EFM32GG11B420F2048IQ64-A  | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 50   | QFP64   | -40 to +125°C |

| EFM32GG11B420F2048IM64-A  | 2048          | 512         | No              | Yes | Yes      | Yes  | Yes  | Yes | 53   | QFN64   | -40 to +125°C |

| EFM32GG11B320F2048GL112-A | 2048          | 512         | No              | No  | No       | No   | No   | Yes | 90   | BGA112  | -40 to +85°C  |

| EFM32GG11B310F2048GL112-A | 2048          | 384         | No              | No  | No       | No   | No   | Yes | 90   | BGA112  | -40 to +85°C  |

| EFM32GG11B320F2048GQ100-A | 2048          | 512         | No              | No  | No       | No   | No   | Yes | 86   | QFP100  | -40 to +85°C  |

| EFM32GG11B310F2048GQ100-A | 2048          | 384         | No              | No  | No       | No   | No   | Yes | 86   | QFP100  | -40 to +85°C  |

| EFM32GG11B120F2048GQ64-A  | 2048          | 512         | No              | No  | No       | No   | No   | No  | 53   | QFP64   | -40 to +85°C  |

| EFM32GG11B110F2048GQ64-A  | 2048          | 384         | No              | No  | No       | No   | No   | No  | 53   | QFP64   | -40 to +85°C  |

| EFM32GG11B120F2048GM64-A  | 2048          | 512         | No              | No  | No       | No   | No   | No  | 56   | QFN64   | -40 to +85°C  |

| EFM32GG11B110F2048GM64-A  | 2048          | 384         | No              | No  | No       | No   | No   | No  | 56   | QFN64   | -40 to +85°C  |

| EFM32GG11B120F2048IQ64-A  | 2048          | 512         | No              | No  | No       | No   | No   | No  | 53   | QFP64   | -40 to +125°C |

| EFM32GG11B110F2048IQ64-A  | 2048          | 384         | No              | No  | No       | No   | No   | No  | 53   | QFP64   | -40 to +125°C |

| EFM32GG11B120F2048IM64-A  | 2048          | 512         | No              | No  | No       | No   | No   | No  | 56   | QFN64   | -40 to +125°C |

| EFM32GG11B110F2048IM64-A  | 2048          | 384         | No              | No  | No       | No   | No   | No  | 56   | QFN64   | -40 to +125°C |

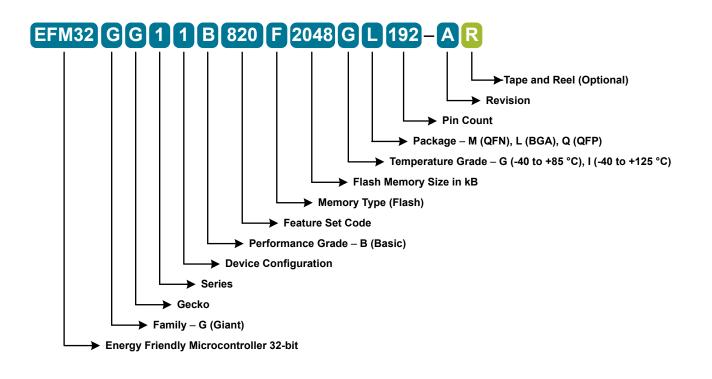

Figure 2.1. Ordering Code Key

#### 3.8.4 Capacitive Sense (CSEN)

The CSEN module is a dedicated Capacitive Sensing block for implementing touch-sensitive user interface elements such a switches and sliders. The CSEN module uses a charge ramping measurement technique, which provides robust sensing even in adverse conditions including radiated noise and moisture. The module can be configured to take measurements on a single port pin or scan through multiple pins and store results to memory through DMA. Several channels can also be shorted together to measure the combined capacitance or implement wake-on-touch from very low energy modes. Hardware includes a digital accumulator and an averaging filter, as well as digital threshold comparators to reduce software overhead.

#### 3.8.5 Digital to Analog Current Converter (IDAC)

The Digital to Analog Current Converter can source or sink a configurable constant current. This current can be driven on an output pin or routed to the selected ADC input pin for capacitive sensing. The full-scale current is programmable between 0.05  $\mu$ A and 64  $\mu$ A with several ranges consisting of various step sizes.

#### 3.8.6 Digital to Analog Converter (VDAC)

The Digital to Analog Converter (VDAC) can convert a digital value to an analog output voltage. The VDAC is a fully differential, 500 ksps, 12-bit converter. The opamps are used in conjunction with the VDAC, to provide output buffering. One opamp is used per singleended channel, or two opamps are used to provide differential outputs. The VDAC may be used for a number of different applications such as sensor interfaces or sound output. The VDAC can generate high-resolution analog signals while the MCU is operating at low frequencies and with low total power consumption. Using DMA and a timer, the VDAC can be used to generate waveforms without any CPU intervention. The VDAC is available in all energy modes down to and including EM3.

#### 3.8.7 Operational Amplifiers

The opamps are low power amplifiers with a high degree of flexibility targeting a wide variety of standard opamp application areas, and are available down to EM3. With flexible built-in programming for gain and interconnection they can be configured to support multiple common opamp functions. All pins are also available externally for filter configurations. Each opamp has a rail to rail input and a rail to rail output. They can be used in conjunction with the VDAC module or in stand-alone configurations. The opamps save energy, PCB space, and cost as compared with standalone opamps because they are integrated on-chip.

#### 3.8.8 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 8x36 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. A patented charge redistribution driver can reduce the LCD module supply current by up to 40%. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

#### 3.9 Reset Management Unit (RMU)

The RMU is responsible for handling reset of the EFM32GG11. A wide range of reset sources are available, including several power supply monitors, pin reset, software controlled reset, core lockup reset, and watchdog reset.

### 3.10 Core and Memory

#### 3.10.1 Processor Core

The ARM Cortex-M processor includes a 32-bit RISC processor integrating the following features and tasks in the system:

- ARM Cortex-M4 RISC processor with FPU achieving 1.25 Dhrystone MIPS/MHz

- Memory Protection Unit (MPU) supporting up to 8 memory segments

- Embedded Trace Macrocell (ETM) for real-time trace and debug

- Up to 2048 kB flash program memory

- · Dual-bank memory with read-while-write support

- Up to 512 kB RAM data memory

- · Configuration and event handling of all modules

- · 2-pin Serial-Wire or 4-pin JTAG debug interface

# 4. Electrical Specifications

## 4.1 Electrical Characteristics

All electrical parameters in all tables are specified under the following conditions, unless stated otherwise:

- Typical values are based on  $T_{AMB}$ =25 °C and  $V_{DD}$ = 3.3 V, by production test and/or technology characterization.

- Minimum and maximum values represent the worst conditions across supply voltage, process variation, and operating temperature, unless stated otherwise.

Refer to 4.1.2.1 General Operating Conditions for more details about operational supply and temperature limits.

| Parameter                                                                              | Symbol               | Test Condition                                                                                          | Min                                    | Тур  | Мах | Unit |

|----------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------|------|-----|------|

| Current consumption in EM2 mode, with voltage scaling                                  | I <sub>EM2_VS</sub>  | Full 512 kB RAM retention and RTCC running from LFXO                                                    | _                                      | 3.9  | _   | μA   |

| enabled                                                                                |                      | Full 512 kB RAM retention and RTCC running from LFRCO                                                   | —                                      | 4.3  | _   | μA   |

|                                                                                        |                      | 16 kB (1 bank) RAM retention and RTCC running from LFRCO <sup>2</sup>                                   | 16 kB (1 bank) RAM retention and — 2.8 |      | TBD | μA   |

| Current consumption in EM3<br>mode, with voltage scaling<br>enabled                    | I <sub>EM3_VS</sub>  | Full 512 kB RAM retention and<br>CRYOTIMER running from ULFR-<br>CO                                     | _                                      | 3.6  | TBD | μA   |

| Current consumption in<br>EM4H mode, with voltage                                      | I <sub>EM4H_VS</sub> | 128 byte RAM retention, RTCC running from LFXO                                                          | _                                      | 1.08 | _   | μA   |

| scaling enabled                                                                        |                      | 128 byte RAM retention, CRYO-<br>TIMER running from ULFRCO                                              | —                                      | 0.69 | _   | μA   |

|                                                                                        |                      | 128 byte RAM retention, no RTCC                                                                         | _                                      | 0.69 | TBD | μA   |

| Current consumption in EM4S mode                                                       | I <sub>EM4S</sub>    | No RAM retention, no RTCC                                                                               | _                                      | 0.16 | TBD | μA   |

| Current consumption of pe-<br>ripheral power domain 1,<br>with voltage scaling enabled | I <sub>PD1_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 1 are enabled <sup>1</sup> | _                                      | 0.68 | _   | μA   |

| Current consumption of pe-<br>ripheral power domain 2,<br>with voltage scaling enabled | I <sub>PD2_VS</sub>  | Additional current consumption in EM2/3 when any peripherals on power domain 2 are enabled <sup>1</sup> | _                                      | 0.28 | _   | μA   |

Note:

1. Extra current consumed by power domain. Does not include current associated with the enabled peripherals. See 3.2.4 EM2 and EM3 Power Domains for a list of the peripherals in each power domain.

2. CMU\_LFRCOCTRL\_ENVREF = 1, CMU\_LFRCOCTRL\_VREFUPDATE = 1

| Parameter                     | Symbol                                         | Test Condition                                                           | Min                   | Тур             | Max            | Unit      |

|-------------------------------|------------------------------------------------|--------------------------------------------------------------------------|-----------------------|-----------------|----------------|-----------|

| Note:                         |                                                |                                                                          | l                     |                 |                |           |

| 1. Supply current s the load. | specifications are for VD                      | AC circuitry operating with static o                                     | output only and do n  | not include cur | rent required  | to drive  |

|                               | ode, the output is define<br>ngle-ended range. | d as the difference between two s                                        | ingle-ended outputs   | s. Absolute vol | tage on each   | output is |

| 3. Entire range is r          | monotonic and has no m                         | issing codes.                                                            |                       |                 |                |           |

|                               | PERCLK is dependent<br>DAC module is enabled   | on HFPERCLK frequency. This cuint in the CMU.                            | urrent contributes to | the total supp  | ly current use | ed when   |

|                               | , U I                                          | be from 10% to 90% of full scale.<br>It 10% of full scale with the measu |                       | by comparing    | actual VDAC    | output a  |

|                               |                                                | ΔV <sub>OUT</sub> ), VDAC output at 90% of f                             |                       |                 |                |           |

| Parameter                                               | Symbol                          | Test Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Min                        | Тур                       | Мах                       | Unit                  |

|---------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|---------------------------|-----------------------|

| Note:                                                   |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                           |                           |                       |

| 1. Specified configurate<br>V. Nominal voltage          |                                 | figuration is: INCBW = 1, HCMDIS = 1,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | , RESINSEL =               | VSS, V <sub>INPUT</sub> = | = 0.5 V, V <sub>OUT</sub> | <sub>FPUT</sub> = 1.5 |

| 2. If the maximum C <sub>LC</sub>                       | AD is exceeded, an              | isolation resistor is required for stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | y. See AN0038              | for more infor            | mation.                   |                       |

| 3. When INCBW is se<br>or the OPAMP may                 |                                 | indwidth is increased. This is allowed o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | only when the r            | non-inverting c           | lose-loop ga              | in is ≥ 3,            |

| drive the resistor fe                                   | edback network. The             | d. When the OPAMP is connected with<br>e internal resistor feedback network has<br>IP drives 1.5 V between output and groups of the state | s total resistan           |                           |                           |                       |

| 5. Step between 0.2V                                    | and V <sub>OPA</sub> -0.2V, 10% | 6-90% rising/falling range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |                           |                           |                       |

| 6. From enable to out                                   | out settled. In sample          | e-and-off mode, RC network after OPA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MP will contrib            | oute extra dela           | y. Settling er            | ror < 1mV             |

|                                                         |                                 | -bandwidth product of the OPAMP. In 3 ion of the feedback network.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3x Gain conne              | ction, UGF is t           | he gain-band              | dwidth                |

| 8. Specified configuration V <sub>OUTPUT</sub> = 0.5 V. | ion for Unit gain buff          | fer configuration is: INCBW = 0, HCME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DIS = 0, RESIN             | ISEL = DISAB              | LE. V <sub>INPUT</sub> =  | 0.5 V,                |

| 9 When HCMDIS=1 a                                       | nd input common m               | ode transitions the region from V <sub>OPA</sub> -1<br>o this transition region.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | .4V to V <sub>OPA</sub> -1 | V, input offset           | will change.              | PSRR                  |

# 4.1.20 LCD Driver

### Table 4.28. LCD Driver

| Parameter                                        | Symbol                                                | Test Condition                                 | Min                         | Тур  | Max                     | Unit |

|--------------------------------------------------|-------------------------------------------------------|------------------------------------------------|-----------------------------|------|-------------------------|------|

| Frame rate                                       | f <sub>LCDFR</sub>                                    |                                                | TBD                         | —    | TBD                     | Hz   |

| LCD supply range <sup>2</sup>                    | V <sub>LCDIN</sub>                                    |                                                | 1.8                         |      | 3.8                     | V    |

| LCD output voltage range                         | V <sub>LCD</sub>                                      | Current source mode, No external LCD capacitor | 2.0                         | _    | V <sub>LCDIN</sub> -0.4 | V    |

|                                                  |                                                       | Step-down mode with external LCD capacitor     | 2.0                         |      | V <sub>LCDIN</sub>      | V    |

|                                                  | Charge pump mode with external 2.0 —<br>LCD capacitor | _                                              | 1.9 *<br>V <sub>LCDIN</sub> | V    |                         |      |

| Contrast control step size                       | STEP <sub>CONTRAST</sub>                              | Current source mode                            | _                           | 64   | _                       | mV   |

|                                                  |                                                       | Charge pump or Step-down mode                  | _                           | 43   | _                       | mV   |

| Contrast control step accura-<br>cy <sup>1</sup> | ACC <sub>CONTRAST</sub>                               |                                                | _                           | +/-4 | —                       | %    |

| Noto                                             |                                                       | 1                                              |                             |      | · · ·                   |      |

### Note:

1. Step size accuracy is measured relative to the typical step size, and typ value represents one standard deviation.

2. V<sub>LCDIN</sub> is selectable between the AVDD or DVDD supply pins, depending on EMU\_PWRCTRL\_ANASW.

| Pin Name | Pin(s)          | Description          | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|-----------------|----------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PD8      | H8              | GPIO                 | PD5      | H9     | GPIO                                                                                                                                                                                                        |

| PD6      | H10             | GPIO                 | PD7      | H11    | GPIO                                                                                                                                                                                                        |

| PC1      | J1              | GPIO (5V)            | PC3      | J2     | GPIO (5V)                                                                                                                                                                                                   |

| PD15     | J3              | GPIO (5V)            | PA12     | J4     | GPIO (5V)                                                                                                                                                                                                   |

| PA9      | J5              | GPIO                 | PA10     | J6     | GPIO                                                                                                                                                                                                        |

| PB9      | J7              | GPIO (5V)            | PB10     | J8     | GPIO (5V)                                                                                                                                                                                                   |

| PD2      | J9              | GPIO (5V)            | PD3      | J10    | GPIO                                                                                                                                                                                                        |

| PD4      | J11             | GPIO                 | PB7      | K1     | GPIO                                                                                                                                                                                                        |

| PC4      | K2              | GPIO                 | PA13     | K3     | GPIO (5V)                                                                                                                                                                                                   |

| PA11     | K5              | GPIO                 | RESETn   | K6     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| AVDD     | K8<br>K9<br>L10 | Analog power supply. | PD1      | K11    | GPIO                                                                                                                                                                                                        |

| PB8      | L1              | GPIO                 | PC5      | L2     | GPIO                                                                                                                                                                                                        |

| PA14     | L3              | GPIO                 | PB11     | L5     | GPIO                                                                                                                                                                                                        |

| PB12     | L6              | GPIO                 | PB13     | L8     | GPIO                                                                                                                                                                                                        |

| PB14     | L9              | GPIO                 | PD0      | L11    | GPIO (5V)                                                                                                                                                                                                   |

# Note:

1. GPIO with 5V tolerance are indicated by (5V).

2. The pins PD13, PD14, and PD15 will not be 5V tolerant on all future devices. In order to preserve upgrade options with full hardware compatibility, do not use these pins with 5V domains.

| Pin Name | Pin(s) | Description                                           | Pin Name | Pin(s) | Description |

|----------|--------|-------------------------------------------------------|----------|--------|-------------|

| PF1      | 77     | GPIO (5V)                                             | PF2      | 78     | GPIO        |

| VBUS     | 79     | USB VBUS signal and auxiliary input to 5 V regulator. | PF12     | 80     | GPIO        |

| PF5      | 81     | GPIO                                                  | PF6      | 84     | GPIO        |

| PF7      | 85     | GPIO                                                  | PF8      | 86     | GPIO        |

| PF9      | 87     | GPIO                                                  | PD9      | 88     | GPIO        |

| PD10     | 89     | GPIO                                                  | PD11     | 90     | GPIO        |

| PD12     | 91     | GPIO                                                  | PE8      | 92     | GPIO        |

| PE9      | 93     | GPIO                                                  | PE10     | 94     | GPIO        |

| PE11     | 95     | GPIO                                                  | PE12     | 96     | GPIO        |

| PE13     | 97     | GPIO                                                  | PE14     | 98     | GPIO        |

| PE15     | 99     | GPIO                                                  | PA15     | 100    | GPIO        |

| Note:    |        |                                                       |          |        |             |

1. GPIO with 5V tolerance are indicated by (5V).

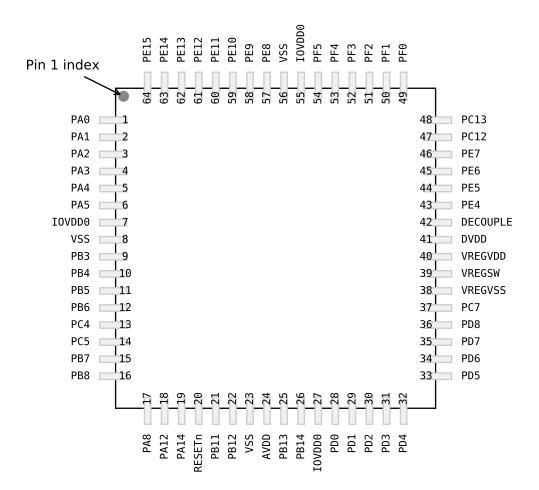

# Figure 5.13. EFM32GG11B5xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>27<br>55 | Digital IO power supply 0. | VSS      | 8<br>23<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

| Pin Name | Pin(s) | Description                   | Pin Name | Pin(s) | Description                                                                                                                                                                                                 |

|----------|--------|-------------------------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC4      | 13     | GPIO                          | PC5      | 14     | GPIO                                                                                                                                                                                                        |

| PB7      | 15     | GPIO                          | PB8      | 16     | GPIO                                                                                                                                                                                                        |

| PA8      | 17     | GPIO                          | PA12     | 18     | GPIO (5V)                                                                                                                                                                                                   |

| PA14     | 19     | GPIO                          | RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |

| PB11     | 21     | GPIO                          | PB12     | 22     | GPIO                                                                                                                                                                                                        |

| AVDD     | 24     | Analog power supply.          | PB13     | 25     | GPIO                                                                                                                                                                                                        |

| PB14     | 26     | GPIO                          | PD0      | 28     | GPIO (5V)                                                                                                                                                                                                   |

| PD1      | 29     | GPIO                          | PD2      | 30     | GPIO (5V)                                                                                                                                                                                                   |

| PD3      | 31     | GPIO                          | PD4      | 32     | GPIO                                                                                                                                                                                                        |

| PD5      | 33     | GPIO                          | PD6      | 34     | GPIO                                                                                                                                                                                                        |

| PD7      | 35     | GPIO                          | PD8      | 36     | GPIO                                                                                                                                                                                                        |

| PC7      | 37     | GPIO                          | VREGVSS  | 38     | Voltage regulator VSS                                                                                                                                                                                       |

| VREGSW   | 39     | DCDC regulator switching node | VREGVDD  | 40     | Voltage regulator VDD input                                                                                                                                                                                 |

| DVDD     | 41     | Digital power supply.         | DECOUPLE | 42     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    |

| PE4      | 43     | GPIO                          | PE5      | 44     | GPIO                                                                                                                                                                                                        |

| PE6      | 45     | GPIO                          | PE7      | 46     | GPIO                                                                                                                                                                                                        |

| PC12     | 47     | GPIO (5V)                     | PC13     | 48     | GPIO (5V)                                                                                                                                                                                                   |

| PF0      | 49     | GPIO (5V)                     | PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   |

| PF2      | 51     | GPIO                          | PF3      | 52     | GPIO                                                                                                                                                                                                        |

| PF4      | 53     | GPIO                          | PF5      | 54     | GPIO                                                                                                                                                                                                        |

| PE8      | 57     | GPIO                          | PE9      | 58     | GPIO                                                                                                                                                                                                        |

| PE10     | 59     | GPIO                          | PE11     | 60     | GPIO                                                                                                                                                                                                        |

| PE12     | 61     | GPIO                          | PE13     | 62     | GPIO                                                                                                                                                                                                        |

| PE14     | 63     | GPIO                          | PE15     | 64     | GPIO                                                                                                                                                                                                        |

1. GPIO with 5V tolerance are indicated by (5V).

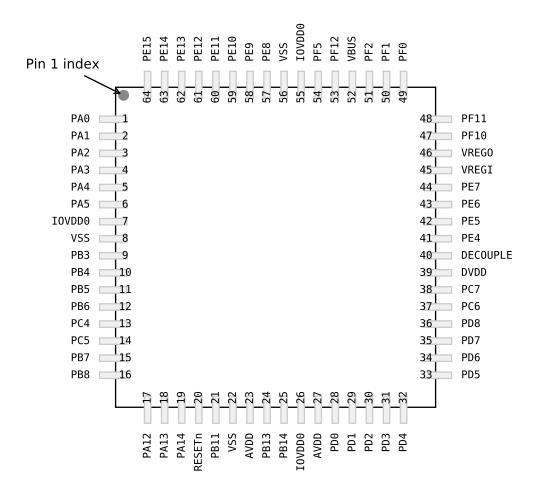

# Figure 5.14. EFM32GG11B4xx in QFP64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Table 5.14. EFM32GG11B4xx in QFP64 Device Pinout |

|--------------------------------------------------|

|--------------------------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s)        | Description |

|----------|---------------|----------------------------|----------|---------------|-------------|

| PA0      | 1             | GPIO                       | PA1      | 2             | GPIO        |

| PA2      | 3             | GPIO                       | PA3      | 4             | GPIO        |

| PA4      | 5             | GPIO                       | PA5      | 6             | GPIO        |

| IOVDD0   | 7<br>26<br>55 | Digital IO power supply 0. | VSS      | 8<br>22<br>56 | Ground      |

| PB3      | 9             | GPIO                       | PB4      | 10            | GPIO        |

| PB5      | 11            | GPIO                       | PB6      | 12            | GPIO        |

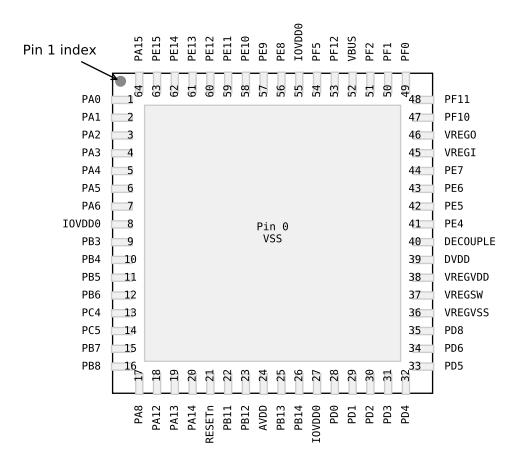

# Figure 5.16. EFM32GG11B8xx in QFN64 Device Pinout

The following table provides package pin connections and general descriptions of pin functionality. For detailed information on the supported features for each GPIO pin, see 5.20 GPIO Functionality Table or 5.21 Alternate Functionality Overview.

| Table 5.16. EFM32GG11B8xx in QFN64 Device Pinout |

|--------------------------------------------------|

|--------------------------------------------------|

| Pin Name | Pin(s)        | Description                | Pin Name | Pin(s) | Description |

|----------|---------------|----------------------------|----------|--------|-------------|

| VSS      | 0             | Ground                     | PA0      | 1      | GPIO        |

| PA1      | 2             | GPIO                       | PA2      | 3      | GPIO        |

| PA3      | 4             | GPIO                       | PA4      | 5      | GPIO        |

| PA5      | 6             | GPIO                       | PA6      | 7      | GPIO        |

| IOVDD0   | 8<br>27<br>55 | Digital IO power supply 0. | PB3      | 9      | GPIO        |

| PB4      | 10            | GPIO                       | PB5      | 11     | GPIO        |

| Pin Name | Pin(s) | Description                                                                                                                                                                                                 | Pin Name    | Pin(s)   | Description           |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------|-----------------------|

| PC3      | 12     | GPIO (5V)                                                                                                                                                                                                   | PC4         | 13       | GPIO                  |

| PC5      | 14     | GPIO                                                                                                                                                                                                        | PB7         | 15       | GPIO                  |

| PB8      | 16     | GPIO                                                                                                                                                                                                        | PA8         | 17       | GPIO                  |

| PA9      | 18     | GPIO                                                                                                                                                                                                        | PA10        | 19       | GPIO                  |

| RESETn   | 20     | Reset input, active low. To apply an ex-<br>ternal reset source to this pin, it is re-<br>quired to only drive this pin low during<br>reset, and let the internal pull-up ensure<br>that reset is released. |             | 21       | GPIO                  |

| PB12     | 22     | GPIO                                                                                                                                                                                                        | AVDD        | 23<br>27 | Analog power supply.  |

| PB13     | 24     | GPIO                                                                                                                                                                                                        | PB14        | 25       | GPIO                  |

| PD0      | 28     | GPIO (5V)                                                                                                                                                                                                   | PD1         | 29       | GPIO                  |

| PD2      | 30     | GPIO (5V)                                                                                                                                                                                                   | PD3         | 31       | GPIO                  |

| PD4      | 32     | GPIO                                                                                                                                                                                                        | PD5         | 33       | GPIO                  |

| PD6      | 34     | GPIO                                                                                                                                                                                                        | PD7         | 35       | GPIO                  |

| PD8      | 36     | GPIO                                                                                                                                                                                                        | PC6 37 GPIO |          | GPIO                  |

| PC7      | 38     | GPIO                                                                                                                                                                                                        | DVDD        | 39       | Digital power supply. |

| DECOUPLE | 40     | Decouple output for on-chip voltage regulator. An external decoupling capacitor is required at this pin.                                                                                                    | PC8         | 41       | GPIO (5V)             |

| PC9      | 42     | GPIO (5V)                                                                                                                                                                                                   | PC10        | 43       | GPIO (5V)             |

| PC11     | 44     | GPIO (5V)                                                                                                                                                                                                   | PC12        | 45       | GPIO (5V)             |

| PC13     | 46     | GPIO (5V)                                                                                                                                                                                                   | PC14        | 47       | GPIO (5V)             |

| PC15     | 48     | GPIO (5V)                                                                                                                                                                                                   | PF0         | 49       | GPIO (5V)             |

| PF1      | 50     | GPIO (5V)                                                                                                                                                                                                   | PF2         | 51       | GPIO                  |

| PF3      | 52     | GPIO                                                                                                                                                                                                        | PF4         | 53       | GPIO                  |

| PF5      | 54     | GPIO                                                                                                                                                                                                        | PE8         | 56       | GPIO                  |

| PE9      | 57     | GPIO                                                                                                                                                                                                        | PE10        | 58       | GPIO                  |

| PE11     | 59     | GPIO                                                                                                                                                                                                        | PE12        | 60       | GPIO                  |

| PE13     | 61     | GPIO                                                                                                                                                                                                        | PE14        | 62       | GPIO                  |

| PE15     | 63     | GPIO                                                                                                                                                                                                        | PA15        | 64       | GPIO                  |

1. GPIO with 5V tolerance are indicated by (5V).

| Alternate LOCATION |         | ATION |                                                                                                                                                                                  |  |  |

|--------------------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Functionality      | 0 - 3   | 4 - 7 | Description                                                                                                                                                                      |  |  |

|                    | 0: PA14 |       | LCD external supply bypass in step down or charge pump mode. If using the LCD in step-down or charge pump mode, a 1 uF (minimum) capacitor between this pin and VSS is required. |  |  |

| LCD_BEXT           |         |       | To reduce supply ripple, a larger capcitor of approximately 1000 times the total LCD segment capacitance may be used.                                                            |  |  |

|                    |         |       | If using the LCD with the internal supply source, this pin may be left unconnected or used as a GPIO.                                                                            |  |  |

|                    | 0: PE4  |       |                                                                                                                                                                                  |  |  |

| LCD_COM0           |         |       | LCD driver common line number 0.                                                                                                                                                 |  |  |

|                    | 0: PE5  |       |                                                                                                                                                                                  |  |  |

| LCD_COM1           |         |       | LCD driver common line number 1.                                                                                                                                                 |  |  |

|                    | 0: PE6  |       |                                                                                                                                                                                  |  |  |

| LCD_COM2           |         |       | LCD driver common line number 2.                                                                                                                                                 |  |  |

|                    | 0: PE7  |       |                                                                                                                                                                                  |  |  |

| LCD_COM3           |         |       | LCD driver common line number 3.                                                                                                                                                 |  |  |

|                    | 0: PF2  |       |                                                                                                                                                                                  |  |  |

| LCD_SEG0           |         |       | LCD segment line 0.                                                                                                                                                              |  |  |

|                    | 0: PF3  |       |                                                                                                                                                                                  |  |  |

| LCD_SEG1           |         |       | LCD segment line 1.                                                                                                                                                              |  |  |

|                    | 0: PF4  |       |                                                                                                                                                                                  |  |  |

| LCD_SEG2           |         |       | LCD segment line 2.                                                                                                                                                              |  |  |

|                    | 0: PF5  |       |                                                                                                                                                                                  |  |  |

| LCD_SEG3           |         |       | LCD segment line 3.                                                                                                                                                              |  |  |

|                    | 0: PE8  |       |                                                                                                                                                                                  |  |  |

| LCD_SEG4           |         |       | LCD segment line 4.                                                                                                                                                              |  |  |

|                    | 0: PE9  |       |                                                                                                                                                                                  |  |  |

| LCD_SEG5           |         |       | LCD segment line 5.                                                                                                                                                              |  |  |

|                    | 0: PE10 |       |                                                                                                                                                                                  |  |  |