Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                  |

| Core Processor             | M8C                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 24MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | LVD, POR, PWM, WDT                                                        |

| Number of I/O              | 24                                                                        |

| Program Memory Size        | 4KB (4K x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                |

| Data Converters            | A/D 2x14b; D/A 2x9b                                                       |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24423-24pi |

|                            |                                                                           |

|     |            | 3.5.5<br>3.5.6<br>3.5.7<br>3.5.8<br>3.5.9 | Destination Indexed  Destination Direct Source Immediate  Destination Indexed Source Immediate  Destination Direct Source Direct  Source Indirect Post Increment | 43<br>44<br>44 |

|-----|------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|     | 3.6        | 3.5.10<br>Register Def<br>3.6.1           | Destination Indirect Post IncrementinitionsCPU_F (Flag) Register                                                                                                 | 45             |

| 4.  | Supervi    | sory ROM (S                               | SROM)                                                                                                                                                            | 47             |

|     | 4.1        | Architectural                             | Description                                                                                                                                                      | 47             |

|     |            | 4.1.1                                     | Additional SROM Feature                                                                                                                                          |                |

|     | 4.0        | 4.1.2                                     | SROM Function Descriptions                                                                                                                                       |                |

|     | 4.2        | Register Det<br>4.2.1                     | initions                                                                                                                                                         |                |

|     | 4.3        |                                           | CPU_SCR1 Register                                                                                                                                                |                |

| _   |            | J                                         |                                                                                                                                                                  |                |

| 5.  | -          |                                           | Description                                                                                                                                                      |                |

|     | 5.1<br>5.2 |                                           | Descriptioninitions                                                                                                                                              |                |

|     | 5.2        | 5.2.1                                     | INT_CLRx Register                                                                                                                                                |                |

|     |            | 5.2.2                                     | INT_MSKx Register                                                                                                                                                |                |

|     |            | 5.2.3                                     | INT_VC Register                                                                                                                                                  |                |

|     |            | 5.2.4                                     | CPU_F Register                                                                                                                                                   |                |

| 6.  | Genera     | l Purnosa IC                              | (GPIO)                                                                                                                                                           | 57             |

| 0.  | 6.1        |                                           | Description                                                                                                                                                      |                |

|     | 0.1        | 6.1.1                                     | Digital IO                                                                                                                                                       |                |

|     |            | 6.1.2                                     | Global IO                                                                                                                                                        |                |

|     |            | 6.1.3                                     | Analog IO                                                                                                                                                        |                |

|     |            | 6.1.4                                     | GPIO Block Interrupts                                                                                                                                            | 58             |

|     | 6.2        | •                                         | initions                                                                                                                                                         |                |

|     |            | 6.2.1                                     | PRTxDR Registers                                                                                                                                                 |                |

|     |            | 6.2.2                                     | PRTxIE Registers                                                                                                                                                 |                |

|     |            | 6.2.3<br>6.2.4                            | PRTxDMx Pogistors                                                                                                                                                |                |

|     |            | 6.2.4<br>6.2.5                            | PRTxDMx Registers PRTxICx Registers                                                                                                                              |                |

|     |            |                                           |                                                                                                                                                                  |                |

| 7.  | •          |                                           | ers                                                                                                                                                              |                |

|     | 7.1        |                                           | Description                                                                                                                                                      |                |

|     | 7.2        | Register De                               | finitionsABF_CR0 Register                                                                                                                                        |                |

|     |            |                                           | •                                                                                                                                                                |                |

| 8.  |            |                                           | ator (IMO)                                                                                                                                                       |                |

|     | 8.1        |                                           | Description                                                                                                                                                      |                |

|     | 8.2        | -                                         | initions                                                                                                                                                         |                |

|     |            | 8.2.1                                     | IMO_TR Register                                                                                                                                                  |                |

| 9.  | Internal   |                                           | Oscillator (ILO)                                                                                                                                                 |                |

|     | 9.1        |                                           | Description                                                                                                                                                      |                |

|     | 9.2        | •                                         | initions                                                                                                                                                         |                |

|     |            | 9.2.1                                     | ILO_TR Register                                                                                                                                                  |                |

| 10. |            |                                           | llator (ECO)                                                                                                                                                     |                |

|     | 10.1       |                                           | Description                                                                                                                                                      |                |

|     | 40.0       | 10.1.1                                    | ECO External Components                                                                                                                                          |                |

|     | 10.2       | Register Def                              | initions                                                                                                                                                         |                |

|     |                              | 17.1.7                                                                                                                                                                                                             | Dead Band Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

|-----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|     |                              | 17.1.8                                                                                                                                                                                                             | CRCPRS Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

|     |                              | 17.1.9                                                                                                                                                                                                             | SPI Protocol Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

|     |                              | 17.1.10                                                                                                                                                                                                            | SPI Master Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 206          |

|     |                              | 17.1.11                                                                                                                                                                                                            | SPI Slave Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |

|     |                              | 17.1.12                                                                                                                                                                                                            | Asynchronous Transmitter Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 207          |

|     |                              | 17.1.13                                                                                                                                                                                                            | Asynchronous Receiver Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 207          |

|     | 17.2                         | Register Def                                                                                                                                                                                                       | initions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 208          |

|     |                              | 17.2.1                                                                                                                                                                                                             | DxBxxDRx Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 208          |

|     |                              | 17.2.2                                                                                                                                                                                                             | DxBxxCR0 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 213          |

|     |                              | 17.2.3                                                                                                                                                                                                             | INT_MSK1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 213          |

|     |                              | 17.2.4                                                                                                                                                                                                             | DxBxxFN Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 213          |

|     |                              | 17.2.5                                                                                                                                                                                                             | DxBxxIN Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 214          |

|     |                              | 17.2.6                                                                                                                                                                                                             | DxBxxOU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 214          |

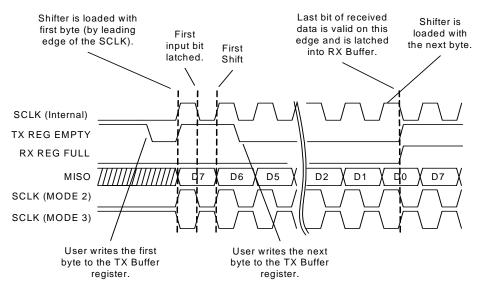

|     | 17.3                         | Timing Diagr                                                                                                                                                                                                       | ams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 214          |

|     |                              | 17.3.1                                                                                                                                                                                                             | Timer Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 215          |

|     |                              | 17.3.2                                                                                                                                                                                                             | Counter Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 216          |

|     |                              | 17.3.3                                                                                                                                                                                                             | Dead Band Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 216          |

|     |                              | 17.3.4                                                                                                                                                                                                             | CRCPRS Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 218          |

|     |                              | 17.3.5                                                                                                                                                                                                             | SPI Mode Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 218          |

|     |                              | 17.3.6                                                                                                                                                                                                             | SPIM Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 219          |

|     |                              | 17.3.7                                                                                                                                                                                                             | SPIS Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|     |                              | 17.3.8                                                                                                                                                                                                             | Transmitter Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 225          |

|     |                              | 17.3.9                                                                                                                                                                                                             | Receiver Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 226          |

|     |                              |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

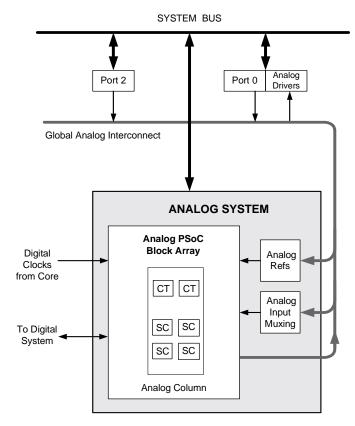

| SEC |                              | ALOG SYST                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 229          |

|     |                              |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | .,,,,        |

|     |                              |                                                                                                                                                                                                                    | chitecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

|     |                              |                                                                                                                                                                                                                    | nmary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| 1   | Analo                        | g Register Sum                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 231          |

| 1   | Analo                        | g Register Sum<br>Interface                                                                                                                                                                                        | nmary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 231          |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface                                                                                                                                                                                        | nmary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 231233233    |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural                                                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 231233233233 |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural<br>18.1.1                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2                                                                                                                                                   | Description Analog Data Bus Interface Analog Comparator Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3                                                                                                                                         | Description  Analog Data Bus Interface  Analog Comparator Bus Interface  Analog Column Clock Generation                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4                                                                                                                               | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface                                                                                                                                                                                                                                                                                                                                                                                                         |              |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| 1   | Analog<br>18. Analog         | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7                                                                                                 | Description  Analog Data Bus Interface  Analog Comparator Bus Interface  Analog Column Clock Generation  Decimator and Incremental ADC Interface  Analog Modulator Interface (Mod Bits)  Analog Synchronization Interface (Stalling)                                                                                                                                                                                                                                                                                                                 |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7                                                                                                 | Description  Analog Data Bus Interface  Analog Comparator Bus Interface  Analog Column Clock Generation  Decimator and Incremental ADC Interface  Analog Modulator Interface (Mod Bits)  Analog Synchronization Interface (Stalling)  SAR Hardware Acceleration                                                                                                                                                                                                                                                                                      |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def                                                                                 | Description Analog Data Bus Interface Analog Comparator Bus Interface. Analog Column Clock Generation. Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions CMP_CR0 Register                                                                                                                                                                                                                                                                 |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1                                                                       | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration                                                                                                                                                                                                                                                                                             |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2                                                             | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions CMP_CR0 Register CMP_CR1 Register                                                                                                                                                                                                                                                  |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2<br>18.2.3                                                   | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions  CMP_CR0 Register CMP_CR1 Register ASY_CR Register                                                                                                                                                                                                                                 |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2<br>18.2.3<br>18.2.4                                         | Description  Analog Data Bus Interface  Analog Comparator Bus Interface  Analog Column Clock Generation  Decimator and Incremental ADC Interface  Analog Modulator Interface (Mod Bits)  Analog Synchronization Interface (Stalling)  SAR Hardware Acceleration  initions  CMP_CR0 Register  CMP_CR1 Register  ASY_CR Register  DEC_CR0 Register                                                                                                                                                                                                     |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2<br>18.2.3<br>18.2.4<br>18.2.5                               | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions  CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR1 Register                                                                                                                                                                                               |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2<br>18.2.3<br>18.2.4<br>18.2.5<br>18.2.6                     | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions  CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR1 Register CLK_CR0 Register                                                                                                                                                                              |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2<br>18.2.3<br>18.2.4<br>18.2.5<br>18.2.6<br>18.2.7           | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions  CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR1 Register CLK_CR0 Register CLK_CR1 Register                                                                                                                                                             |              |

| 1   | Analo<br>18. Analog<br>18.1  | g Register Sum<br>Interface<br>Architectural<br>18.1.1<br>18.1.2<br>18.1.3<br>18.1.4<br>18.1.5<br>18.1.6<br>18.1.7<br>Register Def<br>18.2.1<br>18.2.2<br>18.2.3<br>18.2.4<br>18.2.5<br>18.2.6<br>18.2.7<br>18.2.8 | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR0 Register CLK_CR0 Register CLK_CR1 Register AMD_CR0 Register AMD_CR0 Register                                                                                                                            |              |

|     | Analog<br>18. Analog<br>18.1 | g Register Sum Interface Architectural 18.1.1 18.1.2 18.1.3 18.1.4 18.1.5 18.1.6 18.1.7 Register Def 18.2.1 18.2.2 18.2.3 18.2.4 18.2.5 18.2.6 18.2.7 18.2.8 18.2.9 18.2.10                                        | Description Analog Data Bus Interface Analog Comparator Bus Interface. Analog Column Clock Generation. Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions.  CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR0 Register CLK_CR0 Register CLK_CR0 Register AMD_CR0 Register AMD_CR1 Register |              |

|     | Analog<br>18. Analog<br>18.1 | g Register Sum Interface Architectural 18.1.1 18.1.2 18.1.3 18.1.4 18.1.5 18.1.6 18.1.7 Register Def 18.2.1 18.2.2 18.2.3 18.2.4 18.2.5 18.2.6 18.2.7 18.2.8 18.2.9 18.2.10 Array                                  | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions  CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR0 Register CLK_CR0 Register CLK_CR0 Register AMD_CR1 Register ALT_CR0 Register    |              |

|     | Analog<br>18. Analog<br>18.1 | g Register Sum Interface Architectural 18.1.1 18.1.2 18.1.3 18.1.4 18.1.5 18.1.6 18.1.7 Register Def 18.2.1 18.2.2 18.2.3 18.2.4 18.2.5 18.2.6 18.2.7 18.2.8 18.2.9 18.2.10  Array Architectural                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

|     | Analog<br>18. Analog<br>18.1 | g Register Sum Interface Architectural 18.1.1 18.1.2 18.1.3 18.1.4 18.1.5 18.1.6 18.1.7 Register Def 18.2.1 18.2.2 18.2.3 18.2.4 18.2.5 18.2.6 18.2.7 18.2.8 18.2.9 18.2.10  Array Architectural 19.1.1            | Description Analog Data Bus Interface Analog Comparator Bus Interface Analog Column Clock Generation Decimator and Incremental ADC Interface Analog Modulator Interface (Mod Bits) Analog Synchronization Interface (Stalling) SAR Hardware Acceleration initions  CMP_CR0 Register CMP_CR1 Register ASY_CR Register DEC_CR0 Register DEC_CR0 Register CLK_CR0 Register CLK_CR0 Register AMD_CR1 Register ALT_CR0 Register    |              |

# 3. CPU Core (M8C)

This chapter explains the CPU Core, called M8C, and its associated registers. It covers the internal M8C registers, address spaces, instruction formats, and addressing modes. For additional information concerning the M8C instruction set, reference the *Assembly Language User Guide* available at the Cypress.com web site.

Table 3-1. M8C Registers

| Address      | Name              | Bit 7      | Bit 6    | Bit 5   | Bit 4 | Bit 3  | Bit 2 | Bit 1         | Bit 0 | Access  |  |

|--------------|-------------------|------------|----------|---------|-------|--------|-------|---------------|-------|---------|--|

| M8C Register |                   |            |          |         |       |        |       |               |       |         |  |

| x,F7h        | CPU_F             |            |          |         | XOI   |        | Carry | Zero          | GIE   | RL:00   |  |

| Related Reg  | Related Registers |            |          |         |       |        |       |               |       |         |  |

| 1,E0h        | OSC_CR0           | 32k Select | PLL Mode | No Buzz | Sleep | o[1:0] | (     | CPU Speed[2:0 | ]     | RW:00   |  |

| x,FF         | CPU_SCR0          | GIES       |          | WDRS    | PORS  | Sleep  |       |               | STOP  | RW : 17 |  |

**LEGEND**

The M8C is a four MIPS 8-bit Harvard architecture microprocessor. Code selectable processor clock speeds from 93.7 kHz to 24 MHz allow the M8C to be tuned to a particular application's performance and power requirements. The M8C supports a rich instruction set which allows for efficient low-level language support.

## 3.1 Internal Registers

The M8C has five internal registers that are used in program execution. The following is a list of these registers.

- Accumulator (A)

- Index (X)

- Program Counter (PC) internal use only

- Stack Pointer (SP)

- Flags (F)

All of the internal M8C registers are eight bits in width except for the PC which is 16 bits wide. Upon reset, A, X, PC, and SP are reset to 00h. The Flag register (F) is reset to 02h, indicating that the Z flag is set.

With each stack operation, the SP is automatically incremented or decremented so that it always points to the next stack byte in RAM. If the last byte in the stack is at address FFh the Stack Pointer will wrap to RAM address 00h. It is the firmware developer's responsibility to ensure that the stack does not overlap with user-defined variables in RAM.

With the exception of the F register, the M8C internal registers are not accessible via an explicit register address. The internal M8C registers are accessed using instructions such as:

- MOV A, expr

- MOV X, expr

- SWAP A, SP

- OR F, expr

- JMP LABEL

The F register may be read by using address F7h in either register bank.

## 3.2 Address Spaces

The M8C has three address spaces: ROM, RAM, and registers. The ROM address space includes the supervisory ROM (SROM) and the Flash. The ROM address space is accessed via its own address and data bus. Figure 3-1 illustrates the arrangement of the PSoC microcontroller address spaces.

The ROM address space is composed of the Supervisory ROM and the on-chip Flash program store. Flash is organized into 64-byte blocks. The user need not be concerned with program store page boundaries, as the M8C automatically increments the 16-bit PC on every instruction making the block boundaries invisible to user code. Instructions occurring on a 256-byte Flash page boundary (with the

L: The AND, OR, and XOR flag instructions can be used to modify this register.

x: An "x" before the comma in the address field indicates that this register can be accessed or written to no matter what bank is used.

### 3.4 Instruction Format

The M8C has a total of seven instruction formats which use instruction lengths of one, two, and three bytes. All instruction bytes are fetched from the program memory (Flash) using an address and data bus that are independent from the address and data buses used for register and RAM access.

While examples of instructions will be given in this section, refer to the PSoC Designer Assembly Language User Guide for detailed information on individual instructions.

## 3.4.1 One-Byte Instructions

Many instructions, such as some of the MOV instructions, have single-byte forms because they do not use an address or data as an operand. As shown in Table 3-3, one-byte instructions use an 8-bit opcode. The set of one-byte instructions can be divided into four categories according to where their results are stored.

Table 3-3. One-Byte Instruction Format

| Byte 0       |

|--------------|

| 8-bit opcode |

The first category of one-byte instructions are those that do not update any registers or RAM. Only the one-byte NOP and SSC instructions fit this category. While the Program Counter is incremented as these instructions execute they do not cause any other internal M8C registers to be updated nor do these instructions directly affect the register space or the RAM address space. The SSC instruction will cause SROM code to run which will modify RAM and M8C internal registers.

The second category has only the two PUSH instructions in it. The PUSH instructions are unique because they are the only one-byte instructions that cause a RAM address to be modified. These instructions automatically increment the SP.

The third category has only the HALT instruction in it. The HALT instruction is unique because it is the only single-byte instruction that causes a user register to be modified. The HALT instruction modifies user register space address FFh (CPU SCR).

The final category for single-byte instructions are those that cause internal M8C registers to be updated. This category holds the largest number of instructions: ASL, ASR, CPL, DEC, INC, MOV, POP, RET, RETI, RLC, ROMX, RRC, SWAP. These instructions can cause the A, X, and SP registers or SRAM to be updated.

### 3.4.2 Two-Byte Instructions

The majority of M8C instructions are two bytes in length. While these instructions can be divided into categories identical to the one-byte instructions this would not provide a useful distinction between the three two-byte instruction formats that the M8C uses.

**Table 3-4. Two-Byte Instruction Formats**

| Byte         | e 0           | Byte 1        |  |  |

|--------------|---------------|---------------|--|--|

| 4-bit opcode | 12-bit relati | ve address    |  |  |

| 8-bit opcode |               | 8-bit data    |  |  |

| 8-bit opcode |               | 8-bit address |  |  |

The first two-byte instruction format shown in Table 3-4 is used by short jumps and calls: CALL, JMP, JACC, INDEX, JC, JNC, JNZ, JZ. This instruction format uses only 4-bits for the instruction opcode leaving 12-bits to store the relative destination address in a two's-complement form. These instructions can change program execution to an address relative to the current address by -2048 or +2047.

The second two-byte instruction format (Table 3-4) is used by instructions that employ the Source Immediate addressing mode ("Source Immediate" on page 41). The destination for these instructions is an internal M8C register while the source is a constant value. An example of this type of instruction would be ADD A, 7.

The third two-byte instruction format is used by a wide range of instructions and addressing modes. The following is a list of the addressing modes that use this third two-byte instruction format:

- Source Direct (ADD A, [7])

- Source Indexed (ADD A, [X+7])

- Destination Direct (ADD [7], A)

- Destination Indexed (ADD [X+7], A)

- Source Indirect Post Increment (MVI A, [7])

- Destination Indirect Post Increment (MVI [7], A)

For more information on addressing modes see "Addressing Modes" on page 41.

Regardless of the CPU speed bit's setting, if the actual CPU speed is greater than 12 MHz, the 24 MHz operating requirements apply. An example of this scenario is a device that is configured to use an external clock, which is supplying a frequency of 20 MHz. If the CPU speed register's value is 0b011, the CPU clock will be 20 MHz. Therefore, the supply voltage requirements for the device are the same as if the part was operating at 24 MHz off of the internal main oscillator. The operating voltage requirements are not relaxed until the CPU speed is at 12.0 MHz or less.

Table 10-4. OSC\_CR0[2:0] Bits: CPU Speed

| Bits | Internal Main Oscillator | External Clock |

|------|--------------------------|----------------|

| 000b | 3 MHz                    | EXTCLK/8       |

| 001b | 6 MHz                    | EXTCLK/ 4      |

| 010b | 12 MHz                   | EXTCLK/ 2      |

| 011b | 24 MHz                   | EXTCLK/ 1      |

| 100b | 1.5 MHz                  | EXTCLK/ 16     |

| 101b | 750 kHz                  | EXTCLK/ 32     |

| 110b | 187.5 kHz                | EXTCLK/ 128    |

| 111b | 93.7 kHz                 | EXTCLK/ 256    |

For additional information, reference the OSC\_CR0 register on page 176.

## 10.2.2 ECO\_TR Register

The External Crystal Oscillator Trim register (ECO\_TR) sets the adjustment for the External Crystal Oscillator. The device specific value placed in this register at boot time is based on factory testing. This register does not adjust the frequency of the External Crystal Oscillator. It is recommended that the user not alter the bits in this register.

Bits 7 and 6: PSSDC[1:0]. These bits are used to set the sleep duty cycle.

#### Bits 5 to 0: Reserved.

For additional information, reference the ECO\_TR register on page 184.

### 10.2.3 CPU\_SCR1 Register

The CPU\_SCR1 register is used to convey status and control of events related to internal resets and watchdog reset.

#### Bits 7 to 1: Reserved.

**Bit 0: IRAMDIS.** The Initialize RAM Disable bit is a control bit that is readable and writeable. The default value for this bit is 0, which indicates that the maximum amount of SRAM should be initialized on reset to a value of 00h. When the bit is set, the minimum amount of SRAM is initialized after a watchdog reset. For more information on this bit, see the "SROM Function Descriptions" on page 48.

For additional information, reference the CPU\_SCR1 register on page 153.

### 13.1.7 DxBxxDR2

## **Digital Basic/Communication Type B Block Data Register 2**

## **Individual Register Names and Addresses**

DBB00DR2: 0,22h

DBB01DR2: 0,26h

DCB02DR2: 0,2Ah

DCB03DR2: 0,2Eh

7

6

5

4

3

2

1

0

Access: POR

RW: 00

Bit Name

Data[7:0]

The function of this register is dependant on the function its block has been configured for (selected in the FN[2:0] bits of the DxBxxFN register on page 159. For additional information, reference the "Register Definitions" on page 208 in the Digital Blocks chapter.

| Bit   | Name      | Description         |                   |  |  |

|-------|-----------|---------------------|-------------------|--|--|

| [7:0] | Data[7:0] | Data for selected t | function.         |  |  |

|       |           | Block Function      | Register Function |  |  |

|       |           | Timer               | Capture/Compare   |  |  |

|       |           | Counter             | Compare           |  |  |

|       |           | Dead Band           | Buffer            |  |  |

|       |           | CRCPRS              | Seed/Residue      |  |  |

|       |           | SPIM                | RX Buffer         |  |  |

|       |           | SPIS                | RX Buffer         |  |  |

|       |           | TXUART              | Not applicable    |  |  |

|       |           | RXUART              | RX Buffer         |  |  |

### 13.1.12 DCBxxCR0

## (SPIM Control)

## **Digital Communication Type B Block Control Register 0**

### **Individual Register Names and Addresses**

DCB02CR0: 0,2Bh DCB03CR0: 0,2Fh

|              | 7         | 6       | 5            | 4            | 3           | 2           | 1              | 0      |

|--------------|-----------|---------|--------------|--------------|-------------|-------------|----------------|--------|

| Access : POR | RW:0      | R:0     | R:0          | R : 1        | R:0         | RW:0        | RW:0           | RW:0   |

| Bit Name     | LSB First | Overrun | SPI Complete | TX Reg Empty | RX Reg Full | Clock Phase | Clock Polarity | Enable |

The LSB First, Clock Phase, and Clock Polarity bit are configuration bits and should never be changed once the block is enabled. They can be set at the same time that the block is enabled. For additional information, reference the "Register Definitions" on page 208 in the Digital Blocks chapter.

| Bit | Name           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| [7] | LSB First      | This bit should not be changed during an SPI transfer.  Data is shifted out MSB first.  Data is shifted out LSB first.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| [6] | Overrun        | No overrun has occurred. Overrun has occurred. Indicates that a new byte has been received and loaded into the RX Buffer before the previous one could be read. Cleared on read of this (CR0) register.                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| [5] | SPI Complete   | <ul> <li>Indicates that a byte may still be in the process of shifting out, or no transmission is active.</li> <li>Indicates that a byte has been shifted out and all associated clocks have been generated.</li> <li>Cleared on read of this (CR0) register. Optional interrupt.</li> </ul>                                                                                                                                                        |  |  |  |  |  |  |

| [4] | TX Reg Empty   | The reset state and the state when the block is disabled is '1'.  Indicates that a byte is currently buffered in the TX register.  Indicates that a byte can be written to the TX register. Cleared on write of the TX Buffer (DR1) register. Default interrupt. This status will initially be asserted on block enable; however, the TX Reg Empty interrupt will occur only after the first data byte is written and transferred into the shifter. |  |  |  |  |  |  |

| [3] | RX Reg Full    | <ul> <li>RX register is empty.</li> <li>A byte has been received and loaded into the RX register. Cleared on read of the RX Buffer (DR2) register.</li> </ul>                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| [2] | Clock Phase    | <ul> <li>Data is latched on the leading edge of the clock. Data changes on the trailing edge (Modes 0,1).</li> <li>Data changes on the leading edge of the clock. Data is latched on the trailing edge (Modes 2,3).</li> </ul>                                                                                                                                                                                                                      |  |  |  |  |  |  |

| [1] | Clock Polarity | <ul> <li>Non-inverted, clock idles low (Modes 0,2).</li> <li>Inverted, clock idles high (Modes 1,3).</li> </ul>                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| [0] | Enable         | <ul><li>SPI Master is not enabled.</li><li>SPI Master is enabled.</li></ul>                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

## 13.1.22 ACBxxCR0

## **Analog Continuous Time Type B Block Control Register 0**

### **Individual Register Names and Addresses**

ACB00CR0: x,71h ACB01CR0: x,75h

|              | 7    | 6            | 5 | 4 | 3    | 2       | 1     | 0       |  |

|--------------|------|--------------|---|---|------|---------|-------|---------|--|

| Access : POR | RW:0 |              |   |   | RW:0 | RW:0    | RW:0  |         |  |

| Bit Name     |      | RTapMux[3:0] |   |   |      | RTopMux | RBotM | ux[1:0] |  |

For additional information, reference the "Register Definitions" on page 257 in the Continuous Time Block chapter.

| Bit   | Name         | Descri                                                                                                                                                                                                                                           | ption                                  |                                        |               |            |                                                           |  |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------|---------------|------------|-----------------------------------------------------------|--|

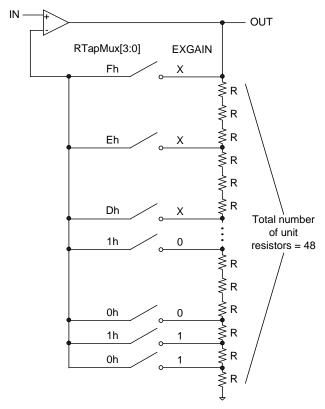

| [7:4] | RTapMux[3:0] | Encoding for selecting one of 18 resistor taps. The four bits of RTapMux[3:0] allow selection of 16 taps. The two additional tap selections are provided using ACBxxCR3 bit 0, EXGAIN. The EXGAIN bit only affects the RTapMux values 0h and 1h. |                                        |                                        |               |            |                                                           |  |

|       |              | RTap                                                                                                                                                                                                                                             | EXGAIN                                 | Rf                                     | Ri            | Loss       | Gain                                                      |  |

|       |              | 0h                                                                                                                                                                                                                                               | 1                                      | 47                                     | 1             | 0.0208     | 48.000                                                    |  |

|       |              | 1h                                                                                                                                                                                                                                               | 1                                      | 46                                     | 2             | 0.0417     | 24.000                                                    |  |

|       |              | 0h                                                                                                                                                                                                                                               | 0                                      | 45                                     | 3             | 0.0625     | 16.000                                                    |  |

|       |              | 1h                                                                                                                                                                                                                                               | 0                                      | 42                                     | 6             | 0.1250     | 8.000                                                     |  |