Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 4KB (4K x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 2x14b; D/A 2x9b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24423-24pvit |

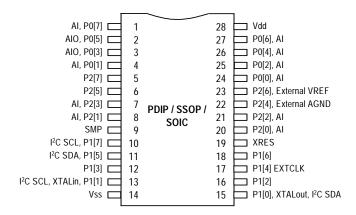

Table 1-4. 28-Pin Part Pinout (PDIP, SSOP, SOIC)

| Pin |                             |  |  |  |

|-----|-----------------------------|--|--|--|

| No. | Description                 |  |  |  |

| 1   | P0[7], A in                 |  |  |  |

| 2   | P0[5], A in, out            |  |  |  |

| 3   | P0[3], A in, out            |  |  |  |

| 4   | P0[1], A in                 |  |  |  |

| 5   | P2[7]                       |  |  |  |

| 6   | P2[5]                       |  |  |  |

| 7   | P2[3], A in (ASC10)         |  |  |  |

| 8   | P2[1], A in (ASD20, ASC10)  |  |  |  |

| 9   | SMP                         |  |  |  |

| 10  | P1[7], I <sup>2</sup> C SCL |  |  |  |

| Pin<br>No. | Description                 |  |  |  |

|------------|-----------------------------|--|--|--|

| 11         | P1[5], I <sup>2</sup> C SDA |  |  |  |

| 12         | P1[3]                       |  |  |  |

| 13         | P1[1], XTALin, I2C SCL      |  |  |  |

| 14         | Vss                         |  |  |  |

| 15         | P1[0], XTALout, I2C SDA     |  |  |  |

| 16         | P1[2],                      |  |  |  |

| 17         | P1[4], EXTCLK               |  |  |  |

| 18         | P1[6]                       |  |  |  |

| 19         | XRES                        |  |  |  |

| 20         | P2[0], A in (ASC21)         |  |  |  |

| Pin<br>No. | Description                |  |  |

|------------|----------------------------|--|--|

| 21         | P2[2], A in (ASD11, ASC21) |  |  |

| 22         | P2[4], External AGND       |  |  |

| 23         | P2[6], External VREF       |  |  |

| 24         | P0[0], A in                |  |  |

| 25         | P0[2], A in                |  |  |

| 26         | P0[4], A in                |  |  |

| 27         | P0[6], A in                |  |  |

| 28         | Vdd                        |  |  |

LEGEND A: analog, D: digital, IO: input or output.

#### 3.5.2 Source Direct

For these instructions the source address is stored in operand 1 of the instruction. During instruction execution the address will be used to retrieve the source value from RAM or register address space. The result of these instructions is

placed in either the M8C A or X register as indicated by the instruction's opcode. All instructions using the Source Direct addressing mode are two bytes in length.

Table 3-7. Source Direct

| Opcode      | Operand 1      |

|-------------|----------------|

| Instruction | Source Address |

#### Source Direct Examples:

| Source ( | Code      | Machine Code | Comments                                                                                                    |

|----------|-----------|--------------|-------------------------------------------------------------------------------------------------------------|

| ADD      | A, [7]    | 02 07        | The value in memory at address 7 is added to the Accumulator and the result is placed into the Accumulator. |

| MOV      | A, REG[8] | 5D 08        | The value in the register space at address 8 is moved into the Accumulator.                                 |

### 3.5.3 Source Indexed

For these instructions the source offset from the  ${\tt X}$  register is stored in operand 1 of the instruction. During instruction execution the current  ${\tt X}$  register value is added to the signed offset to determine the address of the source value in RAM

or register address space. The result of these instructions is placed in either the M8C A or X register as indicated by the instruction's opcode. All instructions using the Source Indexed addressing mode are two bytes in length.

Table 3-8. Source Indexed

| Opcode      | Operand 1    |

|-------------|--------------|

| Instruction | Source Index |

### Source Indexed Examples:

| Source | Code     | Machine Code | Comments                                                                                                 |

|--------|----------|--------------|----------------------------------------------------------------------------------------------------------|

| ADD    | A, [X+7] | 03 07        | The value in memory at address X+7 is added to the Accumulator. The result is placed in the Accumulator. |

| MOV    | X, [X+8] | 59 08        | The value in RAM at address X+8 is moved into the X register.                                            |

### 3.5.4 Destination Direct

For these instructions the destination address is stored in the machine code of the instruction. The source for the operation is either the M8C  $\tt A$  or  $\tt X$  register as indicated by the

instruction's opcode. All instructions using the Destination Direct addressing mode are two bytes in length.

**Table 3-9. Destination Direct**

| Opcode      | Operand 1           |

|-------------|---------------------|

| Instruction | Destination Address |

## **Destination Direct Examples:**

| Source Code |           | Machine Code | Comments                                                                                                                                  |

|-------------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| ADD         | [7], A    | 04 07        | The value in the Accumulator is added to memory, at address 7. The result is placed in memory at address 7. The Accumulator is unchanged. |

| MOV         | REG[8], A | 60 08        | The Accumulator value is moved to register space at address 8. The Accumulator is unchanged.                                              |

Destination Indirect Post Increment Example:

| Source C | Code   | Machine Code | Comments                                                                                                                                                                                             |

|----------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MVI      | [8], A | 3F 08        | The value in memory at address 8 (the indirect address) points to a memory location in RAM. The Accumulator value is moved into the memory location pointed to by the indirect address. The indirect |

address in memory, at address 8, is then incremented.

# 3.6 Register Definitions

## 3.6.1 CPU F (Flag) Register

The Flag register has four chip dependent bits (FL[7:4]) and four dedicated bits (FL[3:0]), as shown in Table 3-1.

#### 3.6.1.1 Chip-Dependent Flag Bits

The chip-dependent Flag bits have no effect internally on the M8C. These bits are manipulated by the user with the Flag-Logic opcodes (for example, XOR F, 80h). Bit Definitions for the PSoC Mixed Signal Array family are as follows.

#### Bits 7, 6, and 5: Reserved.

**Bit 4: XOI.** IO Bank Select. This bit is used to select between register banks, in order to support more than 256 registers.

# 3.6.1.2 Dedicated Flag Bits

The dedicated Flag bits are described as follows.

#### Bit 3: Reserved.

**Bit 2: Carry.** Carry Flag. This bit is set or cleared in response to the result of several instructions. It may also be manipulated by the Flag-Logic opcodes (for example, OR F, 4). See the *PSoC Designer Assembly Guide User Manual* for more details.

**Bit 1: Zero.** Zero Flag. This bit is set or cleared in response to the result of several instructions. It may also be manipulated by the Flag-Logic opcodes (for example, OR F, 2). See the *PSoC Designer Assembly Guide User Manual* for more details.

**Bit 0: GIE.** Global Interrupt Enable. The state of this bit determines whether interrupts (by way of the IRQ) will be recognized by the M8C. This bit is set or cleared by the user, using the Flag-Logic opcodes (e.g., OR F, 1). GIE is also cleared automatically by the interrupt routine, after the flag byte has been stored on the stack.

For GIE=1, the M8C samples the IRQ input for each instruction. For GIE=0, the M8C ignores the IRQ.

For additional information, reference the CPU\_F register on page 152.

#### 4.1.2.5 TableRead Function

The TableRead function gives the user access to part-specific data stored in the Flash during manufacturing. It also returns a Revision ID for the die (not to be confused with the Silicon ID stored in Table 0).

Table 4-9. TableRead Parameters (06h)

| Name    | Address | Description                                |

|---------|---------|--------------------------------------------|

| KEY1    | 0,F8h   | 3Ah                                        |

| KEY2    | 0,F9h   | Stack Pointer value, when SSC is executed. |

| BLOCKID | 0,FAh   | Table number to read.                      |

Table 4-10. Table with Assigned Values in Flash Macro 0

|         | F8h                                                 | F9h                                               | FAh                                            | FBh                                           | FCh                                               | FDh                                             | FEh                                          | FFh                                         |

|---------|-----------------------------------------------------|---------------------------------------------------|------------------------------------------------|-----------------------------------------------|---------------------------------------------------|-------------------------------------------------|----------------------------------------------|---------------------------------------------|

| Table 0 | Silicon ID                                          |                                                   | (May be used for                               | serialization in th                           | e future.)                                        |                                                 |                                              |                                             |

| Table 1 | Voltage<br>Reference trim<br>for 3.3 V<br>reg[1,EA] | Main<br>Oscillator trim<br>for 3.3 V<br>reg[1,E8] | Room<br>Temperature<br>Calibration<br>for 3.3V | Hot<br>Temperature<br>Calibration<br>for 3.3V | Voltage<br>Reference trim<br>for 5 V<br>reg[1,EA] | Main<br>Oscillator trim<br>for 5 V<br>reg[1,E8] | Room<br>Temperature<br>Calibration<br>for 5V | Hot<br>Temperature<br>Calibration<br>for 5V |

| Table 2 |                                                     |                                                   |                                                |                                               |                                                   |                                                 |                                              |                                             |

| Table 3 | М                                                   | В                                                 | Mult                                           | M                                             | В                                                 | Mult                                            | 00h                                          | 01h                                         |

### 4.1.2.6 Checksum Function

The Checksum function calculates a 16-bit checksum over a user specifiable number of blocks, within a single Flash macro (Bank) starting from block zero. The BLOCKID parameter is used to pass in the number of blocks to calculate the checksum over. A BLOCKID value of 1 will calculate the checksum of only block 0, while a BLOCKID value of 0 will calculate the checksum of all 256 user blocks.

The 16-bit checksum is returned in KEY1 and KEY2. The parameter KEY1 holds the lower 8 bits of the checksum and the parameter KEY2 holds the upper 8 bits of the checksum.

The checksum algorithm executes the following sequence of three instructions over the number of blocks times 64 to be checksumed.

romx add [KEY1], A adc [KEY2], 0

Table 4-11. Checksum Parameters (07h)

| Name    | Address | Description                                      |

|---------|---------|--------------------------------------------------|

| KEY1    | 0,F8h   | 3Ah                                              |

| KEY2    | 0,F9h   | Stack Pointer value, when SSC is executed.       |

| BLOCKID | 0,FAh   | Number of Flash blocks to calculate checksum on. |

#### 4.1.2.7 Calibrate 0 Function

The Calibrate0 function transfers the calibration values stored in a special area of the Flash to their appropriate registers.

Table 4-12. Calibrate Parameters (08h)

| Name | Address | Description                                |

|------|---------|--------------------------------------------|

| KEY1 | 0,F8h   | 3Ah                                        |

| KEY2 | 0,F9h   | Stack Pointer value, when SSC is executed. |

### 4.1.2.8 Calibrate 1 Function

While Calibrate1 is a completely separate function from Calibrate0, they perform the same function, which is to transfer the calibration values stored in a special area of the Flash to their appropriate registers. What is unique about Calibrate1 is that it calculates a checksum of the calibration data and, if that checksum is determined to be invalid, Calibrate1 will cause a hardware reset by setting the IRES bit of CPU SCR1.

The Calibrate1 function uses SRAM to calculate a checksum of the calibration data. The POINTER value is used to indicate the address of a 30 byte buffer used by this function. When the function completes, the 30 bytes will be set to 00h.

Calibrate1 was created as a sub function of SWBootReset. However, the Calibrate1 function code was added to provide direct access. For more information on how Calibrate1 works, see the SWBootReset section.

Table 4-13. Calibrate1 Parameters (09h)

| Name    | Address | Description                                       |

|---------|---------|---------------------------------------------------|

| KEY1    | 0,F8h   | 3Ah                                               |

| KEY2    | 0,F9h   | Stack Pointer value, when SSC is executed.        |

| POINTER | 0,FBh   | First of 32 SRAM addresses used by this function. |

together as DM[2:0]. Drive modes are shown in Table 6-3.

Table 6-3. Pin Drive Modes

| Drive Mode<br>DM[2:0] | Pin State                            | Description                                                              |

|-----------------------|--------------------------------------|--------------------------------------------------------------------------|

| 000b                  | Resistive pull down                  | Strong high, resistive low                                               |

| 001b                  | Strong drive                         | Strong high, strong low                                                  |

| 010b                  | High impedance                       | Hi-Z high and low, digital input enabled                                 |

| 011b                  | Resistive pull up                    | Resistive high, strong low                                               |

| 100b                  | Open drain high                      | Slow strong high, Hi-Z low                                               |

| 101b                  | Slow strong drive                    | Slow strong high, slow strong low                                        |

| 110b                  | High impedance, analog (reset state) | Hi-Z high and low, digital input disabled (for zero power) (reset state) |

| 111b                  | Open drain low                       | Slow strong low, Hi-Z high                                               |

For analog IO, the drive mode should be set to one of the Hi-Z modes, either 010b or 110b. The 110b mode has the advantage that the block's digital input buffer is disabled, so no "crowbar" current flows even when the analog input is not close to either power rail. When digital inputs are needed on the same pin as analog inputs, the 010b Drive mode should be used. If the 110b Drive mode is used, the pin will always be read as a zero by the CPU and the pin will not be able to generate a useful interrupt. (It is not strictly required that a Hi-Z mode be selected for analog operation).

For global input modes, the drive mode must be set to 010b.

This GPIO provides a default drive mode of high impedance (Hi-Z). This is achieved by forcing the reset state of all PRTxDM1 and PRTxDM2 registers to FFh.

The resistive drive modes place a resistance in series with the output, for low outputs (mode 000b) or high outputs (mode 011b). Strong drive mode 001b gives the fastest edges at high DC drive strength. Mode 101b gives the same drive strength but with slower edges. The Open drain modes (100b and 111b) also use the slower edge rate drive. These modes enable open drain functions such as I<sup>2</sup>C mode 111b (although the slow edge rate is not slow enough to meet the I<sup>2</sup>C fast mode specification).

For additional information, reference the PRTxDM2 register on page 91, the PRTxDM0 register on page 155, and the PRTxDM1 register on page 156.

#### 6.2.5 PRTxICx Registers

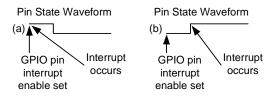

The interrupt mode for the pin is determined by bits in two registers: PRTxIC1 and PRTxIC0. These are referred to as IM1 and IM0, or together as IM[1:0].

There are four possible interrupt modes for each port pin. Two mode bits are required to select one of these modes and these two bits are spread into two different registers (PRTxIC0 and PRTxIC1). The bit position of the effected port pin (Example: Pin[2] in Port 0) is the same as the bit position of each of the Interrupt Control register bits that control the interrupt mode for that pin (Example: Bit[2] in PRT0IC0 and bit[2] in PRT0IC1). The two bits from the two registers are treated as a group.

The interrupt mode must be set to one of the non-zero modes listed in Table 6-4, in order to get an interrupt from the pin.

Table 6-4. GPIO Interrupt Modes

| Interrupt Mode IM[1:0] | Description                                  |

|------------------------|----------------------------------------------|

| 00b                    | Bit interrupt disabled, INTO de-asserted     |

| 01b                    | Assert INTO when PIN = low                   |

| 10b                    | Assert INTO when PIN = high                  |

| 11b                    | Assert INTO when PIN = change from last read |

The GPIO interrupt mode "disabled" (00b) disables interrupts from the pin, even if the GPIO's bit interrupt enable is on (from the PRTxIE register).

Interrupt mode 01b means that the block will assert the interrupt line (INTO) when the pin voltage is low, providing the block's bit interrupt enable line is set (high).

Interrupt mode 10b means that the block will assert the interrupt line (INTO), when the pin voltage is high, providing the block's bit interrupt enable line is set (high).

Interrupt mode 11b means that the block will assert the interrupt line (INTO) when the pin voltage is the opposite of the last state read from the pin (again providing the block's bit interrupt enable line is set high). This mode switches between low mode and high mode, depending on the last value that was read from the port during reads of the data register (PRTxDR). If the last value read from the GPIO was 0, the GPIO will subsequently be in interrupt high mode. If the last value read from the GPIO was 1, the GPIO will then be in interrupt low mode.

## Last Value Read From Pin was 0

#### Last Value Read From Pin was 1

Figure 6-3. GPIO Interrupt Mode 11b

Figure 6-3 assumes that the GIE is set, GPIO interrupt mask is set, and that the GPIO interrupt mode has been set to 11b. The change interrupt mode is different from the other modes, in that it relies on the value of the GPIO's read latch to determine if the pin state has changed. Therefore, the port that contains the GPIO in question must be read during

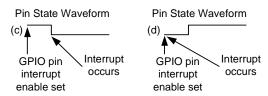

# 7. Analog Output Drivers

This chapter presents the Analog Output Drivers and its associated register. The analog output drivers provide a means for driving analog signals off-chip.

Table 7-1. Analog Output Driver Register

| Address | Name    | Bit 7    | Bit 6 | Bit 5    | Bit 4 | Bit 3    | Bit 2 | Bit 1  | Bit 0 | Access |

|---------|---------|----------|-------|----------|-------|----------|-------|--------|-------|--------|

| 1,62h   | ABF_CR0 | ACol1Mux |       | ABUF1EN0 |       | ABUF0EN0 |       | Bypass | PWR   | RW:00  |

# 7.1 Architectural Description

The PSoC device has two analog drivers used to output analog values on port pins. For a detailed drawing of the analog output drivers in relation to the analog system, reference the Analog Input Configuration chapter on page 245.

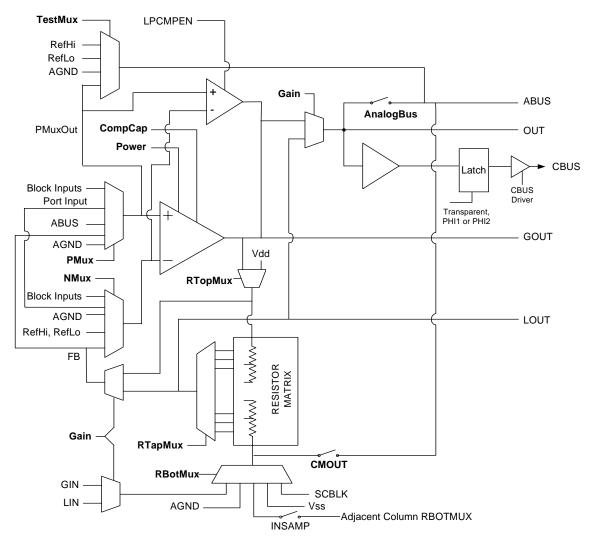

Figure 7-1. Analog Output Drivers

Each of these drivers is a resource available to all the analog blocks in a particular analog column. The user must select one analog block per column to drive a signal on its analog output bus (ABUS), to serve as the input to the analog driver for that column. The output from the analog output driver for each column can be enabled and disabled using the Analog Output Driver register ABF\_CR0.

Figure 7-2.

# 7.2 Register Definitions

Table 7-1 presents an overview of all registers related to the analog output drivers. The following section presents a detail on the use of the register's bits.

## 7.2.1 ABF\_CR0 Register

This register controls analog input muxes from Port 0, and the output buffer amplifiers that drive column outputs to device pins.

**Bit 7: ACOI1MUX.** A mux selects the output of column 0 input mux or column 1 input mux. When set, this bit sets the column 1 input to column 0 input mux output.

Bit 6: Reserved.

**Bits 5 and 3: ABUFxEN0.** These bits enable or disable the column output amplifiers.

Bits 4 and 2: Reserved.

**Bit 1: Bypass.** Bypass mode connects the amplifier input directly to the output. When this bit is set, all amplifiers controlled by the register will be in bypass mode.

**Bit 0: PWR.** This bit is used to set the power level of the amplifiers. When this bit is set, all amplifiers controlled by the register will be in a high power.

For additional information, reference the ABF\_CR0 register on page 166.

# 8. Internal Main Oscillator (IMO)

This chapter briefly presents the Internal Main Oscillator (IMO) and its associated register. The IMO produces clock signals of 24 MHz and 48 MHz.

**Table 8-1. Internal Main Oscillator Register**

| Address | Name   | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Access |

|---------|--------|-----------|-------|-------|-------|-------|-------|-------|-------|--------|

| 1,E8h   | IMO_TR | Trim[7:0] |       |       |       |       |       |       | W:00  |        |

# 8.1 Architectural Description

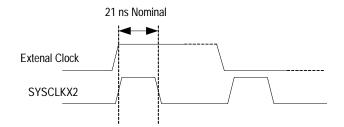

The Internal Main Oscillator outputs two clocks: a SYSCLK, which can be the internal 24 MHz clock or an external clock, and a SYSCLK2X that is always twice the SYSCLK frequency. In the absence of a high-precision input source from the 32 kHz crystal oscillator, the accuracy of the internal 24 MHz/48 MHz clocks will be +/-2.5% over temperature variation and two voltage ranges (3.3V +/-.3V and 5.0V +/-5%). No external components are required to achieve this level of accuracy.

There is an option to phase lock this oscillator to the External Crystal Oscillator. The choice of crystal and its inherent accuracy will determine the overall accuracy of the oscillator. The External Crystal Oscillator must be stable prior to locking the frequency of the Internal Main Oscillator to this reference source.

The IMO can be disabled when using an external clocking source. Also, the frequency doubler circuit, which produces SYSCLK2X, can be disabled to save power. Note that when using an external clock, if SYSCLK2X is needed, then the IMO can not be disabled. Registers for controlling these operations are found in the Digital Clocks chapter on page 263.

# 8.2 Register Definitions

# 8.2.1 IMO\_TR Register

The device specific value for 5 volt operation is loaded into the Internal Main Oscillator Trim Register (IMO\_TR) at boot time. The Internal Main oscillator will operate within specified tolerance over a voltage range of 4.75V to 5.25V, with no modification of this register. If the device is operated at a lower voltage, user code must modify the contents of this register. For operation in the voltage range of 3.3V +/-.3V, this can be accomplished with a Table Read command to the Supervisor ROM, which will supply a trim value for operation in this range. For operation between these Voltage ranges, user code can interpolate the best value using both available factory trim values.

**Bits 7 to 0: Trim.** These bits are used to trim the Internal Main Oscillator. A larger value in this register will increase the speed of the oscillator.

For additional information, reference the IMO\_TR register on page 181.

# 13.1.18 CMP\_CR0

# **Analog Comparator Bus 0 Register**

## **Individual Register Names and Addresses**

CMP\_CR0: 0,64h

|              | 7 | 6 | 5       | 4       | 3 | 2 | 1       | 0       |

|--------------|---|---|---------|---------|---|---|---------|---------|

| Access : POR |   |   | R:0     | R:0     |   |   | RW:0    | RW:0    |

| Bit Name     |   |   | COMP[1] | COMP[0] |   |   | AINT[1] | AINT[0] |

For additional information, reference the "Register Definitions" on page 238 in the Analog Interface chapter.

| Bit   | Name     | Description                                                                                                                                                                                                                                                 |

|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6] | Reserved |                                                                                                                                                                                                                                                             |

| [5]   | COMP[1]  | Comparator bus state for column 1.  This bit is updated on the rising edge of PHI2, unless the comparator latch disable bits are set. If the comparator latch disable bits are set, then this bit is transparent to the comparator bus in the analog array. |

| [4]   | COMP[0]  | Comparator bus state for column 0.  This bit is updated on the rising edge of PHI2, unless the comparator latch disable bits are set. If the comparator latch disable bits are set, then this bit is transparent to the comparator bus in the analog array. |

| [3:2] | Reserved |                                                                                                                                                                                                                                                             |

| [1]   | AINT[1]  | Controls the selection of the analog comparator interrupt for column 1.  The comparator data bit from the column is the input to the interrupt controller.  The falling edge of PHI2 for the column is the input to the interrupt controller.               |

| [0]   | AINT[0]  | Controls the selection of the analog comparator interrupt for column 0.  The comparator data bit from the column is the input to the interrupt controller.  The falling edge of PHI2 for the column is the input to the interrupt controller.               |

# 13.1.37 RDIxLT1

# **Row Digital Interconnect Logic Table Register 1**

# **Individual Register Names and Addresses**

RDI0LT1: x,B4h

|              | 7 | 6    | 5            | 4 | 3         | 2 | 1 | 0 |  |

|--------------|---|------|--------------|---|-----------|---|---|---|--|

| Access : POR |   | RW   | <i>I</i> : 0 |   | RW:0      |   |   |   |  |

| Bit Name     |   | LUT: | 3[3:0]       |   | LUT2[3:0] |   |   |   |  |

For additional information, reference the "Register Definitions" on page 196 in the Row Digital Interconnect chapter.

| Bit   | Name      | Description                                                                                                                                                                                                  |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:4] | LUT3[3:0] | Select logic function for LUT 3.                                                                                                                                                                             |

|       |           | Function  Oh FALSE  1h A AND B  2h A AND B  3h A  4h A AND B  5h B  6h A XOR B  7h A OR B  8h A NOR B  9h A XNOR B  Ah B  Bh A OR B  Ch A  Dh A OR B  Eh A NAND B  Fh TRUE                                   |

| [3:0] | LUT2[3:0] | Select logic function for LUT 2.  Function  Oh FALSE  1h A AND B  2h A AND B  3h A  4h A AND B  5h B  6h A XOR B  7h A OR B  8h A NOR B  9h A XNOR B  Ah B  Bh A OR B  Ch A  Dh A OR B  Eh A NAND B  Fh TRUE |

# 13.1.60 MAC\_X/ACC\_DR1

# **Accumulator Data Register 1**

# **Individual Register Names and Addresses**

MAC\_X/ACC\_DR1: 0,ECh

|              | 7 | 6 | 5 | 4    | 3     | 2 | 1 | 0 |

|--------------|---|---|---|------|-------|---|---|---|

| Access : POR |   |   |   | RW   | : 00  |   |   |   |

| Bit Name     |   |   |   | Data | [7:0] |   |   |   |

For additional information, reference the "Register Definitions" on page 270 in the Multiply Accumulate chapter.

| Bit   | Name      | Descrip       | on                                                                                                                                                                                                                                          |  |  |  |  |

|-------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| [7:0] | Data[7:0] | Read<br>Write | Low byte of the MAC Accumulator sum. Returns the 2nd byte of the 32-bit accumulated value. The 2nd byte is next to the least significant byte for the accumulated value. X multiplicand for the MAC 16-bit multiply and 32-bit accumulator. |  |  |  |  |

# **Digital Register Summary**

The table below lists all the PSoC registers in the digital system.

## **Summary Table of the Digital Registers**

| CLOBAL DIGITAL INTERCONNECT (GDI) REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.D1h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.D1h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1,03h   GDLE_OU   GOEUTIN7   GOEUTIN6   GOEUTIN6   GOEUTIN4   GOEUTIN3   GOEUTIN2   GOEUTIN1   GOEUTIN0   RW: 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Right   Rig  |

| R.B0h   R.D10R1   R.D13[1:0]   R.D12[1:0]   R.D13[1:0]   R.D13[1:0]   R.W: 00     R.B1h   R.D10SYN   R.D10IS   R.W: 00     R.B3h   R.D10LT0   L.D17[3:0]   R.W: 00   R.W: 00     R.B4h   R.D10LT1   L.D173[3:0]   L.D17[3:0]   R.W: 00     R.B5h   R.D10RO0   GOOSEN   GOO1EN   GOESEN   GOEIEN   GOO4EN   GOO0EN   GOE4EN   GOEOEN   R.W: 00     R.B5h   R.D10RO0   GOOSEN   GOO3EN   GOE7EN   GOE3EN   GOO6EN   GOO2EN   GOE2EN   R.W: 00     R.B5h   R.D10RO0   GOO7EN   GOO3EN   GOE7EN   GOE3EN   GOO6EN   GOO2EN   GOE2EN   R.W: 00     R.B5h   R.D10RO0   GOO7EN   GOO3EN   GOE7EN   GOE3EN   GOO6EN   GOO2EN   GOE2EN   R.W: 00     R.B5h   R.D10RO0   GOO7EN   GOO3EN   GOE7EN   GOE3EN   GOO6EN   GOO2EN   GOE2EN   R.W: 00     R.B5h   R.D10RO0   B.D10RO0   B.D10RO0 |

| RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RISSYN   RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| X,B3h   RDIOLTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| R.B5h   RDIOROO   GOOSEN   GOO1EN   GOESEN   GOE1EN   GOO4EN   GOO0EN   GOE4EN   GOE0EN   RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| X,B6h   RDIORO1   GOO7EN   GOO3EN   GOE7EN   GOE3EN   GOO6EN   GOO2EN   GOE2EN   RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Digital Block Registers   Data and Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Data and Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Data   Column   Data   Colu  |

| Data   Column   Data   Colu  |

| 0,22h         DBB00DR2         Data[7:0]         #:00           0,23h         DBB00CR0         Function control/status bits for selected function[6:0]         Enable         #:00           1,20h         DBB00FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW:00           1,21h         DBB00IN         Data Input[3:0]         Clock Input[3:0]         RW:00           1,22h         DBB00OU         AUXCLK         AUXEN         AUX IO Select[1:0]         OUTEN         Output Select[1:0]         RW:00           0,24h         DBB01DR0         Data[7:0]         #:00         #:00           0,25h         DBB01DR1         Data[7:0]         #:00         #:00           0,26h         DBB01DR2         Data[7:0]         #:00         #:00           0,27h         DBB01CR0         Function control/status bits for selected function[6:0]         Enable         #:00           1,24h         DBB01FN         Data Input[3:0]         Mode[1:0]         Function[2:0]         RW:00           1,25h         DBB01IN         Data Input[3:0]         OUTEN         Output Select[1:0]         RW:00           0,28h         DCB02DR0         AUXCLK         AUXEN         AUX IO Select[1:0]         OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DBB00CR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1,20h         DBB00FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW : 00           1,21h         DBB00IN         Data Input[3:0]         Clock Input[3:0]         RW : 00           1,22h         DBB00OU         AUXCLK         AUXEN         AUX IO Select[1:0]         OUTEN         Output Select[1:0]         RW : 00           0,24h         DBB01DR0         Data[7:0]         # : 00         # : 00         # : 00           0,25h         DBB01DR1         Data[7:0]         # : 00         # : 00         # : 00           0,26h         DBB01DR2         Data[7:0]         # : 00         # : 00         # : 00           0,27h         DBB01CR0         Function control/status bits for selected function[6:0]         Enable         # : 00           1,24h         DBB01FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW : 00           1,25h         DBB01IN         Data Input[3:0]         Clock Input[3:0]         RW : 00         1,26h         DBB01OU         AUXCLK         AUXEN         AUX IO Select[1:0]         OUTEN         Output Select[1:0]         RW : 00           0,28h         DCB02DR0         Data[7:0]         Data[7:0]         W :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1,21h   DBB00IN   Data Input[3:0]   Clock Input[3:0]   RW : 00     1,22h   DBB00OU   AUXCLK   AUXEN   AUXIO Select[1:0]   OUTEN   Output Select[1:0]   RW : 00     0,24h   DBB01DR0   Data[7:0]   #: 00     0,25h   DBB01DR1   Data[7:0]   #: 00     0,26h   DBB01DR2   Data[7:0]   #: 00     0,27h   DBB01CR0   Function control/status bits for selected function[6:0]   Enable   #: 00     1,24h   DBB01FN   Data Invert   BCEN   End/Single   Mode[1:0]   Function[2:0]   RW : 00     1,25h   DBB01IN   Data Input[3:0]   Clock Input[3:0]   RW : 00     1,26h   DBB01OU   AUXCLK   AUXEN   AUXIO Select[1:0]   OUTEN   Output Select[1:0]   RW : 00     0,28h   DCB02DR0   Data[7:0]   #: 00     0,28h   DCB02DR1   Data[7:0]   #: 00     0,28h   DCB02DR2   Data[7:0]   #: 00     0,28h   DCB02CR0   Function control/status bits for selected function[6:0]   Enable   #: 00     0,28h   DCB02CR0   Function control/status bits for selected function[6:0]   Enable   #: 00     0,28h   DCB02CR0   Function control/status bits for selected function[6:0]   Enable   #: 00     1,28h   DCB02FN   Data Invert   BCEN   End/Single   Mode[1:0]   Function[2:0]   RW : 00     1,29h   DCB02IN   Data Input[3:0]   Clock Input[3:0]   RW : 00     1,29h   DCB02IN   Data Input[3:0]   RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1,22h   DBB00OU   AUXCLK   AUXEN   AUX IO Select[1:0]   OUTEN   Output Select[1:0]   RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Data    |

| Data    |

| Data    |

| 0,27h         DBB01CR0         Function control/status bits for selected function[6:0]         Enable         # : 00           1,24h         DBB01FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW : 00           1,25h         DBB01IN         Data Input[3:0]         Clock Input[3:0]         RW : 00           1,26h         DBB01OU         AUXCLK         AUXEN         AUX IO Select[1:0]         OUTEN         Output Select[1:0]         RW : 00           0,28h         DCB02DR0         Data[7:0]         # : 00           0,29h         DCB02DR1         Data[7:0]         W : 00           0,2Ah         DCB02DR2         Data[7:0]         # : 00           0,2Bh         DCB02CR0         Function control/status bits for selected function[6:0]         Enable         # : 00           1,28h         DCB02FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW : 00           1,29h         DCB02IN         Data Input[3:0]         Clock Input[3:0]         RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1,24h         DBB01FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW : 00           1,25h         DBB01IN         Data Input[3:0]         Clock Input[3:0]         RW : 00           1,26h         DBB01OU         AUXCLK         AUXEN         AUX IO Select[1:0]         OUTEN         Output Select[1:0]         RW : 00           0,28h         DCB02DR0         Data[7:0]         # : 00           0,29h         DCB02DR1         Data[7:0]         W : 00           0,2Ah         DCB02DR2         Data[7:0]         # : 00           0,2Bh         DCB02CR0         Function control/status bits for selected function[6:0]         Enable         # : 00           1,28h         DCB02FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW : 00           1,29h         DCB02IN         Data Input[3:0]         Clock Input[3:0]         RW : 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1,25h         DBB01IN         Data Input[3:0]         Clock Input[3:0]         RW : 00           1,26h         DBB01OU         AUXCLK         AUXEN         AUX IO Select[1:0]         OUTEN         Output Select[1:0]         RW : 00           0,28h         DCB02DR0         Data[7:0]         #: 00           0,29h         DCB02DR1         W: 00         W: 00           0,2Ah         DCB02DR2         Data[7:0]         #: 00           0,2Bh         DCB02CR0         Function control/status bits for selected function[6:0]         Enable         #: 00           1,28h         DCB02FN         Data Invert         BCEN         End/Single         Mode[1:0]         Function[2:0]         RW: 00           1,29h         DCB02IN         Data Input[3:0]         Clock Input[3:0]         RW: 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |