Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                             |

| Number of I/O                 | 140                                                                                                      |

| Program Memory Size           | 1MB (1M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | -                                                                                                        |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 176-LQFP                                                                                                 |

| Supplier Device Package       | 176-LQFP (24x24)                                                                                         |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f765igt6                                    |

|                               |                                                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Refreshed by software

- DMA capability to read the final conversion data

- Interrupts: end of conversion, overrun, analog watchdog, short circuit, input serial channel clock absence

- "regular" or "injected" conversions:

- "regular" conversions can be requested at any time or even in continuous mode without having any impact on the timing of "injected" conversions

- "injected" conversions for precise timing and with high conversion priority

## 2.43 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with the temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

|         |         |              | l       | Pin N   | umbe     | ər                      |               |         |          |                                |          |               |       |                                                                                                                                          |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | FM32I<br>FM32 |         |          | reset                          |          |               |       |                                                                                                                                          |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                      | Additional<br>functions |

| 81      | 114     | B12          | 142     | 164     | B12      | A4                      | 142           | 164     | B12      | PD0                            | I/O      | FT            | -     | DFSDM1_CKIN6,<br>DFSDM1_DATIN7,<br>UART4_RX, CAN1_RX,<br>FMC_D2, EVENTOUT                                                                | -                       |

| 82      | 115     | C12          | 143     | 165     | C12      | D5                      | 143           | 165     | C12      | PD1                            | I/O      | FT            | -     | DFSDM1_DATIN6,<br>DFSDM1_CKIN7,<br>UART4_TX, CAN1_TX,<br>FMC_D3, EVENTOUT                                                                |                         |

| 83      | 116     | D12          | 144     | 166     | D12      | D6                      | 144           | 166     | D12      | PD2                            | I/O      | FT            | -     | TRACED2, TIM3_ETR,<br>UART5_RX,<br>SDMMC1_CMD,<br>DCMI_D11, EVENTOUT                                                                     | -                       |

| 84      | 117     | D11          | 145     | 167     | C11      | B5                      | 145           | 167     | C11      | PD3                            | I/O      | FT            | -     | DFSDM1_CKOUT,<br>SPI2_SCK/I2S2_CK,<br>DFSDM1_DATIN0,<br>USART2_CTS, FMC_CLK,<br>DCMI_D5, LCD_G7,<br>EVENTOUT                             | -                       |

| 85      | 118     | D10          | 146     | 168     | D11      | A5                      | 146           | 168     | D11      | PD4                            | I/O      | FT            | -     | DFSDM1_CKIN0,<br>USART2_RTS,FMC_NOE,<br>EVENTOUT                                                                                         | -                       |

| 86      | 119     | C11          | 147     | 169     | C10      | C5                      | 147           | 169     | C10      | PD5                            | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                                                          | -                       |

| -       | 120     | D8           | 148     | 170     | F8       | B6                      | 148           | 170     | F8       | VSS                            | S        | -             | -     | -                                                                                                                                        | -                       |

| -       | 121     | C8           | 149     | 171     | E9       | A6                      | 149           | 171     | E9       | VDDSDM<br>MC                   | s        | -             | -     | -                                                                                                                                        | -                       |

| 87      | 122     | B11          | 150     | 172     | B11      | E6                      | 150           | 172     | B11      | PD6                            | I/O      | FT            | -     | DFSDM1_CKIN4,<br>SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A, USART2_RX,<br>DFSDM1_DATIN1,<br>SDMMC2_CK,<br>FMC_NWAIT, DCMI_D10,<br>LCD_B2, EVENTOUT | -                       |

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|        |      |     | 1                         | able 12.     | STM32F                                     | 70588, 6                      |                                                        |                                                                |                                                                                | ntinued                                                       |                                                    | 32F/03X                                                                | A allering                   | ale                                            |                  |               |              |

|--------|------|-----|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|---------------|--------------|

|        |      | AF0 | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             | AF14          | AF15         |

| P      | ort  | SYS | I2C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD           | SYS          |

| Port H | PH14 | -   | -                         | -            | TIM8_CH<br>2N                              | -                             | -                                                      | -                                                              | -                                                                              | UART4_<br>RX                                                  | CAN1_R<br>X                                        | -                                                                      | -                            | FMC_D2<br>2                                    | DCMI_D<br>4      | LCD_G3        | EVEN<br>TOUT |

| POILE  | PH15 | -   | -                         | -            | TIM8_CH<br>3N                              | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>3                                    | DCMI_D<br>11     | LCD_G4        | EVEN<br>TOUT |

|        | PI0  | -   | -                         | TIM5_C<br>H4 | -                                          | -                             | SPI2_NS<br>S/I2S2_<br>WS                               | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>4                                    | DCMI_D<br>13     | LCD_G5        | EVEN<br>TOUT |

|        | PI1  | -   | -                         | -            | TIM8_BKI<br>N2                             | -                             | SPI2_SC<br>K/I2S2_<br>CK                               | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>5                                    | DCMI_D<br>8      | LCD_G6        | EVEN<br>TOUT |

|        | PI2  | -   | -                         | -            | TIM8_CH<br>4                               | -                             | SPI2_MI<br>SO                                          | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>6                                    | DCMI_D<br>9      | LCD_G7        | EVEN<br>TOUT |

|        | PI3  | -   | -                         | -            | TIM8_ET<br>R                               | -                             | SPI2_M<br>OSI/I2S2<br>_SD                              | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>7                                    | DCMI_D<br>10     | -             | EVEN<br>TOUT |

|        | PI4  | -   | -                         | -            | TIM8_BKI<br>N                              | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_MC<br>K_A                                                         | -                            | FMC_NB<br>L2                                   | DCMI_D<br>5      | LCD_B4        | EVEN<br>TOUT |

| Port I | PI5  | -   | -                         | -            | TIM8_CH<br>1                               | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_SC<br>K_A                                                         | -                            | FMC_NB<br>L3                                   | DCMI_V<br>SYNC   | LCD_B5        | EVEN<br>TOUT |

|        | PI6  | -   | -                         | -            | TIM8_CH<br>2                               | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_SD_<br>A                                                          | -                            | FMC_D2<br>8                                    | DCMI_D<br>6      | LCD_B6        | EVEN<br>TOUT |

|        | PI7  | -   | -                         | -            | TIM8_CH<br>3                               | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_FS_<br>A                                                          | -                            | FMC_D2<br>9                                    | DCMI_D<br>7      | LCD_B7        | EVEN<br>TOUT |

|        | PI8  | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -             | EVEN<br>TOUT |

|        | PI9  | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | UART4_<br>RX                                                  | CAN1_R<br>X                                        | -                                                                      | -                            | FMC_D3<br>0                                    | -                | LCD_VS<br>YNC | EVEN<br>TOUT |

|        | PI10 | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | ETH_MII_<br>RX_ER            | FMC_D3<br>1                                    | -                | LCD_HS<br>YNC | EVEN<br>TOUT |

|        | PI11 | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | LCD_G6                                             | OTG_HS_<br>ULPI_DIR                                                    | -                            | -                                              | -                | -             | EVEN<br>TOUT |

#### Table 12. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx alternate

DocID029041 Rev 4

5

103/255

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

Pinouts and pin description

- 7. The over-drive mode is not supported when the internal regulator is OFF.

- 8. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 9. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 10. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation          | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup>   | Conversion time<br>up to 1.2 Msps | 20 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>OFF                | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 216 MHz with 9 wait<br>states and over-drive<br>ON                 | No I/O<br>compensation | 16-bit erase and<br>program<br>operations     |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 216 MHz with 8 wait<br>states and over-drive<br>ON                 | I/O compensation works | 16-bit erase and<br>program<br>operations     |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(4)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 216 MHz with 6 wait<br>states and over-drive<br>ON                 | I/O compensation works | 32-bit erase and program operations           |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator on ITCM interface and L1-cache on AXI interface, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator or L1-cache allows to achieve a performance equivalent to 0-wait state program execution.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.18.2: Internal reset OFF).

- 4. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

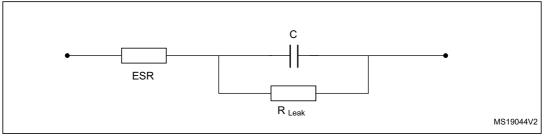

## 5.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 19*.

#### Figure 27. External capacitor C<sub>EXT</sub>

1. Legend: ESR is the equivalent series resistance.

- 1. Guaranteed by characterization results.

- 2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

- When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Cumhal          | Deremeter                |                        |                         | Turn |                        | Max <sup>(1)</sup>     |                         | Unit |  |

|-----------------|--------------------------|------------------------|-------------------------|------|------------------------|------------------------|-------------------------|------|--|

| Symbol          | Parameter                | Conditions             | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit |  |

|                 |                          |                        | 216                     | 128  | 144 <sup>(3)</sup>     | 190 <sup>(3)</sup>     | -                       |      |  |

|                 |                          |                        | 200                     | 119  | 134                    | 180                    | 214                     |      |  |

|                 |                          | All                    | 180                     | 105  | 118 <sup>(3)</sup>     | 153 <sup>(3)</sup>     | 178 <sup>(3)</sup>      |      |  |

|                 |                          | peripherals            | 168                     | 93   | 105                    | 136                    | 156                     |      |  |

|                 |                          | enabled <sup>(2)</sup> | 144                     | 72   | 80                     | 107                    | 124                     |      |  |

|                 |                          |                        | 60                      | 33   | 39                     | 65                     | 82                      |      |  |

|                 | Supply                   |                        | 25                      | 17   | 21                     | 47                     | 65                      | mA   |  |

| I <sub>DD</sub> | current in<br>Sleep mode |                        | 216                     | 18   | 25 <sup>(3)</sup>      | 71 <sup>(3)</sup>      | -                       |      |  |

|                 |                          |                        | 200                     | 17   | 24                     | 70                     | 112                     |      |  |

|                 |                          | All                    | 180                     | 14   | 20 <sup>(3)</sup>      | 54 <sup>(3)</sup>      | 75 <sup>(3)</sup>       |      |  |

|                 |                          | peripherals            | 168                     | 13   | 18                     | 49                     | 69                      |      |  |

|                 |                          | disabled               | 144                     | 10   | 14                     | 40                     | 58                      |      |  |

|                 |                          |                        | 60                      | 6    | 10                     | 36                     | 53                      |      |  |

|                 |                          |                        | 25                      | 4    | 8                      | 34                     | 51                      |      |  |

Table 33. Typical and maximum current consumption in Sleep mode, regulator ON

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. Guaranteed by test in production.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid a current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 39: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{\text{SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

$V_{\text{DD}}$  is the MCU supply voltage

$f_{\mbox{SW}}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol            | Parameter     | Conditions                                                 | I/O toggling<br>frequency (fsw)<br>MHz | Typ<br>V <sub>DD</sub> = 3.3 V | Тур<br>V <sub>DD</sub> = 1.8 V | Unit |

|-------------------|---------------|------------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|------|

|                   |               |                                                            | 2                                      | 0.1                            | 0.1                            |      |

|                   |               |                                                            | 8                                      | 0.4                            | 0.2                            |      |

|                   |               |                                                            | 25                                     | 1.1                            | 0.7                            |      |

|                   |               | $C_{EXT} = 0 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$  | 50                                     | 2.4                            | 1.3                            |      |

|                   |               | $C = C_{INT} + C_S + C_{EXT}$                              | 60                                     | 3.1                            | 1.6                            |      |

|                   |               |                                                            | 84 4.3                                 | 2.4                            |                                |      |

|                   |               |                                                            | 90                                     | 4.9                            | 2.6                            |      |

|                   | I/O switching |                                                            | 100                                    | 5.4                            | 2.8                            | mA   |

| I <sub>DDIO</sub> | Current       |                                                            | 2                                      | 0.2                            | 0.1                            |      |

|                   |               |                                                            | 8                                      | 0.6                            | 0.3                            |      |

|                   |               |                                                            | 25                                     | 1.8                            | 1.1                            |      |

|                   |               | $C_{EXT} = 10 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$ | 50                                     | 3.1                            | 2.3                            |      |

|                   |               | $C = C_{INT} + C_S + C_{EXT}$                              | 60                                     | 4.6                            | 3.4                            |      |

|                   |               |                                                            | 84                                     | 9.7                            | 3.6                            |      |

|                   |               |                                                            | 90                                     | 10.12                          | 5.2                            | 1    |

|                   |               |                                                            | 100                                    | 14.92                          | 5.4                            |      |

| Table 38 | . Switching output | I/O current | consumption <sup>(1)</sup> |

|----------|--------------------|-------------|----------------------------|

|----------|--------------------|-------------|----------------------------|

DocID029041 Rev 4

## 5.3.8 Wakeup time from low-power modes

The wakeup times given in *Table 40* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Symbol                              | Parameter                                   | Conditions                                                                               | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                   |  |

|-------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------|--------------------|--------------------|------------------------|--|

| t <sub>WUSLEEP</sub> <sup>(2)</sup> | Wakeup from Sleep                           | -                                                                                        | 13                 | 13                 | CPU<br>clock<br>cycles |  |

|                                     |                                             | Main regulator is ON                                                                     | 14                 | 14.9               |                        |  |

| twustop <sup>(2)</sup>              | Wakeup from Stop mode                       | Main regulator is ON and Flash<br>memory in Deep power down mode                         | 104.1              | 107.6              |                        |  |

|                                     | with MR/LP regulator in<br>normal mode      | Low power regulator is ON                                                                | 21.4               | 24.2               |                        |  |

|                                     |                                             | Low power regulator is ON and Flash memory in Deep power down mode                       | 111.5              | 116.5              | μs                     |  |

|                                     | Wakeup from Stop mode                       | Main regulator in under-drive mode<br>(Flash memory in Deep power-down<br>mode)          | 107.4              | 113.2              |                        |  |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | with MR/LP regulator in<br>Under-drive mode | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-down<br>mode ) | 112.7              | 120                |                        |  |

| tWUSTDBY                            | Wakeup from Standby                         | Exit Standby mode on rising edge                                                         | 308                | 313                | 1                      |  |

| (2)                                 | mode                                        | Exit Standby mode on falling edge                                                        | 307                | 313                |                        |  |

#### Table 40. Low-power mode wakeup timings

1. Guaranteed by characterization results.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first

| Symbol            | Parameter           | Conditions               | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|--------------------------|--------------------|-----|--------------------|------|

|                   | Programming voltage | 32-bit program operation | 2.7                | -   | 3                  | V    |

| V <sub>prog</sub> |                     | 16-bit program operation | 2.1                | -   | 3.6                | V    |

|                   |                     | 8-bit program operation  | 1.7                | -   | 3.6                | V    |

Table 56. Flash memory programming (single bank configurationnDBANK=1) (continued)

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 100K erase operations.

|                         |                            | nDBANK=0)                                        |                    |      |                    |      |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 250  | 600                | ms   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 200  | 500                |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 1100 | 2400               |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 800  | 1400               | ms   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 500  | 1100               |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 2.1  | 4                  |      |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 1.5  | 2.6                | s    |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 8    | 16                 |      |

| Table 57. Flash memory programming (dual bank configuration |

|-------------------------------------------------------------|

| nDBANK=0)                                                   |

- 1. Guaranteed by characterization results.

- 2. Cycling performed over the whole temperature range.

## 5.3.17 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 60*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> =<br>216 MHz, conforms to IEC 61000-<br>4-2 | 2B              |

| V <sub>FTB</sub>  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> =+25 °C, f <sub>HCLK</sub> =<br>168 MHz, conforms to IEC 61000-<br>4-2  | 5A              |

#### Table 60. EMS characteristics

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

| Symbol                           |                                                                                    | ADC characteristics                                  | ,                                                              | Max   | 11014              |                    |

|----------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|-------|--------------------|--------------------|

| Symbol                           | Parameter                                                                          | Conditions                                           | Min                                                            | Тур   | Мах                | Unit               |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                                                         | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution      | -                                                              | -     | 1764               | kHz                |

|                                  |                                                                                    | -                                                    | -                                                              | -     | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>                                            | -                                                    | 0<br>(V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -     | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                                                           | See <i>Equation 1</i> for details                    | -                                                              | -     | 50                 | kΩ                 |

| $R_{ADC}^{(2)(4)}$               | Sampling switch resistance                                                         | -                                                    | -                                                              | -     | 6                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                                                 | -                                                    | -                                                              | 4     | 7                  | pF                 |

| <b>↓</b> (2)                     | Injection trigger conversion                                                       | f <sub>ADC</sub> = 30 MHz                            | -                                                              | -     | 0.100              | μs                 |

| $t_{lat}^{(2)}$                  | latency                                                                            |                                                      | -                                                              | -     | 3 <sup>(5)</sup>   | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion                                                         | f <sub>ADC</sub> = 30 MHz                            | -                                                              | -     | 0.067              | μs                 |

| <sup>4</sup> atr`´               | latency                                                                            |                                                      | -                                                              | -     | 2 <sup>(5)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                                                                      | f <sub>ADC</sub> = 30 MHz                            | 0.100                                                          | -     | 16                 | μs                 |

| IS T                             |                                                                                    | -                                                    | 3                                                              | -     | 480                | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                                                      | -                                                    | -                                                              | 2     | 3                  | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution       | 0.50                                                           | -     | 16.40              | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution       | 0.43                                                           | -     | 16.34              | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time (including sampling time)                                    | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution        | 0.37                                                           | -     | 16.27              | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution        | 0.30                                                           | -     | 16.20              | μs                 |

|                                  |                                                                                    | 9 to 492 (t <sub>S</sub> for sampling approximation) | +n-bit resolution f                                            | ssive | 1/f <sub>ADC</sub> |                    |

|                                  |                                                                                    | 12-bit resolution<br>Single ADC                      | -                                                              | -     | 2.4                | Msps               |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate<br>(f <sub>ADC</sub> = 36 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode     | -                                                              | -     | 4.5                | Msps               |

|                                  |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode   | -                                                              | -     | 7.2                | Msps               |

## Table 71. ADC characteristics (continued)

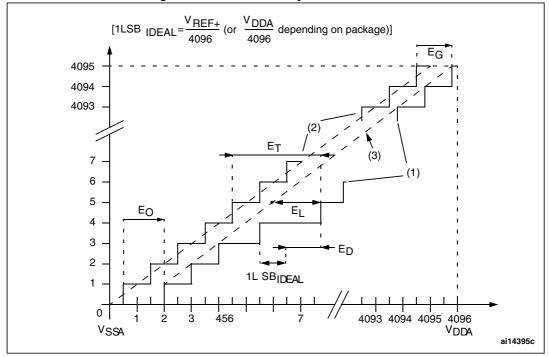

- 1. See also Table 73.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4 End point correlation line.

$E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 5.

EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

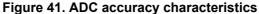

- 1. Refer to Table 71 for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

| Symbol Parameter                  |                         | Conditions | Min | Тур | Мах | Unit   |

|-----------------------------------|-------------------------|------------|-----|-----|-----|--------|

| T <sub>Coeff</sub> <sup>(2)</sup> | Temperature coefficient | -          | -   | 30  | 50  | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup> | Startup time            | -          | -   | 6   | 10  | μs     |

Table 80. internal reference voltage (continued)

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

## Table 81. Internal reference voltage calibration values

| Symbol                 | Parameter                                                                       | Memory address            |

|------------------------|---------------------------------------------------------------------------------|---------------------------|

| V <sub>REFIN_CAL</sub> | Raw data acquired at temperature of 30 $^\circ\text{C}$ <sub>VDDA</sub> = 3.3 V | 0x1FF0 F44A - 0x1FF0 F44B |

## 5.3.28 DAC electrical characteristics

| Symbol                            | Parameter                                                | Min                | Тур | Max                         | Unit | Comments                                                                                                                |

|-----------------------------------|----------------------------------------------------------|--------------------|-----|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                  | Analog supply voltage                                    | 1.7 <sup>(1)</sup> | -   | 3.6                         | V    | -                                                                                                                       |

| V <sub>REF+</sub>                 | Reference supply voltage                                 | 1.7 <sup>(1)</sup> | -   | 3.6                         | V    | $V_{REF+} \le V_{DDA}$                                                                                                  |

| V <sub>SSA</sub>                  | Ground                                                   | 0                  | -   | 0                           | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load with buffer ON                            | 5                  | -   | -                           | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(2)</sup>     | Impedance output with buffer<br>OFF                      | -                  | -   | 15                          | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                          | -                  | -   | 50                          | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage with buffer ON                     | 0.2                | -   | -                           | V    | It gives the maximum output excursion of the DAC.<br>It corresponds to 12-bit input code                                |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage with buffer ON                    | -                  | -   | V <sub>DDA</sub> -<br>0.2   | V    | (0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V and<br>(0x1C7) to (0xE38) at V <sub>REF+</sub> = 1.7 V                  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage<br>with buffer OFF                 | -                  | 0.5 | -                           | mV   | It gives the maximum output excursion of                                                                                |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage<br>with buffer OFF                | -                  | -   | V <sub>REF+</sub> -<br>1LSB | V    | the DAC.                                                                                                                |

| I <sub>VREF+</sub> <sup>(4)</sup> | DAC DC V <sub>REF</sub> current consumption in quiescent | -                  | 170 | 240                         | μA   | With no load, worst code (0x800) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

| VREF+` ′                          | mode (Standby mode)                                      | -                  | 50  | 75                          | μΑ   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

## Table 82. DAC characteristics

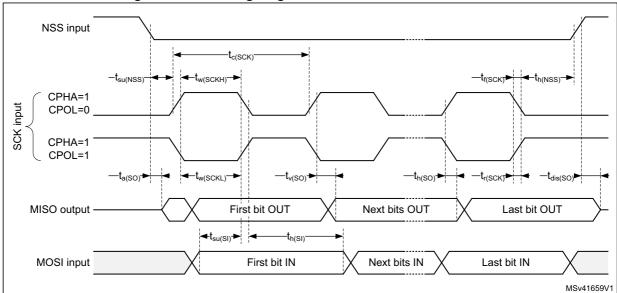

Figure 47. SPI timing diagram - slave mode and CPHA =  $1^{(1)}$

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

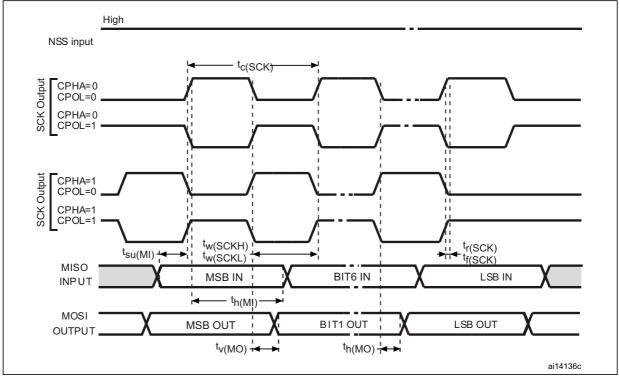

## Figure 48. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at  $0.5V_{DD}$  and with external C<sub>L</sub> = 30 pF.

Refer to *Section 5.3.20: I/O port characteristics* for more details on the input/output characteristics.

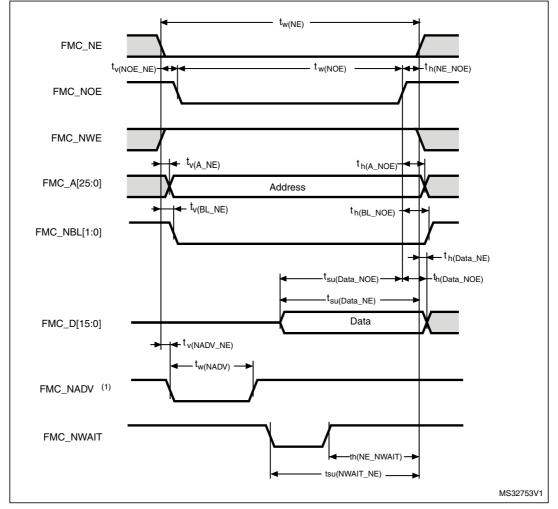

### Asynchronous waveforms and timings

*Figure 61* through *Figure 64* represent asynchronous waveforms and *Table 100* through *Table 107* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- Capcitive load CL = 30 pF

In all timing tables, the T<sub>HCLK</sub> is the HCLK clock period

#### Figure 61. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

## 5.3.34 Digital filter for Sigma-Delta Modulators (DFSDM) characteristics

Unless otherwise specified, the parameters given in *Table 122* for DFSDM are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30pF

- Measurement points are done at CMOS levels: 0.5 x VDD

Refer to *Section 5.3.20: I/O port characteristics* for more details on the input/output alternate function characteristics (DFSDM1\_CKINx, DFSDM1\_DATINx, DFSDM1\_CKOUT for DFSDM1).

| Symbol                | Parameter                               | Conditions                                                                                               | Min | Тур | Мах                              | Unit |

|-----------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-----|----------------------------------|------|

| f <sub>DFSDMCLK</sub> | DFSDM clock                             | 1.71 < V <sub>DD</sub> < 3.6 V                                                                           | -   | -   | f <sub>SYSCLK</sub>              |      |

|                       |                                         | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V | -   | -   | 20<br>(f <sub>DFSDMCLK</sub> /4) |      |

|                       |                                         | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>2.7 < V <sub>DD</sub> < 3.6 V  | -   | -   | 20<br>(f <sub>DFSDMCLK</sub> /4) |      |

|                       | Input clock<br>frequency                | SPI mode (SITP[1:0]=0,1),<br>Internal clock mode<br>(SPICKSEL[1:0]≠0),<br>1.71 < V <sub>DD</sub> < 3.6 V | -   | -   | 20<br>(f <sub>DFSDMCLK</sub> /4) | MHz  |

|                       |                                         | SPI mode (SITP[1:0]=0,1),<br>Internal clock mode<br>(SPICKSEL[1:0]≠0),<br>2.7 < V <sub>DD</sub> < 3.6 V  | -   | -   | 20<br>(f <sub>DFSDMCLK</sub> /4) |      |

| fскоит                | Output clock<br>frequency               | 1.71 < V <sub>DD</sub> < 3.6 V                                                                           | -   | -   | 20                               |      |

| DuCy <sub>CKOUT</sub> | Output clock<br>frequency duty<br>cycle | 1.71 < V <sub>DD</sub> < 3.6 V                                                                           | 45  | 50  | 55                               | %    |

### Table 122. DFSDM measured timing 1.71-3.6V

| Symbol                                         | Parameter                                             | Conditions                                                                                                                | Min                                     | Тур                  | Мах                                     | Unit |

|------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|-----------------------------------------|------|

| <sup>t</sup> wh(CKIN)<br><sup>t</sup> wl(CKIN) | Input clock high<br>and low time                      | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | TCKIN/2 - 0.5                           | T <sub>CKIN</sub> /2 | -                                       |      |

| t <sub>su</sub>                                | Data input setup<br>time                              | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | 2                                       | -                    | -                                       |      |

| t <sub>h</sub>                                 | Data input hold<br>time                               | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | 3                                       | -                    | -                                       | ns   |

| T <sub>Manchester</sub>                        | Manchester data<br>period (recovered<br>clock period) | Manchester mode<br>(SITP[1:0]=2,3),<br>Internal clock mode<br>(SPICKSEL[1:0] $\neq$ 0),<br>1.71 < V <sub>DD</sub> < 3.6 V | (CKOUTDIV+1)<br>* T <sub>DFSDMCLK</sub> | -                    | (2*CKOUTDIV)<br>* T <sub>DFSDMCLK</sub> |      |

| Table 122. DFSDM measur | red timing 1.71-3.6V (co | ontinued) |

|-------------------------|--------------------------|-----------|

|                         |                          |           |

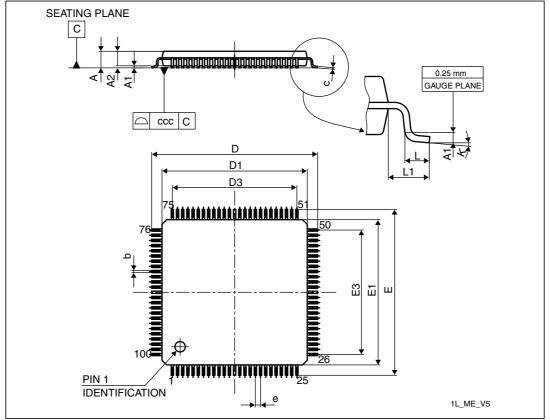

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 6.1 LQFP100 14x 14 mm, low-profile quad flat package information

Figure 83. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol | Min    | Тур         | Max    | Min                   | Тур    | Max    |  |

| A      | -      | -           | 1.600  |                       | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 29.800 | 30.000      | 30.200 | 1.1732                | 1.1811 | 1.1890 |  |

| D1     | 27.800 | 28.000      | 28.200 | 1.0945                | 1.1024 | 1.1102 |  |

| D3     | -      | 25.500      | -      | -                     | 1.0039 | -      |  |

| E      | 29.800 | 30.000      | 30.200 | 1.1732                | 1.1811 | 1.1890 |  |

| E1     | 27.800 | 28.000      | 28.200 | 1.0945                | 1.1024 | 1.1102 |  |

| E3     | -      | 25.500      | -      | -                     | 1.0039 | -      |  |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |  |

| k      | 0°     | 3.5°        | 7.0°   | 0°                    | 3.5°   | 7.0°   |  |

| ссс    | -      | -           | 0.080  | -                     | -      | 0.0031 |  |

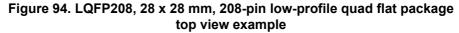

# Table 128. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

### LQFP208 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 6.7 TFBGA216, 13 x 13 x 0.8 mm thin fine-pitch ball grid array package information

Z Seating plane A2 A1 А D1 Χ A1 ball A1 ball D identifier index area F t e ÷00000000000 Α • 4 0000000000000000 G 000000000000000 000000 000000 E1 Е +00000 000000 00000 000000 0000000000000000 000000000000000 е Υ 0000000000000000 000000000000000 R 0000000000000000 15 Øb (216 balls) BOTTOM VIEW TOP VIEW A0L2\_ME\_V3

Figure 101. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

| Table 133. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array |  |

|-----------------------------------------------------------------------|--|

| package mechanical data                                               |  |

| O maked |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|---------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol  | Min    | Тур         | Max    | Min                   | Тур    | Max    |  |

| A       | -      | -           | 1.100  | -                     | -      | 0.0433 |  |

| A1      | 0.150  | -           | -      | 0.0059                | -      | -      |  |

| A2      | -      | 0.760       | -      | -                     | 0.0299 | -      |  |

| b       | 0.350  | 0.400       | 0.450  | 0.0138                | 0.0157 | 0.0177 |  |

| D       | 12.850 | 13.000      | 13.150 | 0.5118                | 0.5118 | 0.5177 |  |

| D1      | -      | 11.200      | -      | -                     | 0.4409 | -      |  |

| E       | 12.850 | 13.000      | 13.150 | 0.5118                | 0.5118 | 0.5177 |  |

| E1      | -      | 11.200      | -      | -                     | 0.4409 | -      |  |

| е       | -      | 0.800       | -      | -                     | 0.0315 | -      |  |

| F       | -      | 0.900       | -      | -                     | 0.0354 | -      |  |

DocID029041 Rev 4