Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status                | Active                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Core Processor                | ARM® Cortex®-M7                                                                                                       |

| Core Size                     | 32-Bit Single-Core                                                                                                    |

| Speed                         | 216MHz                                                                                                                |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                                          |

| Number of I/O                 | 168                                                                                                                   |

| Program Memory Size           | 1MB (1M x 8)                                                                                                          |

| Program Memory Type           | FLASH                                                                                                                 |

| EEPROM Size                   | ·                                                                                                                     |

| RAM Size                      | 512K x 8                                                                                                              |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                                           |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                                 |

| Oscillator Type               | Internal                                                                                                              |

| Operating Temperature         | -40°C ~ 105°C (TA)                                                                                                    |

| Mounting Type                 | Surface Mount                                                                                                         |

| Package / Case                | 216-TFBGA                                                                                                             |

| Supplier Device Package       | 216-TFBGA (13x13)                                                                                                     |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f765ngh7tr                                               |

|                               |                                                                                                                       |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to *Table 3* for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on V\_{CAP \ 1} and V\_{CAP \ 2} pin.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. '-' means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

## 2.19.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In the regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32

The RTC is functional in  $V_{BAT}$  mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in  $V_{BAT}$  mode, but is functional in all low-power modes.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

### 2.21 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup and LPTIM1 asynchronous interrupt).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

#### Table 5. Voltage regulator modes in stop mode

### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering

| Timer<br>type        | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                      | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complem<br>entary<br>output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) <sup>(1)</sup> |

|----------------------|-----------------|-----------------------|-------------------------|------------------------------------------|------------------------------|---------------------------------|-----------------------------|------------------------------------|-----------------------------------------------|

| Advanced<br>-control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                         | 108                                | 216                                           |

|                      | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                          | 54                                 | 108/216                                       |

|                      | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                          | 54                                 | 108/216                                       |

| General              | TIM9            | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 2                               | No                          | 108                                | 216                                           |

| purpose              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 1                               | No                          | 108                                | 216                                           |

|                      | TIM12           | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 2                               | No                          | 54                                 | 108/216                                       |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 1                               | No                          | 54                                 | 108/216                                       |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                          | 54                                 | 108/216                                       |

| Table 6. | Timer | feature  | com   | parison |

|----------|-------|----------|-------|---------|

|          |       | ioutui o | 00111 | parioon |

1. The maximum timer clock is either 108 or 216 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

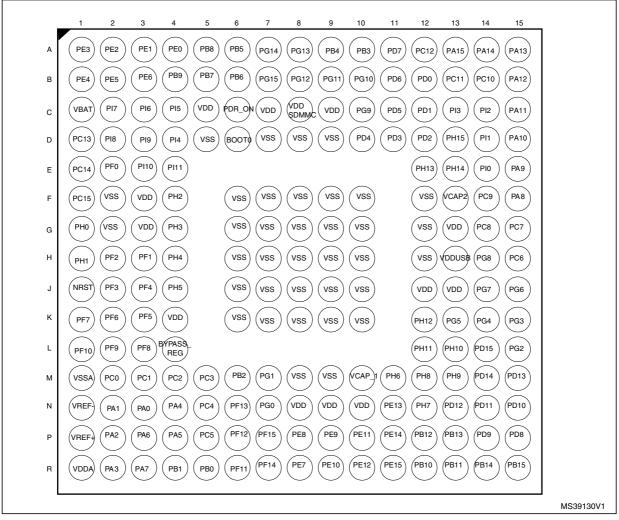

Figure 18. STM32F76xxx UFBGA176 ballout

1. The above figure shows the package top view.

| Name                   | Abbreviation        | Definition                                                                                                                            |  |  |  |  |  |  |  |

|------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin name               |                     | Unless otherwise specified in brackets below the pin name, the pin function during and after reset is the same as the actual pin name |  |  |  |  |  |  |  |

|                        | S                   | Supply pin                                                                                                                            |  |  |  |  |  |  |  |

| Pin type               | I                   | Input only pin                                                                                                                        |  |  |  |  |  |  |  |

|                        | I/O                 | Input / output pin                                                                                                                    |  |  |  |  |  |  |  |

|                        | FT 5 V tolerant I/O |                                                                                                                                       |  |  |  |  |  |  |  |

| I/O structure          | TTa                 | TTa 3.3 V tolerant I/O directly connected to ADC                                                                                      |  |  |  |  |  |  |  |

| 1/O structure          | В                   | Dedicated BOOT pin                                                                                                                    |  |  |  |  |  |  |  |

|                        | RST                 | Bidirectional reset pin with weak pull-up resistor                                                                                    |  |  |  |  |  |  |  |

| Notes                  | Unless otherwise    | specified by a note, all I/Os are set as floating inputs during and after reset                                                       |  |  |  |  |  |  |  |

| Alternate<br>functions | Functions selected  | Functions selected through GPIOx_AFR registers                                                                                        |  |  |  |  |  |  |  |

| Additional functions   | Functions directly  | Functions directly selected/enabled through peripheral registers                                                                      |  |  |  |  |  |  |  |

### Table 9. Legend/abbreviations used in the pinout table

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions

|         |         |              | l       | Pin N   | umbe     | ər                      |         |                |          |                                |          |               |       |                                                                                               |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

|         | -       | TM32<br>TM32 |         |         | I        | -                       |         | F768/<br>F769: |          | reset                          |          |               |       |                                                                                               |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 1       | 1       | A2           | 1       | 1       | A3       | E10                     | 1       | 1              | A3       | PE2                            | I/O      | FT            | -     | TRACECLK, SPI4_SCK,<br>SAI1_MCLK_A,<br>QUADSPI_BK1_IO2,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT | -                       |

| 2       | 2       | A1           | 2       | 2       | A2       | F10                     | 2       | 2              | A2       | PE3                            | I/O      | FT            | -     | TRACED0, SAI1_SD_B,<br>FMC_A19, EVENTOUT                                                      | -                       |

|         |         |              | l       | Pin N   | umb      | er                      |         |                |          |                                |          |               |       |                                                                                                                                                 |                                              |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         |         | F768/<br>F769: |          | reset                          |          |               |       |                                                                                                                                                 |                                              |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                             | Additional<br>functions                      |

| 17      | 28      | M4           | 34      | 37      | M4       | NC                      | 34      | 37             | M4       | PC2                            | I/O      | FT            | -     | DFSDM1_CKIN1,<br>SPI2_MISO,<br>DFSDM1_CKOUT,<br>OTG_HS_ULPI_DIR,<br>ETH_MII_TXD2,<br>FMC_SDNE0, EVENTOUT                                        | ADC1_IN12,<br>ADC2_IN12,<br>ADC3_IN12        |

| 18      | 29      | M5           | 35      | 38      | L4       | NC                      | 35      | 38             | L4       | PC3                            | I/O      | FT            | -     | DFSDM1_DATIN1,<br>SPI2_MOSI/I2S2_SD,<br>OTG_HS_ULPI_NXT,<br>ETH_MII_TX_CLK,<br>FMC_SDCKE0,<br>EVENTOUT                                          | ADC1_IN13,<br>ADC2_IN13,<br>ADC3_IN13        |

| -       | 30      | -            | 36      | 39      | J5       | -                       | 36      | 39             | J5       | VDD                            | s        | -             | -     | -                                                                                                                                               | -                                            |

| -       | -       | -            | -       | -       | J6       | -                       | -       | -              | J6       | VSS                            | s        | -             | -     | -                                                                                                                                               | -                                            |

| 19      | 31      | M1           | 37      | 40      | M1       | M11                     | 37      | 40             | M1       | VSSA                           | s        | -             | -     | -                                                                                                                                               | -                                            |

| -       | -       | N1           | -       | -       | N1       | -                       | -       | -              | N1       | VREF-                          | s        | -             | -     | -                                                                                                                                               | -                                            |

| 20      | 32      | P1           | 38      | 41      | P1       | -                       | 38      | 41             | P1       | VREF+                          | S        | -             | -     | -                                                                                                                                               | -                                            |

| 21      | 33      | R1           | 39      | 42      | R1       | M12                     | 39      | 42             | R1       | VDDA                           | s        | -             | -     | -                                                                                                                                               | -                                            |

| 22      | 34      | N3           | 40      | 43      | N3       | M13                     | 40      | 43             | N3       | PA0-<br>WKUP                   | I/O      | FT            | (4)   | TIM2_CH1/TIM2_ETR,<br>TIM5_CH1, TIM8_ETR,<br>USART2_CTS,<br>UART4_TX, SAI2_SD_B,<br>ETH_MII_CRS,<br>EVENTOUT                                    | ADC1_IN0,<br>ADC2_IN0,<br>ADC3_IN0,<br>WKUP1 |

| 23      | 35      | N2           | 41      | 44      | N2       | J11                     | 41      | 44             | N2       | PA1                            | 1/0      | FT            | -     | TIM2_CH2, TIM5_CH2,<br>USART2_RTS,<br>UART4_RX,<br>QUADSPI_BK1_IO3,<br>SAI2_MCLK_B,<br>ETH_MII_RX_CLK/ETH_R<br>MII_REF_CLK, LCD_R2,<br>EVENTOUT | ADC1_IN1,<br>ADC2_IN1,<br>ADC3_IN1           |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|         |         |              |         | Pin N   | umbe     | ər                      |               |         |          |                                |          |               |       |                                                                                                                                          |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         | -       | TM32<br>TM32 |         |         |          |                         | FM32I<br>FM32 |         |          | reset                          |          |               |       |                                                                                                                                          |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                      | Additional<br>functions |

| 65      | 98      | G14          | 117     | 140     | G14      | G8                      | 121           | 140     | G14      | PC8                            | I/O      | FT            | -     | TRACED1, TIM3_CH3,<br>TIM8_CH3, UART5_RTS,<br>USART6_CK,<br>FMC_NE2/FMC_NCE,<br>SDMMC1_D0, DCMI_D2,<br>EVENTOUT                          |                         |

| 66      | 99      | F14          | 118     | 141     | F14      | E1                      | 122           | 141     | F14      | PC9                            | I/O      | FT            | -     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, UART5_CTS,<br>QUADSPI_BK1_IO0,<br>LCD_G3, SDMMC1_D1,<br>DCMI_D3, LCD_B2,<br>EVENTOUT |                         |

| 67      | 100     | F15          | 119     | 142     | F15      | E2                      | 123           | 142     | F15      | PA8                            | I/O      | FT            | -     | MCO1, TIM1_CH1,<br>TIM8_BKIN2, I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF, CAN3_RX,<br>UART7_RX, LCD_B3,<br>LCD_R6, EVENTOUT                  | -                       |

| 68      | 101     | E15          | 120     | 143     | E15      | F4                      | 124           | 143     | E15      | PA9                            | I/O      | FT            | -     | TIM1_CH2, I2C3_SMBA,<br>SPI2_SCK/I2S2_CK,<br>USART1_TX, DCMI_D0,<br>LCD_R5, EVENTOUT                                                     | OTG_FS_V<br>BUS         |

| 69      | 102     | D15          | 121     | 144     | D15      | F5                      | 125           | 144     | D15      | PA10                           | I/O      | FT            | -     | TIM1_CH3, USART1_RX,<br>LCD_B4, OTG_FS_ID,<br>MDIOS_MDIO, DCMI_D1,<br>LCD_B1, EVENTOUT                                                   | -                       |

| 70      | 103     | C15          | 122     | 145     | C15      | E3                      | 126           | 145     | C15      | PA11                           | I/O      | FT            | -     | TIM1_CH4,<br>SPI2_NSS/I2S2_WS,<br>UART4_RX,<br>USART1_CTS, CAN1_RX,<br>OTG_FS_DM, LCD_R4,<br>EVENTOUT                                    | -                       |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

| 5 |

|---|

|   |

### Table 12. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx alternate

|        |      |                       |                           |              |                                            |                               | functio                                                | on map                                                         | oing (co                                                                       | ntinued                                                       | )                                                  |                                                                        |                              |                                                |                  |        |              |

|--------|------|-----------------------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|--------|--------------|

|        |      | AF0                   | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             | AF14   | AF15         |

| Po     | ort  | SYS                   | 12C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD    | SYS          |

|        | PA11 | -                     | TIM1_C<br>H4              | -            | -                                          | -                             | SPI2_NS<br>S/I2S2_<br>WS                               | UART4_<br>RX                                                   | USART1<br>_CTS                                                                 | -                                                             | CAN1_R<br>X                                        | OTG_FS_<br>DM                                                          | -                            | -                                              | -                | LCD_R4 | EVEN<br>TOUT |

|        | PA12 | -                     | TIM1_ET<br>R              | -            | -                                          | -                             | SPI2_SC<br>K/I2S2_<br>CK                               | UART4_<br>TX                                                   | USART1<br>_RTS                                                                 | SAI2_FS<br>_B                                                 | CAN1_T<br>X                                        | OTG_FS_<br>DP                                                          | -                            | -                                              | -                | LCD_R5 | EVEN<br>TOUT |

| Port A | PA13 | JTMS-<br>SWDIO        | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PA14 | JTCK-<br>SWCLK        | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PA15 | JTDI                  | TIM2_C<br>H1/TIM2<br>_ETR | -            | -                                          | HDMI-<br>CEC                  | SPI1_NS<br>S/I2S1_<br>WS                               | SPI3_NS<br>S/I2S3_<br>WS                                       | SPI6_NS<br>S                                                                   | UART4_<br>RTS                                                 | -                                                  | -                                                                      | CAN3_TX                      | UART7_<br>TX                                   | -                | -      | EVEN<br>TOUT |

|        | PB0  | -                     | TIM1_C<br>H2N             | TIM3_C<br>H3 | TIM8_CH<br>2N                              | -                             | -                                                      | DFSDM1<br>_CKOUT                                               | -                                                                              | UART4_<br>CTS                                                 | LCD_R3                                             | OTG_HS_<br>ULPI_D1                                                     | ETH_MII_<br>RXD2             | -                                              | -                | LCD_G1 | EVEN<br>TOUT |

|        | PB1  | -                     | TIM1_C<br>H3N             | TIM3_C<br>H4 | TIM8_CH<br>3N                              | -                             | -                                                      | DFSDM1<br>_DATIN1                                              | -                                                                              | -                                                             | LCD_R6                                             | OTG_HS_<br>ULPI_D2                                                     | ETH_MII_<br>RXD3             | -                                              | -                | LCD_G0 | EVEN<br>TOUT |

|        | PB2  | -                     | -                         | -            | -                                          | -                             | -                                                      | SAI1_SD<br>_A                                                  | SPI3_MO<br>SI/I2S3_<br>SD                                                      |                                                               | QUADSP<br>I_CLK                                    | DFSDM1_<br>CKIN1                                                       | -                            | -                                              | -                | -      | EVEN<br>TOUT |

| Port B | PB3  | JTDO/T<br>RACES<br>WO | TIM2_C<br>H2              | -            | -                                          | -                             | SPI1_SC<br>K/I2S1_<br>CK                               | SPI3_SC<br>K/I2S3_<br>CK                                       | -                                                                              | SPI6_SC<br>K                                                  | -                                                  | SDMMC2<br>_D2                                                          | CAN3_R<br>X                  | UART7_<br>RX                                   | -                | -      | EVEN<br>TOUT |

|        | PB4  | NJTRST                | -                         | TIM3_C<br>H1 | -                                          | -                             | SPI1_MI<br>SO                                          | SPI3_MI<br>SO                                                  | SPI2_NS<br>S/I2S2_<br>WS                                                       | SPI6_MI<br>SO                                                 | -                                                  | SDMMC2<br>_D3                                                          | CAN3_TX                      | UART7_<br>TX                                   | -                | -      | EVEN<br>TOUT |

|        | PB5  | -                     | UART5_<br>RX              | TIM3_C<br>H2 | -                                          | I2C1_SM<br>BA                 | SPI1_M<br>OSI/I2S1<br>_SD                              | SPI3_M<br>OSI/I2S3<br>_SD                                      | -                                                                              | SPI6_MO<br>SI                                                 | CAN2_R<br>X                                        | OTG_HS_<br>ULPI_D7                                                     | ETH_PPS<br>_OUT              | FMC_SD<br>CKE1                                 | DCMI_D<br>10     | LCD_G7 | EVEN<br>TOUT |

|        | PB6  | -                     | UART5_<br>TX              | TIM4_C<br>H1 | HDMI-<br>CEC                               | I2C1_SC<br>L                  | -                                                      | DFSDM1<br>_DATIN5                                              | USART1<br>_TX                                                                  | -                                                             | CAN2_T<br>X                                        | QUADSPI<br>_BK1_NC<br>S                                                | I2C4_SC<br>L                 | FMC_SD<br>NE1                                  | DCMI_D<br>5      | -      | EVEN<br>TOUT |

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

Pinouts and pin description

93/255

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | HDMI-CEC            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | I2C4                |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | SPDIFRX             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | CAN3                |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | LPTIM1              |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 13. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx register boundary addresses<sup>(1)</sup> (continued)

1. The gray color is used for reserved Flash memory addresses.

| 0               | <b>D</b>          | 0                                            |                         | -   |           | Max <sup>(1)</sup> |                                                                                         |      |

|-----------------|-------------------|----------------------------------------------|-------------------------|-----|-----------|--------------------|-----------------------------------------------------------------------------------------|------|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур | TA= 25 °C | TA=85 °C           | °C     TA=105 °C       -     -       255     220       198       161       105       76 | Unit |

|                 |                   |                                              | 216                     | 176 | 194       | 240                | -                                                                                       |      |

|                 |                   |                                              | 200                     | 164 | 181       | 227                | 255                                                                                     | 1    |

|                 |                   |                                              | 180                     | 149 | 163       | 198                | 220                                                                                     |      |

|                 |                   | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 133 | 145       | 178                | 198                                                                                     | 1    |

|                 |                   |                                              | 144                     | 106 | 116       | 143                | 161                                                                                     |      |

|                 |                   |                                              | 60                      | 54  | 60        | 87                 | 105                                                                                     | 1    |

|                 | Supply current in |                                              | 25                      | 27  | 31        | 58                 | 76                                                                                      | mA   |

| I <sub>DD</sub> | RUN mode          |                                              | 216                     | 77  | 88        | 135                | -                                                                                       | 1    |

|                 |                   |                                              | 200                     | 72  | 82        | 129                | 157                                                                                     | 1    |

|                 |                   |                                              | 180                     | 67  | 75        | 110                | 131                                                                                     | 1    |

|                 |                   | All peripherals disabled <sup>(3)</sup>      | 168                     | 60  | 67        | 99                 | 120                                                                                     |      |

|                 |                   | disabled                                     | 144                     | 50  | 56        | 83                 | 101                                                                                     | 1    |

|                 |                   |                                              | 60                      | 29  | 34        | 60                 | 78                                                                                      | ]    |

|                 |                   |                                              | 25                      | 15  | 19        | 45                 | 63                                                                                      | ]    |

## Table 28. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (Dual bank mode), regulator ON

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

|        |                    |                                                                 |                            | Typ <sup>(1)</sup>         |                            |                                                                                       | Max <sup>(2)</sup>    |                                                                                                                                      |      |

|--------|--------------------|-----------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|

| Symbol | Parameter          | Conditions                                                      | Ţ                          | <sub>A</sub> = 25 °        | С                          | $\begin{array}{c c} T_A = & T_A = \\ 25 \ ^{\circ}C & 85 \ ^{\circ}C & 1 \end{array}$ |                       | T <sub>A</sub> =<br>105 °C                                                                                                           | Unit |

|        |                    |                                                                 | V <sub>DD</sub> =<br>1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V                                                                                     | / <sub>DD</sub> = 3.3 | TA =         105 °C         38 <sup>(3)</sup> 48 <sup>(3)</sup> 55         56         57         59         65         65         68 |      |

|        |                    | Backup SRAM OFF, RTC and LSE OFF                                | 1.1                        | 1.9                        | 2.4                        | 5 <sup>(3)</sup>                                                                      | 18 <sup>(3)</sup>     | 38 <sup>(3)</sup>                                                                                                                    |      |

|        |                    | Backup SRAM ON, RTC and LSE OFF                                 | 1.9                        | 2.7                        | 3.2                        | 6 <sup>(3)</sup>                                                                      | 23 <sup>(3)</sup>     | 48 <sup>(3)</sup>                                                                                                                    |      |

|        |                    | Backup SRAM OFF, RTC ON and LSE in low drive mode               | 1.7                        | 2.7                        | 3.5                        | 7                                                                                     | 26                    | 55                                                                                                                                   |      |

|        | Supply current     | Backup SRAM OFF, RTC ON<br>and LSE in medium low drive<br>mode  | 1.7                        | 2.7                        | 3.5                        | 7                                                                                     | 26                    | 56                                                                                                                                   |      |

|        |                    | Backup SRAM OFF, RTC ON<br>and LSE in medium high drive<br>mode | 1.8                        | 2.8                        | 3.6                        | 8                                                                                     | 28                    | 57                                                                                                                                   |      |

|        | in Standby<br>mode | Backup SRAM OFF, RTC ON<br>and LSE in high drive mode           | 1.9                        | 2.9                        | 3.7                        | 8                                                                                     | 28                    | 59                                                                                                                                   | μA   |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in low drive mode             | 2.4                        | 3.4                        | 4.3                        | 8                                                                                     | 31                    | 65                                                                                                                                   |      |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in Medium low drive<br>mode   | 2.4                        | 3.5                        | 4.3                        | 8                                                                                     | 31                    | 65                                                                                                                                   |      |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in Medium high drive<br>mode  | 2.6                        | 3.7                        | 4.5                        | 8                                                                                     | 33                    | 68                                                                                                                                   |      |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in High drive mode            | 2.6                        | 3.7                        | 4.5                        | 9                                                                                     | 33                    | 68                                                                                                                                   |      |

Table 36. Typical and maximum current consumptions in Standby mode

The typical current consumption values are given with PDR OFF (internal reset OFF). When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2 μA.

2. Guaranteed by characterization results, unless otherwise specified.

3. Guaranteed by test in production.

|                      |                                    | characteristics   |         | illueu) | -   |      |

|----------------------|------------------------------------|-------------------|---------|---------|-----|------|

| Symbol               | Parameter                          | Conditions        | Min     | Тур     | Мах | Unit |

| V <sub>IL</sub>      | Output low level voltage           | -                 | 1.1     | 1.2     | 1.2 | V    |

| V <sub>IL-ULPS</sub> | Output high level voltage          | -                 | -50     | -       | 50  | mV   |

| V <sub>IH</sub>      | Output impedance of LP transmitter | -                 | 110     | -       | -   | Ω    |

| V <sub>hys</sub>     | 15%-85% rise and fall time         | -                 | -       | -       | 25  | ns   |

|                      | LP Contention                      | Detector Characte | ristics |         |     |      |

| V <sub>ILCD</sub>    | Logic 0 contention threshold       | -                 | -       | -       | 200 | mV   |

| V <sub>IHCD</sub>    | Logic 0 contention threshold       | -                 | 450     | -       | -   | IIIV |

|                      |                                    |                   |         |         |     |      |

Table 51. MIPI D-PHY characteristics<sup>(1)</sup> (continued)

1. Guaranteed based on test during characterization.

# Table 52. MIPI D-PHY AC characteristics LP mode and HS/LP transitions<sup>(1)</sup>

| Symbol                                                 | Parameter                                                                                                                                            | Conditions | Min | Тур | Max | Unit |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|------|

| T <sub>LPX</sub>                                       | Transmitted length of any Low-<br>Power state period                                                                                                 | -          | 50  | -   | -   |      |

| T <sub>CLK-PREPARE</sub>                               | Time that the transmitter drives<br>the Clock Lane LP-00 Line<br>state immediately before the<br>HS-0 Line state starting the HS<br>transmission.    | -          | 38  | -   | 95  | ns   |

| T <sub>CLK-PREPARE</sub><br>+<br>T <sub>CLK-ZERO</sub> | Time that the transmitter drives<br>the HS-0 state prior to starting<br>the clock.                                                                   | -          | 300 | -   | -   |      |

| T <sub>CLK-PRE</sub>                                   | Time that the HS clock shall be<br>driven by the transmitter prior to<br>any associated Data Lane<br>beginning the transition from<br>LP to HS mode. | -          | 8   | -   | -   | UI   |

| Symbol   | Parameter                | Conditions                  | Min                   | Тур | Max  | Unit |

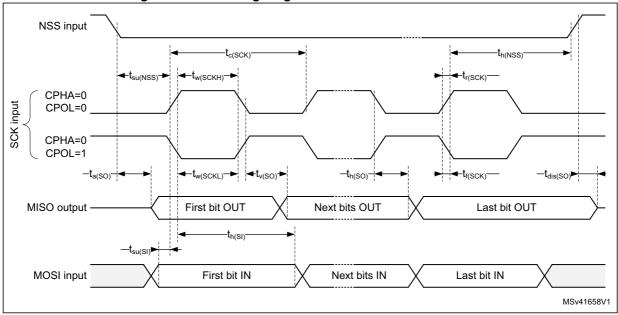

|----------|--------------------------|-----------------------------|-----------------------|-----|------|------|

| tsu(MI)  | Data input setup time    | Master mode                 | 4<br>9 <sup>(4)</sup> | -   | -    |      |

| tsu(SI)  |                          | Slave mode                  | 4.5                   | -   | -    |      |

| th(MI)   | Data input hold time     | Master mode                 | 3<br>0 <sup>(4)</sup> | -   | -    |      |

| th(SI)   |                          | Slave mode                  | 2                     | -   | -    |      |

| ta(SO)   | Data output access time  | Slave mode                  | 7                     | -   | 21   |      |

| tdis(SO) | Data output disable time | Slave mode                  | 5                     | -   | 12   | ns   |

| tu(SO)   |                          | Slave mode 2.7≤VDD≤3.6V     | -                     | 6.5 | 10   |      |

| tv(SO)   | Data output valid time   | Slave mode 1.71≤VDD≤3.6V    | -                     | 6.5 | 13.5 |      |

| tv(MO)   |                          | Master mode                 | -                     | 2   | 6    |      |

| th(SO)   | Data output hold time    | Slave mode<br>1.71≤VDD≤3.6V | 4.5                   | -   | -    |      |

| th(MO)   |                          | Master mode                 | 0                     | -   | -    | 1    |

Table 85. SPI dynamic characteristics<sup>(1)</sup> (continued)

2. Excepting SPI1 with SCK IO pin mapped on PA5. In this configuration, Maximum achievable frequency is 40MHz.

Maximum Frequency of Slave Transmitter is determined by sum of Tv(SO) and Tsu(MI) intervals which has to fit into SCK level phase preceding the SCK sampling edge. This value can be achieved when it communicates with a Master having Tsu(MI)=0 while signal Duty(SCK)=50%.

4. Only for SPI6.

Figure 46. SPI timing diagram - slave mode and CPHA = 0

| Symbol          | Parameter                                                 | Conditions                                  | Min.<br>(1) | Тур. | Max.<br>(1)           | Unit |

|-----------------|-----------------------------------------------------------|---------------------------------------------|-------------|------|-----------------------|------|

| Р               | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | <u> </u>                                    | 17          | 21   | 24                    |      |

| R <sub>PD</sub> | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>DD</sub>           | 2.4         | 5.2  | 8                     | kΩ   |

|                 | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub> 1.5 1.8 2 | 2.1         |      |                       |      |

| R <sub>PU</sub> | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>           | 0.55        | 0.95 | (1)<br>24<br>8<br>2.1 |      |

Table 91. USB OTG full speed DC electrical characteristics (continued)

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DDUSB</sub> voltage range.

3. Guaranteed by design.

4. R<sub>L</sub> is the load connected on the USB OTG full speed drivers.

Note:

When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200 µA current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

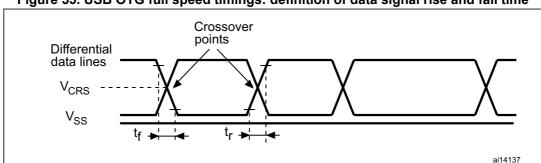

Figure 55. USB OTG full speed timings: definition of data signal rise and fall time

| Table 92 | USB OTG fu | ll sneed electrica | I characteristics <sup>(1)</sup> |

|----------|------------|--------------------|----------------------------------|

|          | 030 010 10 | II SPEEU EIELIILA  |                                  |

|                  | Driver characteristics                 |                                |     |     |      |  |  |  |

|------------------|----------------------------------------|--------------------------------|-----|-----|------|--|--|--|

| Symbol           | Parameter                              | Conditions                     | Min | Max | Unit |  |  |  |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |  |

| t <sub>rfm</sub> | Rise/ fall time matching               | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |  |

| V <sub>CRS</sub> | Output signal crossover voltage        | -                              | 1.3 | 2.0 | V    |  |  |  |

| Z <sub>DRV</sub> | Output driver impedance <sup>(3)</sup> | Driving high or<br>low         | 28  | 44  | Ω    |  |  |  |

| Symbol               | Parameter                        | Min | Тур | Мах  | Unit |

|----------------------|----------------------------------|-----|-----|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 1   | -   | -    |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 2   | -   | -    |      |

| t <sub>su(CRS)</sub> | Carrier sense setup time         | 2   | -   | -    | ns   |

| t <sub>ih(CRS)</sub> | Carrier sense hold time          | 2   | -   | -    | 115  |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 7.5 | 8   | 12   | ]    |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 7   | 7.5 | 12.5 | ]    |

Table 97. Dynamics characteristics: Ethernet MAC signals for RMII<sup>(1)</sup>

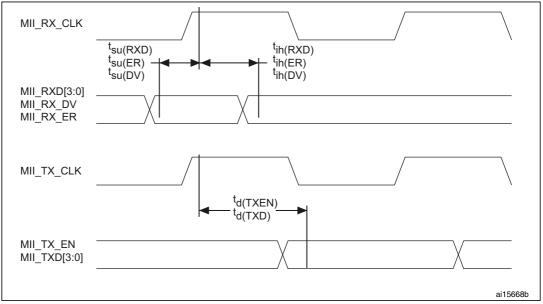

*Table 98* gives the list of Ethernet MAC signals for MII and *Figure 58* shows the corresponding timing diagram.

Figure 59. Ethernet MII timing diagram

Table 98. Dynamics characteristics: Ethernet MAC signals for  $\ensuremath{\mathsf{MII}}^{(1)}$

| Symbol               | Parameter                        | Min | Тур | Max | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 1   | -   | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 2.5 | -   | -   |      |

| t <sub>su(DV)</sub>  | Data valid setup time            | 1.5 | -   | -   |      |

| t <sub>ih(DV)</sub>  | Data valid hold time             | 0.5 | -   | -   |      |

| t <sub>su(ER)</sub>  | Error setup time                 | 2.5 | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  | 0.5 | -   | -   |      |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 10  | 8   | 13  |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 9   | 7.5 | 13  |      |

|                             | Berometer                                |                          | •   | Unit |

|-----------------------------|------------------------------------------|--------------------------|-----|------|

| Symbol                      | Parameter                                | Min                      | Мах | Unit |

| t <sub>(CLK)</sub>          | FMC_CLK period                           | 2T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)        | -                        | 2   |      |

| t <sub>(CLKH-NExH)</sub>    | FMC_CLK high to FMC_NEx high (x= 02)     | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low              | -                        | 0.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high             | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)     | -                        | 2.5 |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | T <sub>HCLK</sub>        | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                        | 1.5 |      |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> + 1    | -   |      |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                        | 3.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | -                        | 2   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> + 1    | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 3.5                      | -   |      |

Table 111. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup>

### NAND controller waveforms and timings

*Figure 69* through *Figure 72* represent synchronous waveforms, and *Table 112* and *Table 113* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

|         |                         |                                   |             |     | <u> </u>    |      |

|---------|-------------------------|-----------------------------------|-------------|-----|-------------|------|

| Symbol  | Parameter               | Conditions                        | Min         | Тур | Мах         | Unit |

| tw(CKH) | Quad-SPI clock high and |                                   | t(CK)/2 - 1 | -   | t(CK)/2     |      |

| tw(CKL) | low time                |                                   | t(CK)/2     | -   | t(CK)/2 + 1 |      |

| ts(IN)  | Data input setup time   |                                   | 0.5         | -   | -           |      |

| th(IN)  | Data input hold time    | -                                 | 3           | -   | -           | ns   |

| tv(OUT) | Data output valid time  | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>  | -           | 1.5 | 3.5         |      |

|         |                         | 1.71 V <v<sub>DD&lt;3.6 V</v<sub> | -           | 1.5 | 2           |      |

| th(OUT) | Data output hold time   | -                                 | 0.5         | -   | -           |      |

Table 118. Quad-SPI characteristics (continued)in SDR mode<sup>(1)</sup> (continued)

| Symbol                | Parameter                           | Conditions                                     | Min                           | Тур                           | Max                           | Unit    |

|-----------------------|-------------------------------------|------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|---------|

|                       | Quad-SPI clock<br>frequency         | 2.7 V <v<sub>DD&lt;3.6 V<br/>CL=20 pF</v<sub>  | -                             | -                             | 80                            | MH<br>z |

| Fck1/t(CK)            |                                     | 1.8 V <v<sub>DD&lt;3.6 V<br/>CL=15 pF</v<sub>  | -                             | -                             | 80                            |         |

|                       |                                     | 1.71 V <v<sub>DD&lt;3.6 V<br/>CL=10 pF</v<sub> | -                             | -                             | 80                            |         |

| tw(CKH)               | Quad-SPI clock high<br>and low time | -                                              | t(CK)/2 - 1                   | -                             | t(CK)/2                       | ns      |

| tw(CKL)               |                                     |                                                | t(CK)/2                       | -                             | t(CK)/2<br>+ 1                |         |

| ts(IN),               | Data input setup time               | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | 0.75                          | -                             | -                             |         |

| tsf(IN)               |                                     | 1.71 V <v<sub>DD&lt;2 V</v<sub>                | 0.5                           | -                             | -                             |         |

| thr(IN),              | Data input hold time                | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | 2                             | -                             | -                             |         |

| thf(IN)               |                                     | 1.71 V <v<sub>DD&lt;2 V</v<sub>                | 3                             | -                             | -                             |         |

|                       | Data output valid time              | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | -                             | 8.5                           | 10                            |         |

| tvr(OUT),<br>tvf(OUT) |                                     | 1.71 V <v<sub>DD&lt;3.6 V<br/>DHHC=0</v<sub>   | -                             | 8                             | 12                            |         |

|                       |                                     | DHHC=1<br>Pres=1, 2                            | -                             | T <sub>HCLK</sub> /2 +<br>1.5 | T <sub>HCLK</sub> /2<br>+ 2.5 |         |

| the (OUT)             |                                     | DHHC=0                                         | 7.5                           | -                             | -                             |         |

| thr(OUT),<br>thf(OUT) | Data output hold time               | DHHC=1<br>Pres=1, 2                            | T <sub>HCLK</sub> /2<br>+ 0.5 | -                             | -                             |         |

| Table 119. Quad SPI characteristics in DDR mode <sup>(1)</sup> |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

1. Guaranteed by characterization results.

57

### LQFP144 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

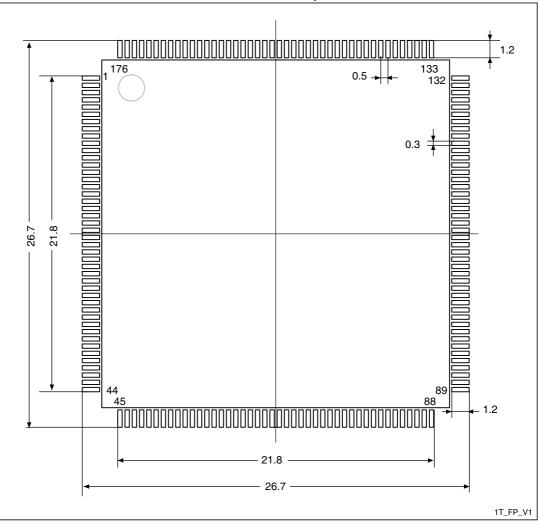

Figure 90. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

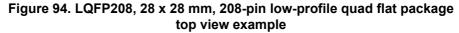

### LQFP208 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.