Welcome to E-XFL.COM

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                             |

| Number of I/O                 | 82                                                                                                       |

| Program Memory Size           | 1MB (1M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | -                                                                                                        |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 16x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 100-TFBGA                                                                                                |

| Supplier Device Package       | 100-TFBGA (8x8)                                                                                          |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f765vgh6                                    |

|                               |                                                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.3 Embedded Flash memory

The STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx devices embed a Flash memory of up to 2 Mbytes available for storing programs and data. The Flash interface features:

- Single /or Dual bank operating modes,

- Read-While-Write (RWW) in Dual bank mode.

### 2.4 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

### 2.5 Embedded SRAM

All the devices feature:

- System SRAM up to 512 Kbytes:

- SRAM1 on AHB bus Matrix: 368 Kbytes

- SRAM2 on AHB bus Matrix: 16 Kbytes

- DTCM-RAM on TCM interface (Tighly Coupled Memory interface): 128 Kbytes for critical real-time data.

- Instruction RAM (ITCM-RAM) 16 Kbytes:

- It is mapped on TCM interface and reserved only for CPU Execution/Instruction useful for critical real-time routines.

The Data TCM RAM is accessible by the GP-DMAs and peripherals DMAs through specific AHB slave of the CPU. The instruction TCM RAM is reserved only for CPU. It is accessed at CPU clock speed with 0 wait states.

• 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

### 2.7 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. The configuration is made by software and the transfer sizes between the source and the destination are independent.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDMMC

- Camera interface (DCMI)

- ADC

- SAI

- SPDIFRX

- Quad-SPI

- HDMI-CEC

- JPEG codec

- DFSDM1

### 2.8 Flexible memory controller (FMC)

The Flexible memory controller (FMC) includes three memory controllers:

- The NOR/PSRAM memory controller

- The NAND/memory controller

- The Synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) controller

The main features of the FMC controller are the following:

- Interface with static-memory mapped devices including:

- Static random access memory (SRAM)

- NOR Flash memory/OneNAND Flash memory

- PSRAM (4 memory banks)

- NAND Flash memory with ECC hardware to check up to 8 Kbytes of data

- Interface with synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) memories

- 8-,16-,32-bit data bus width

- Independent Chip Select control for each memory bank

- Independent configuration for each memory bank

- Write FIFO

- Read FIFO for SDRAM controller

- The maximum FMC\_CLK/FMC\_SDCLK frequency for synchronous accesses is HCLK/2

### LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

### 2.9 Quad-SPI memory interface (QUADSPI)

All the devices embed a Quad-SPI memory interface, which is a specialized communication interface targetting Single, Dual or Quad-SPI Flash memories. It can work in:

- Direct mode through registers

- External Flash status register polling mode

- Memory mapped mode.

Up to 256 Mbytes external Flash are memory mapped, supporting 8, 16 and 32-bit access. Code execution is supported.

The opcode and the frame format are fully programmable. The communication can be either in Single Data Rate or Dual Data Rate.

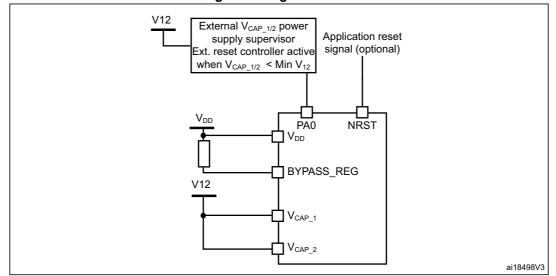

#### Figure 8. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

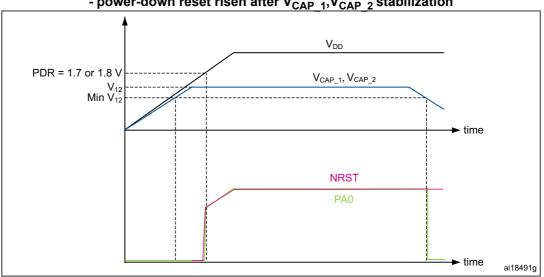

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

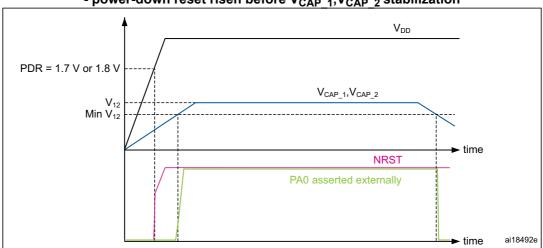

- Otherwise, if the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is slower than the time for  $V_{DD}$  to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

- *Note:* The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

Figure 9. Startup in regulator OFF: slow V<sub>DD</sub> slope - power-down reset risen after V<sub>CAP\_1</sub>, V<sub>CAP\_2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

Figure 10. Startup in regulator OFF mode: fast V<sub>DD</sub> slope - power-down reset risen before V<sub>CAP\_1</sub>, V<sub>CAP\_2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

| features <sup>(1)</sup>               | USART1/2/3/6 | UART4/5/7/8 |  |  |  |  |  |

|---------------------------------------|--------------|-------------|--|--|--|--|--|

| Smartcard mode                        | X            | -           |  |  |  |  |  |

| Single-wire half-duplex communication | X            | Х           |  |  |  |  |  |

| IrDA SIR ENDEC block                  | X            | Х           |  |  |  |  |  |

| LIN mode                              | X            | Х           |  |  |  |  |  |

| Dual clock domain                     | X            | Х           |  |  |  |  |  |

| Receiver timeout interrupt            | X            | Х           |  |  |  |  |  |

| Modbus communication                  | X            | Х           |  |  |  |  |  |

| Auto baud rate detection              | X            | х           |  |  |  |  |  |

| Driver Enable                         | X            | Х           |  |  |  |  |  |

Table 8. USART implementation (continued)

1. X: supported.

# 2.26 Serial peripheral interface (SPI)/inter- integrated sound interfaces (I2S)

The devices feature up to six SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4, SPI5, and SPI6 can communicate at up to 54 Mbits/s, SPI2 and SPI3 can communicate at up to 25 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable from 4 to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation. All the SPIs can be served by the DMA controller.

Three standard  $I^2S$  interfaces (multiplexed with SPI1, SPI2 and SPI3) are available. They can be operated in master or slave mode, in simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

## 2.27 Serial audio interface (SAI)

The devices embed two serial audio interfaces.

The serial audio interface is based on two independent audio subblocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both subblocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

DocID029041 Rev 4

|         |         |              | I       | Pin N   | umbe     | ər                      |         |                |          |                                |          |               |            |                                                                                                                     |                                            |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|         |         | TM32<br>TM32 |         |         | I        |                         |         | F768/<br>F769: |          | reset                          |          |               |            |                                                                                                                     |                                            |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes      | Alternate functions                                                                                                 | Additional<br>functions                    |

| 3       | 3       | B1           | 3       | 3       | A1       | C12                     | 3       | 3              | A1       | PE4                            | I/O      | FT            | -          | TRACED1, SPI4_NSS,<br>SAI1_FS_A,<br>DFSDM1_DATIN3,<br>FMC_A20, DCMI_D4,<br>LCD_B0, EVENTOUT                         | -                                          |

| 4       | 4       | B2           | 4       | 4       | B1       | D12                     | 4       | 4              | B1       | PE5                            | I/O      | FT            | -          | TRACED2, TIM9_CH1,<br>SPI4_MISO, SAI1_SCK_A,<br>DFSDM1_CKIN3,<br>FMC_A21, DCMI_D6,<br>LCD_G0, EVENTOUT              | -                                          |

| 5       | 5       | В3           | 5       | 5       | B2       | E11                     | 5       | 5              | B2       | PE6                            | I/O      | FT            | -          | TRACED3, TIM1_BKIN2,<br>TIM9_CH2, SPI4_MOSI,<br>SAI1_SD_A,<br>SAI2_MCLK_B, FMC_A22,<br>DCMI_D7, LCD_G1,<br>EVENTOUT | -                                          |

| -       | -       | -            | -       | -       | G6       | -                       | -       | -              | G6       | VSS                            | S        | -             | -          | -                                                                                                                   | -                                          |

| -       | -       | -            | -       | -       | F5       | -                       | -       | -              | F5       | VDD                            | S        | -             | -          | -                                                                                                                   | -                                          |

| 6       | 6       | C1           | 6       | 6       | C1       | C13                     | 6       | 6              | C1       | VBAT                           | S        | -             | -          | -                                                                                                                   | -                                          |

| -       | -       | D2           | 7       | 7       | C2       | NC                      | 7       | 7              | C2       | PI8                            | I/O      | FT            | (2)        | EVENTOUT                                                                                                            | RTC_TAMP<br>2/RTC_TS/<br>WKUP5             |

| 7       | 7       | D1           | 8       | 8       | D1       | D13                     | 8       | 8              | D1       | PC13                           | I/O      | FT            | (2)        | EVENTOUT                                                                                                            | RTC_TAMP<br>1/RTC_TS/<br>RTC_OUT/<br>WKUP4 |

| 8       | 8       | E1           | 9       | 9       | E1       | E12                     | 9       | 9              | E1       | PC14-<br>OSC32_I<br>N          | I/O      | FT            | (2)<br>(3) | EVENTOUT                                                                                                            | OSC32_IN                                   |

| 9       | 9       | F1           | 10      | 10      | F1       | E13                     | 10      | 10             | F1       | PC15-<br>OSC32_O<br>UT         | I/O      | FT            | (2)<br>(3) | EVENTOUT                                                                                                            | OSC32_OU<br>T                              |

| -       | -       | -            | -       | -       | G5       | -                       | -       | -              | G5       | VDD                            | S        | -             | -          | -                                                                                                                   | -                                          |

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

| Bus  | Boundary address          | Peripheral               |  |

|------|---------------------------|--------------------------|--|

|      | 0x4008 0000- 0x4FFF FFFF  | Reserved                 |  |

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |  |

|      | 0x4002 BC00- 0x4003 FFFF  | Reserved                 |  |

|      | 0x4002 B000 - 0x4002 BBFF | Chrom-ART (DMA2D)        |  |

|      | 0x4002 9400 - 0x4002 AFFF | Reserved                 |  |

|      | 0x4002 9000 - 0x4002 93FF |                          |  |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |  |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |  |

|      | 0x4002 8400 - 0x4002 87FF |                          |  |

|      | 0x4002 8000 - 0x4002 83FF |                          |  |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |  |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |  |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |  |

|      | 0x4002 5000 - 0X4002 5FFF | Reserved                 |  |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |  |

|      | 0x4002 3800 - 0x4002 3BFF | RCC                      |  |

|      | 0X4002 3400 - 0X4002 37FF | Reserved                 |  |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |  |

|      | 0x4002 2C00 - 0x4002 2FFF | Reserved                 |  |

|      | 0x4002 2800 - 0x4002 2BFF | GPIOK                    |  |

|      | 0x4002 2400 - 0x4002 27FF | GPIOJ                    |  |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |  |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |  |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |  |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |  |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |  |

|      | 0X4002 0C00 - 0x4002 0FFF | GPIOD                    |  |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |  |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |  |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |  |

## Table 13. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx register boundary addresses<sup>(1)</sup> (continued)

DocID029041 Rev 4

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | HDMI-CEC            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | I2C4                |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | SPDIFRX             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | CAN3                |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | LPTIM1              |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

## Table 13. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx register boundary addresses<sup>(1)</sup> (continued)

1. The gray color is used for reserved Flash memory addresses.

- 1. Guaranteed by characterization results.

- 2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

- When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Cumhal          | Deremeter                | Conditions             | £ (MIL-)                    | Turn |                        | Max <sup>(1)</sup>     |                         | Unit |  |

|-----------------|--------------------------|------------------------|-----------------------------|------|------------------------|------------------------|-------------------------|------|--|

| Symbol          | Parameter                | Conditions             | f <sub>HCLK</sub> (MHz) Тур |      | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit |  |

|                 |                          |                        | 216                         | 128  | 144 <sup>(3)</sup>     | 190 <sup>(3)</sup>     | -                       |      |  |

|                 |                          |                        | 200                         | 119  | 134                    | 180                    | 214                     |      |  |

|                 |                          | All                    | 180                         | 105  | 118 <sup>(3)</sup>     | 153 <sup>(3)</sup>     | 178 <sup>(3)</sup>      |      |  |

|                 |                          | peripherals            | 168                         | 93   | 105                    | 136                    | 156                     |      |  |

|                 |                          | enabled <sup>(2)</sup> | enabled <sup>(2)</sup>      | 144  | 72                     | 80                     | 107                     | 124  |  |

|                 |                          |                        | 60                          | 33   | 39                     | 65                     | 82                      | ]    |  |

|                 | Supply                   |                        | 25                          | 17   | 21                     | 47                     | 65                      | mA   |  |

| I <sub>DD</sub> | current in<br>Sleep mode |                        |                             | 216  | 18                     | 25 <sup>(3)</sup>      | 71 <sup>(3)</sup>       | -    |  |

|                 |                          |                        | 200                         | 17   | 24                     | 70                     | 112                     |      |  |

|                 |                          |                        | 180                         | 14   | 20 <sup>(3)</sup>      | 54 <sup>(3)</sup>      | 75 <sup>(3)</sup>       |      |  |

|                 |                          | peripherals            | 168                         | 13   | 18                     | 49                     | 69                      |      |  |

|                 |                          | disabled               | 144                         | 10   | 14                     | 40                     | 58                      |      |  |

|                 |                          |                        | 60                          | 6    | 10                     | 36                     | 53                      |      |  |

|                 |                          |                        | 25                          | 4    | 8                      | 34                     | 51                      |      |  |

Table 33. Typical and maximum current consumption in Sleep mode, regulator ON

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. Guaranteed by test in production.

| Symbol                                     | Parameter                                              | Conditions                     | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|--------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                              | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                              | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                              | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \le V_{IN} \le V_{DD}$ | -                  | -      | ±1                 | μA   |

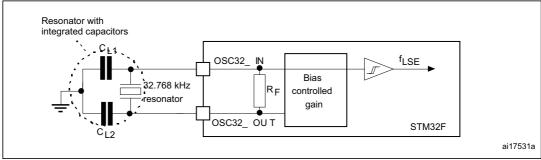

Table 42. Low-speed external user clock characteristics

1. Guaranteed by design.

| Symbol                         | Parameter                                 | Conditions                                     | Min | Тур | Max  | Unit |  |

|--------------------------------|-------------------------------------------|------------------------------------------------|-----|-----|------|------|--|

|                                |                                           | LSEDRV[1:0]=00<br>Low drive capability         | -   | -   | 0.48 |      |  |

|                                | Maximum critical crystal g <sub>m</sub> - | LSEDRV[1:0]=10<br>Medium low drive capability  | -   | -   | 0.75 | uA/V |  |

| G <sub>m</sub> _cnt_max        |                                           | LSEDRV[1:0]=01<br>Medium high drive capability | -   | -   | 1.7  | μΑνν |  |

|                                |                                           | LSEDRV[1:0]=11<br>High drive capability        | -   | -   | 2.7  |      |  |

| t <sub>SU</sub> <sup>(2)</sup> | start-up time                             | V <sub>DD</sub> is stabilized                  | -   | 2   | -    | s    |  |

| Table 44. LSE oscillator characteristics (f <sub>LSE</sub> = 32.76 | 8 kHz) <sup>(1)</sup> (continued) |

|--------------------------------------------------------------------|-----------------------------------|

|                                                                    |                                   |

1. Guaranteed by design.

Guaranteed by characterization results. t<sub>SU</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                       | Conditions                                      | Min | Тур | Мах                | Unit |

|-----------------------------------------------|-------------------------|-----------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------|------|

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 100 <sup>(4)</sup> |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 50                 |      |

|                                               | f                       | Maximum frequency <sup>(3)</sup>                                | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 42.5               | MHz  |

|                                               | f <sub>max(IO)out</sub> |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 180 <sup>(4)</sup> |      |

|                                               |                         | Output high to low level fall                                   | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 100                |      |

| 11                                            |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 72.5               |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 4                  |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 6                  | ns   |

|                                               | t <sub>f(IO)out</sub> / |                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 7                  |      |

|                                               | t <sub>r(IO)out</sub>   | time and output low to high level rise time                     | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 2.5                |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 3.5                |      |

|                                               |                         |                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 4                  |      |

| -                                             | tEXTIpw                 | Pulse width of external signals detected by the EXTI controller | -                                               | 10  | -   | -                  | ns   |

Table 67. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by design.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F76xxx and STM32F77xxx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

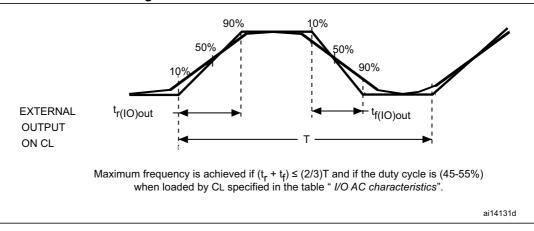

3. The maximum frequency is defined in *Figure 39*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

### Figure 39. I/O AC characteristics definition

#### **General PCB design guidelines**

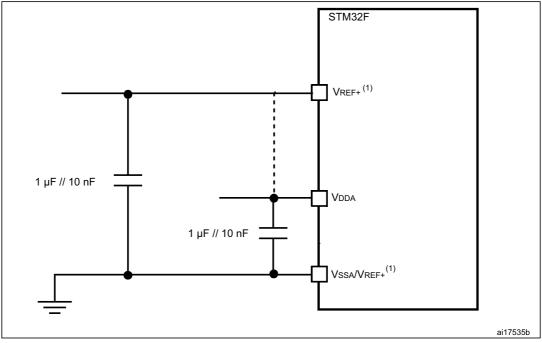

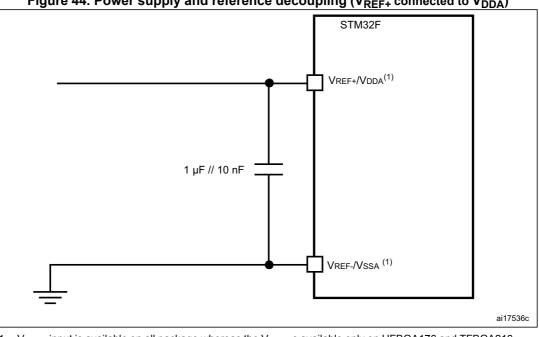

Power supply decoupling should be performed as shown in Figure 43 or Figure 44, depending on whether V<sub>REF+</sub> is connected to V<sub>DDA</sub> or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

Figure 43. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

$V_{REF+}$  input is available on all package whereas the  $V_{REF-}$  s available only on UFBGA176 and TFBGA216. When  $V_{REF-}$  is not available, it isinternally connected to  $V_{DDA}$  and  $V_{SSA}$ . 1.

Figure 44. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

$V_{REF+}$  input is available on all package whereas the  $V_{REF-}$  s available only on UFBGA176 and TFBGA216. When  $V_{REF-}$  is not available, it isinternally connected to  $V_{DDA}$  and  $V_{SSA}$ . 1.

#### **SPI** interface characteristics

Unless otherwise specified, the parameters given in *Table 85* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.20: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                    | Parameter             | Parameter Conditions Min                                            |                                                                | Тур               | Мах                   | Unit |                   |  |

|-------------------------------------------|-----------------------|---------------------------------------------------------------------|----------------------------------------------------------------|-------------------|-----------------------|------|-------------------|--|

|                                           |                       | Master mode<br>SPI1,4,5,6<br>2.7≤VDD≤3.6                            |                                                                |                   | 54 <sup>(2)</sup>     |      |                   |  |

|                                           |                       | Master mode<br>SPI1,4,5,6<br>1.71≤VDD≤3.6                           |                                                                |                   | 27                    |      |                   |  |

|                                           |                       | Master transmitter mode<br>SPI1,4,5,6<br>1.71≤VDD≤3.6               |                                                                |                   | 54                    |      |                   |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency   | Slave receiver mode<br>SPI1,4,5,6<br>1.71≤VDD≤3.6                   | SPI1,4,5,6                                                     |                   | 54                    | MHz  |                   |  |

| (3CK)                                     |                       |                                                                     | Slave mode transmitter,<br>duplex<br>SPI1,4,5,6<br>2.7≤VDD≤3.6 | SPI1,4,5,6        |                       |      | 50 <sup>(3)</sup> |  |

|                                           |                       | Slave mode transmitter/full<br>duplex<br>SPI1,4,5,6<br>1.71≤VDD≤3.6 |                                                                |                   | 37 <sup>(3)</sup>     |      |                   |  |

|                                           |                       | Master & Slave mode<br>SPI2,3<br>1.71≤VDD≤3.6                       |                                                                |                   | 27                    |      |                   |  |

| tsu(NSS)                                  | NSS setup time        | Slave mode, SPI presc = 2                                           | 4*T <sub>PLCK</sub>                                            | -                 | -                     |      |                   |  |

| th(NSS)                                   | NSS hold time         | Slave mode, SPI presc = 2                                           | 2*T <sub>PLCK</sub>                                            | -                 | -                     | ns   |                   |  |

| tw(SCKH)<br>tw(SCKL)                      | SCK high and low time | Master mode                                                         | T <sub>PLCK</sub> - 2                                          | T <sub>PLCK</sub> | T <sub>PLCK</sub> + 2 |      |                   |  |

### Table 85. SPI dynamic characteristics<sup>(1)</sup>

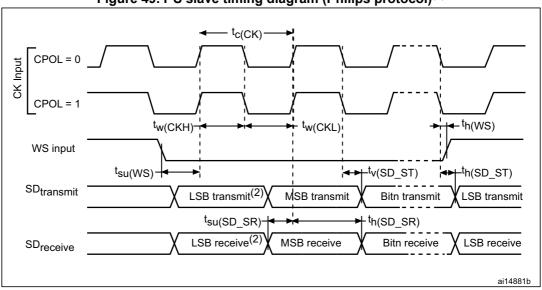

Figure 49. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

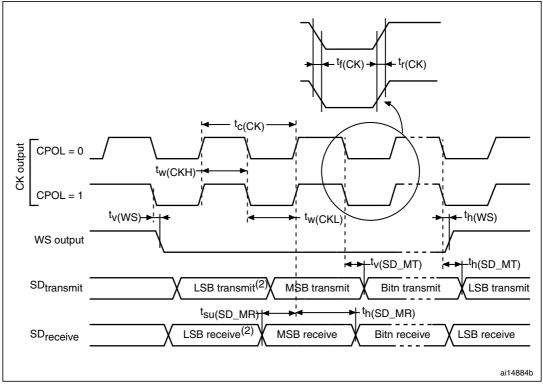

### Figure 50. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |  |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|--|--|

| Symbol | Min    | Тур         | Max    | Min    | Тур                   | Мах    |  |  |  |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |  |  |  |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |  |  |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |  |  |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |  |  |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |  |  |  |

| D      | 21.800 | 22.000      | 22.200 | 0.8583 | 0.8661                | 0.874  |  |  |  |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795 | 0.7874                | 0.7953 |  |  |  |

| D3     | -      | 17.500      | -      | -      | 0.689                 | -      |  |  |  |

| E      | 21.800 | 22.000      | 22.200 | 0.8583 | 0.8661                | 0.8740 |  |  |  |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795 | 0.7874                | 0.7953 |  |  |  |

| E3     | -      | 17.500      | -      | -      | 0.6890                | -      |  |  |  |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |  |  |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |  |  |  |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |  |  |  |

| k      | 0°     | 3.5°        | 7°     | 0°     | 3.5°                  | 7°     |  |  |  |

| CCC    | -      | -           | 0.080  | -      | -                     | 0.0031 |  |  |  |

# Table 126. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 6.7 TFBGA216, 13 x 13 x 0.8 mm thin fine-pitch ball grid array package information

Z Seating plane A2 A1 А D1 Χ A1 ball A1 ball D identifier index area F t e ÷00000000000 Α • 4 0000000000000000 G 000000000000000 000000 000000 E1 Е +00000 000000 00000 000000 0000000000000000 000000000000000 е Υ 0000000000000000 000000000000000 R 0000000000000000 15 Øb (216 balls) BOTTOM VIEW TOP VIEW A0L2\_ME\_V3

Figure 101. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

| Table 133. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array |  |

|-----------------------------------------------------------------------|--|

| package mechanical data                                               |  |

| O maked | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|---------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol  | Min         | Тур    | Max    | Min                   | Тур    | Max    |

| A       | -           | -      | 1.100  | -                     | -      | 0.0433 |

| A1      | 0.150       | -      | -      | 0.0059                | -      | -      |

| A2      | -           | 0.760  | -      | -                     | 0.0299 | -      |

| b       | 0.350       | 0.400  | 0.450  | 0.0138                | 0.0157 | 0.0177 |

| D       | 12.850      | 13.000 | 13.150 | 0.5118                | 0.5118 | 0.5177 |

| D1      | -           | 11.200 | -      | -                     | 0.4409 | -      |

| E       | 12.850      | 13.000 | 13.150 | 0.5118                | 0.5118 | 0.5177 |

| E1      | -           | 11.200 | -      | -                     | 0.4409 | -      |

| е       | -           | 0.800  | -      | -                     | 0.0315 | -      |

| F       | -           | 0.900  | -      | -                     | 0.0354 | -      |

DocID029041 Rev 4

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| G      | -           | 0.900 | -     | -                     | 0.0354 | -      |

| ddd    | -           | -     | 0.100 | -                     | -      | 0.0039 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.080 | -                     | -      | 0.0031 |

## Table 133. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid arraypackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

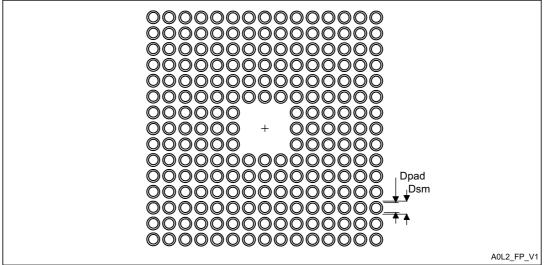

## Figure 102. TFBGA216, 13 x 13 mm, 0.8 mm pitch, thin fine-pitch ball grid array package recommended footprint

#### Table 134. TFBGA216 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.8                                                                   |

| Dpad              | 0.400 mm                                                              |

| Dsm               | 0.470 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.400 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.120 mm                                                              |

## **Revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21-Mar-2016 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 26-Apr-2016 | 2        | <ul> <li>DFSDM replaced by DFSDM1 in:</li> <li>Table 10: STM32F765xx, STM32F767xx, STM32F768Ax and<br/>STM32F769xx pin and ball definitions.</li> <li>Table 12: STM32F765xx, STM32F767xx, STM32F768Ax and<br/>STM32F769xx alternate function mapping.</li> <li>Table 13: STM32F765xx, STM32F767xx, STM32F768Ax and<br/>STM32F769xx register boundary addresses.</li> <li>Section 5.3.34: Digital filter for Sigma-Delta Modulators (DFSDM)<br/>characteristics.</li> <li>Updated Table 2: STM32F765xx, STM32F767xx, STM32F768Ax and<br/>STM32F769xx features and peripheral counts adding DFSDM1<br/>features.</li> <li>Updated Table 39: Peripheral current consumption adding DFSDM1<br/>current consumption.</li> <li>Updated cover in 2 pages.</li> <li>Update cover replacing for SPI 'up to 50 Mbit/s' by 'up to 54 Mbit/s'.</li> </ul> |

| 06-May-2016 | 3        | Updated Table 2: STM32F765xx, STM32F767xx, STM32F768Ax and<br>STM32F769xx features and peripheral counts GPIO number.<br>Updated Table 12: STM32F765xx, STM32F767xx, STM32F768Ax and<br>STM32F769xx alternate function mapping adding CAN3_RX alternate<br>function on PA8/AF11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22-Dec-2016 | 4        | Updated Table 97: Dynamics characteristics: Ethernet MAC signals for<br><i>RMII</i> .<br>Updated Table 71: ADC characteristics sampling rate.<br>Updated all the notes removing 'not tested in production'.<br>Updated Figure 46: SPI timing diagram - slave mode and CPHA = 0 and<br>Figure 47: SPI timing diagram - slave mode and CPHA = 1(1) with<br>modified NSS timing waveforms (among other changes).<br>Updated Table 121: LTDC characteristics clock output frequency at<br>65 MHz.<br>Updated Section 5.2: Absolute maximum ratings.<br>Updated Section 6: Package information adding information about other<br>optional marking or inset/upset marks.                                                                                                                                                                            |