# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                                |

| Core Processor                | ARM® Cortex®-M7                                                                                                       |

| Core Size                     | 32-Bit Single-Core                                                                                                    |

| Speed                         | 216MHz                                                                                                                |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                                          |

| Number of I/O                 | 82                                                                                                                    |

| Program Memory Size           | 1MB (1M x 8)                                                                                                          |

| Program Memory Type           | FLASH                                                                                                                 |

| EEPROM Size                   | ·                                                                                                                     |

| RAM Size                      | 512K x 8                                                                                                              |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                                           |

| Data Converters               | A/D 16x12b; D/A 2x12b                                                                                                 |

| Oscillator Type               | Internal                                                                                                              |

| Operating Temperature         | -40°C ~ 105°C (TA)                                                                                                    |

| Mounting Type                 | Surface Mount                                                                                                         |

| Package / Case                | 100-LQFP                                                                                                              |

| Supplier Device Package       | 100-LQFP (14x14)                                                                                                      |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f765vgt7                                                 |

|                               |                                                                                                                       |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16/255

DocID029041 Rev 4

# Table 2. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx features and peripheral counts

|                              |                        |             |           |                      |              |            |      |               | per         | ipne       | eral C      | ounts           |                    |             |                       |      |            |             |             |              |      |             |      |               |

|------------------------------|------------------------|-------------|-----------|----------------------|--------------|------------|------|---------------|-------------|------------|-------------|-----------------|--------------------|-------------|-----------------------|------|------------|-------------|-------------|--------------|------|-------------|------|---------------|

| Periph                       | ierals                 | STM:<br>765 | 32F<br>Vx | STM3<br>/769         | 2F767<br>9Vx | STM<br>765 |      | STM32<br>/769 | 2F767<br>Zx | STM<br>769 | 132F<br>9Ax | STM32F<br>768Ax | STN<br>76          | 132F<br>51x | STM32<br>/769         |      | STN<br>765 | 132F<br>5Bx | STM3<br>/76 | 2F767<br>9Bx |      | M32F<br>5Nx |      | 32F767<br>9Nx |

| Flash memory in              | Kbytes                 | 1024        | 2048      | 1024                 | 2048         | 1024       | 2048 | 1024          | 2048        | 1024       | 2048        | 2048            | 1024               | 2048        | 1024                  | 2048 | 1024       | 2048        | 1024        | 2048         | 1024 | 2048        | 1024 | 2048          |

|                              | System                 |             |           |                      |              |            |      |               |             |            |             | 512(36          | 8+16+1             | 28)         |                       |      |            |             |             |              |      |             | •    |               |

| SRAM in<br>Kbytes            | Instruction            |             |           |                      |              |            |      |               |             |            |             |                 | 16                 |             |                       |      |            |             |             |              |      |             |      |               |

| ,                            | Backup                 |             |           |                      |              |            |      |               |             |            |             |                 | 4                  |             |                       |      |            |             |             |              |      |             |      |               |

| FMC memory co                | ntroller               |             |           |                      |              |            |      |               |             |            |             | ١               | ′es <sup>(1)</sup> |             |                       |      |            |             |             |              |      |             |      |               |

| Quad-SPI                     |                        |             | Yes       |                      |              |            |      |               |             |            |             |                 |                    |             |                       |      |            |             |             |              |      |             |      |               |

| Ethernet                     | Yes No Yes             |             |           |                      |              |            |      |               |             |            |             |                 |                    |             |                       |      |            |             |             |              |      |             |      |               |

|                              | General-<br>purpose    |             |           | 10                   |              |            |      |               |             |            |             |                 |                    |             |                       |      |            |             |             |              |      |             |      |               |

| Timers                       | Advanced-<br>control   |             |           | 2                    |              |            |      |               |             |            |             |                 |                    |             |                       |      |            |             |             |              |      |             |      |               |

|                              | Basic                  |             |           |                      |              |            |      |               |             |            |             |                 | 2                  |             |                       |      |            |             |             |              |      |             |      |               |

|                              | Low-power              |             |           |                      |              |            |      |               |             |            |             |                 | 1                  |             |                       |      |            |             |             |              |      |             |      |               |

| Random number                | generator              |             |           |                      |              |            |      |               |             |            |             |                 | Yes                |             |                       |      |            |             |             |              |      |             |      |               |

|                              | SPI / I <sup>2</sup> S | 4           | 1/3 (sim  | plex) <sup>(2)</sup> | )            |            |      |               |             |            |             |                 |                    | 6/3 (s      | simplex) <sup>(</sup> | 2)   |            |             |             |              |      |             |      |               |

|                              | l <sup>2</sup> C       |             |           |                      |              |            |      |               |             |            |             |                 | 4                  |             |                       |      |            |             |             |              |      |             |      |               |

|                              | USART/UART             |             |           |                      |              |            |      |               |             |            |             |                 | 4/4                |             |                       |      |            |             |             |              |      |             |      |               |

|                              | USB OTG FS             |             |           |                      |              |            |      |               |             |            |             |                 | Yes                |             |                       |      |            |             |             |              |      |             |      |               |

| Communication                | USB OTG HS             |             |           |                      |              |            |      |               |             |            |             |                 | Yes                |             |                       |      |            |             |             |              |      |             |      |               |

| interfaces                   | CAN                    |             |           |                      |              |            |      |               |             |            |             |                 | 3                  |             |                       |      |            |             |             |              |      |             |      |               |

|                              | SAI                    |             |           |                      |              |            |      |               |             |            |             |                 | 2                  |             |                       |      |            |             |             |              |      |             |      |               |

|                              | SPDIFRX                |             |           |                      |              |            |      |               |             |            |             | 4               | inputs             |             |                       |      |            |             |             |              |      |             |      |               |

|                              | SDMMC1                 |             |           |                      |              |            |      |               |             |            |             |                 | Yes                |             |                       |      |            |             |             |              |      |             |      |               |

|                              | SDMMC2                 |             |           |                      |              |            |      |               |             |            |             | ١               | ′es <sup>(3)</sup> |             |                       |      |            |             |             |              |      |             |      |               |

| Camera interface             |                        | Yes         |           |                      |              |            |      |               |             |            |             |                 |                    |             |                       |      |            |             |             |              |      |             |      |               |

| MIPI-DSI Host <sup>(4)</sup> |                        |             |           |                      | No           | 0          |      |               |             |            | Yes         | 3               | N                  | lo          | Ye                    | 5    | N          | lo          | Ye          | es           |      | No          | Y    | ′es           |

| LCD-TFT                      |                        | No          | c         | Ye                   | es           | Ν          | 0    |               |             | Yes        | 6           |                 | N                  | lo          | Ye                    | 6    | N          | lo          | Ye          | es           |      | No          | Y    | ′es           |

Description

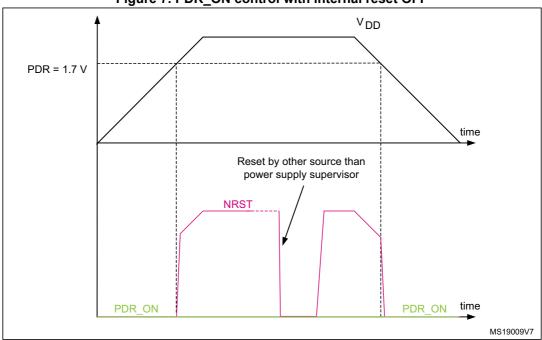

Figure 7. PDR\_ON control with internal reset OFF

# 2.19 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

# 2.19.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep modes

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode:

MR operates in normal mode (default mode of MR in stop mode)

MR operates in under-drive mode (reduced leakage mode).

# 3 Pinouts and pin description

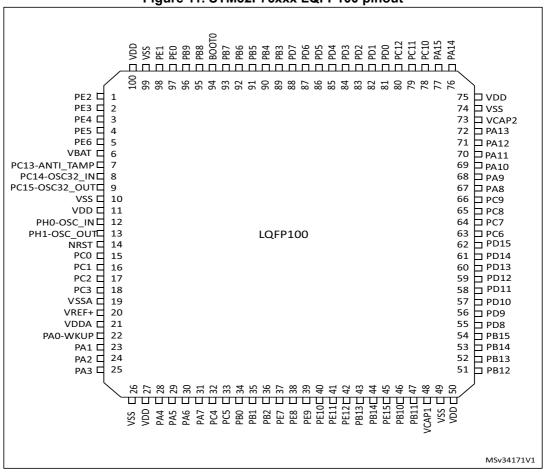

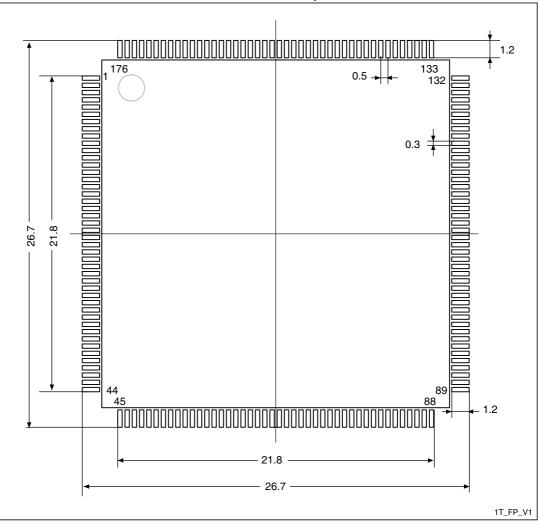

#### Figure 11. STM32F76xxx LQFP100 pinout

1. The above figure shows the package top view.

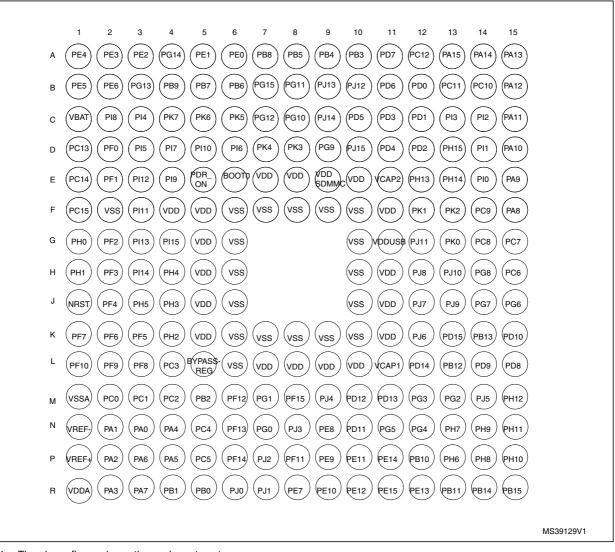

#### Figure 19. STM32F76xxx TFBGA216 ballout

1. The above figure shows the package top view.

|         |         |              | I       | Pin N   | umbe     | ər                      |         |         |          |                                |          |               | ,     |                                                                                                                    |                                                               |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|---------|----------|--------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | M32I    |         |          | reset                          |          |               |       |                                                                                                                    |                                                               |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                | Additional<br>functions                                       |

| -       | 19      | K1           | 25      | 28      | К1       | NC                      | 25      | 28      | К1       | PF7                            | I/O      | FT            | -     | TIM11_CH1, SPI5_SCK,<br>SAI1_MCLK_B,<br>UART7_TX,<br>QUADSPI_BK1_IO2,<br>EVENTOUT                                  | ADC3_IN5                                                      |

| -       | 20      | L3           | 26      | 29      | L3       | NC                      | 26      | 29      | L3       | PF8                            | I/O      | FT            | -     | SPI5_MISO, SAI1_SCK_B,<br>UART7_RTS, TIM13_CH1,<br>QUADSPI_BK1_IO0,<br>EVENTOUT                                    | ADC3_IN6                                                      |

| -       | 21      | L2           | 27      | 30      | L2       | NC                      | 27      | 30      | L2       | PF9                            | I/O      | FT            | -     | SPI5_MOSI, SAI1_FS_B,<br>UART7_CTS, TIM14_CH1,<br>QUADSPI_BK1_IO1,<br>EVENTOUT                                     | ADC3_IN7                                                      |

| -       | 22      | L1           | 28      | 31      | L1       | K11                     | 28      | 31      | L1       | PF10                           | I/O      | FT            | -     | QUADSPI_CLK,<br>DCMI_D11, LCD_DE,<br>EVENTOUT                                                                      | ADC3_IN8                                                      |

| 12      | 23      | G1           | 29      | 32      | G1       | K12                     | 29      | 32      | G1       | PH0-<br>OSC_IN                 | I/O      | FT            | (3)   | EVENTOUT                                                                                                           | OSC_IN                                                        |

| 13      | 24      | H1           | 30      | 33      | H1       | K13                     | 30      | 33      | H1       | PH1-<br>OSC_OU<br>T            | I/O      | FT            | (3)   | EVENTOUT                                                                                                           | OSC_OUT                                                       |

| 14      | 25      | J1           | 31      | 34      | J1       | L11                     | 31      | 34      | J1       | NRST                           | I/O      | RS<br>T       | -     | -                                                                                                                  | -                                                             |

| 15      | 26      | M2           | 32      | 35      | M2       | L12                     | 32      | 35      | M2       | PC0                            | I/O      | FT            | -     | DFSDM1_CKIN0,<br>DFSDM1_DATIN4,<br>SAI2_FS_B,<br>OTG_HS_ULPI_STP,<br>FMC_SDNWE, LCD_R5,<br>EVENTOUT                | ADC1_IN10,<br>ADC2_IN10,<br>ADC3_IN10                         |

| 16      | 27      | M3           | 33      | 36      | M3       | L13                     | 33      | 36      | M3       | PC1                            | I/O      | FT            | -     | TRACED0,<br>DFSDM1_DATIN0,<br>SPI2_MOSI/I2S2_SD,<br>SAI1_SD_A,<br>DFSDM1_CKIN4,<br>ETH_MDC, MDIOS_MDC,<br>EVENTOUT | ADC1_IN11,<br>ADC2_IN11,<br>ADC3_IN11,<br>RTC_TAMP<br>3/WKUP3 |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|         |         |              |         | Pin N   | umbe     | ər                      |               |         |          |                                |          |               |       |                                                                                                                                        |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         | 1        |                         | ГМ32 <br>ГМ32 |         |          | . reset                        |          |               |       |                                                                                                                                        |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                    | Additional<br>functions |

| 47      | 70      | R13          | 80      | 91      | R13      | L5                      | 80            | 91      | R13      | PB11                           | I/O      | FT            | -     | TIM2_CH4, I2C2_SDA,<br>DFSDM1_CKIN7,<br>USART3_RX,<br>OTG_HS_ULPI_D4,<br>ETH_MII_TX_EN/ETH_RM<br>II_TX_EN, DSI_TE,<br>LCD_G5, EVENTOUT | -                       |

| 48      | 71      | M10          | 81      | 92      | L11      | P5                      | 81            | 92      | L11      | VCAP_1                         | S        | -             | -     | -                                                                                                                                      | -                       |

| 49      | -       | -            | -       | 93      | К9       | N5                      | -             | 93      | К9       | VSS                            | s        | -             | -     | -                                                                                                                                      | -                       |

| 50      | 72      | N10          | 82      | 94      | L10      | P4                      | 82            | 94      | L10      | VDD                            | s        | -             | -     | -                                                                                                                                      | -                       |

| -       | -       | -            | -       | 95      | M1<br>4  | NC                      | -             | 95      | M1<br>4  | PJ5                            | 1/0      | FT            | -     | LCD_R6, EVENTOUT                                                                                                                       | -                       |

| -       | -       | M11          | 83      | 96      | P13      | NC                      | 83            | 96      | P13      | PH6                            | I/O      | FT            | -     | I2C2_SMBA, SPI5_SCK,<br>TIM12_CH1,<br>ETH_MII_RXD2,<br>FMC_SDNE1, DCMI_D8,<br>EVENTOUT                                                 | -                       |

| -       | -       | N12          | 84      | 97      | N13      | NC                      | 84            | 97      | N13      | PH7                            | I/O      | FT            | -     | I2C3_SCL, SPI5_MISO,<br>ETH_MII_RXD3,<br>FMC_SDCKE1, DCMI_D9,<br>EVENTOUT                                                              | -                       |

| -       | -       | M12          | 85      | 98      | P14      | M5                      | -             | 98      | P14      | PH8                            | I/O      | FT            | -     | I2C3_SDA, FMC_D16,<br>DCMI_HSYNC, LCD_R2,<br>EVENTOUT                                                                                  | -                       |

| -       | -       | M13          | 86      | 99      | N14      | K4                      | -             | 99      | N14      | PH9                            | I/O      | FT            | -     | I2C3_SMBA, TIM12_CH2,<br>FMC_D17, DCMI_D0,<br>LCD_R3, EVENTOUT                                                                         | -                       |

| -       | -       | L13          | 87      | 100     | P15      | L4                      | -             | 100     | P15      | PH10                           | I/O      | FT            | -     | TIM5_CH1, I2C4_SMBA,<br>FMC_D18, DCMI_D1,<br>LCD_R4, EVENTOUT                                                                          | -                       |

| -       | -       | L12          | 88      | 101     | N15      | M4                      | -             | 101     | N15      | PH11                           | I/O      | FT            | -     | TIM5_CH2, I2C4_SCL,<br>FMC_D19, DCMI_D2,<br>LCD_R5, EVENTOUT                                                                           | -                       |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

- NC (not-connected) pins are not bonded. They must be configured by software to output push-pull and forced to 0 in the output data register to avoid an extra current consumption in low-power modes. list of pins: PI8, PI12, PI13, PI14, PF6, PF7, PF8, PF9, PC2, PC3, PC4, PC5, PI15, PJ0, PJ1, PJ2, PJ3, PJ4, PJ5, PH6, PH7, PJ12, PJ13, PJ14, PJ15, PG14, PK3, PK4, PK5, PK6 and PK7.

- PC13, PC14, PC15 and Pl8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and Pl8 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF. - These I/Os must not be used as a current source (e.g. to drive an LED).

- 3. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- 4. If the device is in regulator OFF/internal reset ON mode (BYPASS\_REG pin is set to VDD), then PA0 is used as an internal reset (active low).

- 5. Internally connected to VDD or VSS depending on part number.

Pinouts and pin description

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

|        |      |               | Т                         | able 12.     | STM32F                                     | 765xx, \$                     |                                                        |                                                                |                                                                                | 768Ax a<br>ntinued                                            |                                                    | 32F769x                                                                | x alterna                                | ate                                            |                  |        |              |

|--------|------|---------------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|------------------|--------|--------------|

|        |      | AF0           | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                                     | AF12                                           | AF13             | AF14   | AF15         |

| Po     | ort  | SYS           | I2C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH             | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD    | SYS          |

|        | PB7  | -             | -                         | TIM4_C<br>H2 | -                                          | I2C1_SD<br>A                  | -                                                      | DFSDM1<br>_CKIN5                                               | USART1<br>_RX                                                                  | -                                                             | -                                                  | -                                                                      | I2S4_SD<br>A                             | FMC_NL                                         | DCMI_V<br>SYNC   | -      | EVEN<br>TOUT |

|        | PB8  | -             | I2C4_SC<br>L              | TIM4_C<br>H3 | TIM10_C<br>H1                              | I2C1_SC<br>L                  | -                                                      | DFSDM1<br>_CKIN7                                               | UART5_<br>RX                                                                   | -                                                             | CAN1_R<br>X                                        | SDMMC2<br>_D4                                                          | ETH_MII_<br>TXD3                         | SDMMC<br>_D4                                   | DCMI_D<br>6      | LCD_B6 | EVEN<br>TOUT |

|        | PB9  | -             | I2S4_SD<br>A              | TIM4_C<br>H4 | TIM11_CH<br>1                              | I2C1_SD<br>A                  | SPI2_NS<br>S/I2S2_<br>WS                               | DFSDM1<br>_DATIN7                                              | UART5_T<br>X                                                                   | -                                                             | CAN1_T<br>X                                        | SDMMC2<br>_D5                                                          | I2C4_SM<br>BA                            | SDMMC<br>_D5                                   | DCMI_D<br>7      | LCD_B7 | EVEN<br>TOUT |

|        | PB10 | -             | TIM2_C<br>H3              | -            | -                                          | I2C2_SC<br>L                  | SPI2_SC<br>K/I2S2_<br>CK                               | DFSDM1<br>_DATIN7                                              | USART3<br>_TX                                                                  | -                                                             | QUADSP<br>I_BK1_N<br>CS                            | OTG_HS_<br>ULPI_D3                                                     | ETH_MII_<br>RX_ER                        | -                                              | -                | LCD_G4 | EVEN<br>TOUT |

| Port B | PB11 | -             | TIM2_C<br>H4              | -            | -                                          | I2C2_SD<br>A                  | -                                                      | DFSDM1<br>_CKIN7                                               | USART3<br>_RX                                                                  | -                                                             | -                                                  | OTG_HS_<br>ULPI_D4                                                     | ETH_MII_<br>TX_EN/E<br>TH_RMII_<br>TX_EN | -                                              | DSI_TE           | LCD_G5 | EVEN<br>TOUT |

|        | PB12 | -             | TIM1_B<br>KIN             | -            | -                                          | I2C2_SM<br>BA                 | SPI2_NS<br>S/I2S2_<br>WS                               | DFSDM1<br>_DATIN1                                              | USART3<br>_CK                                                                  | UART5_<br>RX                                                  | CAN2_R<br>X                                        | OTG_HS_<br>ULPI_D5                                                     | ETH_MII_<br>TXD0/ET<br>H_RMII_T<br>XD0   | OTG_HS<br>_ID                                  | -                | -      | EVEN<br>TOUT |

|        | PB13 | -             | TIM1_C<br>H1N             | -            | -                                          | -                             | SPI2_SC<br>K/I2S2_<br>CK                               | DFSDM1<br>_CKIN1                                               | USART3<br>_CTS                                                                 | UART5_T<br>X                                                  | CAN2_T<br>X                                        | OTG_HS_<br>ULPI_D6                                                     | ETH_MII_<br>TXD1/ET<br>H_RMII_T<br>XD1   | -                                              | -                | -      | EVEN<br>TOUT |

|        | PB14 | -             | TIM1_C<br>H2N             | -            | TIM8_CH<br>2N                              | USART1_<br>TX                 | SPI2_MI<br>SO                                          | DFSDM1<br>_DATIN2                                              | USART3<br>_RTS                                                                 | UART4_<br>RTS                                                 | TIM12_C<br>H1                                      | SDMMC2<br>_D0                                                          | -                                        | OTG_HS<br>_DM                                  | -                | -      | EVEN<br>TOUT |

|        | PB15 | RTC_RE<br>FIN | TIM1_C<br>H3N             | -            | TIM8_CH<br>3N                              | USART1_<br>RX                 | SPI2_M<br>OSI/I2S2<br>_SD                              | DFSDM1<br>_CKIN2                                               | -                                                                              | UART4_<br>CTS                                                 | TIM12_C<br>H2                                      | SDMMC2<br>_D1                                                          | -                                        | OTG_HS<br>_DP                                  | -                | -      | EVEN<br>TOUT |

94/255

DocID029041 Rev 4

3

| Bus  | Boundary address          | Peripheral         |

|------|---------------------------|--------------------|

|      | 0x4001 7C00 - 0x4001 FFFF | Reserved           |

|      | 0x4001 7800 - 0x4001 7BFF | MDIOS              |

|      | 0x4001 7400 - 0x4001 77FF | DFSDM1             |

|      | 0x4001 6C00 - 0x4001 73FF | DSI Host           |

|      | 0x4001 6800 - 0x4001 6BFF | LCD-TFT            |

|      | 0x4001 6000 - 0x4001 67FF | Reserved           |

|      | 0x4001 5C00 - 0x4001 5FFF | SAI2               |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1               |

|      | 0x4001 5400 - 0x4001 57FF | SPI6               |

|      | 0x4001 5000 - 0x4001 53FF | SPI5               |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved           |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11              |

|      | 0x4001 4400 - 0x4001 47FF | TIM10              |

|      | 0x4001 4000 - 0x4001 43FF | TIM9               |

| APB2 | 0x4001 3C00 - 0x4001 3FFF | EXTI               |

|      | 0x4001 3800 - 0x4001 3BFF | SYSCFG             |

|      | 0x4001 3400 - 0x4001 37FF | SPI4               |

|      | 0x4001 3000 - 0x4001 33FF | SPI1/I2S1          |

|      | 0x4001 2C00 - 0x4001 2FFF | SDMMC1             |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved           |

|      | 0x4001 2000 - 0x4001 23FF | ADC1 - ADC2 - ADC3 |

|      | 0x4001 1C00 - 0x4001 1FFF | SDMMC2             |

|      | 0x4001 1800 - 0x4001 1BFF | Reserved           |

|      | 0x4001 1400 - 0x4001 17FF | USART6             |

|      | 0x4001 1000 - 0x4001 13FF | USART1             |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved           |

|      | 0x4001 0400 - 0x4001 07FF | TIM8               |

|      | 0x4001 0000 - 0x4001 03FF | TIM1               |

# Table 13. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx register boundary addresses<sup>(1)</sup> (continued)

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

### Table 19. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

When bypassing the voltage regulator, the two 2.2 μF V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

## 5.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

#### Table 20. Operating conditions at power-up / power-down (regulator ON)

| Symbol           | Parameter                      | Min | Мах | Unit |

|------------------|--------------------------------|-----|-----|------|

| 1 1              | V <sub>DD</sub> rise time rate | 20  | ∞   | µs/V |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate | 20  | 8   | μ5/ν |

# 5.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for T<sub>A</sub>.

### Table 21. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| +                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ∞   |      |

|                   | V <sub>DD</sub> fall time rate               | Power-down | 20  | ∞   |      |

| +                 | $V_{CAP_1}$ and $V_{CAP_2}$ rise time rate   | Power-up   | 20  | ∞   | µs/V |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ∞   |      |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when  $V_{\text{DD}}$  reach below 1.08 V.

# 5.3.5 Reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

|        |                               |                                |                              | Tra         |             |             |             | Ма          | x <sup>(1)</sup> |             |             |             |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|--------|-------------------------------|--------------------------------|------------------------------|-------------|-------------|-------------|-------------|-------------|------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----|-----|----|----|----|----|----|----|----|---|--|

| Symbol | Parameter                     | Conditions                     | , f <sub>HCLK</sub><br>(MHz) |             |             | TA= 2       | 25 °C       | TA= 8       | 85 °C            | TA= 105 °C  |             | Unit        |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        |                               |                                |                              | IDD12       | IDD         | IDD12       | IDD         | IDD12       | IDD              | IDD12       | IDD         |             |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        |                               |                                | 180                          | 102         | 1           | 114         | 2           | 148         | 2                | 168         | 2           |             |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        | All                           | 168                            | 91                           | 1           | 101         | 2           | 132         | 2           | 152              | 2           |             |             |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        | Peripherals                   | 144                            | 71                           | 1           | 78          | 2           | 105         | 2           | 122              | 2           |             |             |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        | Supply                        | Enabled <sup>(2)</sup>         | Enabled                      | 60          | 32          | 1           | 37          | 2           | 64               | 2           | 81          | 2           |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

| IDD12/ | current in<br>RUN mode        |                                | 25                           | 16          | 1           | 20          | 2           | 46          | 2                | 64          | 2           | mA          |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

| IDD    | from V12                      |                                | 180                          | 13          | 1           | 18          | 2           | 53          | 2                | 73          | 2           |             |             |             |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        | and V <sub>DD</sub><br>supply | All<br>Peripherals<br>Disabled | Peripherals                  | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | All Peripherals  | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | Peripherals | AII | 168 | 12 | 1  | 16 | 2  | 47 | 2  | 67 | 2 |  |

|        | Peripherals                   |                                |                              |             |             |             |             |             |                  |             |             |             |             |             |             |             |             |             |             |             | 144 | 9   | 1  | 13 | 2  | 39 | 2  | 56 | 2  |   |  |

|        |                               |                                |                              |             |             |             |             |             |                  | 60          | 5           | 1           | 9           | 2           | 35          | 2           | 52          | 2           |             |             |     |     |    |    |    |    |    |    |    |   |  |

|        |                               |                                |                              |             |             | 25          | 3           | 1           | 7                | 2           | 33          | 2           | 50          | 2           |             |             |             |             |             |             |     |     |    |    |    |    |    |    |    |   |  |

Table 34. Typical and maximum current consumption in Sleep mode, regulator OFF

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

|                              |                                                   |                                                                                                          | Тур                       |                           | Max <sup>(1)</sup>        |                            |      |

|------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol                       | Parameter                                         | Conditions                                                                                               | ιyp                       | v                         | <sub>DD</sub> = 3.6       | v                          | Unit |

|                              |                                                   |                                                                                                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C |      |

|                              | Supply current in Stop mode, main regulator in    | Flash memory in Stop mode,<br>all oscillators OFF, no IWDG                                               | 0.55                      | 3                         | 18                        | 27                         |      |

|                              | Run mode                                          | Flash memory in Deep power<br>down mode, all oscillators OFF                                             | 0.5                       | 3                         | 18                        | 27                         |      |

| IDD_STOP_NM<br>(normal mode) | Supply current in Stop                            | Flash memory in Stop mode, all<br>oscillators OFF, no IWDG                                               | 0.42                      | 2.5                       | 15                        | 24                         |      |

|                              | mode, main regulator in<br>Low-power mode         | Flash memory in Deep power<br>down mode, all oscillators OFF, no<br>IWDG                                 | 0.37                      | 2.5                       | 15                        | 24                         | mA   |

| I <sub>DD_STOP_UDM</sub>     | Supply current in Stop<br>mode, main regulator in | Regulator in Run mode, Flash<br>memory in Deep power down<br>mode, all oscillators OFF, no<br>IWDG       | 0.18                      | 1.2                       | 6                         | 10                         |      |

| (under-drive<br>mode)        | Low voltage and under-<br>drive modes             | Regulator in Low-power mode,<br>Flash memory in Deep power<br>down mode, all oscillators OFF, no<br>IWDG | 0.13                      | 1.1                       | 6                         | 10                         |      |

## Table 35. Typical and maximum current consumptions in Stop mode

1. Data based on characterization, tested in production.

- 1. Guaranteed by characterization results.

- 2. Cycling performed over the whole temperature range.

# 5.3.17 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 60*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> =<br>216 MHz, conforms to IEC 61000-<br>4-2 | 2B              |

| V <sub>FTB</sub>  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> =+25 °C, f <sub>HCLK</sub> =<br>168 MHz, conforms to IEC 61000-<br>4-2  | 5A              |

#### Table 60. EMS characteristics

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

# 5.3.25 Temperature sensor characteristics

| Symbol                             | Parameter                                                      | Min | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  | -   | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 | -   | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -   | μs    |

| Table 77. Temperature sensor characteristics |

|----------------------------------------------|

|----------------------------------------------|

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Table 78. Temperature sensor calibration values |                                                                      |                           |  |  |

|-------------------------------------------------|----------------------------------------------------------------------|---------------------------|--|--|

| Symbol                                          | Parameter                                                            | Memory address            |  |  |

| TS_CAL1                                         | TS ADC raw data acquired at temperature of 30 °C, $V_{DDA}$ = 3.3 V  | 0x1FF0 F44C - 0x1FF0 F44D |  |  |

| TS_CAL2                                         | TS ADC raw data acquired at temperature of 110 °C, $V_{DDA}$ = 3.3 V | 0x1FF0 F44E - 0x1FF0 F44F |  |  |

# 5.3.26 V<sub>BAT</sub> monitoring characteristics

### Table 79. V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            | Min | Тур | Мах | Unit |

|---------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -   | 4   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                           | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy | 5   | -   | -   | μs   |

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

# 5.3.27 Reference voltage

The parameters given in *Table 80* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Table 80. | internal | reference | voltage |

|-----------|----------|-----------|---------|

|-----------|----------|-----------|---------|

| Symbol                                | Parameter                                                     | Conditions                        | Min  | Тур  | Мах  | Unit |

|---------------------------------------|---------------------------------------------------------------|-----------------------------------|------|------|------|------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V    |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage | -                                 | 10   | -    | -    | μs   |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range  | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV   |

DocID029041 Rev 4

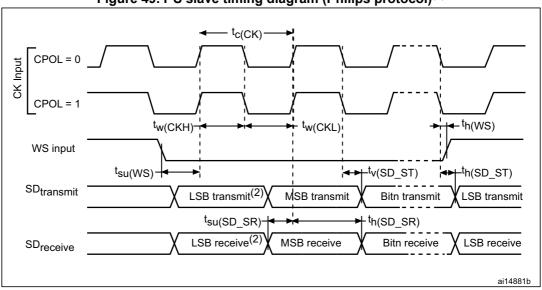

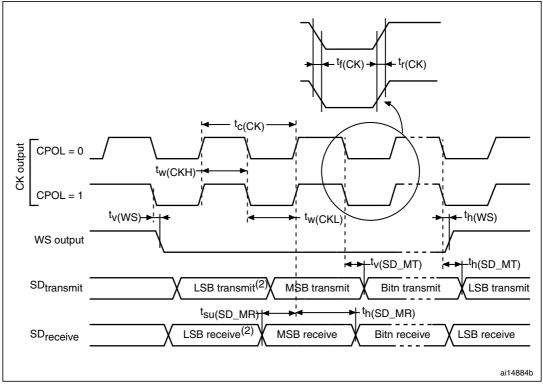

Figure 49. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

## Figure 50. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol                                         | Parameter                                              | Conditions                                              | Min | Max | Unit |

|------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|-----|-----|------|

| t <sub>v(SD_B_ST)</sub> Data output valid time |                                                        | Slave transmitter (after enable edge)<br>2.7≤VDD≤3.6V   | -   | 12  |      |

| t <sub>v(SD_B_ST)</sub> Data output valid time | Slave transmitter (after enable edge)<br>1.71≤VDD≤3.6V | -                                                       | 20  |     |      |

| t <sub>h(SD_B_MT)</sub>                        | Data output hold time                                  | Slave transmitter (after enable edge)                   | 5   | -   | 20   |

| +                                              | Data output valid time                                 | Master transmitter (after enable edge)<br>2.7≤VDD≤3.6V  | -   | 15  | ns   |

| t <sub>v(SD_MT)_A</sub> Dat                    |                                                        | Master transmitter (after enable edge)<br>1.71≤VDD≤3.6V | -   | 20  |      |

| t <sub>h(SD_A_MT)</sub>                        | Data output hold time                                  | Master transmitter (after enable edge)                  | 5   | -   |      |

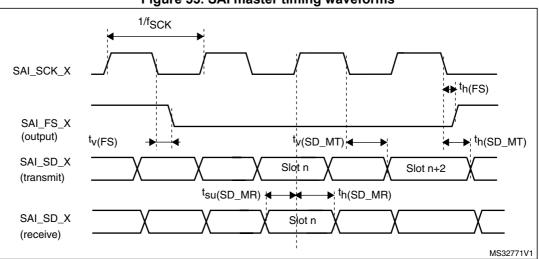

# Table 89. SAI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. APB clock frequency must be at least twice SAI clock frequency.

3. With F<sub>S</sub>=192kHz.

| Symbol          | Parameter                                                 | Conditions                           | Min.<br>(1) | Тур. | Max.<br>(1) | Unit |

|-----------------|-----------------------------------------------------------|--------------------------------------|-------------|------|-------------|------|

| R <sub>PD</sub> | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | <u> </u>                             | 17          | 21   | 24          |      |

|                 | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>DD</sub>    | 2.4         | 5.2  | 8           | kΩ   |

|                 | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | P, V <sub>IN</sub> = V <sub>SS</sub> | 1.5         | 1.8  | 2.1         |      |

| R <sub>PU</sub> | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>    | 0.55        | 0.95 | 1.35        |      |

Table 91. USB OTG full speed DC electrical characteristics (continued)

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DDUSB</sub> voltage range.

3. Guaranteed by design.

4. R<sub>L</sub> is the load connected on the USB OTG full speed drivers.

Note:

When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200 µA current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

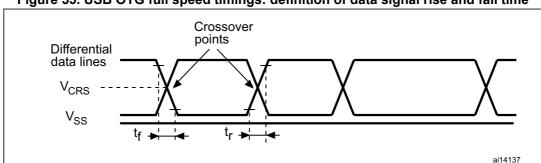

Figure 55. USB OTG full speed timings: definition of data signal rise and fall time

| Table 92 | USB OTG fu | ll sneed electrica | I characteristics <sup>(1)</sup> |

|----------|------------|--------------------|----------------------------------|

|          | 00001010   | II SPEEU EIELIILA  |                                  |

| Driver characteristics |                                        |                                |     |     |      |  |  |

|------------------------|----------------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol                 | Parameter                              | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub>       | Rise/ fall time matching               | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub>       | Output signal crossover voltage        | -                              | 1.3 | 2.0 | V    |  |  |

| Z <sub>DRV</sub>       | Output driver impedance <sup>(3)</sup> | Driving high or<br>low         | 28  | 44  | Ω    |  |  |

DocID029041 Rev 4

Refer to *Section 5.3.20: I/O port characteristics* for more details on the input/output characteristics.

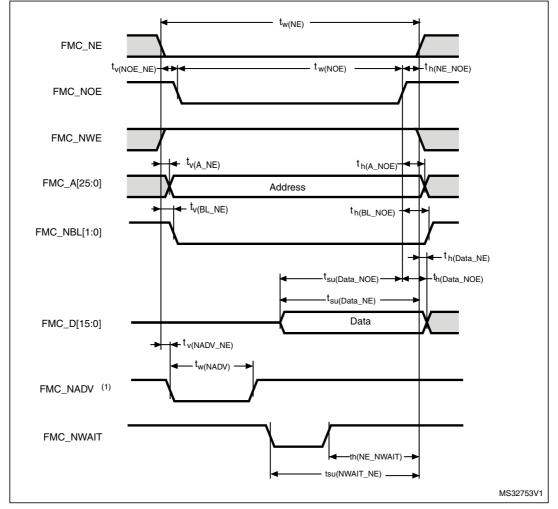

#### Asynchronous waveforms and timings

*Figure 61* through *Figure 64* represent asynchronous waveforms and *Table 100* through *Table 107* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- Capcitive load CL = 30 pF

In all timing tables, the T<sub>HCLK</sub> is the HCLK clock period

#### Figure 61. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

| Symbol                                         | Parameter                                             | Conditions                                                                                                                | Min                                     | Тур                  | Мах                                     | Unit |

|------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|-----------------------------------------|------|

| <sup>t</sup> wh(CKIN)<br><sup>t</sup> wl(CKIN) | Input clock high<br>and low time                      | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | TCKIN/2 - 0.5                           | T <sub>CKIN</sub> /2 | -                                       |      |

| t <sub>su</sub>                                | Data input setup<br>time                              | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | 2                                       | -                    | -                                       |      |

| t <sub>h</sub>                                 | Data input hold<br>time                               | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | 3                                       | -                    | -                                       | ns   |

| T <sub>Manchester</sub>                        | Manchester data<br>period (recovered<br>clock period) | Manchester mode<br>(SITP[1:0]=2,3),<br>Internal clock mode<br>(SPICKSEL[1:0] $\neq$ 0),<br>1.71 < V <sub>DD</sub> < 3.6 V | (CKOUTDIV+1)<br>* T <sub>DFSDMCLK</sub> | -                    | (2*CKOUTDIV)<br>* T <sub>DFSDMCLK</sub> |      |

| Table 122. DFSDM measu | red timing 1.71-3.6V (continued | d) |

|------------------------|---------------------------------|----|

|                        |                                 |    |

Figure 90. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

# 7 Ordering information

## Table 136. Ordering information scheme Example: STM32 76x V GΤ F 6 ххх **Device family** STM32 = ARM-based 32-bit microcontroller Product type F = general-purpose **Device subfamily** 765= STM32F765xx, USB OTG FS/HS, camera interface, Ethernet 767= STM32F767xx, USB OTG FS/HS, camera interface, Ethernet, LCD-TFT 768 = STM32F768Ax, USB OTG FS/HS, camera interface, DSI host, WLCSP with internal regulator OFF 769= STM32F769xx, USB OTG FS/HS, camera interface, Ethernet, DSI host Pin count V = 100 pins Z = 144 pins I = 176 pins A = 180 pins B = 208 pins N = 216 pins Flash memory size G = 1024 Kbytes of Flash memory I = 2048 Kbytes of Flash memory Package T = LQFP K = UFBGA H = TFBGA Y = WLCSP **Temperature range** 6 = Industrial temperature range, -40 to 85 °C. 7 = Industrial temperature range, -40 to 105 °C. Options

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.