# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                             |

| Number of I/O                 | 114                                                                                                      |

| Program Memory Size           | 1MB (1M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | ·                                                                                                        |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 105°C (TA)                                                                                       |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 144-LQFP                                                                                                 |

| Supplier Device Package       | 144-LQFP (20x20)                                                                                         |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f765zgt7                                    |

|                               |                                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Description

The STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M7 32-bit RISC core operating at up to 216 MHz frequency. The Cortex<sup>®</sup>-M7 core features a floating point unit (FPU) which supports ARM<sup>®</sup> double-precision and single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances the application security.

The STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx devices incorporate high-speed embedded memories with a Flash memory up to 2 Mbytes, 512 Kbytes of SRAM (including 128 Kbytes of Data TCM RAM for critical real-time data), 16 Kbytes of instruction TCM RAM (for critical real-time routines), 4 Kbytes of backup SRAM available in the lowest power modes, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses, a 32-bit multi-AHB bus matrix and a multi layer AXI interconnect supporting internal and external memories access.

All the devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve generalpurpose 16-bit timers including two PWM timers for motor control, two general-purpose 32bit timers, a true random number generator (RNG). They also feature standard and advanced communication interfaces.

- Up to four I<sup>2</sup>Cs

- Six SPIs, three I<sup>2</sup>Ss in half-duplex mode. To achieve audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus four UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI)

- Three CANs

- Two SAI serial audio interfaces

- Two SDMMC host interfaces

- Ethernet and camera interfaces

- LCD-TFT display controller

- Chrom-ART Accelerator™

- SPDIFRX interface

- HDMI-CEC

Advanced peripherals include two SDMMC interfaces, a flexible memory control (FMC) interface, a Quad-SPI Flash memory interface, a camera interface for CMOS sensors. Refer to *Table 2: STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx features and peripheral counts* for the list of peripherals available on each part number.

The STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx devices operate in the –40 to +105 °C temperature range from a 1.7 to 3.6 V power supply. Dedicated supply inputs for USB (OTG\_FS and OTG\_HS) and SDMMC2 (clock, command and 4-bit data) are available on all the packages except LQFP100 for a greater power supply choice.

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 2.18.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

DocID029041 Rev 4

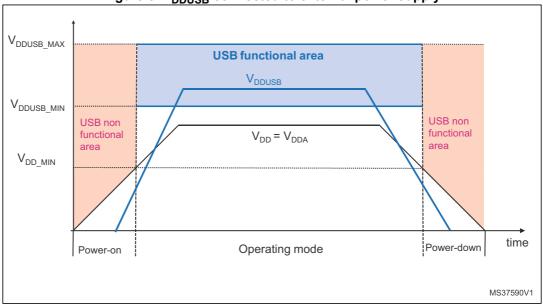

Figure 5. V<sub>DDUSB</sub> connected to external power supply

The DSI (Display Serial Interface) sub-system uses several power supply pins which are independent from the other supply pins:

- V<sub>DDDSI</sub> is an independent DSI power supply dedicated for DSI Regulator and MIPI D-PHY. This supply must be connected to global V<sub>DD</sub>.

- The V<sub>CAPDSI</sub> pin is the output of DSI Regulator (1.2V) which must be connected externally to V<sub>DD12DSI</sub>.

- The V<sub>DD12DSI</sub> pin is used to supply the MIPI D-PHY, and to supply the clock and data lanes pins. An external capacitor of 2.2 uF must be connected on the V<sub>DD12DSI</sub> pin.

- The V<sub>SSDSI</sub> pin is an isolated supply ground used for DSI sub-system.

- If the DSI functionality is not used at all, then:

- The  $V_{DDDSI}$  pin must be connected to global  $V_{DD}$ .

- The V<sub>CAPDSI</sub> pin must be connected externally to V<sub>DD12DSI</sub> but the external capacitor is no more needed.

- The V<sub>SSDSI</sub> pin must be grounded.

## 2.18 Power supply supervisor

### 2.18.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through

- Software configurable to OTG1.3 and OTG2.0 modes of operation

- USB 2.0 LPM (Link Power Management) support

- Battery Charging Specification Revision 1.2 support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 2.36 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The devices embed a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI-CEC controller to wakeup the MCU from Stop mode on data reception.

# 2.37 Digital camera interface (DCMI)

The devices embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbytes/s in 8-bit mode at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

- Refreshed by software

- DMA capability to read the final conversion data

- Interrupts: end of conversion, overrun, analog watchdog, short circuit, input serial channel clock absence

- "regular" or "injected" conversions:

- "regular" conversions can be requested at any time or even in continuous mode without having any impact on the timing of "injected" conversions

- "injected" conversions for precise timing and with high conversion priority

# 2.43 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with the temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as V<sub>BAT</sub>, ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and V<sub>BAT</sub> conversion are enabled at the same time, only V<sub>BAT</sub> conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

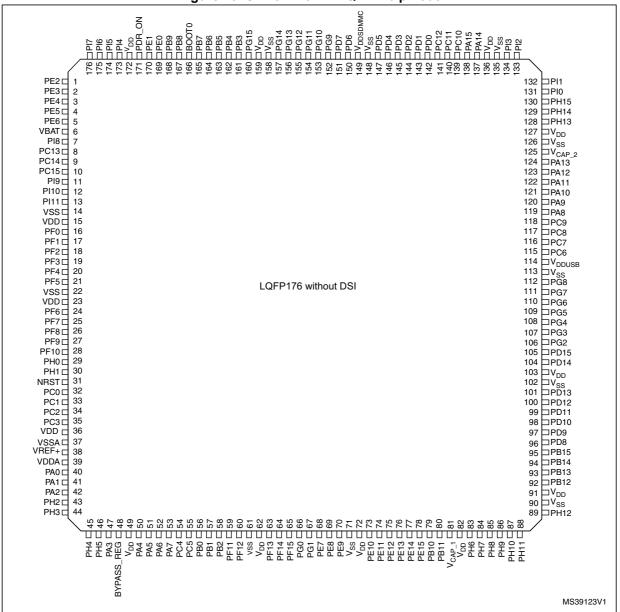

### Figure 13. STM32F76xxx LQFP176 pinout

1. The above figure shows the package top view.

| STM32F765xx         STM32F768xx         STM32F768xx         stm32F769xx         stm32F769xx |         |         |          | I       | Pin N   | umb      | er                      |         |         |          |                          |          |               |       |                     |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|----------|---------|---------|----------|-------------------------|---------|---------|----------|--------------------------|----------|---------------|-------|---------------------|---|

| -       -       F6       -       -       -       -       VSS       S       -       -       -       -         -       -       F7       -       -       -       -       VSS       S       -       -       -       -         -       -       F8       -       -       -       -       VSS       S       -       -       -       -         -       F8       -       -       -       -       VSS       S       -       -       -       -         -       F9       -       -       -       -       VSS       S       -       -       -       -         -       F10       -       -       -       -       VSS       S       -       -       -       -         -       G6       -       -       -       -       VSS       S       -       -       -       -         -       G8       -       -       -       -       VSS       S       -       -       -       -         -       H6       -       -       -       -       VSS       S       - <td< th=""><th></th><th></th><th></th><th></th><th></th><th>1</th><th></th><th></th><th></th><th></th><th>. reset</th><th></th><th></th><th></th><th></th><th></th></td<>                                                                                                                                                                                                                                                                                                                                 |         |         |          |         |         | 1        |                         |         |         |          | . reset                  |          |               |       |                     |   |

| -         F7         -         -         -         -         VSS         S         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                        | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208 | TFBGA216 | Pin name (function after | Pin type | I/O structure | Notes | Alternate functions |   |

| -       -       F8       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>-</td> <td>-</td> <td>F6</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>VSS</td> <td>s</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                         | -       | -       | F6       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       F9       -       -       -       -       VSS       S       -       -       -       -       -         -       F10       -       -       -       -       VSS       S       -       -       -       -       -         -       G6       -       -       -       -       VSS       S       -       -       -       -         -       G6       -       -       -       -       VSS       S       -       -       -       -         -       G7       -       -       -       -       VSS       S       -       -       -       -       -         -       G8       -       -       -       -       VSS       S       -       -       -       -         -       G9       -       -       -       -       VSS       S       -       -       -       -         -       H6       -       -       -       -       VSS       S       -       -       -       -         -       H8       -       -       -       -       VSS       S       - <td< td=""><td>-</td><td>-</td><td>F7</td><td>-</td><td>-</td><td>-</td><td>-</td><td>-</td><td>-</td><td>-</td><td>VSS</td><td>s</td><td>-</td><td>-</td><td>-</td><td>-</td></td<>                                                                                                                                                                                                                                                                                                                      | -       | -       | F7       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       F10       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <td>-</td> <td>-</td> <td>F8</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>VSS</td> <td>s</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                        | -       | -       | F8       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     G6     -     -     -     -     -     VSS     S     -     -     -     -       -     G7     -     -     -     -     -     VSS     S     -     -     -     -       -     G8     -     -     -     -     -     VSS     S     -     -     -     -       -     G8     -     -     -     -     -     VSS     S     -     -     -       -     G9     -     -     -     -     -     VSS     S     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -       -     H6     -     -     -     -     -     VSS     S     -     -     -       -     H7     -     -     -     -     -     VSS     S     -     -     -       -     H8     -     -     -     -     VSS     S     -     -     -       -     H10     -     -     -     -     VSS     S     -     -     -       -     J8     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -       | -       | F9       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     G7     -     -     -     -     -     VSS     S     -     -     -     -       -     G8     -     -     -     -     -     VSS     S     -     -     -     -       -     G9     -     -     -     -     -     VSS     S     -     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -     -       -     H6     -     -     -     -     -     VSS     S     -     -     -       -     H7     -     -     -     -     -     VSS     S     -     -     -       -     H8     -     -     -     -     VSS     S     -     -     -       -     H10     -     -     -     -     VSS     S     -     -     -       -     J6     -     -     -     -     VSS     S     -     -     -       -     J                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -       | -       | F10      | -       | -       | -        | -                       | -       | -       | -        | VSS                      | S        | -             | -     | -                   | - |

| -     G8     -     -     -     -     -     VSS     S     -     -     -     -       -     G9     -     -     -     -     -     VSS     S     -     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -     -       -     H6     -     -     -     -     -     VSS     S     -     -     -     -       -     H6     -     -     -     -     -     VSS     S     -     -     -     -       -     H7     -     -     -     -     -     VSS     S     -     -     -     -       -     H8     -     -     -     -     -     VSS     S     -     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -       -     J6     -     -     -     -     -     VSS     S<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       | -       | G6       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     G9     -     -     -     -     -     VSS     S     -     -     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -     -       -     G10     -     -     -     -     -     VSS     S     -     -     -     -       -     H6     -     -     -     -     -     VSS     S     -     -     -     -       -     H6     -     -     -     -     -     VSS     S     -     -     -       -     H7     -     -     -     -     -     VSS     S     -     -     -       -     H8     -     -     -     -     -     VSS     S     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -       -     H10     -     -     -     -     -     VSS     S     -     -       -     J8     -     -     -     -     VSS     S     -     -     -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -       | -       | G7       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       G10       -       -       -       -       -       VSS       S       -       -       -       -       -         -       H6       -       -       -       -       -       VSS       S       -       -       -       -       -         -       H7       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -       | -       | G8       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     H6     -     -     -     -     -     -     VSS     S     -     -     -     -       -     H7     -     -     -     -     -     VSS     S     -     -     -     -       -     H7     -     -     -     -     -     VSS     S     -     -     -     -       -     H8     -     -     -     -     -     VSS     S     -     -     -     -       -     H8     -     -     -     -     -     VSS     S     -     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -     -       -     H10     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -       -     J7     -     -     -     -     -     VSS </td <td>-</td> <td>-</td> <td>G9</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>VSS</td> <td>s</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                              | -       | -       | G9       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     H7     -     -     -     -     -     VSS     S     -     -     -     -     -       -     H8     -     -     -     -     -     -     VSS     S     -     -     -     -       -     H8     -     -     -     -     -     VSS     S     -     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -     -       -     H10     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J7     -     -     -     -     -     VSS     S     -     -     -       -     J8     -     -     -     -     - <td>-</td> <td>-</td> <td>G10</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>VSS</td> <td>s</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       | -       | G10      | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     H8     -     -     -     -     -     VSS     S     -     -     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -     -       -     H9     -     -     -     -     -     VSS     S     -     -     -     -       -     H10     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     -     VSS     S     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J7     -     -     -     -     -     VSS     S     -     -     -     -       -     J8     -     -     -     -     -     VSS     S     -     -     -     -       -     J10     -     -     -     -     - <td>-</td> <td>-</td> <td>H6</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td> <td>VSS</td> <td>s</td> <td>-</td> <td>-</td> <td>-</td> <td>-</td>                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       | -       | H6       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -     H9     -     -     -     -     -     VSS     S     -     -     -       -     H10     -     -     -     -     -     VSS     S     -     -     -       -     H10     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     VSS     S     -     -     -     -       -     J6     -     -     -     -     -     -     VSS     S     -     -     -     -       -     J7     -     -     -     -     -     -     VSS     S     -     -     -       -     J8     -     -     -     -     -     VSS     S     -     -     -     -       -     J9     -     -     -     -     -     VSS     S     -     -     -       -     J10     -     -     -     -     -     VSS     S     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       | -       | H7       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       H10       -       -       -       -       -       VSS       S       -       -       -       -       -         -       J6       -       -       -       -       -       VSS       S       -       -       -       -       -         -       J6       -       -       -       -       -       VSS       S       -       -       -       -       -         -       J7       -       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -       | -       | H8       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       J6       -       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -       | -       | H9       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       J7       -       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -       | -       | H10      | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       J8       -       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -       | -       | J6       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       J9       -       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -       | -       | J7       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       J10       -       -       -       -       VSS       S       -       -       -       -       -         -       K6       -       -       -       -       VSS       S       -       -       -       -       -         -       K6       -       -       -       -       -       VSS       S       -       -       -       -         -       K7       -       -       -       -       VSS       S       -       -       -       -         -       K8       -       -       -       -       -       VSS       S       -       -       -       -       -         -       K8       -       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -       | -       | J8       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       K6       -       -       -       -       VSS       S       -       -       -       -       -         -       K7       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -       | -       | J9       | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       K6       -       -       -       -       VSS       S       -       -       -       -       -         -       K7       -       -       -       -       VSS       S       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -       | -       | J10      | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | -             | -     | -                   | - |

| -       K7       -       -       -       -       VSS       S       -       -       -       -       -         -       K8       -       -       -       -       VSS       S       -       -       -       -       -         -       K8       -       -       -       -       VSS       S       -       -       -       -         -       K9       -       -       -       -       VSS       S       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -       | -       | K6       | -       | -       | -        | -                       | -       | -       | -        |                          |          | -             | -     | -                   | - |

| -       K8       -       -       -       -       VSS       S       -       -       -       -       -         -       -       K9       -       -       -       -       VSS       S       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -       | -       |          | -       | -       | -        | -                       | -       | -       | -        |                          |          | -             | -     | _                   | - |

| K9 VSS S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -       | -       |          | -       | -       | -        | -                       | -       | -       | -        | VSS                      |          | -             | -     | -                   | - |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -       | -       |          | -       | -       | -        | -                       | -       | -       | -        |                          |          | _             | -     | -                   | - |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -       | -       | K10      | -       | -       | -        | -                       | -       | -       | -        | VSS                      | s        | _             | -     | _                   | _ |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

| Pinouts  |

|----------|

| and p    |

| vin des  |

| scriptio |

|          |

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

### Table 12. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx alternate

function mapping

|        |      |      |                           |              |                                            |                               |                                                        | unction                                                        | тарри                                                                          | <u>'9</u>                                                     |                                                    |                                                                        |                                                 |                                                |                  |               |              |

|--------|------|------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------|------------------|---------------|--------------|

|        |      | AF0  | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                                            | AF12                                           | AF13             | AF14          | AF15         |

| P      | ort  | SYS  | 12C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH                    | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD           | SYS          |

|        | PA0  | -    | TIM2_C<br>H1/TIM2<br>_ETR | TIM5_C<br>H1 | TIM8_ET<br>R                               | -                             | -                                                      | -                                                              | USART2<br>_CTS                                                                 | UART4_<br>TX                                                  | -                                                  | SAI2_SD_<br>B                                                          | ETH_MII_<br>CRS                                 | -                                              | -                | -             | EVEN<br>TOUT |

|        | PA1  | -    | TIM2_C<br>H2              | TIM5_C<br>H2 | -                                          | -                             | -                                                      | -                                                              | USART2<br>_RTS                                                                 | UART4_<br>RX                                                  | QUADSP<br>I_BK1_IO<br>3                            | SAI2_MC<br>K_B                                                         | ETH_MII_<br>RX_CLK/<br>ETH_RMI<br>I_REF_C<br>LK | -                                              | -                | LCD_R2        | EVEN<br>TOUT |

|        | PA2  | -    | TIM2_C<br>H3              | TIM5_C<br>H3 | TIM9_CH<br>1                               | -                             | -                                                      | -                                                              | USART2<br>_TX                                                                  | SAI2_SC<br>K_B                                                | -                                                  | -                                                                      | ETH_MDI<br>O                                    | MDIOS_<br>MDIO                                 | -                | LCD_R1        | EVEN<br>TOUT |

|        | PA3  | -    | TIM2_C<br>H4              | TIM5_C<br>H4 | TIM9_CH<br>2                               | -                             | -                                                      | -                                                              | USART2<br>_RX                                                                  | -                                                             | LCD_B2                                             | OTG_HS_<br>ULPI_D0                                                     | ETH_MII_<br>COL                                 | -                                              | -                | LCD_B5        | EVEN<br>TOUT |

|        | PA4  | -    | -                         | -            | -                                          | -                             | SPI1_NS<br>S/I2S1_<br>WS                               | SPI3_NS<br>S/I2S3_<br>WS                                       | USART2<br>_CK                                                                  | SPI6_NS<br>S                                                  | -                                                  | -                                                                      | -                                               | OTG_HS<br>_SOF                                 | DCMI_H<br>SYNC   | LCD_VS<br>YNC | EVEN<br>TOUT |

| Port A | PA5  | -    | TIM2_C<br>H1/TIM2<br>_ETR | -            | TIM8_CH<br>1N                              | -                             | SPI1_SC<br>K/I2S1_<br>CK                               | -                                                              | -                                                                              | SPI6_SC<br>K                                                  | -                                                  | OTG_HS_<br>ULPI_CK                                                     | -                                               | -                                              | -                | LCD_R4        | EVEN<br>TOUT |

|        | PA6  | -    | TIM1_B<br>KIN             | TIM3_C<br>H1 | TIM8_BKI<br>N                              | -                             | SPI1_MI<br>SO                                          | -                                                              | -                                                                              | SPI6_MI<br>SO                                                 | TIM13_C<br>H1                                      | -                                                                      | -                                               | MDIOS_<br>MDC                                  | DCMI_PI<br>XCLK  | LCD_G2        | EVEN<br>TOUT |

|        | PA7  | -    | TIM1_C<br>H1N             | TIM3_C<br>H2 | TIM8_CH<br>1N                              | -                             | SPI1_M<br>OSI/I2S1<br>_SD                              | -                                                              | -                                                                              | SPI6_MO<br>SI                                                 | TIM14_C<br>H1                                      | -                                                                      | ETH_MII_<br>RX_DV/E<br>TH_RMII_<br>CRS_DV       | FMC_SD<br>NWE                                  | -                | -             | EVEN<br>TOUT |

|        | PA8  | MCO1 | TIM1_C<br>H1              | -            | TIM8_BKI<br>N2                             | I2C3_SC<br>L                  | -                                                      | -                                                              | USART1<br>_CK                                                                  | -                                                             | -                                                  | OTG_FS_<br>SOF                                                         | CAN3_R<br>X                                     | UART7_<br>RX                                   | LCD_B3           | LCD_R6        | EVEN<br>TOUT |

|        | PA9  | -    | TIM1_C<br>H2              | -            | -                                          | I2C3_SM<br>BA                 | SPI2_SC<br>K/I2S2_<br>CK                               | -                                                              | USART1<br>_TX                                                                  | -                                                             | -                                                  | -                                                                      | -                                               | -                                              | DCMI_D<br>0      | LCD_R5        | EVEN<br>TOUT |

|        | PA10 | -    | TIM1_C<br>H3              | -            | -                                          | -                             | -                                                      | -                                                              | USART1<br>_RX                                                                  | -                                                             | LCD_B4                                             | OTG_FS_<br>ID                                                          | -                                               | MDIOS_<br>MDIO                                 | DCMI_D<br>1      | LCD_B1        | EVEN<br>TOUT |

92/255

DocID029041 Rev 4

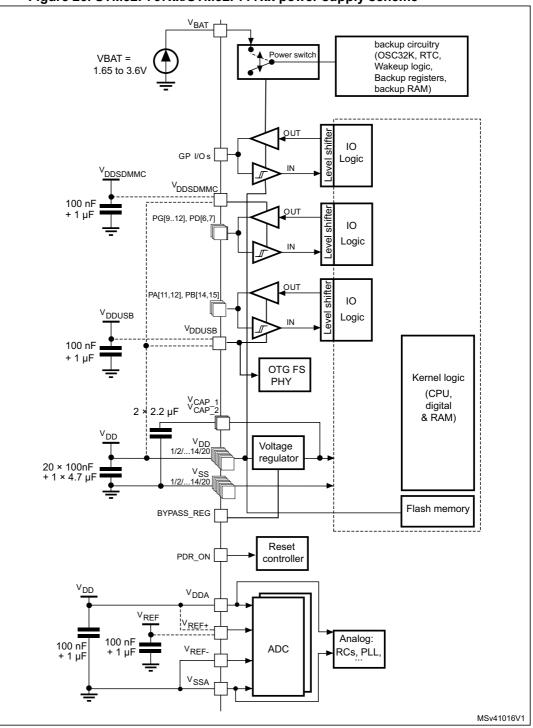

Figure 25. STM32F767xx/STM32F777xx power supply scheme

1. To connect BYPASS\_REG and PDR\_ON pins, refer to Section 2.18: Power supply supervisor and Section 2.19: Voltage regulator.

2. The two 2.2  $\mu F$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

- 3. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

- 4.  $V_{DDA}=V_{DD}$  and  $V_{SSA}=V_{SS}$ .

# Table 30. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (Dual bank mode) on ITCM interface (ART disabled), regulator ON

| Cumhal          | Demonster | Conditions                                   | £ (8411-)               | True |           | Max <sup>(1)</sup> |           | 11   |

|-----------------|-----------|----------------------------------------------|-------------------------|------|-----------|--------------------|-----------|------|

| Symbol          | Parameter | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | TA= 25 °C | TA=85 °C           | TA=105 °C | Unit |

|                 |           |                                              | 216                     | 191  | 218       | 255                | -         |      |

|                 |           |                                              | 200                     | 178  | 195       | 241                | 269       |      |

|                 |           |                                              | 180                     | 164  | 179       | 214                | 236       |      |

|                 |           | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 147  | 160       | 192                | 212       |      |

|                 |           | Supply<br>surrent in                         | 144                     | 121  | 130       | 157                | 175       |      |

|                 |           |                                              | 60                      | 60   | 66        | 93                 | 111       |      |

|                 | Supply    |                                              | 25                      | 28   | 33        | 59                 | 77        | mA   |

| I <sub>DD</sub> | RUN mode  |                                              | 216                     | 93   | 104       | 150                | -         |      |

|                 |           |                                              | 200                     | 87   | 97        | 144                | 171       |      |

|                 |           |                                              | 180                     | 83   | 92        | 126                | 148       |      |

|                 |           | All peripherals disabled <sup>(3)</sup>      | 168                     | 75   | 82        | 114                | 134       |      |

|                 |           | uisabicu                                     | 144                     | 65   | 71        | 97                 | 115       |      |

|                 |           |                                              | 60                      | 35   | 40        | 66                 | 84        |      |

|                 |           |                                              | 25                      | 16   | 20        | 47                 | 64        |      |

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

|        |                    |                                                                 |                                                                | Typ <sup>(1)</sup>         |                            |                           | Max <sup>(2)</sup>        |                            |      |  |

|--------|--------------------|-----------------------------------------------------------------|----------------------------------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|----------------------------|------|--|

| Symbol | Parameter          | Conditions                                                      | Ţ                                                              | <sub>A</sub> = 25 °        | С                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |  |

|        |                    |                                                                 | V <sub>DD</sub> =<br>1.7 V                                     | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V                         | / <sub>DD</sub> = 3.3     | v                          |      |  |

|        |                    | Backup SRAM OFF, RTC and LSE OFF                                | 1.1                                                            | 1.9                        | 2.4                        | 5 <sup>(3)</sup>          | 18 <sup>(3)</sup>         | 38 <sup>(3)</sup>          |      |  |

|        |                    | Backup SRAM ON, RTC and LSE OFF                                 | 1.9                                                            | 2.7                        | 3.2                        | 6 <sup>(3)</sup>          | 23 <sup>(3)</sup>         | 48 <sup>(3)</sup>          |      |  |

|        |                    | Backup SRAM OFF, RTC ON<br>and LSE in low drive mode            | 1.7                                                            | 2.7                        | 3.5                        | 7                         | 26                        | 55                         |      |  |

|        | Supply current     |                                                                 | Backup SRAM OFF, RTC ON<br>and LSE in medium low drive<br>mode | 1.7                        | 2.7                        | 3.5                       | 7                         | 26                         | 56   |  |

|        |                    | Backup SRAM OFF, RTC ON<br>and LSE in medium high drive<br>mode | 1.8                                                            | 2.8                        | 3.6                        | 8                         | 28                        | 57                         | μA   |  |

|        | in Standby<br>mode | Backup SRAM OFF, RTC ON<br>and LSE in high drive mode           | 1.9                                                            | 2.9                        | 3.7                        | 8                         | 28                        | 59                         |      |  |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in low drive mode             | 2.4                                                            | 3.4                        | 4.3                        | 8                         | 31                        | 65                         |      |  |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in Medium low drive<br>mode   | 2.4                                                            | 3.5                        | 4.3                        | 8                         | 31                        | 65                         |      |  |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in Medium high drive<br>mode  | 2.6                                                            | 3.7                        | 4.5                        | 8                         | 8 33                      |                            |      |  |

|        |                    | Backup SRAM ON, RTC ON<br>and LSE in High drive mode            | 2.6                                                            | 3.7                        | 4.5                        | 9                         | 33                        | 68                         |      |  |

Table 36. Typical and maximum current consumptions in Standby mode

The typical current consumption values are given with PDR OFF (internal reset OFF). When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2 μA.

2. Guaranteed by characterization results, unless otherwise specified.

3. Guaranteed by test in production.

### 5.3.8 Wakeup time from low-power modes

The wakeup times given in *Table 40* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Symbol                              | Parameter                                   | Conditions                                                                               | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                   |

|-------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------|--------------------|--------------------|------------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup> | Wakeup from Sleep                           | -                                                                                        | 13                 | 13                 | CPU<br>clock<br>cycles |

|                                     |                                             | Main regulator is ON                                                                     | 14                 | 14.9               |                        |

| . (2)                               | Wakeup from Stop mode                       | Main regulator is ON and Flash<br>memory in Deep power down mode                         | 104.1              | 107.6              |                        |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | with MR/LP regulator in normal mode         | Low power regulator is ON                                                                | 21.4               | 24.2               |                        |

|                                     |                                             | Low power regulator is ON and Flash memory in Deep power down mode                       | 111.5              | 116.5              | μs                     |

|                                     | Wakeup from Stop mode                       | Main regulator in under-drive mode<br>(Flash memory in Deep power-down<br>mode)          | 107.4              | 113.2              |                        |

| t <sub>WUSTOP</sub> <sup>(2)</sup>  | with MR/LP regulator in<br>Under-drive mode | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-down<br>mode ) | 112.7              | 120                |                        |