# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                                |

| Core Processor                | ARM® Cortex®-M7                                                                                                       |

| Core Size                     | 32-Bit Single-Core                                                                                                    |

| Speed                         | 216MHz                                                                                                                |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                                     |

| Number of I/O                 | 82                                                                                                                    |

| Program Memory Size           | 1MB (1M x 8)                                                                                                          |

| Program Memory Type           | FLASH                                                                                                                 |

| EEPROM Size                   | ·                                                                                                                     |

| RAM Size                      | 512K x 8                                                                                                              |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                                           |

| Data Converters               | A/D 16x12b; D/A 2x12b                                                                                                 |

| Oscillator Type               | Internal                                                                                                              |

| Operating Temperature         | -40°C ~ 105°C (TA)                                                                                                    |

| Mounting Type                 | Surface Mount                                                                                                         |

| Package / Case                | 100-LQFP                                                                                                              |

| Supplier Device Package       | 100-LQFP (14x14)                                                                                                      |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f767vgt7                                                 |

|                               |                                                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

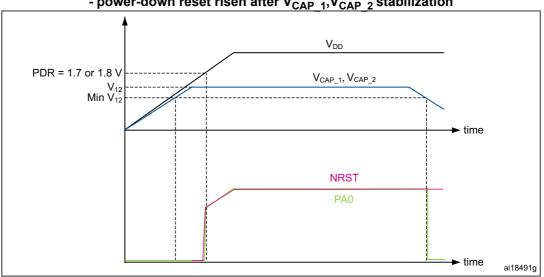

Figure 9. Startup in regulator OFF: slow V<sub>DD</sub> slope - power-down reset risen after V<sub>CAP\_1</sub>, V<sub>CAP\_2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

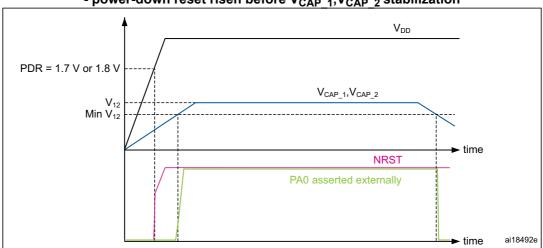

Figure 10. Startup in regulator OFF mode: fast V<sub>DD</sub> slope - power-down reset risen before V<sub>CAP\_1</sub>, V<sub>CAP\_2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

SAI1 and SAI2 can be served by the DMA controller

## 2.28 SPDIFRX Receiver Interface (SPDIFRX)

The SPDIFRX peripheral, is designed to receive an S/PDIF flow compliant with IEC-60958 and IEC-61937. These standards support simple stereo streams up to high sample rate, and compressed multi-channel surround sound, such as those defined by Dolby or DTS (up to 5.1).

The main features of the SPDIFRX are the following:

- Up to 4 inputs available

- Automatic symbol rate detection

- Maximum symbol rate: 12.288 MHz

- Stereo stream from 32 to 192 kHz supported

- Supports Audio IEC-60958 and IEC-61937, consumer applications

- Parity bit management

- Communication using DMA for audio samples

- Communication using DMA for control and user channel information

- Interrupt capabilities

The SPDIFRX receiver provides all the necessary features to detect the symbol rate, and decode the incoming data stream. The user can select the wanted SPDIF input, and when a valid signal will be available, the SPDIFRX will re-sample the incoming signal, decode the manchester stream, recognize frames, sub-frames and blocks elements. It delivers to the CPU decoded data, and associated status flags.

The SPDIFRX also offers a signal named spdif\_frame\_sync, which toggles at the S/PDIF sub-frame rate that will be used to compute the exact sample rate for clock drift algorithms.

## 2.29 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the  $I^2S/SAI$  flow with an external PLL (or Codec output).

## 2.30 Audio and LCD PLL (PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

## 2.44 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- Two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

### 2.45 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 2.46 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F76xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

- Programmable polarity of all LTDC interface signals

- Extended resolutions beyond the DPI standard

- Maximum resolution of 800x480 pixels:

- Maximum resolution is limited by available DSI physical link bandwidth:

- Number of lanes: 2

- Maximum speed per lane: 500 Mbps1Gbps

#### Adapted interface features

Support for sending large amounts of data through the memory\_write\_start(WMS) and memory\_write\_continue(WMC) DCS commands

- LTDC interface color coding mappings into 24-bit interface:

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

#### Video mode pattern generator:

- Vertical and horizontal color bar generation without LTDC stimuli

- BER pattern without LTDC stimuli

| Name                   | Abbreviation                                                     | Definition                                                                                         |  |  |  |  |  |  |

|------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Pin name               |                                                                  | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |  |

|                        | S Supply pin                                                     |                                                                                                    |  |  |  |  |  |  |

| Pin type               | I                                                                | Input only pin                                                                                     |  |  |  |  |  |  |

|                        | I/O                                                              | Input / output pin                                                                                 |  |  |  |  |  |  |

|                        | FT                                                               | 5 V tolerant I/O                                                                                   |  |  |  |  |  |  |

| I/O structure          | TTa 3.3 V tolerant I/O directly connected to ADC                 |                                                                                                    |  |  |  |  |  |  |

| 1/O structure          | B Dedicated BOOT pin                                             |                                                                                                    |  |  |  |  |  |  |

|                        | RST                                                              | Bidirectional reset pin with weak pull-up resistor                                                 |  |  |  |  |  |  |

| Notes                  | Unless otherwise                                                 | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |  |

| Alternate<br>functions | Functions selected                                               | d through GPIOx_AFR registers                                                                      |  |  |  |  |  |  |

| Additional functions   | Functions directly selected/enabled through peripheral registers |                                                                                                    |  |  |  |  |  |  |

#### Table 9. Legend/abbreviations used in the pinout table

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions

|         |         |              | l       | Pin N   | umbe     | ər                      |         |                |          |                                |          |               |       |                                                                                               |                         |  |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|--|

|         | -       | TM32<br>TM32 |         |         | I        | -                       |         | F768/<br>F769: |          | reset                          | reset    |               |       |                                                                                               |                         |  |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                           | Additional<br>functions |  |

| 1       | 1       | A2           | 1       | 1       | A3       | E10                     | 1       | 1              | A3       | PE2                            | I/O      | FT            | -     | TRACECLK, SPI4_SCK,<br>SAI1_MCLK_A,<br>QUADSPI_BK1_IO2,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT | -                       |  |

| 2       | 2       | A1           | 2       | 2       | A2       | F10                     | 2       | 2              | A2       | PE3                            | I/O      | FT            | -     | TRACED0, SAI1_SD_B,<br>FMC_A19, EVENTOUT                                                      | -                       |  |

|         |         |              | l       | Pin N   | umbe     | ər                      |             |         |          |                                |          |               | -     |                                                                                                                                                   |                                    |  |

|---------|---------|--------------|---------|---------|----------|-------------------------|-------------|---------|----------|--------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|

|         |         | TM32<br>TM32 |         |         | 1        |                         | M32I<br>M32 |         |          | reset                          |          |               |       |                                                                                                                                                   |                                    |  |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176     | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                               | Additional<br>functions            |  |

| 28      | 40      | N4           | 50      | 53      | N4       | L9                      | 50          | 53      | N4       | PA4                            | I/O      | TT<br>a       | -     | SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK, SPI6_NSS,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC, EVENTOUT                               | ADC1_IN4,<br>ADC2_IN4,<br>DAC_OUT1 |  |

| 29      | 41      | P4           | 51      | 54      | P4       | P11                     | 51          | 54      | P4       | PA5                            | I/O      | TT<br>a       | -     | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK/I2S1_CK,<br>SPI6_SCK,<br>OTG_HS_ULPI_CK,<br>LCD_R4, EVENTOUT                                         | ADC1_IN5,<br>ADC2_IN5,<br>DAC_OUT2 |  |

| 30      | 42      | P3           | 52      | 55      | P3       | N10                     | 52          | 55      | P3       | PA6                            | I/O      | FT            | -     | TIM1_BKIN, TIM3_CH1,<br>TIM8_BKIN, SPI1_MISO,<br>SPI6_MISO, TIM13_CH1,<br>MDIOS_MDC,<br>DCMI_PIXCLK, LCD_G2,<br>EVENTOUT                          | ADC1_IN6,<br>ADC2_IN6              |  |

| 31      | 43      | R3           | 53      | 56      | R3       | М9                      | 53          | 56      | R3       | PA7                            | I/O      | FT            | -     | TIM1_CH1N, TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI/I2S1_SD,<br>SPI6_MOSI, TIM14_CH1,<br>ETH_MII_RX_DV/ETH_RM<br>II_CRS_DV,<br>FMC_SDNWE,<br>EVENTOUT | ADC1_IN7,<br>ADC2_IN7              |  |

| 32      | 44      | N5           | 54      | 57      | N5       | NC                      | 54          | 57      | N5       | PC4                            | I/O      | FT            | -     | DFSDM1_CKIN2,<br>I2S1_MCK, SPDIF_RX2,<br>ETH_MII_RXD0/ETH_RMII<br>_RXD0, FMC_SDNE0,<br>EVENTOUT                                                   | ADC1_IN14,<br>ADC2_IN14            |  |

| 33      | 45      | P5           | 55      | 58      | P5       | NC                      | 55          | 58      | P5       | PC5                            | I/O      | FT            | -     | DFSDM1_DATIN2,<br>SPDIF_RX3,<br>ETH_MII_RXD1/ETH_RMII<br>_RXD1, FMC_SDCKE0,<br>EVENTOUT                                                           | ADC1_IN15,<br>ADC2_IN15            |  |

| -       | -       | -            | -       | 59      | L7       | -                       | -           | 59      | L7       | VDD                            | S        | -             | -     | -                                                                                                                                                 | -                                  |  |

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|         |         |              | I       | Pin N   | umbe     | er                      |               |         |          |                                |          |               | ,     |                                                                                  |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | FM32 <br>FM32 |         |          | reset                          |          |               |       |                                                                                  |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -       | 51      | M8           | 61      | 72      | K7       | P9                      | 61            | 72      | K7       | VSS                            | S        |               | -     | -                                                                                | -                       |

| -       | 52      | N8           | 62      | 73      | L8       | M8                      | 62            | 73      | L8       | VDD                            | S        |               | -     | -                                                                                | -                       |

| -       | 53      | N6           | 63      | 74      | N6       | L8                      | 63            | 74      | N6       | PF13                           | I/O      | FT            | -     | I2C4_SMBA,<br>DFSDM1_DATIN6,<br>FMC_A7, EVENTOUT                                 | -                       |

| -       | 54      | R7           | 64      | 75      | P6       | K8                      | 64            | 75      | P6       | PF14                           | I/O      | FT            | -     | I2C4_SCL,<br>DFSDM1_CKIN6,<br>FMC_A8, EVENTOUT                                   | -                       |

| -       | 55      | P7           | 65      | 76      | M8       | P8                      | 65            | 76      | M8       | PF15                           | 1/0      | FT            | -     | I2C4_SDA, FMC_A9,<br>EVENTOUT                                                    | -                       |

| -       | 56      | N7           | 66      | 77      | N7       | N8                      | 66            | 77      | N7       | PG0                            | I/O      | FT            | -     | FMC_A10, EVENTOUT                                                                | -                       |

| -       | 57      | M7           | 67      | 78      | M7       | L7                      | 67            | 78      | M7       | PG1                            | I/O      | FT            | -     | FMC_A11, EVENTOUT                                                                | -                       |

| 37      | 58      | R8           | 68      | 79      | R8       | M7                      | 68            | 79      | R8       | PE7                            | I/O      | FT            | -     | TIM1_ETR,<br>DFSDM1_DATIN2,<br>UART7_RX,<br>QUADSPI_BK2_IO0,<br>FMC_D4, EVENTOUT | -                       |

| 38      | 59      | P8           | 69      | 80      | N9       | N7                      | 69            | 80      | N9       | PE8                            | I/O      | FT            | -     | TIM1_CH1N,<br>DFSDM1_CKIN2,<br>UART7_TX,<br>QUADSPI_BK2_IO1,<br>FMC_D5, EVENTOUT | -                       |

| 39      | 60      | P9           | 70      | 81      | P9       | P7                      | 70            | 81      | P9       | PE9                            | I/O      | FT            | -     | TIM1_CH1,<br>DFSDM1_CKOUT,<br>UART7_RTS,<br>QUADSPI_BK2_IO2,<br>FMC_D6, EVENTOUT | -                       |

| -       | 61      | M9           | 71      | 82      | K8       | -                       | 71            | 82      | K8       | VSS                            | S        | -             | -     | -                                                                                | -                       |

| -       | 62      | N9           | 72      | 83      | L9       | -                       | 72            | 83      | L9       | VDD                            | S        | -             | -     | -                                                                                | -                       |

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|         |         |              | l       | Pin N   | umbe     | er                      |               |         |          |                                |          |               |       |                                                                                                                                                                                 |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         | 1        |                         | FM32I<br>FM32 |         |          | reset                          |          |               |       |                                                                                                                                                                                 |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                                             | Additional<br>functions |

| 96      | 140     | B4           | 168     | 199     | B4       | D9                      | 168           | 199     | B4       | PB9                            | I/O      | FT            | -     | I2C4_SDA, TIM4_CH4,<br>TIM11_CH1, I2C1_SDA,<br>SPI2_NSS/I2S2_WS,<br>DFSDM1_DATIN7,<br>UART5_TX, CAN1_TX,<br>SDMMC2_D5,<br>I2C4_SMBA,<br>SDMMC1_D5, DCMI_D7,<br>LCD_B7, EVENTOUT | -                       |

| 97      | 141     | A4           | 169     | 200     | A6       | C9                      | 169           | 200     | A6       | PE0                            | I/O      | FT            | -     | TIM4_ETR, LPTIM1_ETR,<br>UART8_RX,<br>SAI2_MCLK_A,<br>FMC_NBL0, DCMI_D2,<br>EVENTOUT                                                                                            | -                       |

| 98      | 142     | A3           | 170     | 201     | A5       | B10                     | 170           | 201     | A5       | PE1                            | I/O      | FT            | -     | LPTIM1_IN2, UART8_TX,<br>FMC_NBL1, DCMI_D3,<br>EVENTOUT                                                                                                                         | -                       |

| 99      | -       | D5           | -       | 202     | F6       | A11                     | -             | 202     | F6       | VSS                            | s        | -             | -     | -                                                                                                                                                                               | -                       |

| -       | 143     | C6           | 171     | 203     | E5       | C10                     | 171           | 203     | E5       | PDR_ON                         | s        | -             | -     | -                                                                                                                                                                               | -                       |

| 10<br>0 | 144     | C5           | 172     | 204     | E7       | B11                     | 172           | 204     | E7       | VDD                            | s        | -             | -     | -                                                                                                                                                                               | -                       |

| -       | -       | D4           | 173     | 205     | C3       | D10                     | 173           | 205     | C3       | Pl4                            | I/O      | FT            | -     | TIM8_BKIN,<br>SAI2_MCLK_A,<br>FMC_NBL2, DCMI_D5,<br>LCD_B4, EVENTOUT                                                                                                            | -                       |

| -       | -       | C4           | 174     | 206     | D3       | D11                     | 174           | 206     | D3       | PI5                            | I/O      | FT            | -     | TIM8_CH1, SAI2_SCK_A,<br>FMC_NBL3,<br>DCMI_VSYNC, LCD_B5,<br>EVENTOUT                                                                                                           | -                       |

| -       | -       | C3           | 175     | 207     | D6       | C11                     | 175           | 207     | D6       | Pl6                            | 1/0      | FT            | -     | TIM8_CH2, SAI2_SD_A,<br>FMC_D28, DCMI_D6,<br>LCD_B6, EVENTOUT                                                                                                                   | -                       |

| -       | -       | C2           | 176     | 208     | D4       | B12                     | 176           | 208     | D4       | PI7                            | I/O      | FT            | -     | TIM8_CH3, SAI2_FS_A,<br>FMC_D29, DCMI_D7,<br>LCD_B7, EVENTOUT                                                                                                                   | -                       |

## Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

| Pin name | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |  |  |  |  |

|----------|--------------------|------------------|--------|-------|--|--|--|--|--|--|--|--|

| PF0      | A0                 | -                | -      | A0    |  |  |  |  |  |  |  |  |

| PF1      | A1                 | -                | -      | A1    |  |  |  |  |  |  |  |  |

| PF2      | A2                 | -                | -      | A2    |  |  |  |  |  |  |  |  |

| PF3      | A3                 | -                | -      | A3    |  |  |  |  |  |  |  |  |

| PF4      | A4                 | -                | -      | A4    |  |  |  |  |  |  |  |  |

| PF5      | A5                 | -                | -      | A5    |  |  |  |  |  |  |  |  |

| PF12     | A6                 | -                | -      | A6    |  |  |  |  |  |  |  |  |

| PF13     | A7                 | -                | -      | A7    |  |  |  |  |  |  |  |  |

| PF14     | A8                 | -                | -      | A8    |  |  |  |  |  |  |  |  |

| PF15     | A9                 | -                | -      | A9    |  |  |  |  |  |  |  |  |

| PG0      | A10                | -                | -      | A10   |  |  |  |  |  |  |  |  |

| PG1      | A11                | -                | -      | A11   |  |  |  |  |  |  |  |  |

| PG2      | A12                | -                | -      | A12   |  |  |  |  |  |  |  |  |

| PG3      | A13                | -                | -      | -     |  |  |  |  |  |  |  |  |

| PG4      | A14                | -                | -      | BA0   |  |  |  |  |  |  |  |  |

| PG5      | A15                | -                | -      | BA1   |  |  |  |  |  |  |  |  |

| PD11     | A16                | A16              | CLE    | -     |  |  |  |  |  |  |  |  |

| PD12     | A17                | A17              | ALE    | -     |  |  |  |  |  |  |  |  |

| PD13     | A18                | A18              | -      | -     |  |  |  |  |  |  |  |  |

| PE3      | A19                | A19              | -      | -     |  |  |  |  |  |  |  |  |

| PE4      | A20                | A20              | _      | -     |  |  |  |  |  |  |  |  |

| PE5      | A21                | A21              | -      | _     |  |  |  |  |  |  |  |  |

| PE6      | A22                | A22              | -      | -     |  |  |  |  |  |  |  |  |

| PE2      | A23                | A23              | -      | -     |  |  |  |  |  |  |  |  |

| PG13     | A24                | A24              | -      | -     |  |  |  |  |  |  |  |  |

| PG14     | A25                | A25              | -      | -     |  |  |  |  |  |  |  |  |

| PD14     | D0                 | DA0              | D0     | D0    |  |  |  |  |  |  |  |  |

| PD15     | D1                 | DA1              | D1     | D1    |  |  |  |  |  |  |  |  |

| PD0      | D2                 | DA2              | D2     | D2    |  |  |  |  |  |  |  |  |

| PD1      | D3                 | DA3              | D3     | D3    |  |  |  |  |  |  |  |  |

| PE7      | D4                 | DA4              | D4     | D4    |  |  |  |  |  |  |  |  |

| PE8      | D5                 | DA5              | D5     | D5    |  |  |  |  |  |  |  |  |

| PE9      | D6                 | DA6              | D6     | D6    |  |  |  |  |  |  |  |  |

| PE10     | D7                 | DA7              | D7     | D7    |  |  |  |  |  |  |  |  |

Table 11. FMC pin definition

| Pinouts  |

|----------|

| and p    |

| vin des  |

| scriptio |

|          |

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

### Table 12. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx alternate

function mapping

|        |      | AF0  | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                                            | AF12                                           | AF13             | AF14          | AF15         |

|--------|------|------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------|------------------|---------------|--------------|

| P      | ort  | SYS  | 12C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH                    | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD           | SYS          |

|        | PA0  | -    | TIM2_C<br>H1/TIM2<br>_ETR | TIM5_C<br>H1 | TIM8_ET<br>R                               | -                             | -                                                      | -                                                              | USART2<br>_CTS                                                                 | UART4_<br>TX                                                  | -                                                  | SAI2_SD_<br>B                                                          | ETH_MII_<br>CRS                                 | -                                              | -                | -             | EVEN<br>TOUT |

|        | PA1  | -    | TIM2_C<br>H2              | TIM5_C<br>H2 | -                                          | -                             | -                                                      | -                                                              | USART2<br>_RTS                                                                 | UART4_<br>RX                                                  | QUADSP<br>I_BK1_IO<br>3                            | SAI2_MC<br>K_B                                                         | ETH_MII_<br>RX_CLK/<br>ETH_RMI<br>I_REF_C<br>LK | -                                              | -                | LCD_R2        | EVEN<br>TOUT |

|        | PA2  | -    | TIM2_C<br>H3              | TIM5_C<br>H3 | TIM9_CH<br>1                               | -                             | -                                                      | -                                                              | USART2<br>_TX                                                                  | SAI2_SC<br>K_B                                                | -                                                  | -                                                                      | ETH_MDI<br>O                                    | MDIOS_<br>MDIO                                 | -                | LCD_R1        | EVEN<br>TOUT |

|        | PA3  | -    | TIM2_C<br>H4              | TIM5_C<br>H4 | TIM9_CH<br>2                               | -                             | -                                                      | -                                                              | USART2<br>_RX                                                                  | -                                                             | LCD_B2                                             | OTG_HS_<br>ULPI_D0                                                     | ETH_MII_<br>COL                                 | -                                              | -                | LCD_B5        | EVEN<br>TOUT |

|        | PA4  | -    | -                         | -            | -                                          | -                             | SPI1_NS<br>S/I2S1_<br>WS                               | SPI3_NS<br>S/I2S3_<br>WS                                       | USART2<br>_CK                                                                  | SPI6_NS<br>S                                                  | -                                                  | -                                                                      | -                                               | OTG_HS<br>_SOF                                 | DCMI_H<br>SYNC   | LCD_VS<br>YNC | EVEN<br>TOUT |

| Port A | PA5  | -    | TIM2_C<br>H1/TIM2<br>_ETR | -            | TIM8_CH<br>1N                              | -                             | SPI1_SC<br>K/I2S1_<br>CK                               | -                                                              | -                                                                              | SPI6_SC<br>K                                                  | -                                                  | OTG_HS_<br>ULPI_CK                                                     | -                                               | -                                              | -                | LCD_R4        | EVEN<br>TOUT |

|        | PA6  | -    | TIM1_B<br>KIN             | TIM3_C<br>H1 | TIM8_BKI<br>N                              | -                             | SPI1_MI<br>SO                                          | -                                                              | -                                                                              | SPI6_MI<br>SO                                                 | TIM13_C<br>H1                                      | -                                                                      | -                                               | MDIOS_<br>MDC                                  | DCMI_PI<br>XCLK  | LCD_G2        | EVEN<br>TOUT |

|        | PA7  | -    | TIM1_C<br>H1N             | TIM3_C<br>H2 | TIM8_CH<br>1N                              | -                             | SPI1_M<br>OSI/I2S1<br>_SD                              | -                                                              | -                                                                              | SPI6_MO<br>SI                                                 | TIM14_C<br>H1                                      | -                                                                      | ETH_MII_<br>RX_DV/E<br>TH_RMII_<br>CRS_DV       | FMC_SD<br>NWE                                  | -                | -             | EVEN<br>TOUT |

|        | PA8  | MCO1 | TIM1_C<br>H1              | -            | TIM8_BKI<br>N2                             | I2C3_SC<br>L                  | -                                                      | -                                                              | USART1<br>_CK                                                                  | -                                                             | -                                                  | OTG_FS_<br>SOF                                                         | CAN3_R<br>X                                     | UART7_<br>RX                                   | LCD_B3           | LCD_R6        | EVEN<br>TOUT |

|        | PA9  | -    | TIM1_C<br>H2              | -            | -                                          | I2C3_SM<br>BA                 | SPI2_SC<br>K/I2S2_<br>CK                               | -                                                              | USART1<br>_TX                                                                  | -                                                             | -                                                  | -                                                                      | -                                               | -                                              | DCMI_D<br>0      | LCD_R5        | EVEN<br>TOUT |

|        | PA10 | -    | TIM1_C<br>H3              | -            | -                                          | -                             | -                                                      | -                                                              | USART1<br>_RX                                                                  | -                                                             | LCD_B4                                             | OTG_FS_<br>ID                                                          | -                                               | MDIOS_<br>MDIO                                 | DCMI_D<br>1      | LCD_B1        | EVEN<br>TOUT |

92/255

| Bus       | Boundary address          | Peripheral                     |

|-----------|---------------------------|--------------------------------|

|           | 0xE00F FFFF - 0xFFFF FFFF | Reserved                       |

| Cortex-M7 | 0xE000 0000 - 0xE00F FFFF | Cortex-M7 internal peripherals |

|           | 0xD000 0000 - 0xDFFF FFFF | FMC bank 6                     |

|           | 0xC000 0000 - 0xCFFF FFFF | FMC bank 5                     |

|           | 0xA000 2000 - 0xBFFF FFFF | Reserved                       |

|           | 0xA000 1000 - 0xA000 1FFF | Quad-SPI control register      |

| AHB3      | 0xA000 0000- 0xA000 0FFF  | FMC control register           |

|           | 0x9000 0000 - 0x9FFF FFFF | Quad-SPI                       |

|           | 0x8000 0000 - 0x8FFF FFFF | FMC bank 3                     |

|           | 0x7000 0000 - 0x7FFF FFFF | FMC bank 2                     |

|           | 0x6000 0000 - 0x6FFF FFFF | FMC bank 1                     |

|           | 0x5006 0C00- 0x5FFF FFFF  | Reserved                       |

|           | 0x5006 0800 - 0x5006 0BFF | RNG                            |

|           | 0x5005 2000 - 0x5005 FFFF | Reserved                       |

|           | 0x5005 1000 - 0x5005 1FFF | JPEG codec                     |

| AHB2      | 0x5005 0000 - 0x5005 03FF | DCMI                           |

| ANDZ      | 0x5004 0000- 0x5004 FFFF  | Reserved                       |

|           | 0x5000 0000 - 0x5003 FFFF | USB OTG FS                     |

# Table 13. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx register boundary addresses<sup>(1)</sup>

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid a current consumption related to floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

#### I/O dynamic current consumption

In addition to the internal peripheral current consumption (see *Table 39: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

$I_{\text{SW}}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

$V_{\text{DD}}$  is the MCU supply voltage

$f_{\mbox{SW}}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

| Symbol            | Parameter     | Conditions                                                                          | I/O toggling<br>frequency (fsw)<br>MHz | Typ<br>V <sub>DD</sub> = 3.3 V | Тур<br>V <sub>DD</sub> = 1.8 V | Unit |

|-------------------|---------------|-------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|------|

|                   |               |                                                                                     | 2                                      | 0.1                            | 0.1                            |      |

|                   |               | C <sub>EXT</sub> = 0 pF<br>C = C <sub>INT</sub> + C <sub>S</sub> + C <sub>EXT</sub> | 8                                      | 0.4                            | 0.2                            |      |

|                   |               |                                                                                     | 25                                     | 1.1                            | 0.7                            |      |

|                   |               |                                                                                     | 50                                     | 2.4                            | 1.3                            |      |

|                   |               |                                                                                     | 60                                     | 3.1                            | 1.6                            |      |

|                   |               |                                                                                     | 84                                     | 4.3                            | 2.4                            |      |

|                   |               |                                                                                     | 90                                     | 4.9                            | 2.6                            |      |

|                   | I/O switching |                                                                                     | 100                                    | 5.4                            | 2.8                            |      |

| I <sub>DDIO</sub> | Current       |                                                                                     | 2                                      | 0.2                            | 0.1                            | mA   |

|                   |               |                                                                                     | 8                                      | 0.6                            | 0.3                            | 1    |

|                   |               |                                                                                     | 25                                     | 1.8                            | 1.1                            |      |

|                   |               | $C_{EXT} = 10 \text{ pF}$                                                           | 50                                     | 3.1                            | 2.3                            |      |

|                   |               | $C = C_{INT} + C_S + C_{EXT}$                                                       | 60                                     | 4.6                            | 3.4                            |      |

|                   |               |                                                                                     | 84                                     | 9.7                            | 3.6                            |      |

|                   |               |                                                                                     | 90                                     | 10.12                          | 5.2                            |      |

|                   |               |                                                                                     | 100                                    | 14.92                          | 5.4                            |      |

#### Table 38. Switching output I/O current consumption<sup>(1)</sup>

| Symbol                                  | Parameter                                    | Conditions                                                             |                    | Min          | Тур  | Max          | Unit |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------|--------------------|--------------|------|--------------|------|

| +                                       | PLLSAI lock time                             | VCO freq = 192 MHz                                                     | 2                  | 75           | -    | 200          |      |

| t <sub>LOCK</sub>                       |                                              | VCO freq = 432 MHz                                                     | 2                  | 100          | -    | 300          | μs   |

|                                         |                                              | Cycle to cycle at                                                      | RMS                | -            | 90   | -            |      |

| Jitter <sup>(3)</sup>                   | Master SAI clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -            | ±280 | -            | ps   |

|                                         |                                              | Average frequency o<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                  | -            | 90   | -            | ps   |

|                                         | FS clock jitter                              | Cycle to cycle at 48 l<br>on 1000 samples                              | KHz                | -            | 400  | -            | ps   |

| I <sub>DD(PLLSAI)</sub> <sup>(4)</sup>  | PLLSAI power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLSAI)</sub> <sup>(4)</sup> | PLLSAI power consumption on $V_{\text{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

Table 49. PLLISAI characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

### 5.3.12 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 61: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup>  | Unit |

|-------------------|-----------------------|------|-----|---------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                  | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                   | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> – 1 | -    |

### Table 50. SSCG parameters constraint

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL\_IN}/(4 \times f_{Mod})]$

$f_{\mathsf{PLL\_IN}}$  and  $f_{\mathsf{Mod}}$  must be expressed in Hz. As an example:

| Symbol                                 | Parameter                          | Conditions | Min | Тур | Мах | Unit |  |

|----------------------------------------|------------------------------------|------------|-----|-----|-----|------|--|

| V <sub>IL</sub>                        | Output low level voltage           | -          | 1.1 | 1.2 | 1.2 | V    |  |

| V <sub>IL-ULPS</sub>                   | Output high level voltage          | -          | -50 | -   | 50  | mV   |  |

| V <sub>IH</sub>                        | Output impedance of LP transmitter | -          | 110 | -   | -   | Ω    |  |

| V <sub>hys</sub>                       | 15%-85% rise and fall time         | -          | -   | -   | 25  | ns   |  |

| LP Contention Detector Characteristics |                                    |            |     |     |     |      |  |

| V <sub>ILCD</sub>                      | Logic 0 contention threshold       | -          | -   | -   | 200 | mV   |  |

| V <sub>IHCD</sub>                      | Logic 0 contention threshold       | -          | 450 | -   | -   |      |  |

|                                        |                                    |            |     |     |     |      |  |

Table 51. MIPI D-PHY characteristics<sup>(1)</sup> (continued)

1. Guaranteed based on test during characterization.

## Table 52. MIPI D-PHY AC characteristics LP mode and HS/LP transitions<sup>(1)</sup>

| Symbol                                                 | Parameter                                                                                                                                            | Conditions | Min | Тур | Max | Unit |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|------|

| T <sub>LPX</sub>                                       | Transmitted length of any Low-<br>Power state period                                                                                                 | -          | 50  | -   | -   |      |

| T <sub>CLK-PREPARE</sub>                               | Time that the transmitter drives<br>the Clock Lane LP-00 Line<br>state immediately before the<br>HS-0 Line state starting the HS<br>transmission.    | -          | 38  | -   | 95  | ns   |

| T <sub>CLK-PREPARE</sub><br>+<br>T <sub>CLK-ZERO</sub> | Time that the transmitter drives<br>the HS-0 state prior to starting<br>the clock.                                                                   | -          | 300 | -   | -   |      |

| T <sub>CLK-PRE</sub>                                   | Time that the HS clock shall be<br>driven by the transmitter prior to<br>any associated Data Lane<br>beginning the transition from<br>LP to HS mode. | -          | 8   | -   | -   | UI   |

- 1. Guaranteed by characterization results.

- 2. Cycling performed over the whole temperature range.

### 5.3.17 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 60*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> =<br>216 MHz, conforms to IEC 61000-<br>4-2 | 2B              |

| V <sub>FTB</sub>  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> =+25 °C, f <sub>HCLK</sub> =<br>168 MHz, conforms to IEC 61000-<br>4-2  | 5A              |

#### Table 60. EMS characteristics

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol P         | Parameter  | Conditions                                                                                      | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit |

|------------------|------------|-------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|------|

|                  |            |                                                                                                 | inequency band              | 8/200 MHz                                        |      |

|                  |            |                                                                                                 | 0.1 to 30 MHz               | 5                                                |      |

|                  |            | V <sub>DD</sub> = 3.6 V, T <sub>A</sub> = 25 °C, TFBGA216 package,                              | 30 to 130 MHz               | 10                                               | dBµV |

|                  |            | conforming to IEC61967-2 ART/L1-cache ON, over-drive ON, all peripheral clocks enabled,         | 130 MHz to 1 GHz            | 18                                               | ubμv |

|                  |            | clock dithering disabled.                                                                       | 1 GHz to 2 GHz              | 10                                               |      |

| 6                | Peak level |                                                                                                 | EMI Level                   | 3.5                                              | -    |

| S <sub>EMI</sub> | reak level |                                                                                                 | 0.1 to 30 MHz               | 2                                                |      |

|                  |            | $V_{DD}$ = 3.6 V, $T_A$ = 25 °C, TFBGA216 package,<br>conforming to IEC61967-2 ART/L1-cache ON, | 30 to 130 MHz               | 9                                                | dBuV |

|                  |            | over-drive ON, all peripheral clocks enabled,                                                   | 130 MHz to 1 GHz            | 14                                               | μομν |

|                  |            | clock dithering enabled.                                                                        | 1 GHz to 2 GHz              | 9                                                |      |

|                  |            |                                                                                                 | EMI Level                   | 3                                                | -    |

#### Table 61. EMI characteristics

#### 5.3.18 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/ESDA/JEDEC JS-001-2012 and ANSI/ESD S5.3.1-2009 standards.

| Symbol                                                                | Parar                                                                | neter                                                                | Conditions                          | Min | Тур | Max | Unit  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------|-----|-----|-----|-------|

|                                                                       | I/O input leaka                                                      | ge current <sup>(4)</sup>                                            | $V_{SS} \leq V_{IN} \leq V_{DD}$    | -   | -   | ±1  |       |

| l <sub>lkg</sub>                                                      | I/O FT input lea                                                     | akage current                                                        | V <sub>IN</sub> = 5 V               | -   | -   | 3   | μA    |

| Weak pull-up<br>R <sub>PU</sub> equivalent<br>resistor <sup>(6)</sup> | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_I<br>D,OTG_HS_<br>ID) | V <sub>IN</sub> = V <sub>SS</sub>                                    | 30                                  | 40  | 50  |     |       |

|                                                                       |                                                                      | PA10/PB12<br>(OTG_FS_I<br>D,OTG_HS_<br>ID)                           | PA10/PB12<br>(OTG_FS_I<br>D,OTG_HS_ | 7   | 10  | 14  | - kΩ  |

| R <sub>PD</sub>                                                       | Weak pull-<br>down<br>equivalent                                     | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_I<br>D,OTG_HS_<br>ID) | <u> </u>                            | 30  | 40  | 50  | - K22 |

|                                                                       | resistor <sup>(7)</sup>                                              | PA10/PB12<br>(OTG_FS_I<br>D,OTG_HS_<br>ID)                           |                                     | 7   | 10  | 14  |       |

| C <sub>IO</sub> <sup>(8)</sup>                                        | I/O pin capacita                                                     | ance                                                                 | -                                   | -   | 5   | -   | pF    |

Table 65. I/O static characteristics (continued)

- 1. Guaranteed by design.

- 2. Tested in production.

- 3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 64: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 64: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT I/Os is shown in *Figure 38*.

1. Guaranteed by characterization results.

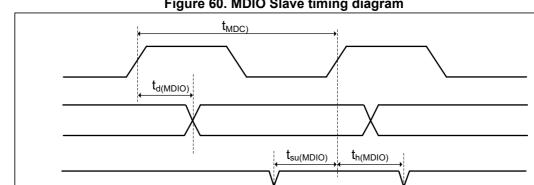

| Table 99. | MDIO | Slave | timina | parameters |

|-----------|------|-------|--------|------------|

|           |      | Oldve | unning | parameters |

| Symbol                | Parameter                                      | Min | Тур | Max | Unit |

|-----------------------|------------------------------------------------|-----|-----|-----|------|

| F <sub>sDC</sub>      | Management Data clock                          | -   | -   | 40  | MHz  |

| t <sub>d(MDIO)</sub>  | Management Data input/output output valid time | 7   | 8   | 20  |      |

| t <sub>su(MDIO)</sub> | Management Data input/output setup time        | 4   | -   | -   | ns   |

| t <sub>h(MDIO)</sub>  | Management Data input/output hold time         | 1   | -   | -   |      |

The MDIO controller is mapped on APB2 domain. The frequency of the APB bus should at least 1.5 times the MDC frequency: F<sub>PCLK2</sub> ≥ 1.5 \* F<sub>MDC</sub>

#### CAN (controller area network) interface

Refer to Section 5.3.20: I/O port characteristics for more details on the input/output alternate function characteristics (CANx\_TX and CANx\_RX).

#### 5.3.30 **FMC** characteristics

Unless otherwise specified, the parameters given in Table 100 to Table 113 for the FMC interface are derived from tests performed under the ambient temperature, f<sub>HCLK</sub> frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

MSv40460V1

Figure 67. Synchronous non-multiplexed NOR/PSRAM read timings

| Symbol                     | Parameter                                  | Min                      | Max | Unit |

|----------------------------|--------------------------------------------|--------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FMC_CLK period                             | 2T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                        | 2   |      |

| t <sub>d(CLKH-NExH)</sub>  | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub> | FMC_CLK low to FMC_NADV low                | -                        | 0.5 |      |

| t <sub>d(CLKL-NADVH)</sub> | FMC_CLK low to FMC_NADV high               | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>    | FMC_CLK low to FMC_Ax valid (x=1625)       | -                        | 2.5 |      |

| t <sub>d(CLKH-AIV)</sub>   | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>        | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>  | FMC_CLK low to FMC_NOE low                 | -                        | 1.5 |      |

| t <sub>d(CLKH-NOEH)</sub>  | FMC_CLK high to FMC_NOE high               | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>su(DV-CLKH)</sub>   | FMC_D[15:0] valid data before FMC_CLK high | 1.5                      | -   |      |

| t <sub>h(CLKH-DV)</sub>    | FMC_D[15:0] valid data after FMC_CLK high  | 3.5                      | -   |      |

| t <sub>(NWAIT-CLKH)</sub>  | FMC_NWAIT valid before FMC_CLK high        | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub> | FMC_NWAIT valid after FMC_CLK high         | 3.5                      | -   |      |

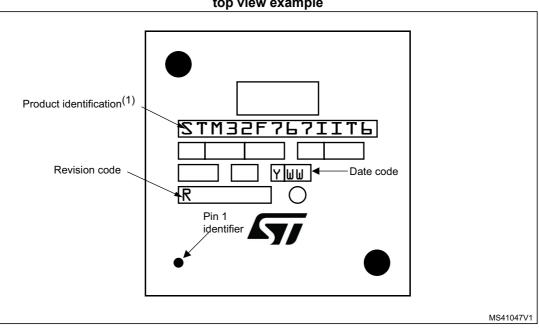

#### LQFP176 device marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 91. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.