Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                        |

| Number of I/O                 | 140                                                                                                      |

| Program Memory Size           | 2MB (2M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | -                                                                                                        |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 176-LQFP                                                                                                 |

| Supplier Device Package       | 176-LQFP (24x24)                                                                                         |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f769iit6e                                   |

|                               |                                                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. The configuration is made by software and the transfer sizes between the source and the destination are independent.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDMMC

- Camera interface (DCMI)

- ADC

- SAI

- SPDIFRX

- Quad-SPI

- HDMI-CEC

- JPEG codec

- DFSDM1

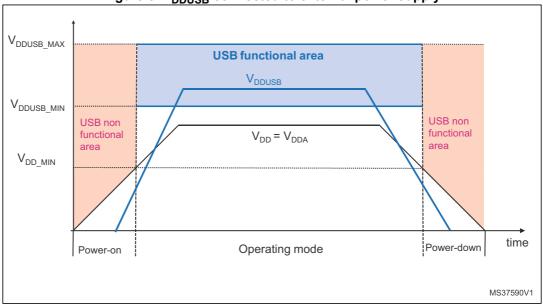

Figure 5. V<sub>DDUSB</sub> connected to external power supply

The DSI (Display Serial Interface) sub-system uses several power supply pins which are independent from the other supply pins:

- V<sub>DDDSI</sub> is an independent DSI power supply dedicated for DSI Regulator and MIPI D-PHY. This supply must be connected to global V<sub>DD</sub>.

- The V<sub>CAPDSI</sub> pin is the output of DSI Regulator (1.2V) which must be connected externally to V<sub>DD12DSI</sub>.

- The V<sub>DD12DSI</sub> pin is used to supply the MIPI D-PHY, and to supply the clock and data lanes pins. An external capacitor of 2.2 uF must be connected on the V<sub>DD12DSI</sub> pin.

- The V<sub>SSDSI</sub> pin is an isolated supply ground used for DSI sub-system.

- If the DSI functionality is not used at all, then:

- The  $V_{DDDSI}$  pin must be connected to global  $V_{DD}$ .

- The V<sub>CAPDSI</sub> pin must be connected externally to V<sub>DD12DSI</sub> but the external capacitor is no more needed.

- The V<sub>SSDSI</sub> pin must be grounded.

# 2.18 Power supply supervisor

## 2.18.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On the other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR thresholds, or to disable BOR permanently. Three BOR thresholds are available through

option bytes. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

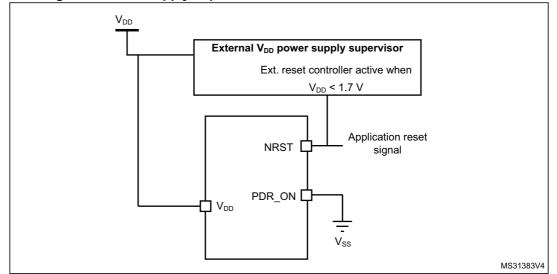

### 2.18.2 Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled through the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and NRST and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to  $V_{SS}$ . Refer to *Figure 6: Power supply supervisor interconnection with internal reset OFF*.

Figure 6. Power supply supervisor interconnection with internal reset OFF

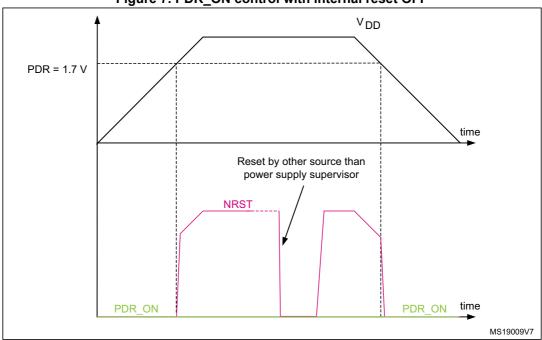

The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.7 V (see *Figure 7*).

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry must be disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>.

All the packages, except for the LQFP100, allow to disable the internal reset through the PDR\_ON signal when connected to  $V_{SS}$ .

Figure 7. PDR\_ON control with internal reset OFF

# 2.19 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low power regulator (LPR)

- Power-down

- Regulator OFF

## 2.19.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep modes

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during stop mode:

MR operates in normal mode (default mode of MR in stop mode)

MR operates in under-drive mode (reduced leakage mode).

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32

The RTC is functional in  $V_{BAT}$  mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in  $V_{BAT}$  mode, but is functional in all low-power modes.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

## 2.21 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup and LPTIM1 asynchronous interrupt).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

#### Table 5. Voltage regulator modes in stop mode

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering

| features <sup>(1)</sup>               | USART1/2/3/6 | UART4/5/7/8 |  |  |  |  |  |  |  |  |  |

|---------------------------------------|--------------|-------------|--|--|--|--|--|--|--|--|--|

| Smartcard mode                        | X            | -           |  |  |  |  |  |  |  |  |  |

| Single-wire half-duplex communication | X            | Х           |  |  |  |  |  |  |  |  |  |

| IrDA SIR ENDEC block                  | X            | Х           |  |  |  |  |  |  |  |  |  |

| LIN mode                              | X            | Х           |  |  |  |  |  |  |  |  |  |

| Dual clock domain                     | X            | Х           |  |  |  |  |  |  |  |  |  |

| Receiver timeout interrupt            | X            | Х           |  |  |  |  |  |  |  |  |  |

| Modbus communication                  | X            | Х           |  |  |  |  |  |  |  |  |  |

| Auto baud rate detection              | X            | х           |  |  |  |  |  |  |  |  |  |

| Driver Enable                         | X            | Х           |  |  |  |  |  |  |  |  |  |

Table 8. USART implementation (continued)

1. X: supported.

# 2.26 Serial peripheral interface (SPI)/inter- integrated sound interfaces (I2S)

The devices feature up to six SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4, SPI5, and SPI6 can communicate at up to 54 Mbits/s, SPI2 and SPI3 can communicate at up to 25 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable from 4 to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation. All the SPIs can be served by the DMA controller.

Three standard  $I^2S$  interfaces (multiplexed with SPI1, SPI2 and SPI3) are available. They can be operated in master or slave mode, in simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

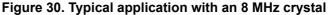

# 2.27 Serial audio interface (SAI)

The devices embed two serial audio interfaces.

The serial audio interface is based on two independent audio subblocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both subblocks can be configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

DocID029041 Rev 4

# 2.44 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- Two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

# 2.45 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 2.46 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F76xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

# 2.47 DSI Host (DSIHOST)

The DSI Host is a dedicated peripheral for interfacing with MIPI<sup>®</sup> DSI compliant displays. It includes a dedicated video interface internally connected to the LTDC and a generic APB interface that can be used to transmit information to the display.

These interfaces are as follows:

- LTDC interface:

- Used to transmit information in Video mode, in which the transfers from the host processor to the peripheral take the form of a real-time pixel stream (DPI).

- Through a customized for mode, this interface can be used to transmit information in full bandwidth in the Adapted Command mode (DBI).

- APB slave interface:

- Allows the transmission of generic information in Command mode, and follows a proprietary register interface.

- Can operate concurrently with either LTDC interface in either Video mode or Adapted Command mode.

- Video mode pattern generator:

- Allows the transmission of horizontal/vertical color bar and D-PHY BER testing pattern without any kind of stimuli.

The DSI Host main features:

- Compliant with MIPI<sup>®</sup> Alliance standards

- Interface with MIPI<sup>®</sup> D-PHY

- Supports all commands defined in the MIPI<sup>®</sup> Alliance specification for DCS:

- Transmission of all Command mode packets through the APB interface

- Transmission of commands in low-power and high-speed during Video mode

- Supports up to two D-PHY data lanes

- Bidirectional communication and escape mode support through data lane 0

- Supports non-continuous clock in D-PHY clock lane for additional power saving

- Supports Ultra Low-power mode with PLL disabled

- ECC and Checksum capabilities

- Support for End of Transmission Packet (EoTp)

- Fault recovery schemes

- 3D transmission support

- Configurable selection of system interfaces:

- AMBA APB for control and optional support for Generic and DCS commands

- Video Mode interface through LTDC

- Adapted Command mode interface through LTDC

- Independently programmable Virtual Channel ID in

- Video mode

- Adapted Command mode

- APB Slave

#### Video Mode interfaces features:

• LTDC interface color coding mappings into 24-bit interface:

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

- Programmable polarity of all LTDC interface signals

- Extended resolutions beyond the DPI standard

- Maximum resolution of 800x480 pixels:

- Maximum resolution is limited by available DSI physical link bandwidth:

- Number of lanes: 2

- Maximum speed per lane: 500 Mbps1Gbps

#### Adapted interface features

Support for sending large amounts of data through the memory\_write\_start(WMS) and memory\_write\_continue(WMC) DCS commands

- LTDC interface color coding mappings into 24-bit interface:

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

#### Video mode pattern generator:

- Vertical and horizontal color bar generation without LTDC stimuli

- BER pattern without LTDC stimuli

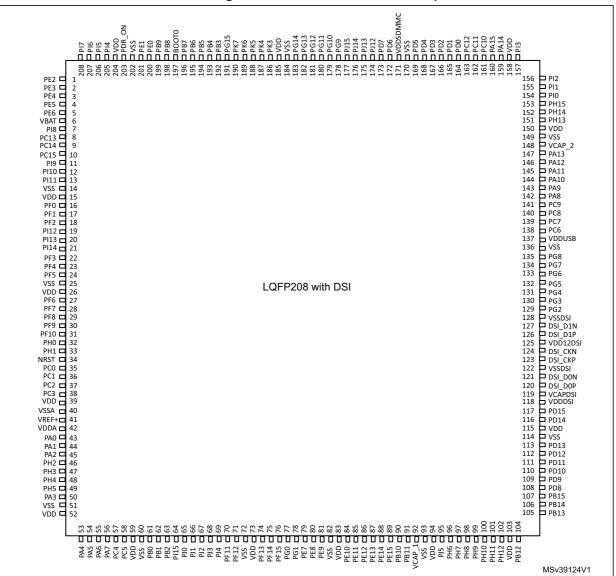

#### Figure 17. STM32F769xx LQFP208 pinout

1. The above figure shows the package top view.

|         |         |              | l       | Pin N   | umbe     | ər                      |             |         |          |                                |          |               | -     |                                                                                                                                                   |                                    |

|---------|---------|--------------|---------|---------|----------|-------------------------|-------------|---------|----------|--------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

|         |         | TM32<br>TM32 |         |         | 1        |                         | M32I<br>M32 |         |          | reset                          |          |               |       |                                                                                                                                                   |                                    |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176     | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                               | Additional<br>functions            |

| 28      | 40      | N4           | 50      | 53      | N4       | L9                      | 50          | 53      | N4       | PA4                            | I/O      | TT<br>a       | -     | SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>USART2_CK, SPI6_NSS,<br>OTG_HS_SOF,<br>DCMI_HSYNC,<br>LCD_VSYNC, EVENTOUT                               | ADC1_IN4,<br>ADC2_IN4,<br>DAC_OUT1 |

| 29      | 41      | P4           | 51      | 54      | P4       | P11                     | 51          | 54      | P4       | PA5                            | I/O      | TT<br>a       | -     | TIM2_CH1/TIM2_ETR,<br>TIM8_CH1N,<br>SPI1_SCK/I2S1_CK,<br>SPI6_SCK,<br>OTG_HS_ULPI_CK,<br>LCD_R4, EVENTOUT                                         | ADC1_IN5,<br>ADC2_IN5,<br>DAC_OUT2 |

| 30      | 42      | P3           | 52      | 55      | P3       | N10                     | 52          | 55      | P3       | PA6                            | I/O      | FT            | -     | TIM1_BKIN, TIM3_CH1,<br>TIM8_BKIN, SPI1_MISO,<br>SPI6_MISO, TIM13_CH1,<br>MDIOS_MDC,<br>DCMI_PIXCLK, LCD_G2,<br>EVENTOUT                          | ADC1_IN6,<br>ADC2_IN6              |

| 31      | 43      | R3           | 53      | 56      | R3       | М9                      | 53          | 56      | R3       | PA7                            | I/O      | FT            | -     | TIM1_CH1N, TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI/I2S1_SD,<br>SPI6_MOSI, TIM14_CH1,<br>ETH_MII_RX_DV/ETH_RM<br>II_CRS_DV,<br>FMC_SDNWE,<br>EVENTOUT | ADC1_IN7,<br>ADC2_IN7              |

| 32      | 44      | N5           | 54      | 57      | N5       | NC                      | 54          | 57      | N5       | PC4                            | I/O      | FT            | -     | DFSDM1_CKIN2,<br>I2S1_MCK, SPDIF_RX2,<br>ETH_MII_RXD0/ETH_RMII<br>_RXD0, FMC_SDNE0,<br>EVENTOUT                                                   | ADC1_IN14,<br>ADC2_IN14            |

| 33      | 45      | P5           | 55      | 58      | P5       | NC                      | 55          | 58      | P5       | PC5                            | I/O      | FT            | -     | DFSDM1_DATIN2,<br>SPDIF_RX3,<br>ETH_MII_RXD1/ETH_RMII<br>_RXD1, FMC_SDCKE0,<br>EVENTOUT                                                           | ADC1_IN15,<br>ADC2_IN15            |

| -       | -       | -            | -       | 59      | L7       | -                       | -           | 59      | L7       | VDD                            | S        | -             | -     | -                                                                                                                                                 | -                                  |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

DocID029041 Rev 4

|         |         |              |         | Pin N   | umbe     | ər                      |         |                |          |                                |          |               | /     |                                                                                                                  |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         | 1        |                         |         | F768/<br>F769: |          | . reset                        |          |               |       |                                                                                                                  |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                              | Additional<br>functions |

| 55      | 77      | P15          | 96      | 108     | L15      | М3                      | 89      | 108            | L15      | PD8                            | I/O      | FT            | -     | DFSDM1_CKIN3,<br>USART3_TX, SPDIF_RX1,<br>FMC_D13, EVENTOUT                                                      | -                       |

| 56      | 78      | P14          | 97      | 109     | L14      | L3                      | 90      | 109            | L14      | PD9                            | I/O      | FT            | -     | DFSDM1_DATIN3,<br>USART3_RX, FMC_D14,<br>EVENTOUT                                                                | -                       |

| 57      | 79      | N15          | 98      | 110     | K15      | M2                      | 91      | 110            | K15      | PD10                           | I/O      | FT            | -     | DFSDM1_CKOUT,<br>USART3_CK, FMC_D15,<br>LCD_B3, EVENTOUT                                                         | -                       |

| 58      | 80      | N14          | 99      | 111     | N10      | K3                      | 92      | 111            | N10      | PD11                           | I/O      | FT            | -     | I2C4_SMBA,<br>USART3_CTS,<br>QUADSPI_BK1_IO0,<br>SAI2_SD_A,<br>FMC_A16/FMC_CLE,<br>EVENTOUT                      | -                       |

| 59      | 81      | N13          | 100     | 112     | M1<br>0  | J4                      | 93      | 112            | M1<br>0  | PD12                           | I/O      | FT            | -     | TIM4_CH1, LPTIM1_IN1,<br>I2C4_SCL, USART3_RTS,<br>QUADSPI_BK1_IO1,<br>SAI2_FS_A,<br>FMC_A17/FMC_ALE,<br>EVENTOUT | -                       |

| 60      | 82      | M15          | 101     | 113     | M11      | L2                      | 94      | 113            | M11      | PD13                           | I/O      | FT            | -     | TIM4_CH2, LPTIM1_OUT,<br>I2C4_SDA,<br>QUADSPI_BK1_IO3,<br>SAI2_SCK_A, FMC_A18,<br>EVENTOUT                       | -                       |

| -       | 83      | -            | 102     | 114     | J10      | M1                      | 95      | 114            | J10      | VSS                            | S        |               | -     | -                                                                                                                | -                       |

| -       | 84      | J13          | 103     | 115     | J11      | -                       | 96      | 115            | J11      | VDD                            | s        |               | -     | -                                                                                                                | -                       |

| 61      | 85      | M14          | 104     | 116     | L12      | L1                      | 97      | 116            | L12      | PD14                           | 1/0      | FT            | -     | TIM4_CH3, UART8_CTS,<br>FMC_D0, EVENTOUT                                                                         | -                       |

| 62      | 86      | L14          | 105     | 117     | К13      | K2                      | 98      | 117            | K13      | PD15                           | 1/0      | FT            | -     | TIM4_CH4, UART8_RTS,<br>FMC_D1, EVENTOUT                                                                         | -                       |

| -       | -       | -            | -       | 118     | K12      | -                       | -       | -              | -        | PJ6                            | I/O      | FT            | -     | LCD_R7, EVENTOUT                                                                                                 | -                       |

| -       | -       | -            | -       | 119     | J12      | -                       | -       | -              | -        | PJ7                            | I/O      | FT            | -     | LCD_G0, EVENTOUT                                                                                                 | -                       |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|         |         |              | l       | Pin N   | umbe     | ər                      |                |         |          |                                |          |               |       |                                                                                                                                 |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|----------------|---------|----------|--------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | FM321<br>FM321 |         |          | . reset                        |          |               |       |                                                                                                                                 |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176        | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                             | Additional<br>functions |

| 88      | 123     | A11          | 151     | 173     | A11      | E7                      | 151            | 173     | A11      | PD7                            | I/O      | FT            | -     | DFSDM1_DATIN4,<br>SPI1_MOSI/I2S1_SD,<br>DFSDM1_CKIN1,<br>USART2_CK, SPDIF_RX0,<br>SDMMC2_CMD,<br>FMC_NE1, EVENTOUT              | -                       |

| -       | -       | -            | -       | 174     | B10      | NC                      | -              | 174     | B10      | PJ12                           | I/O      | FT            | -     | LCD_G3, LCD_B0,<br>EVENTOUT                                                                                                     | -                       |

| -       | -       | -            | -       | 175     | B9       | NC                      | -              | 175     | B9       | PJ13                           | I/O      | FT            | -     | LCD_G4, LCD_B1,<br>EVENTOUT                                                                                                     | -                       |

| -       | -       | -            | -       | 176     | C9       | NC                      | -              | 176     | C9       | PJ14                           | I/O      | FT            | -     | LCD_B2, EVENTOUT                                                                                                                | -                       |

| -       | -       | -            | -       | 177     | D10      | -                       | -              | 177     | D10      | PJ15                           | I/O      | FT            | -     | LCD_B3, EVENTOUT                                                                                                                | -                       |

| -       | 124     | C10          | 152     | 178     | D9       | C6                      | 152            | 178     | D9       | PG9                            | I/O      | FT            | -     | SPI1_MISO, SPDIF_RX3,<br>USART6_RX,<br>QUADSPI_BK2_IO2,<br>SAI2_FS_B, SDMMC2_D0,<br>FMC_NE2/FMC_NCE,<br>DCMI_VSYNC,<br>EVENTOUT | -                       |

| -       | 125     | B10          | 153     | 179     | C8       | A7                      | 153            | 179     | C8       | PG10                           | I/O      | FT            | -     | SPI1_NSS/I2S1_WS,<br>LCD_G3, SAI2_SD_B,<br>SDMMC2_D1, FMC_NE3,<br>DCMI_D2, LCD_B2,<br>EVENTOUT                                  | -                       |

| -       | 126     | В9           | 154     | 180     | B8       | B7                      | 154            | 180     | B8       | PG11                           | I/O      | FT            | -     | SPI1_SCK/I2S1_CK,<br>SPDIF_RX0,<br>SDMMC2_D2,<br>ETH_MII_TX_EN/ETH_RM<br>II_TX_EN, DCMI_D3,<br>LCD_B3, EVENTOUT                 | -                       |

| -       | 127     | B8           | 155     | 181     | C7       | D7                      | 155            | 181     | C7       | PG12                           | I/O      | FT            | -     | LPTIM1_IN1, SPI6_MISO,<br>SPDIF_RX1,<br>USART6_RTS, LCD_B4,<br>SDMMC2_D3, FMC_NE4,<br>LCD_B1, EVENTOUT                          | -                       |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

96/255

# DocID029041 Rev 4

|        |      |        | Та                        | able 12.     | STM32F                                     | 765xx, \$                     |                                                        |                                                                |                                                                                | 768Ax a<br>ntinued                                            |                                                    | 32F769x                                                                | x alterna                    | ate                                            |                  |        |              |

|--------|------|--------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|--------|--------------|

|        |      | AF0    | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             | AF14   | AF15         |

| Po     | ort  | SYS    | I2C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD    | SYS          |

|        | PC11 | -      | -                         | -            | DFSDM1_<br>DATAIN5                         | -                             | -                                                      | SPI3_MI<br>SO                                                  | USART3<br>_RX                                                                  | UART4_<br>RX                                                  | QUADSP<br>I_BK2_N<br>CS                            | -                                                                      | -                            | SDMMC<br>_D3                                   | DCMI_D<br>4      | -      | EVEN<br>TOUT |

|        | PC12 | TRACED | -                         | -            | -                                          | -                             | -                                                      | SPI3_M<br>OSI/I2S3<br>_SD                                      | USART3<br>_CK                                                                  | UART5_T<br>X                                                  | -                                                  | -                                                                      | -                            | SDMMC<br>_CK                                   | DCMI_D<br>9      | -      | EVEN<br>TOUT |

| Port C | PC13 | -      | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PC14 | -      | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PC15 | -      | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PD0  | -      | -                         | -            | DFSDM1_<br>CKIN6                           | -                             | -                                                      | DFSDM1<br>_DATAIN<br>7                                         | -                                                                              | UART4_<br>RX                                                  | CAN1_R<br>X                                        | -                                                                      | -                            | FMC_D2                                         | -                | -      | EVEN<br>TOUT |

|        | PD1  | -      | -                         | -            | DFSDM1_<br>DATAIN6                         | -                             | -                                                      | DFSDM1<br>_CKIN7                                               | -                                                                              | UART4_T<br>X                                                  | CAN1_T<br>X                                        | -                                                                      | -                            | FMC_D3                                         | -                | -      | EVEN<br>TOUT |

|        | PD2  | TRACED | -                         | TIM3_ET<br>R | -                                          | -                             | -                                                      | -                                                              | -                                                                              | UART5_<br>RX                                                  | -                                                  | -                                                                      | -                            | SDMMC<br>_CMD                                  | DCMI_D<br>11     | -      | EVEN<br>TOUT |

| D. (D  | PD3  | -      | -                         | -            | DFSDM1_<br>CKOUT                           | -                             | SPI2_SC<br>K/I2S2_<br>CK                               | DFSDM1<br>_DATAIN<br>0                                         | USART2<br>_CTS                                                                 | -                                                             | -                                                  | -                                                                      | -                            | FMC_CL<br>K                                    | DCMI_D<br>5      | LCD_G7 | EVEN<br>TOUT |

| Port D | PD4  | -      | -                         | -            | -                                          | -                             | -                                                      | DFSDM1<br>_CKIN0                                               | USART2<br>_RTS                                                                 | -                                                             | -                                                  | -                                                                      | -                            | FMC_N<br>OE                                    | -                | -      | EVEN<br>TOUT |

|        | PD5  | -      | -                         | -            | -                                          | -                             | -                                                      | -                                                              | USART2<br>_TX                                                                  | -                                                             | -                                                  | -                                                                      | -                            | FMC_N<br>WE                                    | -                | -      | EVEN<br>TOUT |

|        | PD6  | -      | -                         | -            | DFSDM1_<br>CKIN4                           | -                             | SPI3_M<br>OSI/I2S3<br>_SD                              | SAI1_SD<br>_A                                                  | USART2<br>_RX                                                                  | -                                                             | -                                                  | DFSDM1_<br>DATAIN1                                                     | SDMMC2<br>_CK                | FMC_N<br>WAIT                                  | DCMI_D<br>10     | LCD_B2 | EVEN<br>TOUT |

|        | PD7  | -      | -                         | -            | DFSDM1_<br>DATAIN4                         | -                             | SPI1_M<br>OSI/I2S1<br>_SD                              | DFSDM1<br>_CKIN1                                               | USART2<br>_CK                                                                  | SPDIF_R<br>X0                                                 | -                                                  | -                                                                      | SDMMC2<br>_CMD               | FMC_NE<br>1                                    | -                | -      | EVEN<br>TOUT |

Pinouts and pin description

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

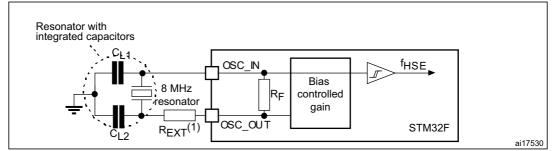

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 30*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . The PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

|                 |                         | inaracteristics (I <sub>LSE</sub> – 52.7       |     | <b>~</b> )`` |     |      |

|-----------------|-------------------------|------------------------------------------------|-----|--------------|-----|------|

| Symbol          | Parameter               | Conditions                                     | Min | Тур          | Мах | Unit |

|                 |                         | LSEDRV[1:0]=00<br>Low drive capability         | -   | 250          | -   |      |

|                 |                         | LSEDRV[1:0]=10<br>Medium low drive capability  | -   | 300          | -   | ~^   |

| I <sub>DD</sub> | LSE current consumption | LSEDRV[1:0]=01<br>Medium high drive capability | -   | 370          | -   | nA   |

|                 |                         | LSEDRV[1:0]=11<br>High drive capability        | -   | 480          | -   |      |

Table 44. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

| Symbol                                  | Parameter                                    | Conditions                                                             |                    | Min                 | Тур  | Max          | Unit |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLLI2S_IN</sub>                  | PLLI2S input clock <sup>(1)</sup>            | -                                                                      |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLLI2SP_OUT</sub>                | PLLI2S multiplier output clock for SPDIFRX   | -                                                                      |                    | -                   | -    | 216          |      |

| f <sub>PLLI2SQ_OUT</sub>                | PLLI2S multiplier output clock for SAI       | -                                                                      |                    | -                   | -    | 216          | MHz  |

| f <sub>PLLI2SR_OUT</sub>                | PLLI2S multiplier output clock for I2S       | -                                                                      |                    | -                   | -    | 216          |      |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                            | -                                                                      |                    | 100                 | -    | 432          |      |

| +                                       | PLLI2S lock time                             | VCO freq = 192 MHz                                                     | 2                  | 75                  | -    | 200          |      |

| t <sub>LOCK</sub>                       |                                              | VCO freq = 432 MHz                                                     | 2                  | 100                 | -    | 300          | μs   |

|                                         |                                              | Cycle to cycle at                                                      | RMS                | -                   | 90   | -            |      |

|                                         | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -                   | ±280 | -            | ps   |

| Jitter <sup>(3)</sup>                   |                                              | Average frequency o<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                  | -                   | 90   | -            | ps   |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 k<br>on 1000 samples                              | КНz                | -                   | 400  | -            | ps   |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on V <sub>DDA</sub> | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 | mA   |

Table 48. PLLI2S characteristics

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

| Symbol                   | Parameter                                     | Conditions | Min                 | Тур | Max  | Unit |

|--------------------------|-----------------------------------------------|------------|---------------------|-----|------|------|

| f <sub>PLLSAI_IN</sub>   | PLLSAI input clock <sup>(1)</sup>             | -          | 0.95 <sup>(2)</sup> | 1   | 2.10 |      |

| fpllsaip_out             | PLLSAI multiplier output clock for 48 MHz     | -          | -                   | 48  | 75   |      |

| fpllsaiq_out             | PLLSAI multiplier output clock<br>for SAI     | -          | -                   | -   | 216  | MHz  |

| f <sub>PLLSAIR_OUT</sub> | PLLSAI multiplier output clock<br>for LCD-TFT | -          | -                   | -   | 216  |      |

| f <sub>VCO_ОUT</sub>     | PLLSAI VCO output                             | -          | 100                 | -   | 432  |      |

|        |                              | <b>7</b> ADV                                                                  |     |                    |      |

|--------|------------------------------|-------------------------------------------------------------------------------|-----|--------------------|------|

| Symbol | Parameter                    | Test conditions                                                               | Тур | Max <sup>(1)</sup> | Unit |

| ET     | Total unadjusted error       |                                                                               | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,                 | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{DDA} = 2.4 \text{ to } 3.6 \text{ V},$<br>V <sub>RFF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                                   | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                               | ±3  | ±6                 |      |

Table 74. ADC static accuracy at f<sub>ADC</sub> = 36 MHz

1. Guaranteed by characterization results.

| Table 75. ADC dynamic accuracy at f <sub>ADC</sub> = 18 MHz - limited test conditions <sup>(1)</sup> |

|------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------|

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     |      | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

#### Table 76. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter Test conditions            |                              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in *Section 5.3.20* does not affect the ADC accuracy.

| Symbol                   | Parameter              | Conditions                                                | Min | Max | Unit |

|--------------------------|------------------------|-----------------------------------------------------------|-----|-----|------|

|                          |                        | Slave transmitter (after enable edge)<br>2.7≤VDD≤3.6V     | -   | 12  |      |

| <sup>t</sup> v(SD_B_ST)  | Data output valid time | Slave transmitter (after enable edge)       1.71≤VDD≤3.6V | 20  |     |      |

| t <sub>h(SD_B_MT)</sub>  | Data output hold time  | Slave transmitter (after enable edge)                     | 5   | -   | 20   |

| t <sub>v(SD_MT)_</sub> A | Data output valid time | Master transmitter (after enable edge)<br>2.7≤VDD≤3.6V    | -   | 15  | ns   |

|                          |                        | Master transmitter (after enable edge)<br>1.71≤VDD≤3.6V   | -   | 20  |      |

| t <sub>h(SD_A_MT)</sub>  | Data output hold time  | Master transmitter (after enable edge) 5 -                |     | -   |      |

## Table 89. SAI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. APB clock frequency must be at least twice SAI clock frequency.

3. With F<sub>S</sub>=192kHz.

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|--------|--------|-------------|--------|-----------------------|--------|--------|

| Symbol | Min    | Тур         | Max    | Min                   | Тур    | Мах    |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.874  |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| D3     | -      | 17.500      | -      | -                     | 0.689  | -      |

| E      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.8740 |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795                | 0.7874 | 0.7953 |

| E3     | -      | 17.500      | -      | -                     | 0.6890 | -      |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |

# Table 126. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

| Symbol           |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|------------------|-------|-------------|-------|--------|-----------------------|--------|--|

| Symbol           | Min   | Тур         | Мах   | Min    | Тур                   | Max    |  |

| A                | 0.525 | 0.555       | 0.585 | 0.0207 | 0.0219                | 0.230  |  |

| A1               | -     | 0.175       | -     | -      | 0.0069                | -      |  |

| A2               | -     | 0.380       | -     | -      | 0.0150                | -      |  |

| A3               | -     | 0.025       | -     | -      | 0.0010                | -      |  |

| b <sup>(2)</sup> | 0.220 | 0.250       | 0.280 | 0.0087 | 0.0098                | 0.0110 |  |

| D                | 5.502 | 5.537       | 5.572 | 0.2166 | 0.2180                | 0.2194 |  |

| E                | 6.060 | 6.095       | 6.130 | 0.2386 | 0.2400                | 0.2413 |  |

| е                | -     | 0.400       | -     | -      | 0.0157                | -      |  |

| e1               | -     | 4.800       | -     | -      | 0.1890                | -      |  |

| e2               | -     | 5.200       | -     | -      | 0.2047                | -      |  |

| F                | -     | 0.368       | -     | -      | 0.0145                | -      |  |

| G                | -     | 0.477       | -     | -      | 0.0188                | -      |  |

| aaa              | -     | 0.110       | -     | -      | 0.0043                | -      |  |

| bbb              | -     | 0.110       | -     | -      | 0.0043                | -      |  |

| ССС              | -     | 0.110       | -     | -      | 0.0043                | -      |  |

| ddd              | -     | 0.050       | -     | -      | 0.0020                | -      |  |

| eee              | -     | 0.050       | -     | -      | 0.0020                | -      |  |

# Table 129. WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scalepackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.