Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                        |

| Number of I/O                 | 140                                                                                                      |

| Program Memory Size           | 2MB (2M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | -                                                                                                        |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 176-LQFP                                                                                                 |

| Supplier Device Package       | 176-LQFP (24x24)                                                                                         |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f769iit6g                                   |

|                               |                                                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

| LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package outline     | 237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| recommended footprint                                                  | 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| top view example                                                       | 240                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package outline                                                        | 241                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package recommended footprint                                          | 243                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WLCSP180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale package |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| top view example                                                       | 244                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

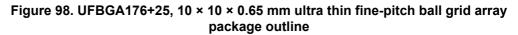

| UFBGA176+25, 10 × 10 × 0.65 mm ultra thin fine-pitch ball grid array   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package outline                                                        | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UFBGA176+25, 10 x 10 mm x 0.65 mm, ultra fine-pitch ball grid array    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package recommended footprint                                          | 246                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| UFBGA 176+25, 10 × 10 × 0.65 mm ultra thin fine-pitch ball grid array  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package top view example                                               | 247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package outline                                                        | 248                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TFBGA216, 13 x 13 mm, 0.8 mm pitch, thin fine-pitch ball grid array    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package recommended footprint                                          | 249                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| package top view example                                               | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                        | LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package<br>recommended footprint.<br>LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package<br>top view example<br>WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale<br>package outline.<br>WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale<br>package recommended footprint<br>WLCSP180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale package<br>top view example<br>UFBGA176+25, 10 × 10 × 0.65 mm ultra thin fine-pitch ball grid array<br>package outline.<br>UFBGA176+25, 10 × 10 mm x 0.65 mm, ultra fine-pitch ball grid array<br>package recommended footprint<br>UFBGA 176+25, 10 × 10 × 0.65 mm ultra thin fine-pitch ball grid array<br>package top view example<br>TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array<br>package outline.<br>TFBGA216, 13 × 13 mm, 0.8 mm pitch, thin fine-pitch ball grid array<br>package recommended footprint |

• LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to *Table 3* for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on V\_{CAP \ 1} and V\_{CAP \ 2} pin.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down<br>mode                | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. '-' means that the corresponding configuration is not available.

2. The over-drive mode is not available when  $V_{DD}$  = 1.7 to 2.1 V.

# 2.19.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In the regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

DocID029041 Rev 4

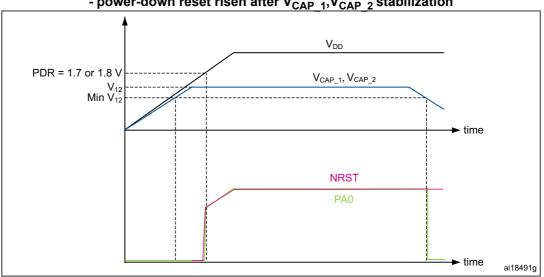

Figure 9. Startup in regulator OFF: slow V<sub>DD</sub> slope - power-down reset risen after V<sub>CAP\_1</sub>, V<sub>CAP\_2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

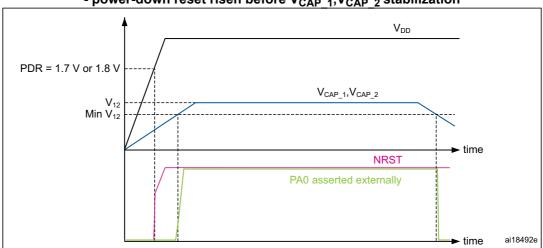

Figure 10. Startup in regulator OFF mode: fast V<sub>DD</sub> slope - power-down reset risen before V<sub>CAP\_1</sub>, V<sub>CAP\_2</sub> stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32

The RTC is functional in  $V_{BAT}$  mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in  $V_{BAT}$  mode, but is functional in all low-power modes.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

# 2.21 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup and LPTIM1 asynchronous interrupt).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

#### Table 5. Voltage regulator modes in stop mode

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering

|         | Pin Number |              |         |         |          |                         |               |         |          |                                |          |               |       |                                                                                  |                         |

|---------|------------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------|-------------------------|

|         |            | TM32<br>TM32 |         |         |          |                         | FM32 <br>FM32 |         |          | reset                          |          |               |       |                                                                                  |                         |

| LQFP100 | LQFP144    | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -       | 51         | M8           | 61      | 72      | K7       | P9                      | 61            | 72      | K7       | VSS                            | S        |               | -     | -                                                                                | -                       |

| -       | 52         | N8           | 62      | 73      | L8       | M8                      | 62            | 73      | L8       | VDD                            | S        |               | -     | -                                                                                | -                       |

| -       | 53         | N6           | 63      | 74      | N6       | L8                      | 63            | 74      | N6       | PF13                           | I/O      | FT            | -     | I2C4_SMBA,<br>DFSDM1_DATIN6,<br>FMC_A7, EVENTOUT                                 | -                       |

| -       | 54         | R7           | 64      | 75      | P6       | K8                      | 64            | 75      | P6       | PF14                           | I/O      | FT            | -     | I2C4_SCL,<br>DFSDM1_CKIN6,<br>FMC_A8, EVENTOUT                                   | -                       |

| -       | 55         | P7           | 65      | 76      | M8       | P8                      | 65            | 76      | M8       | PF15                           | 1/0      | FT            | -     | I2C4_SDA, FMC_A9,<br>EVENTOUT                                                    | -                       |

| -       | 56         | N7           | 66      | 77      | N7       | N8                      | 66            | 77      | N7       | PG0                            | I/O      | FT            | -     | FMC_A10, EVENTOUT                                                                | -                       |

| -       | 57         | M7           | 67      | 78      | M7       | L7                      | 67            | 78      | M7       | PG1                            | I/O      | FT            | -     | FMC_A11, EVENTOUT                                                                | -                       |

| 37      | 58         | R8           | 68      | 79      | R8       | M7                      | 68            | 79      | R8       | PE7                            | I/O      | FT            | -     | TIM1_ETR,<br>DFSDM1_DATIN2,<br>UART7_RX,<br>QUADSPI_BK2_IO0,<br>FMC_D4, EVENTOUT | -                       |

| 38      | 59         | P8           | 69      | 80      | N9       | N7                      | 69            | 80      | N9       | PE8                            | I/O      | FT            | -     | TIM1_CH1N,<br>DFSDM1_CKIN2,<br>UART7_TX,<br>QUADSPI_BK2_IO1,<br>FMC_D5, EVENTOUT | -                       |

| 39      | 60         | P9           | 70      | 81      | P9       | P7                      | 70            | 81      | P9       | PE9                            | I/O      | FT            | -     | TIM1_CH1,<br>DFSDM1_CKOUT,<br>UART7_RTS,<br>QUADSPI_BK2_IO2,<br>FMC_D6, EVENTOUT | -                       |

| -       | 61         | M9           | 71      | 82      | K8       | -                       | 71            | 82      | K8       | VSS                            | S        | -             | -     | -                                                                                | -                       |

| -       | 62         | N9           | 72      | 83      | L9       | -                       | 72            | 83      | L9       | VDD                            | S        | -             | -     | -                                                                                | -                       |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

|         |         |              |         | Pin N   | umbe     | ər                      |         |                |          |                                |          |               | /     |                                                                                                                  |                         |  |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------|-------------------------|--|

|         |         | TM32<br>TM32 |         |         | 1        |                         |         | F768/<br>F769: |          | . reset                        |          |               |       |                                                                                                                  |                         |  |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                              | Additional<br>functions |  |

| 55      | 77      | P15          | 96      | 108     | L15      | М3                      | 89      | 108            | L15      | PD8                            | I/O      | FT            | -     | DFSDM1_CKIN3,<br>USART3_TX, SPDIF_RX1,<br>FMC_D13, EVENTOUT                                                      | -                       |  |

| 56      | 78      | P14          | 97      | 109     | L14      | L3                      | 90      | 109            | L14      | PD9                            | I/O      | FT            | -     | DFSDM1_DATIN3,<br>USART3_RX, FMC_D14,<br>EVENTOUT                                                                | -                       |  |

| 57      | 79      | N15          | 98      | 110     | K15      | M2                      | 91      | 110            | K15      | PD10                           | I/O      | FT            | -     | DFSDM1_CKOUT,<br>USART3_CK, FMC_D15,<br>LCD_B3, EVENTOUT                                                         | -                       |  |

| 58      | 80      | N14          | 99      | 111     | N10      | K3                      | 92      | 111            | N10      | PD11                           | I/O      | FT            | -     | I2C4_SMBA,<br>USART3_CTS,<br>QUADSPI_BK1_IO0,<br>SAI2_SD_A,<br>FMC_A16/FMC_CLE,<br>EVENTOUT                      | -                       |  |

| 59      | 81      | N13          | 100     | 112     | M1<br>0  | J4                      | 93      | 112            | M1<br>0  | PD12                           | I/O      | FT            | -     | TIM4_CH1, LPTIM1_IN1,<br>I2C4_SCL, USART3_RTS,<br>QUADSPI_BK1_IO1,<br>SAI2_FS_A,<br>FMC_A17/FMC_ALE,<br>EVENTOUT | -                       |  |

| 60      | 82      | M15          | 101     | 113     | M11      | L2                      | 94      | 113            | M11      | PD13                           | I/O      | FT            | -     | TIM4_CH2, LPTIM1_OUT,<br>I2C4_SDA,<br>QUADSPI_BK1_IO3,<br>SAI2_SCK_A, FMC_A18,<br>EVENTOUT                       | -                       |  |

| -       | 83      | -            | 102     | 114     | J10      | M1                      | 95      | 114            | J10      | VSS                            | S        |               | -     | -                                                                                                                | -                       |  |

| -       | 84      | J13          | 103     | 115     | J11      | -                       | 96      | 115            | J11      | VDD                            | s        |               | -     | -                                                                                                                | -                       |  |

| 61      | 85      | M14          | 104     | 116     | L12      | L1                      | 97      | 116            | L12      | PD14                           | I/O      | FT            | -     | TIM4_CH3, UART8_CTS,<br>FMC_D0, EVENTOUT                                                                         | -                       |  |

| 62      | 86      | L14          | 105     | 117     | К13      | K2                      | 98      | 117            | K13      | PD15                           | 1/0      | FT            | -     | TIM4_CH4, UART8_RTS,<br>FMC_D1, EVENTOUT                                                                         | -                       |  |

| -       | -       | -            | -       | 118     | K12      | -                       | -       | -              | -        | PJ6                            | I/O      | FT            | -     | LCD_R7, EVENTOUT                                                                                                 | -                       |  |

| -       | -       | -            | -       | 119     | J12      | -                       | -       | -              | -        | PJ7                            | I/O      | FT            | -     | LCD_G0, EVENTOUT                                                                                                 | -                       |  |

# Table 10. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx pin and ball definitions (continued)

| 5 |

|---|

|   |

## Table 12. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx alternate

|        |      |                       |                           |              |                                            |                               | functio                                                | on map                                                         | oing (co                                                                       | ntinued                                                       | )                                                  |                                                                        |                              |                                                |                  |        |              |

|--------|------|-----------------------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|--------|--------------|

|        |      | AF0                   | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             | AF14   | AF15         |

| Po     | ort  | SYS                   | 12C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD    | SYS          |

|        | PA11 | -                     | TIM1_C<br>H4              | -            | -                                          | -                             | SPI2_NS<br>S/I2S2_<br>WS                               | UART4_<br>RX                                                   | USART1<br>_CTS                                                                 | -                                                             | CAN1_R<br>X                                        | OTG_FS_<br>DM                                                          | -                            | -                                              | -                | LCD_R4 | EVEN<br>TOUT |

|        | PA12 | -                     | TIM1_ET<br>R              | -            | -                                          | -                             | SPI2_SC<br>K/I2S2_<br>CK                               | UART4_<br>TX                                                   | USART1<br>_RTS                                                                 | SAI2_FS<br>_B                                                 | CAN1_T<br>X                                        | OTG_FS_<br>DP                                                          | -                            | -                                              | -                | LCD_R5 | EVEN<br>TOUT |

| Port A | PA13 | JTMS-<br>SWDIO        | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PA14 | JTCK-<br>SWCLK        | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -      | EVEN<br>TOUT |

|        | PA15 | JTDI                  | TIM2_C<br>H1/TIM2<br>_ETR | -            | -                                          | HDMI-<br>CEC                  | SPI1_NS<br>S/I2S1_<br>WS                               | SPI3_NS<br>S/I2S3_<br>WS                                       | SPI6_NS<br>S                                                                   | UART4_<br>RTS                                                 | -                                                  | -                                                                      | CAN3_TX                      | UART7_<br>TX                                   | -                | -      | EVEN<br>TOUT |

|        | PB0  | -                     | TIM1_C<br>H2N             | TIM3_C<br>H3 | TIM8_CH<br>2N                              | -                             | -                                                      | DFSDM1<br>_CKOUT                                               | -                                                                              | UART4_<br>CTS                                                 | LCD_R3                                             | OTG_HS_<br>ULPI_D1                                                     | ETH_MII_<br>RXD2             | -                                              | -                | LCD_G1 | EVEN<br>TOUT |

|        | PB1  | -                     | TIM1_C<br>H3N             | TIM3_C<br>H4 | TIM8_CH<br>3N                              | -                             | -                                                      | DFSDM1<br>_DATIN1                                              | -                                                                              | -                                                             | LCD_R6                                             | OTG_HS_<br>ULPI_D2                                                     | ETH_MII_<br>RXD3             | -                                              | -                | LCD_G0 | EVEN<br>TOUT |

|        | PB2  | -                     | -                         | -            | -                                          | -                             | -                                                      | SAI1_SD<br>_A                                                  | SPI3_MO<br>SI/I2S3_<br>SD                                                      |                                                               | QUADSP<br>I_CLK                                    | DFSDM1_<br>CKIN1                                                       | -                            | -                                              | -                | -      | EVEN<br>TOUT |

| Port B | PB3  | JTDO/T<br>RACES<br>WO | TIM2_C<br>H2              | -            | -                                          | -                             | SPI1_SC<br>K/I2S1_<br>CK                               | SPI3_SC<br>K/I2S3_<br>CK                                       | -                                                                              | SPI6_SC<br>K                                                  | -                                                  | SDMMC2<br>_D2                                                          | CAN3_R<br>X                  | UART7_<br>RX                                   | -                | -      | EVEN<br>TOUT |

|        | PB4  | NJTRST                | -                         | TIM3_C<br>H1 | -                                          | -                             | SPI1_MI<br>SO                                          | SPI3_MI<br>SO                                                  | SPI2_NS<br>S/I2S2_<br>WS                                                       | SPI6_MI<br>SO                                                 | -                                                  | SDMMC2<br>_D3                                                          | CAN3_TX                      | UART7_<br>TX                                   | -                | -      | EVEN<br>TOUT |

|        | PB5  | -                     | UART5_<br>RX              | TIM3_C<br>H2 | -                                          | I2C1_SM<br>BA                 | SPI1_M<br>OSI/I2S1<br>_SD                              | SPI3_M<br>OSI/I2S3<br>_SD                                      | -                                                                              | SPI6_MO<br>SI                                                 | CAN2_R<br>X                                        | OTG_HS_<br>ULPI_D7                                                     | ETH_PPS<br>_OUT              | FMC_SD<br>CKE1                                 | DCMI_D<br>10     | LCD_G7 | EVEN<br>TOUT |

|        | PB6  | -                     | UART5_<br>TX              | TIM4_C<br>H1 | HDMI-<br>CEC                               | I2C1_SC<br>L                  | -                                                      | DFSDM1<br>_DATIN5                                              | USART1<br>_TX                                                                  | -                                                             | CAN2_T<br>X                                        | QUADSPI<br>_BK1_NC<br>S                                                | I2C4_SC<br>L                 | FMC_SD<br>NE1                                  | DCMI_D<br>5      | -      | EVEN<br>TOUT |

STM32F765xx STM32F767xx STM32F768Ax STM32F769xx

Pinouts and pin description

93/255

DocID029041 Rev 4

# Table 30. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (Dual bank mode) on ITCM interface (ART disabled), regulator ON

| Cumhal          | Demonster                        | Conditions                                   | £ (8411-)                   | True |           | Max <sup>(1)</sup> |           | Unit |  |

|-----------------|----------------------------------|----------------------------------------------|-----------------------------|------|-----------|--------------------|-----------|------|--|

| Symbol          | Parameter                        | Conditions                                   | f <sub>HCLK</sub> (MHz) Тур |      | TA= 25 °C | TA=85 °C           | TA=105 °C |      |  |

|                 |                                  |                                              | 216                         | 191  | 218       | 255                | -         |      |  |

|                 |                                  |                                              | 200                         | 178  | 195       | 241                | 269       |      |  |

|                 |                                  |                                              | 180                         | 164  | 179       | 214                | 236       |      |  |

|                 |                                  | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                         | 147  | 160       | 192                | 212       |      |  |

|                 | Supply<br>current in<br>RUN mode | chabled                                      | 144                         | 121  | 130       | 157                | 175       |      |  |

|                 |                                  |                                              | 60                          | 60   | 66        | 93                 | 111       | mA   |  |

|                 |                                  |                                              | 25                          | 28   | 33        | 59                 | 77        |      |  |

| I <sub>DD</sub> |                                  |                                              | 216                         | 93   | 104       | 150                | -         |      |  |

|                 |                                  |                                              | 200                         | 87   | 97        | 144                | 171       |      |  |

|                 |                                  |                                              | 180                         | 83   | 92        | 126                | 148       |      |  |

|                 |                                  | All peripherals disabled <sup>(3)</sup>      | 168                         | 75   | 82        | 114                | 134       |      |  |

|                 |                                  | disubled                                     | 144                         | 65   | 71        | 97                 | 115       |      |  |

|                 |                                  |                                              | 60                          | 35   | 40        | 66                 | 84        |      |  |

|                 |                                  |                                              | 25                          | 16   | 20        | 47                 | 64        |      |  |

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

|        |                                            |                                                                 |                             | Тур                         |                             |                       | x <sup>(2)</sup>       |      |  |  |

|--------|--------------------------------------------|-----------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------|------------------------|------|--|--|

| Symbol | Parameter                                  | Conditions <sup>(1)</sup>                                       | ٦                           | ۲ <sub>A</sub> =25 °(       | <b>C</b>                    | T <sub>A</sub> =85 °C | T <sub>A</sub> =105 °C | Unit |  |  |

|        |                                            |                                                                 | V <sub>BAT</sub> =<br>1.7 V | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub> =<br>3.3 V | V <sub>BAT</sub> =    | = 3.6 V                |      |  |  |

|        |                                            | Backup SRAM OFF, RTC and LSE OFF                                | 0.03                        | 0.04                        | 0.04                        | 0.2                   | 0.4                    |      |  |  |

|        |                                            | Backup SRAM ON, RTC and LSE OFF                                 | 0.77                        | 0.78                        | 0.83                        | 3.2                   | 7.4                    |      |  |  |

|        | Supply current<br>in V <sub>BAT</sub> mode | Backup SRAM OFF, RTC ON<br>and LSE in low drive mode            | 0.62                        | 0.8                         | 1.13                        | 4.4                   | 10.2                   |      |  |  |

|        |                                            | Backup SRAM OFF, RTC ON<br>and LSE in medium low drive<br>mode  | 0.65                        | 0.83                        | 1.17                        | 4.6                   | 10.6                   |      |  |  |

|        |                                            | Backup SRAM OFF, RTC ON<br>and LSE in medium high drive<br>mode | 0.75                        | 0.94                        | 1.28                        | 5.0                   | 11.4                   | μA   |  |  |

|        |                                            | Backup SRAM OFF, RTC ON<br>and LSE in high drive mode           | 0.9                         | 1.08                        | 1.43                        | 5.5                   | 12.8                   |      |  |  |

|        |                                            | Backup SRAM ON, RTC ON and LSE in low drive mode                | 1.35                        | 1.54                        | 1.91                        | 7.3                   | 17.2                   |      |  |  |

|        |                                            | Backup SRAM ON, RTC ON and LSE in Medium low drive mode         | 1.38                        | 1.57                        | 1.93                        | 7.9                   | 18.4                   |      |  |  |

|        |                                            | Backup SRAM ON, RTC ON and LSE in Medium high drive mode        | 1.53                        | 1.73                        | 2.11                        | 8.0                   | 18.7                   |      |  |  |

|        |                                            | Backup SRAM ON, RTC ON and LSE in High drive mode               | 1.67                        | 1.87                        | 2.26                        | 9.0                   | 21.0                   |      |  |  |

Table 37. Typical and maximum current consumptions in V<sub>BAT</sub> mode

1. Crystal used: Abracon ABS07-120-32.768 kHz-T with a  $\rm C_L$  of 6 pF for typical values.

2. Guaranteed by characterization results.

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate a current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 65: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

An additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

| Symbol | Parameter     | Conditions                                                 | I/O toggling<br>frequency (fsw)<br>MHz | Typ<br>V <sub>DD</sub> = 3.3 V | Typ<br>V <sub>DD</sub> = 1.8 V | Unit |

|--------|---------------|------------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|------|

|        |               |                                                            | 2                                      | 0.3                            | 0.1                            |      |

|        |               |                                                            | 8                                      | 1.0                            | 0.5                            | ]    |

|        |               |                                                            | 25                                     | 3.5                            | 1.6                            |      |

|        |               | $C_{EXT} = 22 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$ | 50                                     | 5.9                            | 4.2                            | - mA |

|        |               |                                                            | 60                                     | 10.0                           | 4.4                            |      |

|        | I/O switching |                                                            | 84                                     | 19.12                          | 5.8                            |      |

| IDDIO  | Current       |                                                            | 90                                     | 19.6                           | -                              |      |

|        |               |                                                            | 2                                      | 0.3                            | 0.2                            |      |

|        |               |                                                            | 8                                      | 1.3                            | 0.7                            |      |

|        |               | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$ | 25                                     | 3.5                            | 2.3                            |      |

|        |               |                                                            | 50                                     | 10.26                          | 5.19                           |      |

|        |               |                                                            | 60                                     | 16.53                          | -                              | 1    |

1. CINT +  $C_{S_1}$  PCB board capacitance including the pad pin is estimated to15 pF.

# On-chip peripheral current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- I/O compensation cell enabled.

- The ART/L1-cache is ON.

- Scale 1 mode selected, internal digital voltage V12 = 1.32 V.

- HCLK is the system clock. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- f<sub>HCLK</sub> = 216 MHz (Scale 1 + over-drive ON), f<sub>HCLK</sub> = 168 MHz (Scale 2), f<sub>HCLK</sub> = 144 MHz (Scale 3)

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

|                    |                                                    | 55. Peripiteral  |                  |                  |            |

|--------------------|----------------------------------------------------|------------------|------------------|------------------|------------|

| •                  | Peripheral                                         | Scale 1          | Scale 2          | Scale 3          | Unit       |

|                    | GPIOA                                              | 2.9              | 2.8              | 2.2              |            |

|                    | GPIOB                                              | 3.0              | 2.9              | 2.2              |            |

|                    | GPIOC                                              | 2.9              | 2.8              | 2.2              |            |

|                    | GPIOD                                              | 3.1              | 3.0              | 2.3              |            |

|                    | GPIOE                                              | 3.1              | 3.0              | 2.3              |            |

|                    | GPIOF                                              | 2.9              | 2.8              | 2.2              |            |

|                    | GPIOG                                              | 2.9              | 2.8              | 2.2              |            |

|                    | GPIOH                                              | 3.1              | 3.1              | 2.4              |            |

|                    | GPIOI                                              | 3.0              | 2.9              | 2.2              |            |

| AHB1               | GPIOJ                                              | 2.9              | 2.9              | 2.2              |            |

| (up to             | GPIOK                                              | 2.8              | 2.8              | 2.4              | µA/MHz     |

| 216 MHz)           | CRC                                                | 1.0              | 0.9              | 0.8              |            |

|                    | BKPSRAM                                            | 0.9              | 0.9              | 0.7              |            |

|                    | DMA1                                               | 3.17 x N + 11.63 | 3.08 x N + 11.39 | 2.6 x N + 9.64   |            |

|                    | DMA2                                               | 3.33 x N + 12.84 | 3.27 x N + 11.84 | 2.75 x N + 10.10 |            |

|                    | DMA2D                                              | 77.7             | 76.3             | 63.5             |            |

|                    | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 40.1             | 39.5             | 32.8             |            |

|                    | OTG_HS                                             | 58.5             | 57.4             | 48.1             |            |

|                    | OTG_HS+ULPI                                        | 58.5             | 57.4             | 48.1             |            |

|                    | DCMI                                               | 2.9              | 2.8              | 2.1              |            |

| AHB2               | JPEG                                               | 74.8             | 73.4             | 61.9             |            |

| (up to             | RNG                                                | 6.7              | 6.7              | 5.4              | µA/MHz     |

| 216 MHz)           | USB_OTG_FS                                         | 32.4             | 31.9             | 26.7             | μΑντίντητε |

| AHB3               | FMC                                                | 18.6             | 18.2             | 15.1             | µA/MHz     |

| (up to<br>216 MHz) | QSPI                                               | 22.3             | 21.8             | 18.1             |            |

| В                  | us matrix <sup>(2)</sup>                           | 3.94             | 3.25             | 2.12             | µA/MHz     |

Table 39. Peripheral current consumption

|          |                          |         | It consumption<br>I <sub>DD</sub> (Typ) <sup>(1)</sup> | ()      |        |

|----------|--------------------------|---------|--------------------------------------------------------|---------|--------|

| F        | Peripheral               | Scale 1 | Scale 2                                                | Scale 3 | Unit   |

|          | TIM1                     | 24.1    | 23.8                                                   | 19.6    |        |

|          | TIM8                     | 24.5    | 24.2                                                   | 20.0    |        |

|          | USART1                   | 17.7    | 17.4                                                   | 14.3    |        |

|          | USART6                   | 11.9    | 11.8                                                   | 9.4     |        |

|          | ADC1 <sup>(5)</sup>      | 4.5     | 4.7                                                    | 3.5     |        |

|          | ADC2 <sup>(5)</sup>      | 4.5     | 4.7                                                    | 3.3     |        |

|          | ADC3 <sup>(5)</sup>      | 4.5     | 4.6                                                    | 3.3     |        |

|          | SDMMC1                   | 8.4     | 8.3                                                    | 6.9     |        |

|          | SDMMC2                   | 8.2     | 8.2                                                    | 6.4     |        |

|          | SPI1/I2S1 <sup>(3)</sup> | 3.9     | 3.6                                                    | 3.1     |        |

| APB2     | SPI4                     | 3.9     | 3.6                                                    | 3.1     |        |

| (up to   | SYSCFG                   | 2.5     | 2.2                                                    | 1.9     | µA/MHz |

| 108 MHz) | TIM9                     | 8.0     | 8.0                                                    | 6.2     |        |

|          | TIM10                    | 5.0     | 5.1                                                    | 3.7     |        |

|          | TIM11                    | 6.9     | 6.9                                                    | 5.3     |        |

|          | SPI5                     | 2.7     | 2.8                                                    | 1.8     |        |

|          | SPI6                     | 3.1     | 3.2                                                    | 2.2     |        |

|          | SAI1                     | 3.2     | 3.3                                                    | 2.2     |        |

|          | DFSDM1                   | 10.9    | 10.7                                                   | 9.0     |        |

|          | SAI2                     | 3.9     | 3.9                                                    | 2.8     |        |

|          | MDIO                     | 7.1     | 7.0                                                    | 5.8     |        |

|          | LTDC                     | 51.2    | 50.3                                                   | 41.8    |        |

|          | DSI                      | 8.5     | 8.4                                                    | 8.1     |        |

Table 39. Peripheral current consumption (continued)

1. When the I/O compensation cell  $\,$  is ON,  $\rm I_{DD}$  typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.75 mA per DAC channel for the analog part.

5. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Symbol                                     | Parameter                                           | Conditions                     | Min                | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|--------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |