Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Details                       |                                                                                                                       |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                                |

| Core Processor                | ARM® Cortex®-M7                                                                                                       |

| Core Size                     | 32-Bit Single-Core                                                                                                    |

| Speed                         | 216MHz                                                                                                                |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                                     |

| Number of I/O                 | 168                                                                                                                   |

| Program Memory Size           | 1MB (1M x 8)                                                                                                          |

| Program Memory Type           | FLASH                                                                                                                 |

| EEPROM Size                   | -                                                                                                                     |

| RAM Size                      | 512K x 8                                                                                                              |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                                           |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                                 |

| Oscillator Type               | Internal                                                                                                              |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                                     |

| Mounting Type                 | Surface Mount                                                                                                         |

| Package / Case                | 216-TFBGA                                                                                                             |

| Supplier Device Package       | 216-TFBGA (13x13)                                                                                                     |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f769ngh6                                                 |

|                               |                                                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The devices embed two dedicated PLL (PLLI2S and PLLSAI) which allow to achieve audio class performance. In this case, the I<sup>2</sup>S and SAI master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

### 2.16 Boot modes

At startup, the boot memory space is selected by the BOOT pin and BOOT\_ADDx option bytes, allowing to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF which includes:

- All Flash address space mapped on ITCM or AXIM interface

- All RAM address space: ITCM, DTCM RAMs and SRAMs mapped on AXIM interface

- The System memory bootloader

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface. Refer to *STM32 microcontroller system memory boot mode* application note (AN2606) for details.

### 2.17 Power supply schemes

- V<sub>DD</sub> = 1.7 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Note: V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.18.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

- $V_{\text{DDSDMMC}}$  can be connected either to  $V_{\text{DD}}$  or an external independent power supply (1.8 to 3.6V) for SDMMC2 pins (clock, command, and 4-bit data). For example, when the device is powered at 1.8V, an independent power supply 2.7V can be connected to  $V_{\text{DDSDMMC}}$ . When the  $V_{\text{DDSDMMC}}$  is connected to a separated power supply, it is independent from  $V_{\text{DD}}$  or  $V_{\text{DDA}}$  but it must be the last supply to be provided and the first to disappear. The following conditions  $V_{\text{DDSDMMC}}$  must be respected:

- During the power-on phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDSDMMC}$  should be always lower than  $V_{DD}$

- During the power-down phase (V<sub>DD</sub> < V<sub>DD\_MIN</sub>), V<sub>DDSDMMC</sub> should be always lower than V<sub>DD</sub>

- The V<sub>DDSDMMC</sub> rising and falling time rate specifications must be respected (see Table 20 and Table 21)

- In operating mode phase, V<sub>DDSDMMC</sub> could be lower or higher than V<sub>DD</sub>: All associated GPIOs powered by V<sub>DDSDMMC</sub> are operating between V<sub>DDSDMMC\_MIN</sub> and V<sub>DDSDMMC\_MAX</sub>.

- V<sub>DDUSB</sub> can be connected either to V<sub>DD</sub> or an external independent power supply (3.0 to 3.6V) for USB transceivers (refer to *Figure 4* and *Figure 5*). For example, when the device is powered at 1.8V, an independent power supply 3.3V can be connected to V<sub>DDUSB</sub>. When the V<sub>DDUSB</sub> is connected to a separated power supply, it is independent from V<sub>DD</sub> or V<sub>DDA</sub> but it must be the last supply to be provided and the first to

### 2.31 SD/SDIO/MMC card host interface (SDMMC)

SDMMC host interfaces are available, that support the MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 50 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDMMC Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDMMC/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

The SDMMC can be served by the DMA controller

# 2.32 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

- Programmable polarity of all LTDC interface signals

- Extended resolutions beyond the DPI standard

- Maximum resolution of 800x480 pixels:

- Maximum resolution is limited by available DSI physical link bandwidth:

- Number of lanes: 2

- Maximum speed per lane: 500 Mbps1Gbps

#### Adapted interface features

Support for sending large amounts of data through the memory\_write\_start(WMS) and memory\_write\_continue(WMC) DCS commands

- LTDC interface color coding mappings into 24-bit interface:

- 16-bit RGB, configurations 1, 2, and 3

- 18-bit RGB, configurations 1 and 2

- 24-bit RGB

#### Video mode pattern generator:

- Vertical and horizontal color bar generation without LTDC stimuli

- BER pattern without LTDC stimuli

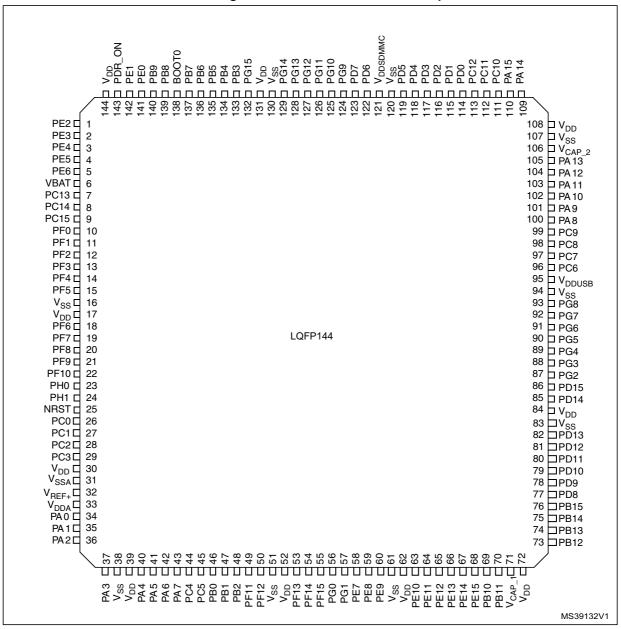

Figure 12. STM32F76xxx LQFP144 pinout

1. The above figure shows the package top view.

|         |         |              | I       | Pin N   | umbe     | er                      |               |         |          |                                |          |               | ,     |                                                                                  |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | FM32 <br>FM32 |         |          | reset                          |          |               |       |                                                                                  |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -       | 51      | M8           | 61      | 72      | K7       | P9                      | 61            | 72      | K7       | VSS                            | S        |               | -     | -                                                                                | -                       |

| -       | 52      | N8           | 62      | 73      | L8       | M8                      | 62            | 73      | L8       | VDD                            | S        |               | -     | -                                                                                | -                       |

| -       | 53      | N6           | 63      | 74      | N6       | L8                      | 63            | 74      | N6       | PF13                           | I/O      | FT            | -     | I2C4_SMBA,<br>DFSDM1_DATIN6,<br>FMC_A7, EVENTOUT                                 | -                       |

| -       | 54      | R7           | 64      | 75      | P6       | K8                      | 64            | 75      | P6       | PF14                           | I/O      | FT            | -     | I2C4_SCL,<br>DFSDM1_CKIN6,<br>FMC_A8, EVENTOUT                                   | -                       |

| -       | 55      | P7           | 65      | 76      | M8       | P8                      | 65            | 76      | M8       | PF15                           | 1/0      | FT            | -     | I2C4_SDA, FMC_A9,<br>EVENTOUT                                                    | -                       |

| -       | 56      | N7           | 66      | 77      | N7       | N8                      | 66            | 77      | N7       | PG0                            | I/O      | FT            | -     | FMC_A10, EVENTOUT                                                                | -                       |

| -       | 57      | M7           | 67      | 78      | M7       | L7                      | 67            | 78      | M7       | PG1                            | I/O      | FT            | -     | FMC_A11, EVENTOUT                                                                | -                       |

| 37      | 58      | R8           | 68      | 79      | R8       | M7                      | 68            | 79      | R8       | PE7                            | I/O      | FT            | -     | TIM1_ETR,<br>DFSDM1_DATIN2,<br>UART7_RX,<br>QUADSPI_BK2_IO0,<br>FMC_D4, EVENTOUT | -                       |

| 38      | 59      | P8           | 69      | 80      | N9       | N7                      | 69            | 80      | N9       | PE8                            | I/O      | FT            | -     | TIM1_CH1N,<br>DFSDM1_CKIN2,<br>UART7_TX,<br>QUADSPI_BK2_IO1,<br>FMC_D5, EVENTOUT | -                       |

| 39      | 60      | P9           | 70      | 81      | P9       | P7                      | 70            | 81      | P9       | PE9                            | I/O      | FT            | -     | TIM1_CH1,<br>DFSDM1_CKOUT,<br>UART7_RTS,<br>QUADSPI_BK2_IO2,<br>FMC_D6, EVENTOUT | -                       |

| -       | 61      | M9           | 71      | 82      | K8       | -                       | 71            | 82      | K8       | VSS                            | S        | -             | -     | -                                                                                | -                       |

| -       | 62      | N9           | 72      | 83      | L9       | -                       | 72            | 83      | L9       | VDD                            | S        | -             | -     | -                                                                                | -                       |

|         |         |              |         | Pin N   | umbe     | ər                      |         |                |          |                                |          |               | /     |                                                                                                                  |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         | 1        |                         |         | F768/<br>F769: |          | . reset                        |          |               |       |                                                                                                                  |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                              | Additional<br>functions |

| 55      | 77      | P15          | 96      | 108     | L15      | М3                      | 89      | 108            | L15      | PD8                            | I/O      | FT            | -     | DFSDM1_CKIN3,<br>USART3_TX, SPDIF_RX1,<br>FMC_D13, EVENTOUT                                                      | -                       |

| 56      | 78      | P14          | 97      | 109     | L14      | L3                      | 90      | 109            | L14      | PD9                            | I/O      | FT            | -     | DFSDM1_DATIN3,<br>USART3_RX, FMC_D14,<br>EVENTOUT                                                                | -                       |

| 57      | 79      | N15          | 98      | 110     | K15      | M2                      | 91      | 110            | K15      | PD10                           | I/O      | FT            | -     | DFSDM1_CKOUT,<br>USART3_CK, FMC_D15,<br>LCD_B3, EVENTOUT                                                         | -                       |

| 58      | 80      | N14          | 99      | 111     | N10      | K3                      | 92      | 111            | N10      | PD11                           | I/O      | FT            | -     | I2C4_SMBA,<br>USART3_CTS,<br>QUADSPI_BK1_IO0,<br>SAI2_SD_A,<br>FMC_A16/FMC_CLE,<br>EVENTOUT                      | -                       |

| 59      | 81      | N13          | 100     | 112     | M1<br>0  | J4                      | 93      | 112            | M1<br>0  | PD12                           | I/O      | FT            | -     | TIM4_CH1, LPTIM1_IN1,<br>I2C4_SCL, USART3_RTS,<br>QUADSPI_BK1_IO1,<br>SAI2_FS_A,<br>FMC_A17/FMC_ALE,<br>EVENTOUT | -                       |

| 60      | 82      | M15          | 101     | 113     | M11      | L2                      | 94      | 113            | M11      | PD13                           | I/O      | FT            | -     | TIM4_CH2, LPTIM1_OUT,<br>I2C4_SDA,<br>QUADSPI_BK1_IO3,<br>SAI2_SCK_A, FMC_A18,<br>EVENTOUT                       | -                       |

| -       | 83      | -            | 102     | 114     | J10      | M1                      | 95      | 114            | J10      | VSS                            | S        |               | -     | -                                                                                                                | -                       |

| -       | 84      | J13          | 103     | 115     | J11      | -                       | 96      | 115            | J11      | VDD                            | s        |               | -     | -                                                                                                                | -                       |

| 61      | 85      | M14          | 104     | 116     | L12      | L1                      | 97      | 116            | L12      | PD14                           | I/O      | FT            | -     | TIM4_CH3, UART8_CTS,<br>FMC_D0, EVENTOUT                                                                         | -                       |

| 62      | 86      | L14          | 105     | 117     | К13      | K2                      | 98      | 117            | K13      | PD15                           | 1/0      | FT            | -     | TIM4_CH4, UART8_RTS,<br>FMC_D1, EVENTOUT                                                                         | -                       |

| -       | -       | -            | -       | 118     | K12      | -                       | -       | -              | -        | PJ6                            | I/O      | FT            | -     | LCD_R7, EVENTOUT                                                                                                 | -                       |

| -       | -       | -            | -       | 119     | J12      | -                       | -       | -              | -        | PJ7                            | I/O      | FT            | -     | LCD_G0, EVENTOUT                                                                                                 | -                       |

|         |         |              | I       | Pin N   | umbe     | ər                      |               |         |          |                                |          |               |       |                                                                                                                                           |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | FM321<br>FM32 |         |          | reset                          |          |               |       |                                                                                                                                           |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                       | Additional<br>functions |

| -       | 89      | K14          | 108     | 131     | N12      | G1                      | 112           | 131     | N12      | PG4                            | I/O      | FT            | -     | FMC_A14/FMC_BA0,<br>EVENTOUT                                                                                                              | -                       |

| -       | 90      | K13          | 109     | 132     | N11      | G2                      | 113           | 132     | N11      | PG5                            | I/O      | FT            | -     | FMC_A15/FMC_BA1,<br>EVENTOUT                                                                                                              | -                       |

| -       | 91      | J15          | 110     | 133     | J15      | G3                      | 114           | 133     | J15      | PG6                            | 1/0      | FT            | -     | FMC_NE3, DCMI_D12,<br>LCD_R7, EVENTOUT                                                                                                    | -                       |

| -       | 92      | J14          | 111     | 134     | J14      | G4                      | 115           | 134     | J14      | PG7                            | I/O      | FT            | -     | SAI1_MCLK_A,<br>USART6_CK, FMC_INT,<br>DCMI_D13, LCD_CLK,<br>EVENTOUT                                                                     | -                       |

| -       | 93      | H14          | 112     | 135     | H14      | G5                      | 116           | 135     | H14      | PG8                            | I/O      | FT            | -     | SPI6_NSS, SPDIF_RX2,<br>USART6_RTS,<br>ETH_PPS_OUT,<br>FMC_SDCLK, LCD_G7,<br>EVENTOUT                                                     | -                       |

| -       | 94      | G12          | 113     | 136     | G10      | F1                      | 117           | 136     | G10      | VSS                            | S        |               | -     | -                                                                                                                                         | -                       |

| -       | 95      | H13          | 114     | 137     | G11      | F2                      | 118           | 137     | G11      | VDDUSB                         | S        |               | -     | -                                                                                                                                         | -                       |

| 63      | 96      | H15          | 115     | 138     | H15      | G6                      | 119           | 138     | H15      | PC6                            | I/O      | FT            | -     | TIM3_CH1, TIM8_CH1,<br>I2S2_MCK,<br>DFSDM1_CKIN3,<br>USART6_TX,<br>FMC_NWAIT,<br>SDMMC2_D6,<br>SDMMC1_D6, DCMI_D0,<br>LCD_HSYNC, EVENTOUT | -                       |

| 64      | 97      | G15          | 116     | 139     | G15      | F3                      | 120           | 139     | G15      | PC7                            | I/O      | FT            | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK,<br>DFSDM1_DATIN3,<br>USART6_RX, FMC_NE1,<br>SDMMC2_D7,<br>SDMMC1_D7, DCMI_D1,<br>LCD_G6, EVENTOUT        | -                       |

|         |         |              |         | Pin N   | umbe     | ər                      |             |         |          |                                |          |               | -     |                                                                                                                                              |                         |

|---------|---------|--------------|---------|---------|----------|-------------------------|-------------|---------|----------|--------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |         | TM32<br>TM32 |         |         |          |                         | M32I<br>M32 |         |          | reset                          |          |               |       |                                                                                                                                              |                         |

| LQFP100 | LQFP144 | UFBGA176     | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176     | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                          | Additional<br>functions |

| -       | -       | C13          | 134     | 157     | C13      | D3                      | 134         | 157     | C13      | PI3                            | I/O      | FT            | -     | TIM8_ETR,<br>SPI2_MOSI/I2S2_SD,<br>FMC_D27, DCMI_D10,<br>EVENTOUT                                                                            | -                       |

| -       | -       | D9           | 135     | -       | F9       | -                       | 135         | -       | F9       | VSS                            | s        | -             | -     | -                                                                                                                                            |                         |

| -       | -       | C9           | 136     | 158     | E10      | -                       | 136         | 158     | E10      | VDD                            | s        | -             | -     | -                                                                                                                                            |                         |

| 76      | 109     | A14          | 137     | 159     | A14      | A3                      | 137         | 159     | A14      | PA14(JTC<br>K-<br>SWCLK)       | I/O      | FT            | -     | JTCK-SWCLK,<br>EVENTOUT                                                                                                                      | -                       |

| 77      | 110     | A13          | 138     | 160     | A13      | F8                      | 138         | 160     | A13      | PA15(JTD<br>I)                 | I/O      | FT            | _     | JTDI,<br>TIM2_CH1/TIM2_ETR,<br>HDMI_CEC,<br>SPI1_NSS/I2S1_WS,<br>SPI3_NSS/I2S3_WS,<br>SPI6_NSS, UART4_RTS,<br>CAN3_TX, UART7_TX,<br>EVENTOUT | -                       |

| 78      | 111     | B14          | 139     | 161     | B14      | B4                      | 139         | 161     | B14      | PC10                           | I/O      | FT            | -     | DFSDM1_CKIN5,<br>SPI3_SCK/I2S3_CK,<br>USART3_TX, UART4_TX,<br>QUADSPI_BK1_IO1,<br>SDMMC1_D2, DCMI_D8,<br>LCD_R2, EVENTOUT                    | -                       |

| 79      | 112     | B13          | 140     | 162     | B13      | C4                      | 140         | 162     | B13      | PC11                           | I/O      | FT            | -     | DFSDM1_DATIN5,<br>SPI3_MISO, USART3_RX,<br>UART4_RX,<br>QUADSPI_BK2_NCS,<br>SDMMC1_D3, DCMI_D4,<br>EVENTOUT                                  | -                       |

| 80      | 113     | A12          | 141     | 163     | A12      | D4                      | 141         | 163     | A12      | PC12                           | I/O      | FT            | -     | TRACED3,<br>SPI3_MOSI/I2S3_SD,<br>USART3_CK, UART5_TX,<br>SDMMC1_CK, DCMI_D9,<br>EVENTOUT                                                    | -                       |

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | HDMI-CEC            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | I2C4                |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | SPDIFRX             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | CAN3                |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | LPTIM1              |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

# Table 13. STM32F765xx, STM32F767xx, STM32F768Ax and STM32F769xx register boundary addresses<sup>(1)</sup> (continued)

1. The gray color is used for reserved Flash memory addresses.

## 5.3 Operating conditions

### 5.3.1 General operating conditions

| Symbol                             | Parameter                                                        | Conditions <sup>(1)</sup>                                                             |                       | Min                | Тур | Max                | Unit |

|------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------|--------------------|-----|--------------------|------|

|                                    |                                                                  | Power Scale 3 (VOS[1:0] bits in<br>PWR_CR register = 0x01), Reg<br>ON, over-drive OFF |                       | 0                  | -   | 144                |      |

|                                    |                                                                  | Power Scale 2 (VOS[1:0] bits<br>in PWR_CR register = 0x10),                           | Over-<br>drive<br>OFF | 0                  | -   | 168                |      |

| f <sub>HCLK</sub>                  | Internal AHB clock frequency                                     | Regulator ON                                                                          | Over-<br>drive<br>ON  |                    | -   | 144                |      |

|                                    |                                                                  | Power Scale 1 (VOS[1:0] bits in PWR CR register= 0x11),                               | Over-<br>drive<br>OFF | 0                  | -   | 180                | MHz  |

|                                    |                                                                  | Regulator ON                                                                          | Over-<br>drive<br>ON  |                    | -   | 216 <sup>(2)</sup> |      |

| f                                  | Internal APB1 clock frequency                                    | Over-drive OFF                                                                        | •                     | 0                  | -   | 45                 |      |

| f <sub>PCLK1</sub>                 | Internal APB1 clock frequency                                    | Over-drive ON                                                                         |                       | 0                  | -   | 54                 |      |

| f <sub>PCLK2</sub>                 | Internal APB2 clock frequency                                    | Over-drive OFF                                                                        |                       | 0                  | -   | 90                 |      |

| 'PCLK2                             |                                                                  | Over-drive ON                                                                         |                       | 0                  | -   | 108                |      |

| V <sub>DD</sub>                    | Standard operating voltage                                       | -                                                                                     |                       | 1.7 <sup>(3)</sup> | -   | 3.6                |      |

| V <sub>DDA</sub> <sup>(4)(5)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M samples)       | Must be the same potential as V                                                       | (6)                   | 1.7 <sup>(3)</sup> | -   | 2.4                |      |

| VDDA.                              | Analog operating voltage<br>(ADC limited to 2.4 M samples)       | Must be the same potential as                                                         | VDD`                  | 2.4                | -   | 3.6                |      |

|                                    | USB supply voltage (supply                                       | USB not used                                                                          |                       | 1.7                | 3.3 | 3.6                | V    |

| V <sub>DDUSB</sub>                 | voltage for PA11,PA12, PB14<br>and PB15 pins)                    | USB used                                                                              |                       | 3.0                | -   | 3.6                | v    |

| V <sub>BAT</sub>                   | Backup operating voltage                                         | -                                                                                     |                       | 1.65               | -   | 3.6                |      |

| V <sub>DDSDMMC</sub>               | SDMMC2 supply voltage (supply voltage for PG[12:9] and PD6 pins) | It can be different from VDD                                                          |                       | 1.7                | -   | 3.6                |      |

| V <sub>DDDSI</sub>                 | DSI system operating                                             | -                                                                                     |                       | 1.7                | -   | 3.6                |      |

### 5.3.16 Memory characteristics

#### **Flash memory**

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter | Conditions                                  | Min | Тур | Max | Unit |

|-----------------|-----------|---------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> |           | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 14  | -   |      |

|                 |           | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 17  | -   | mA   |

|                 |           | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 24  | -   |      |

#### Table 55. Flash memory characteristics

# Table 56. Flash memory programming (single bank configurationnDBANK=1)

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE32KB</sub>  | Sector (32 KB) erase time  | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 250  | 600                | ms   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 200  | 500                |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 1100 | 2400               |      |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 800  | 1400               | ms   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 500  | 1100               |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 2.1  | 4                  |      |

| t <sub>ERASE256KB</sub> | Sector (256 KB) erase time | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 1.5  | 2.6                | s    |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 8    | 16                 |      |

| Symbol            | Parameter           | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|---------------------------------------------|--------------------|-----|--------------------|------|

|                   |                     | Program/erase<br>parallelism (PSIZE) = x 8  | -                  | 16  | 32                 |      |

| t <sub>BE</sub>   | Bank erase time     | Program/erase<br>parallelism (PSIZE) = x 16 | -                  | 11  | 22                 | s    |

|                   |                     | Program/erase<br>parallelism (PSIZE) = x 32 | -                  | 8   | 32                 |      |

|                   |                     | 32-bit program operation                    | 2.7                | -   | 3                  | V    |

| V <sub>prog</sub> | Programming voltage | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                   |                     | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

# Table 57. Flash memory programming (dual bank configurationnDBANK=0) (continued)

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 100K erase operations.

|                                 |                                                  | eniory programming      |                    | <u> </u> |                    |      |

|---------------------------------|--------------------------------------------------|-------------------------|--------------------|----------|--------------------|------|

| Symbol                          | Parameter                                        | Conditions              | Min <sup>(1)</sup> | Тур      | Max <sup>(1)</sup> | Unit |

| t <sub>prog</sub>               | Double word programming                          |                         | -                  | 16       | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE32KB</sub>          | Sector (32 KB) erase time                        | $T_A = 0$ to +40 °C     | -                  | 180      | -                  |      |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>DD</sub> = 3.3 V | -                  | 450      | -                  | ms   |

| t <sub>ERASE256KB</sub>         | Sector (256 KB) erase time                       | V <sub>PP</sub> = 8.5 V | -                  | 900      | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                         | -                  | 6.9      | -                  | s    |

| V <sub>prog</sub>               | Programming voltage                              | -                       | 2.7                | -        | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                       | 7                  | -        | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                       | 10                 | -        | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                       | -                  | -        | 1                  | hour |

Table 58. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3. V<sub>PP</sub> should only be connected during programming/erasing.

#### Table 59. Flash memory endurance and data retention

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |  |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|--|

| N <sub>END</sub> | l Enduranco    | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |  |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |  |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |  |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |  |

DocID029041 Rev 4

| Symbol Parameter                     |                                                                                                                                                                    |   | Тур | Мах  | Unit | Comments                                                                                                             |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|------|------|----------------------------------------------------------------------------------------------------------------------|

|                                      | DAC DC V <sub>DDA</sub> current                                                                                                                                    | - | 280 | 380  | μA   | With no load, middle code (0x800) on the inputs                                                                      |

| I <sub>DDA</sub> <sup>(4)</sup>      | consumption in quiescent mode <sup>(3)</sup>                                                                                                                       | - | 475 | 625  | μΑ   | With no load, worst code (0xF1C) at $V_{REF+}$ = 3.6 V in terms of DC consumption on the inputs                      |

| DNL <sup>(4)</sup>                   | Differential non linearity<br>Difference between two                                                                                                               | - | -   | ±0.5 | LSB  | Given for the DAC in 10-bit configuration.                                                                           |

|                                      | consecutive code-1LSB)                                                                                                                                             | - | -   | ±2   | LSB  | Given for the DAC in 12-bit configuration.                                                                           |

|                                      | Integral non linearity                                                                                                                                             | - | -   | ±1   | LSB  | Given for the DAC in 10-bit configuration.                                                                           |

| INL <sup>(4)</sup>                   | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023)                                | - | -   | ±4   | LSB  | Given for the DAC in 12-bit configuration.                                                                           |

|                                      | Offset error<br>(difference between<br>measured value at Code<br>(0x800) and the ideal value =<br>V <sub>REF+</sub> /2)                                            | - | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                            |

| Offset <sup>(4)</sup>                |                                                                                                                                                                    | - | -   | ±3   | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> =<br>3.6 V                                                          |

|                                      |                                                                                                                                                                    | - | -   | ±12  | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub> =<br>3.6 V                                                          |

| Gain<br>error <sup>(4)</sup>         | Gain error                                                                                                                                                         | - | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                            |

| t <sub>SETTLING</sub> <sup>(4)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±4LSB | - | 3   | 6    | μs   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                    |

| THD <sup>(4)</sup>                   | Total Harmonic Distortion<br>Buffer ON                                                                                                                             | - | -   | -    | dB   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                    |

| Update<br>rate <sup>(2)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | - | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                    |

| t <sub>WAKEUP</sub> <sup>(4)</sup>   | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | - | 6.5 | 10   | μs   | $C_{LOAD} \le 50 \text{ pF}, R_{LOAD} \ge 5 \text{ k}\Omega$<br>input code between lowest and highest possible ones. |

| PSRR+ <sup>(2)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement)                                                                                  | - | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                     |

Table 82. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.18.2: Internal reset OFF).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization results.

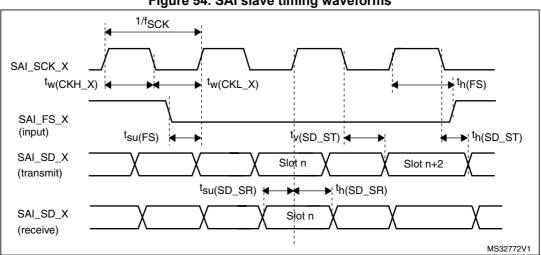

#### Figure 54. SAI slave timing waveforms

### USB OTG full speed (FS) characteristics

This interface is present in both the USB OTG HS and USB OTG FS controllers.

#### Table 90. USB OTG full speed startup time

| Symbol                              | Parameter                                   | Мах | Unit |  |

|-------------------------------------|---------------------------------------------|-----|------|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG full speed transceiver startup time | 1   | μs   |  |

1. Guaranteed by design.

| Symbol          |                                                  | Parameter                                              | Conditions                                                       | Min.<br>(1)        | Тур. | Max.<br>(1) | Unit |

|-----------------|--------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------|--------------------|------|-------------|------|

|                 | V <sub>DDUSB</sub>                               | USB OTG full speed<br>transceiver operating<br>voltage | -                                                                | 3.0 <sup>(2)</sup> | -    | 3.6         | V    |

| Input<br>levels | V <sub>DI</sub> <sup>(3)</sup>                   | Differential input sensitivity                         | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                | -    | -           |      |

| levels          | V <sub>CM</sub> <sup>(3)</sup>                   | Differential common mode range                         | Includes V <sub>DI</sub> range                                   | 0.8                | -    | 2.5         | V    |

|                 | $V_{SE}^{(3)}$                                   | Single ended receiver threshold                        | -                                                                | 1.3                | -    | 2.0         |      |

| Output          | Dutput V <sub>OL</sub> Static output level low I |                                                        | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(4)}$       | -                  | -    | 0.3         | v    |

| levels          | V <sub>OH</sub>                                  | Static output level high                               | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                | -    | 3.6         |      |

#### Table 91. USB OTG full speed DC electrical characteristics

| Symbol                    | Parameter                                 | Min                      | Мах                      | Unit |

|---------------------------|-------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> – 1   | 8T <sub>HCLK</sub> + 1   |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> – 1.5 | 6T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> – 1   | -                        | 115  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> + 2   | -                        |      |

Table 103. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings<sup>(1)</sup>

1. Guaranteed by characterization results.

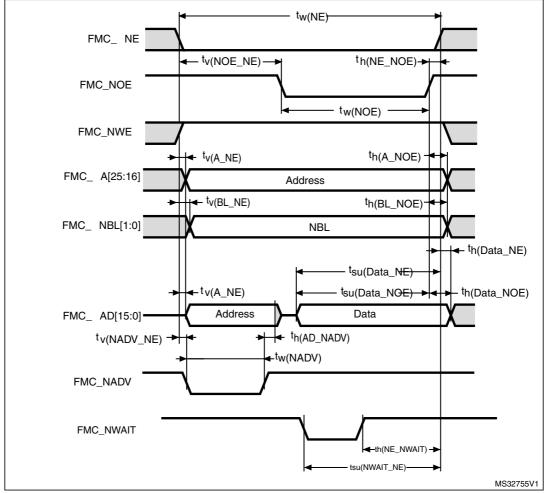

### Figure 63. Asynchronous multiplexed PSRAM/NOR read waveforms

Figure 67. Synchronous non-multiplexed NOR/PSRAM read timings

| Symbol                     | Parameter                                  | Min                      | Max | Unit |

|----------------------------|--------------------------------------------|--------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FMC_CLK period                             | 2T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                        | 2   |      |

| t <sub>d(CLKH-NExH)</sub>  | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub> | FMC_CLK low to FMC_NADV low                | -                        | 0.5 |      |

| t <sub>d(CLKL-NADVH)</sub> | FMC_CLK low to FMC_NADV high               | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>    | FMC_CLK low to FMC_Ax valid (x=1625)       | -                        | 2.5 |      |

| t <sub>d(CLKH-AIV)</sub>   | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>        | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>  | FMC_CLK low to FMC_NOE low                 | -                        | 1.5 |      |

| t <sub>d(CLKH-NOEH)</sub>  | FMC_CLK high to FMC_NOE high               | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>su(DV-CLKH)</sub>   | FMC_D[15:0] valid data before FMC_CLK high | 1.5                      | -   |      |

| t <sub>h(CLKH-DV)</sub>    | FMC_D[15:0] valid data after FMC_CLK high  | 3.5                      | -   |      |

| t <sub>(NWAIT-CLKH)</sub>  | FMC_NWAIT valid before FMC_CLK high        | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub> | FMC_NWAIT valid after FMC_CLK high         | 3.5                      | -   |      |

| Symbol                                         | Parameter                                             | Conditions                                                                                                                | Min                                     | Тур                  | Мах                                     | Unit |

|------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|-----------------------------------------|------|

| <sup>t</sup> wh(CKIN)<br><sup>t</sup> wl(CKIN) | Input clock high<br>and low time                      | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | TCKIN/2 - 0.5                           | T <sub>CKIN</sub> /2 | -                                       |      |

| t <sub>su</sub>                                | Data input setup<br>time                              | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | 2                                       | -                    | -                                       |      |

| t <sub>h</sub>                                 | Data input hold<br>time                               | SPI mode (SITP[1:0]=0,1),<br>External clock mode<br>(SPICKSEL[1:0]=0),<br>1.71 < V <sub>DD</sub> < 3.6 V                  | 3                                       | -                    | -                                       | ns   |

| T <sub>Manchester</sub>                        | Manchester data<br>period (recovered<br>clock period) | Manchester mode<br>(SITP[1:0]=2,3),<br>Internal clock mode<br>(SPICKSEL[1:0] $\neq$ 0),<br>1.71 < V <sub>DD</sub> < 3.6 V | (CKOUTDIV+1)<br>* T <sub>DFSDMCLK</sub> | -                    | (2*CKOUTDIV)<br>* T <sub>DFSDMCLK</sub> |      |

| Table 122. DFSDM measur | red timing 1.71-3.6V (co | ontinued) |

|-------------------------|--------------------------|-----------|

|                         |                          |           |

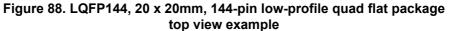

#### LQFP144 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

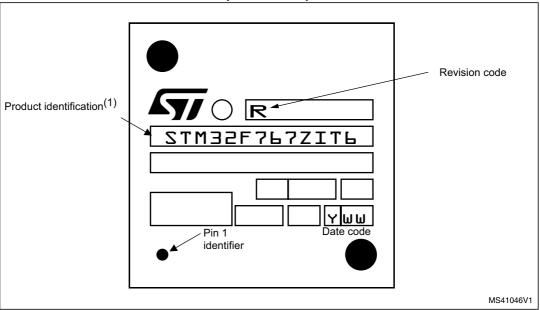

#### LQFP176 device marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 91. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

### 6.8 Thermal characteristics

The maximum chip-junction temperature,  ${\sf T}_{\sf J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \left(\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}\right) + \Sigma((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                   | Value | Unit |

|---------------|-----------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch  | 43    |      |

|               | Thermal resistance junction-ambient<br>WLCSP180 - 0.4 mm pitch              | 30    | _    |

|               | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch  | 40    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP176 - 24 × 24 mm / 0.5 mm pitch  | 38    | °C/W |

|               | Thermal resistance junction-ambient<br>LQFP208 - 28 × 28 mm / 0.5 mm pitch  | 19    |      |

|               | Thermal resistance junction-ambient<br>UFBGA176 - 10× 10 mm / 0.5 mm pitch  | 39    |      |

|               | Thermal resistance junction-ambient<br>TFBGA216 - 13 × 13 mm / 0.8 mm pitch | 29    |      |

Table 135. Package thermal characteristics

#### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.