Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Core ProcessorC166SV2Core Size16/32-BitSpeed128MHzConnectivityCANbus, EBI/EMI, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsI²S, POR, PWM, WDTNumber of I/O118Program Memory Size1.06MB (1.06M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadTemperature0-C-UPF144-4 | Detalls                    |                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------|

| Core Size16/32-BitSpeed128MHzConnectivityCANbus, EBI/EMI, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsI²S, POR, PWM, WDTNumber of I/O118Program Memory Size1.06MB (1.06M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSurface PackagePG-LQFP-144-4                 | Product Status             | Obsolete                                                                           |

| Speed128MHzConnectivityCANbus, EBI/EMI, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsI²S, POR, PWM, WDTNumber of I/O118Program Memory Size1.06MB (1.06M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG_LQFP-144-4    | Core Processor             | C1665V2                                                                            |

| ConnectivityCANbus, EBI/EMI, FlexRay, I²C, LINbus, SPI, UART/USARTPeripheralsI²S, POR, PWM, WDTNumber of I/O118Program Memory Size1.06MB (1.06M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4               | Core Size                  | 16/32-Bit                                                                          |

| PeripheralsI*S, POR, PWM, WDTNumber of I/O118Program Memory Size1.06MB (1.06M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                 | Speed                      | 128MHz                                                                             |

| Number of I/O118Program Memory Size1.06MB (1.06M × 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K × 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                              | Connectivity               | CANbus, EBI/EMI, FlexRay, I <sup>2</sup> C, LINbus, SPI, UART/USART                |

| Program Memory Size1.06MB (1.06M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                              | Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                    |

| Program Memory TypeFLASHEEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                                                                   | Number of I/O              | 118                                                                                |

| EEPROM Size-RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                                                                                           | Program Memory Size        | 1.06MB (1.06M x 8)                                                                 |

| RAM Size90K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                                                                                                       | Program Memory Type        | FLASH                                                                              |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                                                                                                                      | EEPROM Size                |                                                                                    |

| Data ConvertersA/D 24x12bOscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                                                                                                                                                         | RAM Size                   | 90K x 8                                                                            |

| Oscillator TypeExternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case144-LQFP Exposed PadSupplier Device PackagePG-LQFP-144-4                                                                                                                                                                                                                                                                                  | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                          |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     144-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-144-4                                                                                                                                                                                                                                                                | Data Converters            | A/D 24x12b                                                                         |

| Mounting Type     Surface Mount       Package / Case     144-LQFP Exposed Pad       Supplier Device Package     PG-LQFP-144-4                                                                                                                                                                                                                                                                                                                   | Oscillator Type            | External                                                                           |

| Package / Case 144-LQFP Exposed Pad Supplier Device Package PG-LQFP-144-4                                                                                                                                                                                                                                                                                                                                                                       | Operating Temperature      | -40°C ~ 125°C (TA)                                                                 |

| Supplier Device Package PG-LQFP-144-4                                                                                                                                                                                                                                                                                                                                                                                                           | Mounting Type              | Surface Mount                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Package / Case             | 144-LQFP Exposed Pad                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc2388e136f128laakxuma1                                                                                                                                                                                                                                                                                                                                                 | Supplier Device Package    | PG-LQFP-144-4                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2388e136f128laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

## 16/32-Bit Single-Chip Microcontroller with 32-Bit Performance XC238xE (XC2000 Family)

# 1 Summary of Features

For a quick overview and easy reference, the features of the XC238xE are summarized here.

- High-performance CPU with five-stage pipeline and MPU

- 7.8 ns instruction cycle at 128 MHz CPU clock (single-cycle execution)

- One-cycle 32-bit addition and subtraction with 40-bit result

- One-cycle multiplication (16 × 16 bit)

- Background division (32 / 16 bit) in 21 cycles

- One-cycle multiply-and-accumulate (MAC) instructions

- Enhanced Boolean bit manipulation facilities

- Zero-cycle jump execution

- Additional instructions to support HLL and operating systems

- Register-based design with multiple variable register banks

- Fast context switching support with two additional local register banks

- 16 Kbytes of two-way set-associative Instruction Cache (ICache)

- 16 Mbytes total linear address space for code and data

- 1024 Bytes on-chip special function register area (C166 Family compatible)

- Integrated Memory Protection Unit (MPU)

- Interrupt system with 16 priority levels providing 112 interrupt nodes

- Selectable external inputs for interrupt generation and wake-up

- Fastest sample-rate 7.8 ns

- Sixteen-channel interrupt-driven single-cycle data transfer with Peripheral Event Controller (PEC), 24-bit pointers cover total address space

- Clock generation from internal or external clock sources, using on-chip PLL or prescaler

- Hardware CRC-Checker with Programmable Polynomial to Supervise On-Chip Memory Areas

- On-chip memory modules

- 8 Kbytes on-chip stand-by RAM (SBRAM)

- 2 Kbytes on-chip dual-port RAM (DPRAM)

- 24 Kbytes on-chip data SRAM (DSRAM)

- Up to 64 Kbytes on-chip program/data SRAM (PSRAM)

- Up to 1 088 Kbytes on-chip program memory (Flash memory)

- Memory content protection through Error Correction Code (ECC)

- On-Chip Peripheral Modules

#### **Summary of Features**

#### **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the function set of the corresponding product type

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XC238xE please contact your sales representative or local distributor.

This document describes several derivatives of the XC238xE group:

**Basic Device Types** are readily available and **Special Device Types** are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term **XC238xE** is used for all derivatives throughout this document.

### 1.1 Basic Device Types

Basic device types are available and can be ordered through Infineon's direct and/or distribution channels.

| Table 1         Synopsis of XC238xE Basic Device Types |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Derivative <sup>1)</sup> | • | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>                         |

|--------------------------|---|------------------------------|------------------------|----------------------------|--------------------------------------------------|

| XC2388E-136FxxLR         |   | 64 Kbytes<br>24 Kbytes       | CC2<br>CCU60/1/2/3     | 16 + 8                     | 3 CAN Nodes<br>8 Serial Chan.<br>2 FlexRay Nodes |

1) xx is a placeholder for the available speed grade (in MHz).

2) Specific information about the on-chip Flash memory in Table 3.

3) All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

Specific information about the available channels in Table 5. Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

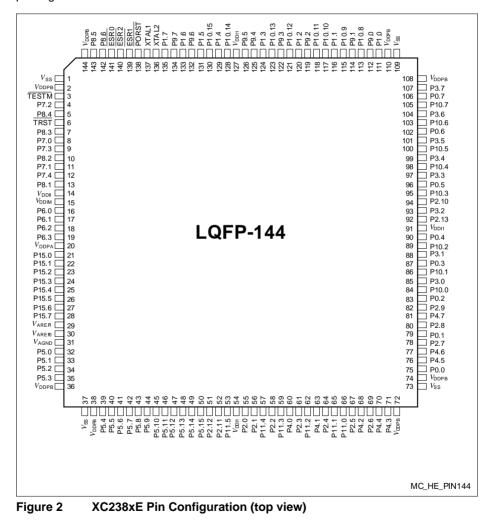

## 2.1 Pin Configuration and Definition

The pins of the XC238xE are described in detail in **Table 6**, which includes all alternate functions. For further explanations please refer to the footnotes at the end of the table. The following figure summarizes all pins, showing their locations on the four sides of the package.

#### **Key to Pin Definitions**

Ctrl.: The output signal for a port pin is selected by bit field PC in the associated • register Px\_IOCRy. Output O0 is selected by setting the respective bit field PC to  $1x00_{\rm P}$ , output O1 is selected by  $1x01_{\rm P}$ , etc.

Output signal OH is controlled by hardware.

- **Type**: Indicates the pad type and its power supply domain (A, B, M, 1). •

- St: Standard pad

- Sp: Special pad e.g. XTALx

- DP: Double pad can be used as standard or high speed pad

- In: Input only pad

- PS: Power supply pad

| Pin | Symbol            | Ctrl.  | Туре | Function                                                                                                                                                                                       |  |  |

|-----|-------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3   | TESTM             | I      | In/B | Testmode EnableEnables factory test modes, must be held HIGH fornormal operation (connect to $V_{\text{DDPB}}$ ).An internal pull-up device will hold this pin highwhen nothing is driving it. |  |  |

| 4   | P7.2              | 00 / I | St/B | Bit 2 of Port 7, General Purpose Input/Output                                                                                                                                                  |  |  |

|     | EMUX0             | 01     | St/B | External Analog MUX Control Output 0 (ADC1)                                                                                                                                                    |  |  |

|     | CCU62_CCP<br>OS0A | I      | St/B | CCU62 Position Input 0                                                                                                                                                                         |  |  |

|     | TDI_C             | IH     | St/B | JTAG Test Data Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin high wher<br>nothing is driving it.                                       |  |  |

| 5   | P8.4              | O0 / I | St/B | Bit 4 of Port 8, General Purpose Input/Output                                                                                                                                                  |  |  |

|     | CCU60_COU<br>T61  | O1     | St/B | CCU60 Channel 1 Output                                                                                                                                                                         |  |  |

|     | CCU62_CC6<br>1    | O2     | St/B | CCU62 Channel 1 Output                                                                                                                                                                         |  |  |

|     | TMS_D             | IH     | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. D is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.                             |  |  |

|     | CCU62_CC6         | I      | St/B | CCU62 Channel 1 Input                                                                                                                                                                          |  |  |

#### Table 6 Pin Definitions and Functions

1INB

| Pin | Symbol            | Ctrl.      | Туре | Function                                                                                                                                                                                                                                                                                                                                                    |

|-----|-------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | TRST              | 1          | In/B | Test-System Reset Input<br>For normal system operation, pin TRST should be<br>held low. A high level at this pin at the rising edge<br>of PORST activates the XC238xE's debug system.<br>In this case, pin TRST must be driven low once to<br>reset the debug system.<br>An internal pull-down device will hold this pin low<br>when nothing is driving it. |

| 7   | P8.3              | O0 / I     | St/B | Bit 3 of Port 8, General Purpose Input/Output                                                                                                                                                                                                                                                                                                               |

| -   | CCU60_COU<br>T60  | O1         | St/B | CCU60 Channel 0 Output                                                                                                                                                                                                                                                                                                                                      |

|     | CCU62_CC6<br>0    | O2         | St/B | CCU62 Channel 0 Output                                                                                                                                                                                                                                                                                                                                      |

|     | TDI_D             | IH         | St/B | JTAG Test Data Input<br>If JTAG pos. D is selected during start-up, an<br>internal pull-up device will hold this pin low when<br>nothing is driving it.                                                                                                                                                                                                     |

|     | CCU62_CC6<br>0INB | I          | St/B | CCU62 Channel 0 Input                                                                                                                                                                                                                                                                                                                                       |

| 8   | P7.0              | O0 / I     | St/B | Bit 0 of Port 7, General Purpose Input/Output                                                                                                                                                                                                                                                                                                               |

|     | T3OUT             | O1         | St/B | GPT12E Timer T3 Toggle Latch Output                                                                                                                                                                                                                                                                                                                         |

|     | T6OUT             | O2         | St/B | GPT12E Timer T6 Toggle Latch Output                                                                                                                                                                                                                                                                                                                         |

|     | TDO_A             | OH /<br>IH | St/B | JTAG Test Data Output / DAP1 Input/Output<br>If DAP pos. 0 or 2 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it.                                                                                                                                                                          |

|     | ESR2_1            | I          | St/B | ESR2 Trigger Input 1                                                                                                                                                                                                                                                                                                                                        |

| Table | Table 6Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                   |  |  |  |

|-------|-----------------------------------------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin   | Symbol                                        | Ctrl.  | Туре | Function                                                                                                                                                          |  |  |  |

| 9     | P7.3                                          | O0 / I | St/B | Bit 3 of Port 7, General Purpose Input/Output                                                                                                                     |  |  |  |

|       | EMUX1                                         | 01     | St/B | External Analog MUX Control Output 1 (ADC1)                                                                                                                       |  |  |  |

|       | U0C1_DOUT                                     | 02     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                 |  |  |  |

|       | U0C0_DOUT                                     | O3     | St/B | USIC0 Channel 0 Shift Data Output                                                                                                                                 |  |  |  |

|       | CCU62_CCP<br>OS1A                             | I      | St/B | CCU62 Position Input 1                                                                                                                                            |  |  |  |

|       | TMS_C                                         | IH     | St/B | JTAG Test Mode Selection Input<br>If JTAG pos. C is selected during start-up, an<br>internal pull-up device will hold this pin low when<br>nothing is driving it. |  |  |  |

|       | U0C1_DX0F                                     | I      | St/B | USIC0 Channel 1 Shift Data Input                                                                                                                                  |  |  |  |

| 10    | P8.2                                          | O0 / I | St/B | Bit 2 of Port 8, General Purpose Input/Output                                                                                                                     |  |  |  |

|       | CCU60_CC6<br>2                                | O1     | St/B | CCU60 Channel 2 Output                                                                                                                                            |  |  |  |

|       | TxDC1                                         | 02     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                   |  |  |  |

|       | U1C1_DOUT                                     | O3     | St/B | USIC1 Channel 1 Shift Data output                                                                                                                                 |  |  |  |

|       | CCU60_CC6<br>2INB                             | I      | St/B | CCU60 Channel 2 Input                                                                                                                                             |  |  |  |

| 11    | P7.1                                          | O0 / I | St/B | Bit 1 of Port 7, General Purpose Input/Output                                                                                                                     |  |  |  |

|       | EXTCLK                                        | 01     | St/B | Programmable Clock Signal Output                                                                                                                                  |  |  |  |

|       | CCU62_CTR<br>APA                              | I      | St/B | CCU62 Emergency Trap Input                                                                                                                                        |  |  |  |

|       | BRKIN_C                                       | I      | St/B | OCDS Break Signal Input                                                                                                                                           |  |  |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                |  |  |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |  |  |  |

| 79    | P0.1                                                   | O0 / I | St/B | Bit 1 of Port 0, General Purpose Input/Output  |  |  |  |  |

|       | U1C0_DOUT                                              | 01     | St/B | USIC1 Channel 0 Shift Data Output              |  |  |  |  |

|       | TxDC0                                                  | 02     | St/B | CAN Node 0 Transmit Data Output                |  |  |  |  |

|       | CCU61_CC6<br>1                                         | O3     | St/B | CCU61 Channel 1 Output                         |  |  |  |  |

|       | A1                                                     | OH     | St/B | External Bus Interface Address Line 1          |  |  |  |  |

|       | U1C0_DX0B                                              | I      | St/B | USIC1 Channel 0 Shift Data Input               |  |  |  |  |

|       | CCU61_CC6<br>1INA                                      | I      | St/B | CCU61 Channel 1 Input                          |  |  |  |  |

|       | U1C0_DX1A                                              | I      | St/B | USIC1 Channel 0 Shift Clock Input              |  |  |  |  |

| 80    | P2.8                                                   | O0 / I | DP/B | Bit 8 of Port 2, General Purpose Input/Output  |  |  |  |  |

|       | U0C1_SCLK<br>OUT                                       | O1     | DP/B | USIC0 Channel 1 Shift Clock Output             |  |  |  |  |

|       | EXTCLK                                                 | O2     | DP/B | Programmable Clock Signal Output               |  |  |  |  |

|       | CC2_CC21                                               | O3 / I | DP/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.      |  |  |  |  |

|       | A21                                                    | OH     | DP/B | External Bus Interface Address Line 21         |  |  |  |  |

|       | U0C1_DX1D                                              | I      | DP/B | USIC0 Channel 1 Shift Clock Input              |  |  |  |  |

| 81    | P4.7                                                   | O0 / I | St/B | Bit 7 of Port 4, General Purpose Input/Output  |  |  |  |  |

|       | CC2_CC31                                               | O3 / I | St/B | CAPCOM2 CC31IO Capture Inp./ Compare Out.      |  |  |  |  |

|       | T4EUDA                                                 | I      | St/B | GPT12E Timer T4 External Up/Down Control Input |  |  |  |  |

|       | CCU61_CCP<br>OS2A                                      | I      | St/B | CCU61 Position Input 2                         |  |  |  |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                             |  |  |  |

| 82    | P2.9                                                   | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |  |

|       | U0C1_DOUT                                              | 01     | St/B | USIC0 Channel 1 Shift Data Output                                                                                                                                                                                                                                                                    |  |  |  |

|       | TxDC1                                                  | 02     | St/B | CAN Node 1 Transmit Data Output                                                                                                                                                                                                                                                                      |  |  |  |

|       | CC2_CC22                                               | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.                                                                                                                                                                                                                                                            |  |  |  |

|       | A22                                                    | ОН     | St/B | External Bus Interface Address Line 22                                                                                                                                                                                                                                                               |  |  |  |

|       | CLKIN1                                                 | I      | St/B | Clock Signal Input 1                                                                                                                                                                                                                                                                                 |  |  |  |

|       | TCK_A                                                  | IH     | St/B | <b>DAP0/JTAG Clock Input</b><br>If JTAG pos. A is selected during start-up, an<br>internal pull-up device will hold this pin high when<br>nothing is driving it.<br>If DAP pos. 0 is selected during start-up, an<br>internal pull-down device will hold this pin low<br>when nothing is driving it. |  |  |  |

| 83    | P0.2                                                   | O0 / I | St/B | Bit 2 of Port 0, General Purpose Input/Output                                                                                                                                                                                                                                                        |  |  |  |

|       | U1C0_SCLK<br>OUT                                       | 01     | St/B | USIC1 Channel 0 Shift Clock Output                                                                                                                                                                                                                                                                   |  |  |  |

|       | TxDC0                                                  | 02     | St/B | CAN Node 0 Transmit Data Output                                                                                                                                                                                                                                                                      |  |  |  |

|       | CCU61_CC6<br>2                                         | O3     | St/B | CCU61 Channel 2 Output                                                                                                                                                                                                                                                                               |  |  |  |

|       | A2                                                     | ОН     | St/B | External Bus Interface Address Line 2                                                                                                                                                                                                                                                                |  |  |  |

|       | U1C0_DX1B                                              | I      | St/B | USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                    |  |  |  |

|       | CCU61_CC6<br>2INA                                      | I      | St/B | CCU61 Channel 2 Input                                                                                                                                                                                                                                                                                |  |  |  |

| Table 6Pin Definitions and Functions (cont'd) |                   |        |      |                                               |  |  |  |

|-----------------------------------------------|-------------------|--------|------|-----------------------------------------------|--|--|--|

| Pin                                           | Symbol            | Ctrl.  | Туре | Function                                      |  |  |  |

| 119                                           | P9.2              | O0 / I | St/B | Bit 2 of Port 9, General Purpose Input/Output |  |  |  |

|                                               | CCU63_CC6<br>2    | 01     | St/B | CCU63 Channel 2 Output                        |  |  |  |

|                                               | ERAY_TxEN<br>B    | O3     | St/B | ERAY Transmit Enable Output Channel B         |  |  |  |

|                                               | CCU63_CC6<br>2INA | I      | St/B | CCU63 Channel 2 Input                         |  |  |  |

|                                               | CAPINB            | I      | St/B | GPT12E Register CAPREL Capture Input          |  |  |  |

| 120                                           | P1.2              | O0 / I | St/B | Bit 2 of Port 1, General Purpose Input/Output |  |  |  |

| _                                             | CCU62_CC6<br>2    | 01     | St/B | CCU62 Channel 2 Output                        |  |  |  |

|                                               | U1C0_SELO<br>6    | O2     | St/B | USIC1 Channel 0 Select/Control 6 Output       |  |  |  |

|                                               | U2C1_SCLK<br>OUT  | O3     | St/B | USIC2 Channel 1 Shift Clock Output            |  |  |  |

|                                               | A10               | OH     | St/B | External Bus Interface Address Line 10        |  |  |  |

|                                               | ESR1_4            | I      | St/B | ESR1 Trigger Input 4                          |  |  |  |

|                                               | ERU_2A0           | I      | St/B | External Request Unit Channel 2 Input A0      |  |  |  |

|                                               | CCU61_T12<br>HRB  | I      | St/B | External Run Control Input for T12 of CCU61   |  |  |  |

|                                               | CCU62_CC6<br>2INA | I      | St/B | CCU62 Channel 2 Input                         |  |  |  |

|                                               | U2C1_DX0D         | I      | St/B | USIC2 Channel 1 Shift Data Input              |  |  |  |

|                                               | U2C1_DX1C         | I      | St/B | USIC2 Channel 1 Shift Clock Input             |  |  |  |

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                               |  |  |  |  |

|-------|--------------------------------------------------------|--------|------|-----------------------------------------------|--|--|--|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                      |  |  |  |  |

| 124   | P1.3                                                   | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output |  |  |  |  |

|       | CCU62_COU<br>T63                                       | O1     | St/B | CCU62 Channel 3 Output                        |  |  |  |  |

|       | U1C0_SELO<br>7                                         | O2     | St/B | USIC1 Channel 0 Select/Control 7 Output       |  |  |  |  |

|       | U2C0_SELO<br>4                                         | O3     | St/B | USIC2 Channel 0 Select/Control 4 Output       |  |  |  |  |

|       | A11                                                    | OH     | St/B | External Bus Interface Address Line 11        |  |  |  |  |

|       | ESR2_4                                                 | I      | St/B | ESR2 Trigger Input 4                          |  |  |  |  |

|       | ERU_3A0                                                | I      | St/B | External Request Unit Channel 3 Input A0      |  |  |  |  |

|       | CCU62_T12<br>HRB                                       | I      | St/B | External Run Control Input for T12 of CCU62   |  |  |  |  |

| 125   | P9.4                                                   | O0 / I | St/B | Bit 4 of Port 9, General Purpose Input/Output |  |  |  |  |

|       | CCU63_COU<br>T61                                       | O1     | St/B | CCU63 Channel 1 Output                        |  |  |  |  |

|       | U2C0_DOUT                                              | O2     | St/B | USIC2 Channel 0 Shift Data Output             |  |  |  |  |

|       | CCU62_COU<br>T63                                       | O3     | St/B | CCU62 Channel 3 Output                        |  |  |  |  |

| 126   | P9.5                                                   | O0 / I | St/B | Bit 5 of Port 9, General Purpose Input/Output |  |  |  |  |

|       | CCU63_COU<br>T62                                       | O1     | St/B | CCU63 Channel 2 Output                        |  |  |  |  |

|       | U2C0_DOUT                                              | O2     | St/B | USIC2 Channel 0 Shift Data Output             |  |  |  |  |

|       | CCU62_COU<br>T62                                       | O3     | St/B | CCU62 Channel 2 Output                        |  |  |  |  |

|       | U2C0_DX0E                                              | I      | St/B | USIC2 Channel 0 Shift Data Input              |  |  |  |  |

|       | CCU60_CCP<br>OS2B                                      | I      | St/B | CCU60 Position Input 2                        |  |  |  |  |

#### **General Device Information**

|                                        | Table 6     Pin Definitions and Functions (cont'd) |       |        |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|----------------------------------------|----------------------------------------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin                                    | Symbol                                             | Ctrl. | Туре   | Function                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 20                                     | V <sub>DDPA</sub>                                  | -     | - PS/A | Connect decoupling capacitors to adjacent $V_{\rm DDP}/V_{\rm SS}$ pin pairs as close as possible to the pins.                                                                                                                                                                                       |  |  |  |  |  |

|                                        |                                                    |       |        | Note: The A/D Converters and ports P5, P6 and P15 are fed from supply voltage $V_{DDPA}$ .                                                                                                                                                                                                           |  |  |  |  |  |

| 2,<br>36,<br>38,<br>72,<br>74,<br>108, | V <sub>DDPB</sub>                                  | -     | PS/B   | Digital Pad Supply Voltage for Domain B<br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The on-chip voltage regulators and all ports<br>except P5, P6 and P15 are fed from supply<br>voltage $V_{\text{DDPB}}$ . |  |  |  |  |  |

| 110,<br>144                            |                                                    |       |        |                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 1,<br>37,<br>73,                       | V <sub>SS</sub>                                    | -     | PS/    | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line or ground-plane.                                                                                                                                                                                                     |  |  |  |  |  |

| 109                                    |                                                    |       |        | Note: Also the exposed pad is connected<br>internally to $V_{SS}$ . To improve the EMC<br>behavior, it is recommended to connect the<br>exposed pad to the board ground.<br>For thermal aspects, please refer to the<br>Data Sheet. Board layout examples are<br>given in an application note.       |  |  |  |  |  |

To generate the reference clock output for bus timing measurement, f<sub>SYS</sub> must be selected as source for EXTCLK and P2.8 must be selected as output pin. Also the high-speed clock pad must be enabled. This configuration is referred to as reference clock output signal CLKOUT.

#### **Functional Description**

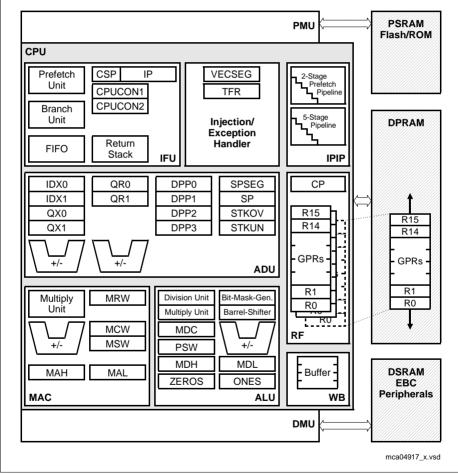

## 3.3 Central Processing Unit (CPU)

The core of the CPU consists of a 5-stage execution pipeline with a 2-stage instructionfetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply and accumulate unit (MAC), a register-file providing three register banks, and dedicated SFRs. The ALU features a multiply-and-divide unit, a bit-mask generator, and a barrel shifter.

### Figure 3 CPU Block Diagram

#### **Functional Description**

## 3.6 Interrupt System

The architecture of the XC238xE supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Using a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed. With the PEC just one cycle is 'stolen' from the current CPU activity to perform the PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC238xE has eight PEC channels, each with fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC238xE can react quickly to the occurrence of non-deterministic events.

#### Interrupt Nodes and Source Selection

The interrupt system provides 112 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

### External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

### Trap Processing

The XC238xE provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

#### **Functional Description**

## 3.12 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 16 + 8 multiplexed input channels and a sample and hold circuit have been integrated on-chip. 4 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XC238xE support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

## 4.3 Analog/Digital Converter Parameters

These parameters describe the conditions for optimum ADC performance. *Note: Operating Conditions apply.*

#### Table 20 ADC Parameters for All Voltage Ranges

| Parameter                                               | Symbol                     |                                                          | Values                                 |                             | Unit | Note /                            |

|---------------------------------------------------------|----------------------------|----------------------------------------------------------|----------------------------------------|-----------------------------|------|-----------------------------------|

|                                                         |                            | Min.                                                     | Тур.                                   | Max.                        |      | Test Condition                    |

| Switched capacitance at an analog input                 | C <sub>AINSW</sub><br>CC   | _                                                        | 9                                      | 20                          | pF   | not subject to<br>production test |

| Total capacitance at an analog input                    | C <sub>AINT</sub><br>CC    | -                                                        | 20                                     | 30                          | pF   | not subject to<br>production test |

| Switched capacitance at the reference input             | C <sub>AREFSW</sub><br>CC  | -                                                        | 15                                     | 30                          | pF   | not subject to<br>production test |

| Total capacitance at the reference input                | C <sub>AREFT</sub><br>CC   | -                                                        | 20                                     | 40                          | pF   | not subject to<br>production test |

| Broken wire detection delay against VAGND <sup>2)</sup> | t <sub>BWG</sub> CC        | -                                                        | -                                      | 50                          | 3)   |                                   |

| Broken wire detection delay against VAREF <sup>2)</sup> | t <sub>BWR</sub> CC        | -                                                        | -                                      | 50                          | 4)   |                                   |

| Conversion time for 8-bit result <sup>2)</sup>          | t <sub>c8</sub> CC         | $(10 + STC) \times t_{ADCI}$<br>+ 2 x $t_{SYS}$          |                                        |                             |      |                                   |

| Conversion time for 10-bit result <sup>2)</sup>         | <i>t</i> <sub>c10</sub> CC | (12 + S<br>+ 2 x t <sub>S</sub>                          | TC) x t <sub>AE</sub><br><sub>YS</sub> | DCI                         |      |                                   |

| Conversion time for 12-bit result <sup>2)</sup>         | <i>t</i> <sub>c12</sub> CC | (16 + STC) x t <sub>ADCI</sub><br>+ 2 x t <sub>SYS</sub> |                                        |                             |      |                                   |

| Analog reference ground                                 | $V_{AGND}$ SR              | V <sub>SS</sub><br>- 0.05                                | -                                      | 1.5                         | V    |                                   |

| Analog input voltage range                              | $V_{\rm AIN}{ m SR}$       | $V_{\rm AGND}$                                           | -                                      | $V_{AREF}$                  | V    | 5)                                |

| Analog reference voltage                                | $V_{AREF}$ SR              | V <sub>AGND</sub><br>+ 1.0                               | _                                      | V <sub>DDPA</sub><br>+ 0.05 | V    |                                   |

These parameter values cover the complete operating range. Under relaxed operating conditions (room temperature, nominal supply voltage) the typical values can be used for calculation.

## 4.4 System Parameters

The following parameters specify several aspects which are important when integrating the XC238xE into an application system.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

| Parameter                                                             | Symbol                 | Values                                       |                 |                            | Unit | Note /                               |

|-----------------------------------------------------------------------|------------------------|----------------------------------------------|-----------------|----------------------------|------|--------------------------------------|

|                                                                       |                        | Min.                                         | Тур.            | Max.                       |      | Test Condition                       |

| Short-term deviation of internal clock source frequency <sup>1)</sup> | ∆f <sub>INT</sub> CC   | -1                                           | -               | 1                          | %    | ⊿ <i>T</i> <sub>J</sub> ≤ 10 °C      |

| Internal clock source frequency                                       | $f_{\rm INT}$ CC       | 4.8                                          | 5.0             | 5.2                        | MHz  |                                      |

| Wakeup clock source                                                   | f <sub>₩U</sub> CC     | 400                                          | -               | 700                        | kHz  | FREQSEL= 00                          |

| frequency <sup>2)</sup>                                               |                        | 210                                          | -               | 390                        | kHz  | FREQSEL= 01                          |

|                                                                       |                        | 140                                          | -               | 260                        | kHz  | FREQSEL= 10                          |

|                                                                       |                        | 110                                          | -               | 200                        | kHz  | FREQSEL= 11                          |

| Startup time from power-<br>on with code execution<br>from Flash      | t <sub>SPO</sub> CC    | 1.9                                          | 2.5             | 3.7                        | ms   | $f_{\rm WU}$ = 500 kHz               |

| Startup time from standby<br>mode with code execution<br>from Flash   | t <sub>SSB</sub> CC    | 3.1                                          | 4.0             | 5.2                        | ms   | $f_{\rm WU}$ = 140 kHz               |

|                                                                       |                        | 1.9                                          | 2.4             | 3.6                        | ms   | $f_{\rm WU}$ = 500 kHz               |

| Startup time from stopover<br>mode with code execution<br>from PSRAM  | t <sub>SSO</sub> CC    | 11 /<br><i>f</i> <sub>WU</sub> <sup>3)</sup> | _               | 12 /<br>ƒ <sub>WU</sub> ³) | μS   |                                      |

| Core voltage (PVC)<br>supervision level                               | V <sub>PVC</sub> CC    | V <sub>LV</sub><br>- 0.03                    | V <sub>LV</sub> | V <sub>LV</sub><br>+ 0.07  | V    | 5)                                   |

| Supply watchdog (SWD) supervision level                               | V <sub>SWD</sub><br>CC | V <sub>LV</sub><br>- 0.10 <sup>6)</sup>      | $V_{\rm LV}$    | V <sub>LV</sub><br>+ 0.15  | V    | Lower voltage range <sup>5)</sup>    |

|                                                                       |                        | V <sub>LV</sub><br>- 0.15                    | $V_{\rm LV}$    | V <sub>LV</sub><br>+ 0.15  | V    | Upper voltage<br>range <sup>5)</sup> |

#### Table 24 Various System Parameters

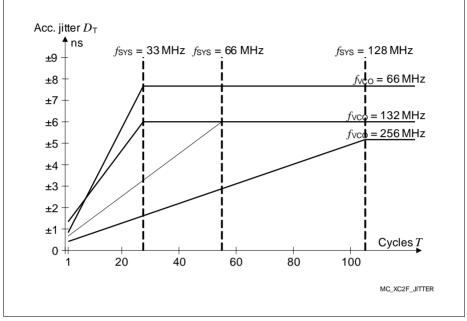

Figure 17 Approximated Accumulated PLL Jitter

Note: The specified PLL jitter values are valid if the capacitive load per pin does not exceed  $C_L = 20 \text{ pF}$ .

The maximum peak-to-peak noise on the pad supply voltage (measured between  $V_{DDPB}$  pin 144 and  $V_{SS}$  pin 1) is limited to a peak-to-peak voltage of  $V_{PP}$  = 50 mV. This can be achieved by appropriate blocking of the supply voltage as close as possible to the supply pins and using PCB supply and ground planes.

## 4.6.2.2 Wakeup Clock

When wakeup operation is selected (SYSCON0.CLKSEL =  $00_B$ ), the system clock is derived from the low-frequency wakeup clock source:

$f_{SYS} = f_{WU}$ .

In this mode, a basic functionality can be maintained without requiring an external clock source and while minimizing the power consumption.

## 4.6.2.3 Selecting and Changing the Operating Frequency

When selecting a clock source and the clock generation method, the required parameters must be carefully written to the respective bitfields, to avoid unintended intermediate states.

Many applications change the frequency of the system clock ( $f_{SYS}$ ) during operation in order to optimize system performance and power consumption. Changing the operating frequency also changes the switching currents, which influences the power supply.

To ensure proper operation of the on-chip EVRs while they generate the core voltage, the operating frequency shall only be changed in certain steps. This prevents overshoots and undershoots of the supply voltage.

To avoid the indicated problems, recommended sequences are provided which ensure the intended operation of the clock system interacting with the power system. Please refer to the Programmer's Guide.

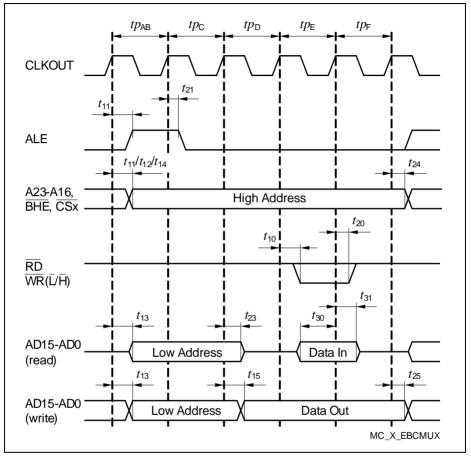

Note: The term CLKOUT refers to the reference clock output signal which is generated by selecting  $f_{SYS}$  as the source signal for the clock output signal EXTCLK on pin P2.8 and by enabling the high-speed clock driver on this pin.

#### Variable Memory Cycles

External bus cycles of the XC238xE are executed in five consecutive cycle phases (AB, C, D, E, F). The duration of each cycle phase is programmable (via the TCONCSx registers) to adapt the external bus cycles to the respective external module (memory, peripheral, etc.).

The duration of the access phase can optionally be controlled by the external module using the READY handshake input.

This table provides a summary of the phases and the ranges for their length.

| Table 34 | Programmable Bus C  | vcle Phases (  | (see timing | diagrams) |

|----------|---------------------|----------------|-------------|-----------|

|          | Trogrammable Duo og | yolo i naoco ( |             | alugianio |

| Bus Cycle Phase                                                                                                                                | Parameter | Valid Values | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|

| Address setup phase, the standard duration of this phase (1 $\dots$ 2 TCS) can be extended by 0 $\dots$ 3 TCS if the address window is changed | tpAB      | 1 2 (5)      | TCS  |

| Command delay phase                                                                                                                            | tpC       | 03           | TCS  |

| Write Data setup/MUX Tristate phase                                                                                                            | tpD       | 0 1          | TCS  |

| Access phase                                                                                                                                   | tpE       | 1 32         | TCS  |

| Address/Write Data hold phase                                                                                                                  | tpF       | 0 3          | TCS  |

Note: The bandwidth of a parameter (from minimum to maximum value) covers the whole operating range (temperature, voltage) as well as process variations. Within a given device, however, this bandwidth is smaller than the specified range. This is also due to interdependencies between certain parameters. Some of these interdependencies are described in additional notes (see standard timing).

Note: Operating Conditions apply;  $C_L = 20 \text{ pF}$ .

Figure 20 Multiplexed Bus Cycle