Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Not For New Designs                                                                 |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                             |

| Core Size                  | 16/32-Bit                                                                           |

| Speed                      | 128MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, FlexRay, I <sup>2</sup> C, LINbus, SPI, UART/USART                 |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                     |

| Number of I/O              | 118                                                                                 |

| Program Memory Size        | 1.06MB (1.06M x 8)                                                                  |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 90K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                           |

| Data Converters            | A/D 24x12b                                                                          |

| Oscillator Type            | External                                                                            |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 144-LQFP Exposed Pad                                                                |

| Supplier Device Package    | PG-LQFP-144-4                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2388e136f128Iraakxuma1 |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| XC238xE Data Sheet<br>Revision History: V1.3 2014-07 |                                                          |  |  |  |  |  |

|------------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|

| Previous V                                           | ersions:                                                 |  |  |  |  |  |

| V1.2 2012-                                           | 06                                                       |  |  |  |  |  |

| V1.1 2011-                                           | 10                                                       |  |  |  |  |  |

| V1.0 2010-                                           | 12                                                       |  |  |  |  |  |

| Page                                                 | Subjects (major changes since last revision)             |  |  |  |  |  |

| 9                                                    | Added XC2388E-136FxxLR to Basic Device Types             |  |  |  |  |  |

| 10                                                   | Moved XC2388E-136FxxL from Basic to Special Device Types |  |  |  |  |  |

| 141                                                  | Added package type PG-LQFP-144-23                        |  |  |  |  |  |

# Trademarks

C166<sup>™</sup>, TriCore<sup>™</sup> and DAVE<sup>™</sup> are trademarks of Infineon Technologies AG.

### We Listen to Your Comments

Is there any information in this document that you feel is wrong, unclear or missing? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

### **Table of Contents**

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2<br>1.3                                                                                                                                   | Summary of Features7Basic Device Types9Special Device Types10Definition of Feature Variants11                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>2</b><br>2.1<br>2.2                                                                                                                                          | General Device Information       12         Pin Configuration and Definition       13         Identification Registers       51                                                                                                                                                                                                                                                                                                                                                                             |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14<br>3.15<br>3.16<br>3.17<br>3.18<br>3.19<br>3.20 | Functional Description52Memory Subsystem and Organization52External Bus Controller57Central Processing Unit (CPU)58Memory Protection Unit (MPU)60Memory Checker Module (MCHK)60Interrupt System61On-Chip Debug Support (OCDS)62Capture/Compare Unit (CC2)63Capture/Compare Units CCU6x65General Purpose Timer (GPT12E) Unit67Real Time Clock71A/D Converters73Universal Serial Interface Channel Modules (USIC)74MultiCAN Module76System Timer77Watchdog Timer77Power Management80Instruction Set Summary81 |

| <b>4</b><br>4.1<br>4.1.1                                                                                                                                        | Electrical Parameters       84         General Parameters       84         Absolut Maximum Rating Conditions       84                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.1.2                                                                                                                                                           | Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.1.3                                                                                                                                                           | Voltage Range Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.1.4                                                                                                                                                           | Pad Timing Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.1.5                                                                                                                                                           | Parameter Interpretation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.2                                                                                                                                                             | DC Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.2.1                                                                                                                                                           | DC Parameters for Upper Voltage Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2.2                                                                                                                                                           | DC Parameters for Lower Voltage Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.2.3                                                                                                                                                           | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### **Summary of Features**

# **Ordering Information**

The ordering code for an Infineon microcontroller provides an exact reference to a specific product. This ordering code identifies:

- the function set of the corresponding product type

- the temperature range:

- SAF-...: -40°C to 85°C

- SAH-...: -40°C to 110°C

- SAK-...: -40°C to 125°C

- the package and the type of delivery.

For ordering codes for the XC238xE please contact your sales representative or local distributor.

This document describes several derivatives of the XC238xE group:

**Basic Device Types** are readily available and **Special Device Types** are only available on request.

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term **XC238xE** is used for all derivatives throughout this document.

# 1.1 Basic Device Types

Basic device types are available and can be ordered through Infineon's direct and/or distribution channels.

| Table 1         Synopsis of XC238xE Basic Device Types |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Derivative <sup>1)</sup> | • | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>                         |

|--------------------------|---|------------------------------|------------------------|----------------------------|--------------------------------------------------|

| XC2388E-136FxxLR         |   | 64 Kbytes<br>24 Kbytes       | CC2<br>CCU60/1/2/3     | 16 + 8                     | 3 CAN Nodes<br>8 Serial Chan.<br>2 FlexRay Nodes |

1) xx is a placeholder for the available speed grade (in MHz).

2) Specific information about the on-chip Flash memory in Table 3.

3) All derivatives additionally provide 8 Kbytes SBRAM and 2 Kbytes DPRAM.

Specific information about the available channels in Table 5. Analog input channels are listed for each Analog/Digital Converter module separately (ADC0 + ADC1).

### **General Device Information**

| Table | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                |  |

|-------|--------------------------------------------------------|--------|------|------------------------------------------------|--|

| Pin   | Symbol                                                 | Ctrl.  | Туре | Function                                       |  |

| 66    | P11.0                                                  | O0 / I | St/B | Bit 0 of Port 11, General Purpose Input/Output |  |

|       | CCU61_COU<br>T60                                       | O1     | St/B | CCU61 Channel 0 Output                         |  |

|       | U3C1_SCLK<br>OUT                                       | O2     | St/B | USIC3 Channel 1 Shift Clock Output             |  |

|       | CCU63_CCP<br>OS0A                                      | 1      | St/B | CCU63 Position Input 0                         |  |

|       | RxDC0F                                                 | I      | St/B | CAN Node 0 Receive Data Input                  |  |

|       | U3C1_DX1A                                              | I      | St/B | USIC3 Channel 1 Shift Clock Input              |  |

|       | ESR1_7                                                 | I      | St/B | ESR1 Trigger Input 7                           |  |

| 67    | P2.5                                                   | O0 / I | St/B | Bit 5 of Port 2, General Purpose Input/Output  |  |

|       | U0C0_SCLK<br>OUT                                       | O1     | St/B | USIC0 Channel 0 Shift Clock Output             |  |

|       | TxDC0                                                  | 02     | St/B | CAN Node 0 Transmit Data Output                |  |

|       | CC2_CC18                                               | O3 / I | St/B | CAPCOM2 CC18IO Capture Inp./ Compare Out.      |  |

|       | A18                                                    | ОН     | St/B | External Bus Interface Address Line 18         |  |

|       | U0C0_DX1D                                              | I      | St/B | USIC0 Channel 0 Shift Clock Input              |  |

|       | ESR1_10                                                | I      | St/B | ESR1 Trigger Input 10                          |  |

| _     | U3C1_DX0D                                              | I      | St/B | USIC3 Channel 1 Shift Data Input               |  |

| 68    | P4.2                                                   | O0 / I | St/B | Bit 2 of Port 4, General Purpose Input/Output  |  |

|       | U3C0_SCLK<br>OUT                                       | O1     | St/B | USIC3 Channel 0 Shift Clock Output             |  |

|       | TxDC2                                                  | 02     | St/B | CAN Node 2 Transmit Data Output                |  |

|       | CC2_CC26                                               | O3 / I | St/B | CAPCOM2 CC26IO Capture Inp./ Compare Out.      |  |

|       | CS2                                                    | ОН     | St/B | External Bus Interface Chip Select 2 Output    |  |

|       | T2INA                                                  | I      | St/B | GPT12E Timer T2 Count/Gate Input               |  |

|       | CCU62_CCP<br>OS1B                                      | I      | St/B | CCU62 Position Input 1                         |  |

|       | U3C0_DX1B                                              | I      | St/B | USIC3 Channel 0 Shift Clock Input              |  |

### **General Device Information**

|     | 1                 | 1      |      | Functions (cont'd)                            |  |  |

|-----|-------------------|--------|------|-----------------------------------------------|--|--|

| Pin | Symbol            | Ctrl.  | Туре |                                               |  |  |

| 75  | P0.0              | O0 / I | St/B | Bit 0 of Port 0, General Purpose Input/Output |  |  |

|     | U1C0_DOUT         | 01     | St/B | USIC1 Channel 0 Shift Data Output             |  |  |

|     | CCU61_CC6<br>0    | O3     | St/B | CCU61 Channel 0 IOutput                       |  |  |

|     | A0                | ОН     | St/B | External Bus Interface Address Line 0         |  |  |

|     | U1C0_DX0A         | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |

|     | CCU61_CC6<br>0INA | I      | St/B | CCU61 Channel 0 Input                         |  |  |

|     | ESR1_11           | I      | St/B | ESR1 Trigger Input 11                         |  |  |

| 76  | P4.5              | O0 / I | St/B | Bit 5 of Port 4, General Purpose Input/Output |  |  |

|     | U3C0_DOUT         | 01     | St/B | USIC3 Channel 0 Shift Data Output             |  |  |

|     | CC2_CC29          | O3 / I | St/B | CAPCOM2 CC29IO Capture Inp./Compare Out.      |  |  |

|     | CCU61_CCP<br>OS0A | I      | St/B | CCU61 Position Input 0                        |  |  |

|     | U3C0_DX0B         | I      | St/B | USIC3 Channel 0 Shift Data Input              |  |  |

|     | ESR2_10           | I      | St/B | ESR2 Trigger Input 10                         |  |  |

| 77  | P4.6              | 00 / 1 | St/B | Bit 6 of Port 4, General Purpose Input/Output |  |  |

|     | U3C0_DOUT         | 01     | St/B | USIC3 Channel 0 Shift Data Output             |  |  |

|     | CC2_CC30          | O3 / I | St/B | CAPCOM2 CC30IO Capture Inp./ Compare Out.     |  |  |

|     | T4INA             | I      | St/B | GPT12E Timer T4 Count/Gate Input              |  |  |

|     | CCU61_CCP<br>OS1A | I      | St/B | CCU61 Position Input 1                        |  |  |

| 78  | P2.7              | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |

|     | U0C1_SELO<br>0    | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |

|     | U0C0_SELO<br>1    | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |

|     | CC2_CC20          | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |

|     | A20               | OH     | St/B | External Bus Interface Address Line 20        |  |  |

|     | U0C1_DX2C         | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |

|     | RxDC1C            | I      | St/B | CAN Node 1 Receive Data Input                 |  |  |

|     | ESR2_7            | I      | St/B | ESR2 Trigger Input 7                          |  |  |

### **General Device Information**

|                                        | Table 6         Pin Definitions and Functions (cont'd) |       |      |                                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------|--------------------------------------------------------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin                                    | Symbol                                                 | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                             |  |  |

| 20                                     | V <sub>DDPA</sub>                                      | -     | PS/A | Connect decoupling capacitors to adjacent $V_{\rm DDP}/V_{\rm SS}$ pin pairs as close as possible to the pins.                                                                                                                                                                                       |  |  |

|                                        |                                                        |       |      | Note: The A/D Converters and ports P5, P6 and P15 are fed from supply voltage $V_{DDPA}$ .                                                                                                                                                                                                           |  |  |

| 2,<br>36,<br>38,<br>72,<br>74,<br>108, | V <sub>DDPB</sub>                                      | -     | PS/B | Digital Pad Supply Voltage for Domain B<br>Connect decoupling capacitors to adjacent<br>$V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pins.<br>Note: The on-chip voltage regulators and all ports<br>except P5, P6 and P15 are fed from supply<br>voltage $V_{\text{DDPB}}$ . |  |  |

| 110,<br>144                            |                                                        |       |      |                                                                                                                                                                                                                                                                                                      |  |  |

| 1,<br>37,<br>73,                       | V <sub>SS</sub>                                        | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line or ground-plane.                                                                                                                                                                                                     |  |  |

| 109                                    |                                                        |       |      | Note: Also the exposed pad is connected<br>internally to $V_{SS}$ . To improve the EMC<br>behavior, it is recommended to connect the<br>exposed pad to the board ground.<br>For thermal aspects, please refer to the<br>Data Sheet. Board layout examples are<br>given in an application note.       |  |  |

To generate the reference clock output for bus timing measurement, f<sub>SYS</sub> must be selected as source for EXTCLK and P2.8 must be selected as output pin. Also the high-speed clock pad must be enabled. This configuration is referred to as reference clock output signal CLKOUT.

### **General Device Information**

# 2.2 Identification Registers

The identification registers describe the current version of the XC238xE and of its modules.

# Table 7 XC238xE Identification Registers

| Short Name  | Value                  | Address              | Notes   |

|-------------|------------------------|----------------------|---------|

| SCU_IDMANUF | 1820 <sub>H</sub>      | 00'F07E <sub>H</sub> |         |

| SCU_IDCHIP  | 4801 <sub>H</sub>      | 00'F07C <sub>H</sub> | Step AA |

| SCU_IDMEM   | 310F <sub>H</sub>      | 00'F07A <sub>H</sub> |         |

| SCU_IDPROG  | 1313 <sub>H</sub>      | 00'F078 <sub>H</sub> |         |

| JTAG_ID     | 101B'F083 <sub>H</sub> |                      |         |

# 3 Functional Description

The architecture of the XC238xE combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources. This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC238xE.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC238xE.

# 3.1 Memory Subsystem and Organization

The memory space of the XC238xE is configured in the von Neumann architecture. In this architecture all internal and external resources, including code memory, data memory, registers and I/O ports, are organized in the same linear address space.

| Address Area                   | Start Loc.           | End Loc.             | Area Size <sup>2)</sup>  | Notes               |

|--------------------------------|----------------------|----------------------|--------------------------|---------------------|

| IMB register space             | FF'FF00 <sub>H</sub> | FF'FFFF <sub>H</sub> | 256 Bytes                |                     |

| Reserved                       | F0'0000 <sub>H</sub> | FF'FEFF <sub>H</sub> | < 1 Mbyte                | Minus IMB registers |

| Reserved for EPSRAM            | E9'0000 <sub>H</sub> | EF'FFFF <sub>H</sub> | 448 Kbytes               | Mirrors EPSRAM      |

| Emulated PSRAM                 | E8'0000 <sub>H</sub> | E8'FFFF <sub>H</sub> | up to<br>64 Kbytes       | With Flash timing   |

| Reserved for PSRAM             | E1'0000 <sub>H</sub> | E7'FFFF <sub>H</sub> | 448 Kbytes               | Mirrors PSRAM       |

| PSRAM                          | E0'0000 <sub>H</sub> | E0'FFFF <sub>H</sub> | up to<br>64 Kbytes       | Program SRAM        |

| Reserved for Flash             | D1'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | 448 Kbytes               |                     |

| Flash 4                        | D0'0000 <sub>H</sub> | D0'FFFF <sub>H</sub> | 64 Kbytes                |                     |

| Flash 3                        | CC'0000 <sub>H</sub> | CF'FFFF <sub>H</sub> | 256 Kbytes               |                     |

| Flash 2                        | C8'0000 <sub>H</sub> | CB'FFFF <sub>H</sub> | 256 Kbytes               |                     |

| Flash 1                        | C4'0000 <sub>H</sub> | C7'FFFF <sub>H</sub> | 256 Kbytes               |                     |

| Flash 0                        | C0'0000 <sub>H</sub> | C3'FFFF <sub>H</sub> | 256 Kbytes <sup>3)</sup> | Minus res. seg.     |

| External memory area           | 40'0000 <sub>H</sub> | BF'FFFF <sub>H</sub> | 8 Mbytes                 |                     |

| External IO area <sup>4)</sup> | 21'0000 <sub>H</sub> | 3F'FFFF <sub>H</sub> | 1 984 Kbytes             |                     |

# Table 8 XC238xE Memory Map <sup>1)</sup>

Up to 24 Kbytes of on-chip Data SRAM (DSRAM) are used for storage of general user data. The DSRAM is accessed via a separate interface and is optimized for data access.

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** provide storage for user-defined variables, for the system stack, and for general purpose register banks. A register bank can consist of up to 16 word-wide (R0 to R15) and/or byte-wide (RL0, RH0, ..., RL7, RH7) General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC2000 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

In order to meet the requirements of designs where more memory is required than is available on chip, up to 12 Mbytes (approximately, see **Table 8**) of external RAM and/or ROM can be connected to the microcontroller. The External Bus Interface also provides access to external peripherals.

**The on-chip Flash memory** stores code, constant data, and control data. The 1 088 Kbytes of on-chip Flash memory consist of 1 module of 64 Kbytes (preferably for data storage) and 4 modules of 256 Kbytes. Each module is organized in 4-Kbyte sectors.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.6.

<sup>1)</sup> To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

With this hardware most XC238xE instructions are executed in a single machine cycle of ns @ -MHz CPU clock. For example, shift and rotate instructions are always processed during one machine cycle, no matter how many bits are shifted. Also, multiplication and most MAC instructions execute in one cycle. All multiple-cycle instructions have been optimized so that they can be executed very fast; for example, a 32-/16-bit division is started within 4 cycles while the remaining cycles are executed in the background. Another pipeline optimization, the branch target prediction, eliminates the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 wordwide GPRs each at its disposal. One of these register banks is physically allocated within the on-chip DPRAM area. A Context Pointer (CP) register determines the base address of the active register bank accessed by the CPU at any time. The number of these register bank copies is only restricted by the available internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided for storage of temporary data. The system stack can be allocated to any location within the address space (preferably in the on-chip RAM area); it is accessed by the CPU with the stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly compared with the stack pointer value during each stack access to detect stack overflow or underflow.

The high performance of the CPU hardware implementation can be best utilized by the programmer with the highly efficient XC238xE instruction set. This includes the following instruction classes:

- Standard Arithmetic Instructions

- DSP-Oriented Arithmetic Instructions

- Logical Instructions

- Boolean Bit Manipulation Instructions

- Compare and Loop Control Instructions

- Shift and Rotate Instructions

- Prioritize Instruction

- Data Movement Instructions

- System Stack Instructions

- Jump and Call Instructions

- Return Instructions

- System Control Instructions

- Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes and words. A variety of direct, indirect or immediate addressing modes are provided to specify the required operands.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

# Table 9Compare Modes (cont'd)

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the compare mode selected.

The default Watchdog Timer interval after power-up is 6.5 ms (@ 10 MHz).

# 3.17 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XC238xE from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on one of two selectable pins.

# 3.18 Parallel Ports

The XC238xE provides up to 119 I/O lines which are organized into 11 input/output ports and 2 input ports. All port lines are bit-addressable, and all input/output lines can be individually (bit-wise) configured via port control registers. This configuration selects the direction (input/output), push/pull or open-drain operation, activation of pull devices, and edge characteristics (shape) and driver characteristics (output current) of the port drivers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. During the internal reset, all port pins are configured as inputs without pull devices active.

All port lines have alternate input or output functions associated with them. These alternate functions can be programmed to be assigned to various port pins to support the best utilization for a given application. For this reason, certain functions appear several times in **Table 10**.

All port lines that are not used for alternate functions may be used as general purpose I/O lines.

| Port | Width | I/O | Connected Modules                                                               |

|------|-------|-----|---------------------------------------------------------------------------------|

| P0   | 8     | I/O | EBC (A7A0), CCU6, USIC, CAN                                                     |

| P1   | 8     | I/O | EBC (A15A8), CCU6, USIC                                                         |

| P2   | 14    | I/O | EBC (READY, BHE, A23A16, AD15AD13, D15D13),<br>CAN, CC2, GPT12E, USIC, DAP/JTAG |

| P3   | 8     | I/O | CAN, USIC                                                                       |

| P4   | 8     | I/O | EBC (CS4CS0), CC2, CAN, GPT12E, USIC                                            |

| P5   | 16    | I   | Analog Inputs, CCU6, DAP/JTAG, GPT12E, CAN                                      |

| P6   | 4     | I/O | ADC, CAN, GPT12E                                                                |

| P7   | 5     | I/O | CAN, GPT12E, SCU, DAP/JTAG, CCU6, ADC, USIC                                     |

| P8   |       | I/O | CCU6, DAP/JTAG, USIC                                                            |

| P9   | 8     | I/O | CCU6, DAP/JTAG, CAN, ERAY                                                       |

| P10  | 16    | I/O | EBC (ALE, RD, WR, AD12AD0, D12D0), CCU6, USIC, DAP/JTAG, CAN, ERAY              |

| P11  | 6     | I/O | CCU6, USIC, CAN                                                                 |

| P15  | 8     | I   | Analog Inputs, GPT12E                                                           |

# Table 10Summary of the XC238xE's Ports

# 3.20 Instruction Set Summary

Table 11 lists the instructions of the XC238xE.

The addressing modes that can be used with a specific instruction, the function of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "**Instruction Set Manual**".

This document also provides a detailed description of each instruction.

| Mnemonic      | Description                                                                                       | Bytes |

|---------------|---------------------------------------------------------------------------------------------------|-------|

| ADD(B)        | Add word (byte) operands                                                                          | 2/4   |

| ADDC(B)       | Add word (byte) operands with Carry                                                               | 2/4   |

| SUB(B)        | Subtract word (byte) operands                                                                     | 2/4   |

| SUBC(B)       | Subtract word (byte) operands with Carry                                                          | 2/4   |

| MUL(U)        | (Un)Signed multiply direct GPR by direct GPR (16- $\times$ 16-bit)                                | 2     |

| DIV(U)        | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                         | 2     |

| DIVL(U)       | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                         | 2     |

| CPL(B)        | Complement direct word (byte) GPR                                                                 | 2     |

| NEG(B)        | Negate direct word (byte) GPR                                                                     | 2     |

| AND(B)        | Bitwise AND, (word/byte operands)                                                                 | 2/4   |

| OR(B)         | Bitwise OR, (word/byte operands)                                                                  | 2/4   |

| XOR(B)        | Bitwise exclusive OR, (word/byte operands)                                                        | 2/4   |

| BCLR/BSET     | Clear/Set direct bit                                                                              | 2     |

| BMOV(N)       | Move (negated) direct bit to direct bit                                                           | 4     |

| BAND/BOR/BXOR | AND/OR/XOR direct bit with direct bit                                                             | 4     |

| BCMP          | Compare direct bit to direct bit                                                                  | 4     |

| BFLDH/BFLDL   | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data     | 4     |

| CMP(B)        | Compare word (byte) operands                                                                      | 2/4   |

| CMPD1/2       | Compare word data to GPR and decrement GPR by 1/2                                                 | 2/4   |

| CMPI1/2       | Compare word data to GPR and increment GPR by 1/2                                                 | 2/4   |

| PRIOR         | Determine number of shift cycles to normalize direct word GPR and store result in direct word GPR | 2     |

| SHL/SHR       | Shift left/right direct word GPR                                                                  | 2     |

# Table 11 Instruction Set Summary

# 4.1.2 Operating Conditions

The following operating conditions must not be exceeded to ensure correct operation of the XC238xE. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

Note: Typical parameter values refer to room temperature and nominal supply voltage, minimum/maximum parameter values also include conditions of minimum/maximum temperature and minimum/maximum supply voltage. Additional details are described where applicable.

| Parameter                                                        | Symbol                    | Values |                           |                           | Unit | Note /                                                              |

|------------------------------------------------------------------|---------------------------|--------|---------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                  |                           | Min.   | Тур.                      | Max.                      | 1    | Test Condition                                                      |

| Voltage Regulator Buffer<br>Capacitance for DMP_M                | $C_{\rm EVRM} \ { m SR}$  | 1.0    | -                         | 4.7                       | μF   | 1)                                                                  |

| Voltage Regulator Buffer<br>Capacitance for DMP_1                | $C_{\rm EVR1}$ SR         | 0.68   | -                         | 2.2                       | μF   | 1)2)                                                                |

| External Load<br>Capacitance                                     | $C_{L} \operatorname{SR}$ | -      | 20 <sup>3)</sup>          | -                         | pF   | pin out<br>driver= default                                          |

| System frequency                                                 | $f_{\rm SYS}{\rm SR}$     | -      | -                         | 128                       | MHz  | 5)                                                                  |

| Overload current for analog inputs <sup>6)</sup>                 | I <sub>OVA</sub> SR       | -2     | -                         | 5                         | mA   | not subject to<br>production test                                   |

| Overload current for digital inputs <sup>6)</sup>                | I <sub>OVD</sub> SR       | -5     | -                         | 5                         | mA   | not subject to<br>production test                                   |

| Overload current coupling factor for analog inputs <sup>7)</sup> | K <sub>OVA</sub><br>CC    | -      | 2.5 x<br>10 <sup>-4</sup> | 1.5 x<br>10 <sup>-3</sup> | -    | <i>I</i> <sub>OV</sub> < 0 mA;<br>not subject to<br>production test |

|                                                                  |                           | _      | 1.0 x<br>10 <sup>-6</sup> | 1.0 x<br>10 <sup>-4</sup> | -    | <i>I</i> <sub>OV</sub> > 0 mA;<br>not subject to<br>production test |

| Overload current coupling factor for digital I/O pins            | K <sub>OVD</sub><br>CC    | _      | 1.0 x<br>10 <sup>-2</sup> | 3.0 x<br>10 <sup>-2</sup> |      | <i>I</i> <sub>OV</sub> < 0 mA;<br>not subject to<br>production test |

|                                                                  |                           | _      | 1.0 x<br>10 <sup>-4</sup> | 5.0 x<br>10 <sup>-3</sup> |      | <i>I</i> <sub>OV</sub> > 0 mA;<br>not subject to<br>production test |

# Table 13 Operating Conditions

# 4.1.3 Voltage Range Definition

The XC238xE timing depends on the supply voltage. If such a dependency exists the timing values are given for 2 voltage areas commonly used. The voltage areas are defined in the following tables.

### Table 14 Upper Voltage Range Definition

| Parameter                                                       | Symbol                |      | Values |      | Unit | Note /<br>Test Condition         |

|-----------------------------------------------------------------|-----------------------|------|--------|------|------|----------------------------------|

|                                                                 |                       | Min. | Тур.   | Max. |      |                                  |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{\rm SR}$ | 4.5  | 5      | 5.5  | V    | $f_{\rm SYS} \le 100 \; \rm MHz$ |

|                                                                 |                       | 4.75 | 5      | 5.25 | V    | f <sub>SYS</sub> ≤ 128 MHz       |

# Table 15 Lower Voltage Range Definition

| Parameter                                                       | Symbol               |      | Values |      | Unit | Note /<br>Test Condition |

|-----------------------------------------------------------------|----------------------|------|--------|------|------|--------------------------|

|                                                                 |                      | Min. | Тур.   | Max. |      |                          |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 3.0  | 3.3    | 4.5  | V    |                          |

# 4.1.4 Pad Timing Definition

If not otherwise noted, all timing parameters are tested and are valid for the corresponding output pins operating in strong driver, fast edge mode. See also "Pad Properties" on Page 118.

# 4.1.5 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC238xE and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC238xE provides signals with the specified characteristics.

SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC238xE.

- 2) This parameter includes the sample time (also the additional sample time specified by STC), the time to determine the digital result and the time to load the result register with the conversion result. Values for the basic clock t<sub>ADCI</sub> depend on programming.

- The broken wire detection delay against V<sub>AGND</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 500 μs. Result below 10% (66<sub>H</sub>).

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332<sub>µ</sub>).

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

| Parameter                                               | Symbol                     | Values |      |      | Unit | Note /                                     |

|---------------------------------------------------------|----------------------------|--------|------|------|------|--------------------------------------------|

|                                                         |                            | Min.   | Тур. | Max. |      | Test Condition                             |

| Input resistance of the selected analog channel         | R <sub>AIN</sub> CC        | -      | 0.9  | 1.5  | kΩ   | not subject to<br>production test          |

| Input resistance of the reference input                 | R <sub>AREF</sub><br>CC    | -      | 0.5  | 1    | kΩ   | not subject to<br>production test          |

| Differential Non-Linearity<br>Error <sup>2)3)4)5)</sup> | EA <sub>DNL</sub>  <br>CC  | -      | 1.5  | 3.0  | LSB  | not subject to production test             |

| Gain Error <sup>2)3)4)5)</sup>                          | EA <sub>GAIN</sub>  <br>CC | -      | 0.5  | 3.5  | LSB  | not subject to<br>production test          |

| Integral Non-Linearity<br>2)3)4)5)                      | EA <sub>INL</sub>  <br>CC  | -      | 1.5  | 3.0  | LSB  | not subject to<br>production test          |

| Offset Error <sup>2)3)4)5)</sup>                        | EA <sub>OFF</sub>  <br>CC  | -      | 1.0  | 4.0  | LSB  | not subject to<br>production test          |

| Total Unadjusted Error <sup>3)4)</sup>                  | TUE <br>CC                 | -      | 2.5  | 4    | LSB  | 6)                                         |

| Analog clock frequency                                  | $f_{\rm ADCI}{\rm SR}$     | 2      | -    | 20   | MHz  | Std. reference input ( $V_{\text{AREF}}$ ) |

|                                                         |                            | 2      | -    | 17.5 | MHz  | Alt. reference<br>input (CH0)              |

| Wakeup time from analog powerdown, fast mode            | t <sub>WAF</sub> CC        | -      | -    | 7    | μS   |                                            |

| Wakeup time from analog powerdown, slow mode            | t <sub>WAS</sub> CC        | _      | -    | 11.5 | μS   |                                            |

# Table 21 ADC Parameters for Upper Voltage Range

| Parameter                                    | Symbol              | Values |      |      | Unit | Note /         |

|----------------------------------------------|---------------------|--------|------|------|------|----------------|

|                                              |                     | Min.   | Тур. | Max. |      | Test Condition |

| Wakeup time from analog powerdown, fast mode | t <sub>WAF</sub> CC | -      | -    | 8.5  | μS   |                |

| Wakeup time from analog powerdown, slow mode | t <sub>WAS</sub> CC | -      | -    | 15   | μS   |                |

#### Table 22 ADC Parameters for Lower Voltage Range (cont'd)

These parameter values cover the complete operating range. Under relaxed operating conditions (room temperature, nominal supply voltage) the typical values can be used for calculation.

- 2) The sum of DNL/INL/GAIN/OFF errors does not exceed the related TUE total unadjusted error.

- If a reduced analog reference voltage between 1 V and V<sub>DDPA</sub> / 2 is used, there is an additional decrease of the ADC speed and accuracy.

- 4) If the analog reference voltage is below V<sub>DDPA</sub> but still in the range of V<sub>DDPA</sub> / 2 and V<sub>DDPA</sub>, the ADC errors increase. Reducing the reference voltage by a factor k (k < 1) increases TUE, DNL, INL, Gain and Offset errors by a factor 1/k.</p>

- 5) If the analog reference voltage is above  $V_{\text{DDPA}}$ , the ADC errors increase.

6) TUE is based on 12-bit conversions.

TUE is tested at  $V_{AREF} = V_{DDPA} = 3.3 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ . It is verified by design for all other voltages within the defined voltage range. The specified TUE is valid only if the absolute sum of input overload currents on analog port pins (see  $I_{OV}$  specification) does not exceed 10 mA, and if  $V_{AREF}$  and  $V_{AGND}$  remain stable during the measurement time.

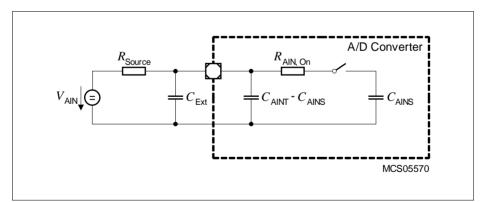

Figure 13 Equivalent Circuitry for Analog Inputs

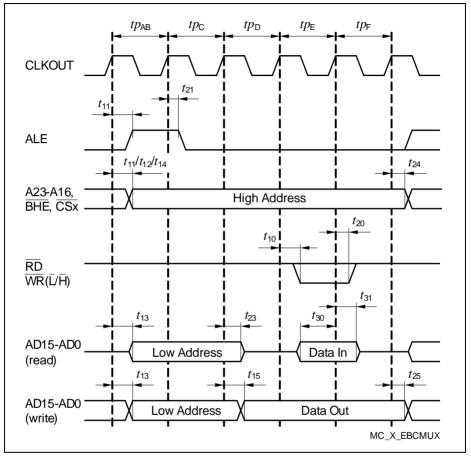

Figure 20 Multiplexed Bus Cycle

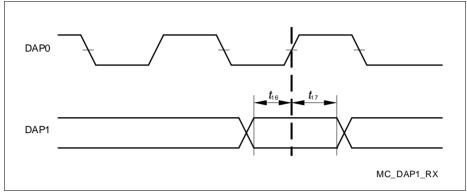

Figure 26 DAP Timing Host to Device

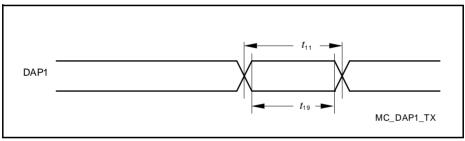

Figure 27 DAP Timing Device to Host

Note: The transmission timing is determined by the receiving debugger by evaluating the sync-request synchronization pattern telegram.