#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                             |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 96KB (96K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 5K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 18x10b                                                                      |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-BQFP                                                                        |

| Supplier Device Package    | 100-QFP (14x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30302fapfp-u5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# RENESAS

# M16C/30P Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

### 1. Overview

The M16C/30P Group of single-chip microcomputers is built using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core and is packaged in a 100-pin plastic molded QFP.

These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, they are capable of executing instructions at high speed. In addition, these microcomputers contain a multiplier and DMAC which combined with fast instruction processing capability, make it suitable for control of various OA, communication, and industrial equipment which requires high-speed arithmetic/ logic operations.

### 1.1 Applications

Audio, cameras, TV, home appliance, office/communications/portable/industrial equipment, etc.

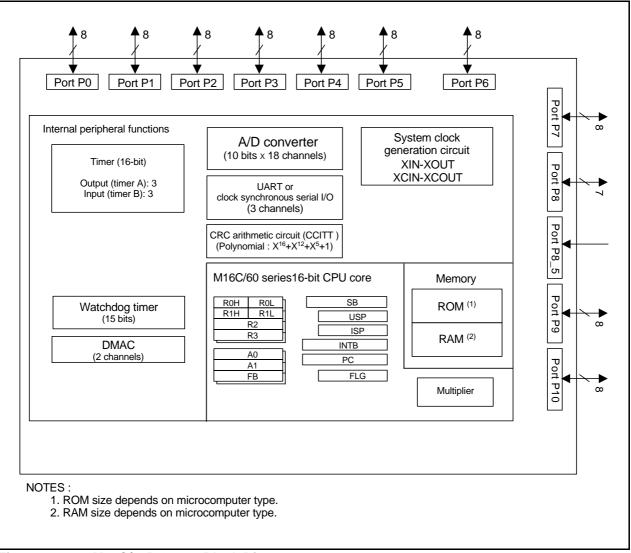

### 1.3 Block Diagram

Figure 1.1 is a M16C/30P Group Block Diagram.

Figure 1.1

M16C/30P Group Block Diagram

#### 1.4 **Product List**

Table 1.2 lists the M16C/30P group products and Figure 1.2 shows the Part No., Memory Size, and Package. Table 1.4 lists Product Code of MASK ROM version for M16C/30P. Figure 1.3 shows the Marking Diagram of Mask ROM Version for M16C/30P (Top View). Table 1.5 lists Product Code of One Time Flash version, Flash Memory version, and ROM-less version for M16C/30P. Figure 1.4 shows the Marking Diagram of One Time Flash version, Flash Memory version, and ROM-less Version for M16C/30P (Top View). Please specify the marking for M16C30P (MASK ROM version) when placing an order for ROM.

| Table 1.2 Proc  |       | . (1)        |              |                  | AS OF March 2007               |

|-----------------|-------|--------------|--------------|------------------|--------------------------------|

| Part No.        |       | ROM Capacity | RAM Capacity | package code (1) | Remarks                        |

| M30302MAP-XXXFF | C     | 96 Kbytes    | 5 Kbytes     | PRQP0100JB-A     | Mask ROM version               |

| M30302MAP-XXXG  | Р     |              |              | PLQP0100KB-A     |                                |

| M30302MCP-XXXF  | C     | 128 Kbytes   |              | PRQP0100JB-A     |                                |

| M30302MCP-XXXG  | Р     |              |              | PLQP0100KB-A     |                                |

| M30302MDP-XXXF  | C     | 160 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302MDP-XXXG  | P     |              |              | PLQP0100KB-A     |                                |

| M30302MEP-XXXFF | C     | 192 Kbytes   | _            | PRQP0100JB-A     |                                |

| M30302MEP-XXXG  | Ρ     |              |              | PLQP0100KB-A     |                                |

| M30302GAPFP     |       | 96 Kbytes    | 5 Kbytes     | PRQP0100JB-A     | One Time Flash                 |

| M30302GAPGP     | (D)   |              |              | PLQP0100KB-A     | version<br>(blank product)     |

| M30302GCPFP     |       | 128 Kbytes   |              | PRQP0100JB-A     |                                |

| M30302GCPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GDPFP     |       | 160 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GDPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30304GDPFP     | (D)   |              | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30304GDPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GEPFP     |       | 192 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GEPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30304GEPFP     | (D)   |              | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30304GEPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GGPFP     | (D)   | 256 Kbytes   | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30302GGPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GAP-XXXFF | )     | 96 Kbytes    | 5 Kbytes     | PRQP0100JB-A     | One Time Flash                 |

| M30302GAPvGP    | (D)   |              |              | PLQP0100KB-A     | version<br>(factory programmed |

| M30302GCP-XXXFF | 2     | 128 Kbytes   |              | PRQP0100JB-A     | product)                       |

| M30302GCP-XXXG  | P (D) | -            |              | PLQP0100KB-A     |                                |

| M30302GDP-XXXFF | 2     | 160 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GDP-XXXG  | P (D) |              |              | PLQP0100KB-A     |                                |

| M30304GDP-XXXFF | р (D) |              | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30304GDP-XXXG  | P (D) |              |              | PLQP0100KB-A     |                                |

| M30302GEP-XXXFF | )     | 192 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GEP-XXXG  | - (D) |              |              | PLQP0100KB-A     | 1                              |

| M30304GEP-XXXFF | P (D) |              | 12 Kbytes    | PRQP0100JB-A     | 1                              |

| M30304GEP-XXXG  | > (D) |              |              | PLQP0100KB-A     | 1                              |

| M30302GGP-XXXF  | P (D) | 256 Kbytes   | 12 Kbytes    | PRQP0100JB-A     | 1                              |

| M30302GGP-XXXG  | P (D) |              |              | PLQP0100KB-A     | 1                              |

#### Table 1.2 **Product List (1)**

As of March 2007

(D): Under development

(P): Under planning

NOTES:

1. Previous package codes are as follows.

PRQP0100JB-A : 100P6S-A, PLQP0100KB-A : 100P6Q-A

2. Block A (4-Kbytes space) is available in flash memory version.

RENESAS

Product Code

|                       | гаскауе             |                                                                                                 |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|

| U1                    | Lead-free           | -20°C to 85°C                                                                                   |

| U4                    |                     | -40°C to 85°C                                                                                   |

|                       |                     |                                                                                                 |

|                       | 3-A (100P6S-A)      |                                                                                                 |

| 1. Standard R         | Renesas Mark        |                                                                                                 |

|                       | N A                 | 1 6 C                                                                                           |

| M3030                 | )2MDP-XX            |                                                                                                 |

| A                     | U 1 X X X X         | X X X — Chip version, product code and date code                                                |

|                       |                     | A : Shows chip version.<br>Henceforth, whenever it changes a version,                           |

| 0                     |                     | it continues with A, B, and C.<br>U1 : Shows Product code. (See <b>table 1.3 Product Code</b> ) |

|                       |                     | XXXXXXX : Seven digits                                                                          |

| 2. Customer's         | s Parts Number + F  | Renesas catalog name                                                                            |

|                       |                     |                                                                                                 |

| M3.0.3(               | 02MDP - XX          | X F P Part No. (See Figure 1.2 Part No., Memory Size, and Package)                              |

|                       | -                   | U 1 ——— Chip version and product code                                                           |

| M <sup>1</sup>        | 16C XXXX            | Henceforth, whenever it changes a version,                                                      |

| 0                     |                     | it continues with A, B, and C.<br>U1 : Shows Product code. (See <b>table 1.3 Product Code</b> ) |

| L                     |                     | Date code seven digits                                                                          |

|                       |                     |                                                                                                 |

| PLQP0100KE            | 3-A (100P6Q-A)      |                                                                                                 |

| 1. Standard F         | Renesas Mark        |                                                                                                 |

|                       |                     |                                                                                                 |

|                       | M16C                |                                                                                                 |

| M 3                   | 0 3 0 2 MD P        | Part No. (See Figure 1.2 Part No., Memory Size, and Package)                                    |

| A U 1                 | - XXXGP<br>XXXXXXX  | - Chip version, product code and date code                                                      |

|                       |                     | A : Shows chip version.<br>Henceforth, whenever it changes a version,                           |

| 0                     |                     | it continues with A, B, and C.                                                                  |

|                       |                     | U1 : Shows Product code. (See <b>table 1.3 Product Code</b> )<br>XXXXXXX : Seven digits         |

| 2. Customer'          | 's Parts Number + I | Renesas catalog name                                                                            |

|                       |                     |                                                                                                 |

|                       |                     |                                                                                                 |

| М 3                   | 0 3 0 2 M D P       | — Part No. (See Figure 1.2 Part No., Memory Size, and Package)                                  |

| A U 1                 | - XXXGP             | Chip version and product code     A : Shows chip version.                                       |

|                       |                     | Henceforth, whenever it changes a version,<br>it continues with A, B, and C.                    |

| 0                     |                     | U1 : Shows Product code. (See <b>table 1.3 Product Code</b> )                                   |

| L                     |                     | — Date code seven digits                                                                        |

|                       |                     |                                                                                                 |

| NOTES:<br>1. Refer to | o the mark specific | cation form for details of the Mask ROM version marking.                                        |

|                       |                     |                                                                                                 |

| ure 1.3 N             | larking Diagra      | m of Mask ROM Version for M16C/30P (Top View)                                                   |

Package

**Operating Ambient Temperature**

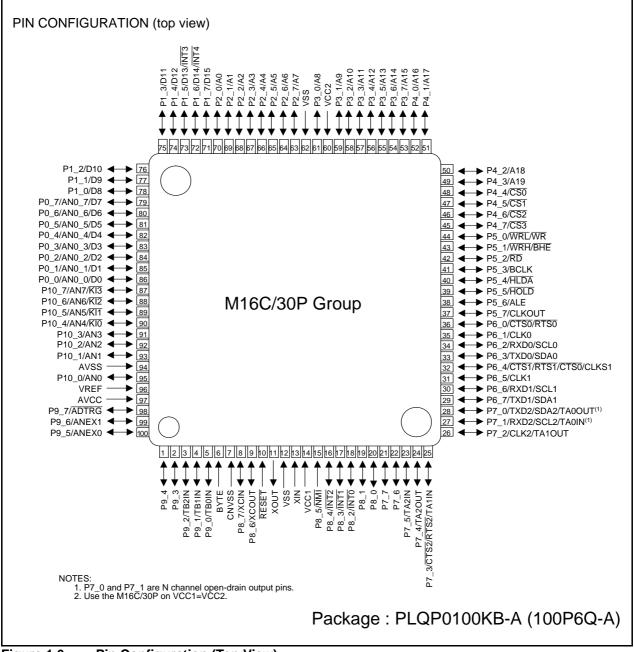

Figure 1.6 Pin Configuration (Top View)

RENESAS

| Signal Name                  | Pin Name                                                                                                                                              | I/O Type | Description                                                                                                                                                                                                                                                                                      |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main clock                   | XIN                                                                                                                                                   | I        | I/O pins for the main clock generation circuit. Connect a ceramic                                                                                                                                                                                                                                |

| input                        |                                                                                                                                                       |          | resonator or crystal oscillator between XIN and XOUT. To use the                                                                                                                                                                                                                                 |

| Main clock<br>output         | XOUT                                                                                                                                                  | 0        | external clock, input the clock from XIN and leave XOUT open.                                                                                                                                                                                                                                    |

| Sub clock<br>input           | XCIN                                                                                                                                                  | Ι        | I/O pins for a sub clock oscillation circuit. Connect a crystal oscillator between XCIN and XCOUT. To use the external clock, input the clock                                                                                                                                                    |

| Sub clock<br>output          | XCOUT                                                                                                                                                 | 0        | from XCIN and leave XCOUT open.                                                                                                                                                                                                                                                                  |

| Clock output                 | CLKOUT                                                                                                                                                | 0        | The clock of the same cycle as fC, f8, or f32 is outputted.                                                                                                                                                                                                                                      |

| INT interrupt input          | INT0 to INT4                                                                                                                                          | Ι        | Input pins for the INT interrupt.                                                                                                                                                                                                                                                                |

| NMI interrupt input          | NMI                                                                                                                                                   | Ι        | Input pin for the NMI interrupt.                                                                                                                                                                                                                                                                 |

| Key input<br>interrupt input | KI0 to KI3                                                                                                                                            | I        | Input pins for the key input interrupt.                                                                                                                                                                                                                                                          |

| Timer A                      | TA0OUT to<br>TA2OUT                                                                                                                                   | I/O      | These are timer A0 to timer A2 I/O pins. (however, the output of TA0OUT for the N-channel open drain output.)                                                                                                                                                                                    |

|                              | TA0IN to TA2IN                                                                                                                                        | Ι        | These are timer A0 to timer A2 input pins.                                                                                                                                                                                                                                                       |

| Timer B                      | TB0IN to TB2IN                                                                                                                                        | Ι        | These are timer B0 to timer B2 input pins.                                                                                                                                                                                                                                                       |

| Serial                       | CTS0 to CTS2                                                                                                                                          | Ι        | These are send control input pins.                                                                                                                                                                                                                                                               |

| interface                    | RTS0 to RTS2                                                                                                                                          | 0        | These are receive control output pins.                                                                                                                                                                                                                                                           |

|                              | CLK0 to CLK2                                                                                                                                          | I/O      | These are transfer clock I/O pins.                                                                                                                                                                                                                                                               |

|                              | RXD0 to RXD2                                                                                                                                          | I        | These are serial data input pins.                                                                                                                                                                                                                                                                |

|                              | TXD0 to TXD2                                                                                                                                          | 0        | These are serial data output pins. (however, TXD2 for the N-channel open drain output.)                                                                                                                                                                                                          |

|                              | CLKS1                                                                                                                                                 | 0        | This is output pin for transfer clock output from multiple pins function.                                                                                                                                                                                                                        |

| I <sup>2</sup> C mode        | SDA0 to SDA2                                                                                                                                          | I/O      | These are serial data I/O pins. (however, SDA2 for the N-channel open drain output.)                                                                                                                                                                                                             |

|                              | SCL0 to SCL2                                                                                                                                          | I/O      | These are transfer clock I/O pins. (however, SCL2 for the N-channel open drain output.)                                                                                                                                                                                                          |

| Reference<br>voltage input   | VREF                                                                                                                                                  | Ι        | Applies the reference voltage for the A/D converter.                                                                                                                                                                                                                                             |

| A/D converter                | AN0 to AN7,<br>AN0_0 to AN0_7                                                                                                                         | Ι        | Analog input pins for the A/D converter.                                                                                                                                                                                                                                                         |

|                              | ADTRG                                                                                                                                                 | I        | This is an A/D trigger input pin.                                                                                                                                                                                                                                                                |

|                              | ANEX0                                                                                                                                                 | I/O      | This is the extended analog input pin for the A/D converter, and is the output in external op-amp connection mode.                                                                                                                                                                               |

|                              | ANEX1                                                                                                                                                 | Ι        | This is the extended analog input pin for the A/D converter.                                                                                                                                                                                                                                     |

| I/O port                     | P0_0 to P0_7,<br>P1_0 to P1_7,<br>P2_0 to P2_7,<br>P3_0 to P3_7,<br>P4_0 to P4_7,<br>P5_0 to P5_7,<br>P6_0 to P6_7,<br>P7_0 to P7_7,<br>P9_0 to P9_7, | I/O      | 8-bit I/O ports in CMOS, having a direction register to select an input<br>or output.<br>Each pin is set as an input port or output port. An input port can be set<br>for a pull-up or for no pull-up in 4-bit unit by program. (however, P7_0<br>and P7_1 for the N-channel open drain output.) |

|                              | P10_0 to P10_7<br>P8_0 to P8_4,<br>P8_6, P8_7                                                                                                         | I/O      | I/O ports having equivalent functions to P0.                                                                                                                                                                                                                                                     |

| Input port                   | P8_5                                                                                                                                                  | I        | Input pin for the $\overline{\text{NMI}}$ interrupt. Pin states can be read by the P8_5 bit in the P8 register.                                                                                                                                                                                  |

Table 1.9Pin Description (2)

I : Input O : Output I/O : Input and output

## 2. Central Processing Unit (CPU)

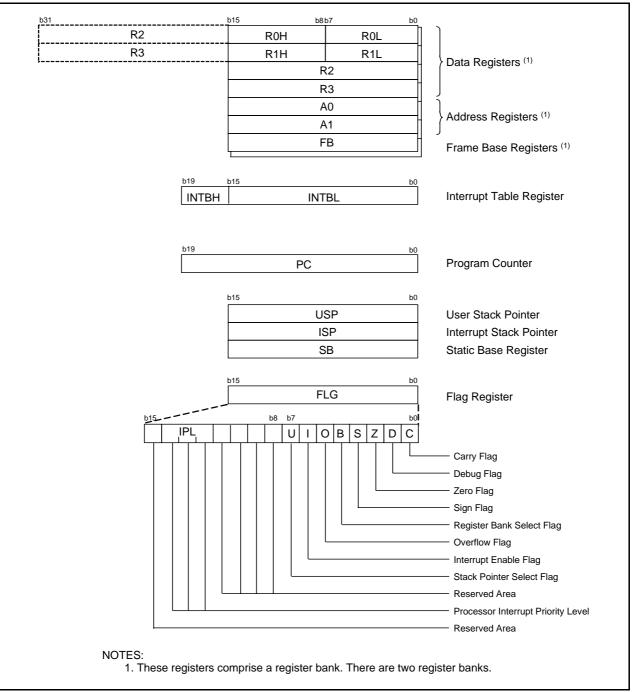

Figure 2.1 shows the CPU registers. The CPU has 13 registers. Of these, R0, R1, R2, R3, A0, A1 and FB comprise a register bank. There are two register banks.

### 2.1 Data Registers (R0, R1, R2 and R3)

The R0 register consists of 16 bits, and is used mainly for transfers and arithmetic/logic operations. R1 to R3 are the same as R0.

The R0 register can be separated between high (R0H) and low (R0L) for use as two 8-bit data registers.

R1H and R1L are the same as R0H and R0L. Conversely, R2 and R0 can be combined for use as a 32-bit data register (R2R0). R3R1 is the same as R2R0.

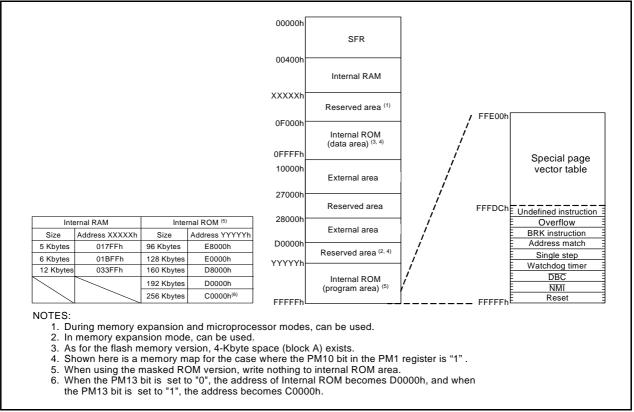

### 3. Memory

Figure 3.1 is a Memory Map of the M16C/30P group. The address space extends the 1 Mbyte from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a 64-Kbyte internal ROM is allocated to the addresses from F0000h to FFFFFh.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a 5-Kbyte internal RAM is allocated to the addresses from 00400h to 017FFh. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated. The SFR is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by the JMPS or JSRS instruction. For details, refer to the M16C/60 and M16C/20 Series Software Manual.

Figure 3.1 Memory Map

| O wash a l | Derometor                               |                                                                                                                                                                              |        | Linit  |            |      |

|------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|------|

| Symbol     |                                         | Parameter                                                                                                                                                                    | Min.   | Тур.   | Max.       | Unit |

| Vcc        | Supply Voltage (\                       | /cc1=Vcc2)                                                                                                                                                                   | 2.7    | 5.0    | 5.5        | V    |

| AVcc       | Analog Supply Vo                        | bltage                                                                                                                                                                       |        | Vcc    |            | V    |

| Vss        | Supply Voltage                          |                                                                                                                                                                              | 0      |        |            | V    |

| AVss       | Analog Supply Vo                        | bltage                                                                                                                                                                       |        | 0      |            | V    |

| Viн        | HIGH Input                              | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7                                                                                                                                     | 0.8Vcc |        | Vcc        | V    |

|            | Voltage                                 | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(during single-chip mode)                                                                                                  | 0.8Vcc |        | Vcc        | V    |

|            |                                         | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input during memory expansion and microprocessor mode)                                                               | 0.5Vcc |        | Vcc        | V    |

|            |                                         | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, XIN, RESET, CNVSS, BYTE                                                                           | 0.8Vcc |        | Vcc        | V    |

|            |                                         | P7_0, P7_1                                                                                                                                                                   | 0.8Vcc |        | 6.5        | V    |

| VIL        | LOW Input                               | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7                                                                                                                                     | 0      |        | 0.2Vcc     | V    |

|            | Voltage                                 | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(during single-chip mode)                                                                                                  | 0      |        | 0.2Vcc     | V    |

|            |                                         | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input during memory expansion and microprocessor mode)                                                               | 0      |        | 0.16Vcc    | V    |

|            |                                         | P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7, XIN, RESET, CNVSS, BYTE                                                                                              | 0      |        | 0.2Vcc     | V    |

| IOH(peak)  | HIGH Peak<br>Output Current             | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | -10.0      | mA   |

| IOH(avg)   | HIGH Average<br>Output Current          | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | -5.0       | mA   |

| IOL(peak)  | LOW Peak<br>Output Current              | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | 10.0       | mA   |

| IOL(avg)   | LOW Average<br>Output Current           | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | 5.0        | mA   |

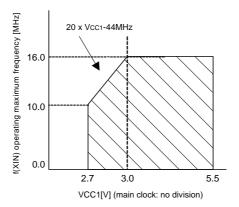

| f(XIN)     | Main Clock Input                        | VCC=3.0V to 5.5V                                                                                                                                                             | 0      |        | 16         | MHz  |

|            | Oscillation<br>Frequency <sup>(4)</sup> | VCC=2.7V to 3.0V                                                                                                                                                             | 0      |        | 20×Vcc1-44 | MHz  |

| f(XCIN)    | Sub-Clock Oscilla                       | ation Frequency                                                                                                                                                              |        | 32.768 | 50         | kHz  |

| f(BCLK)    | CPU Operation C                         | lock                                                                                                                                                                         | 0      |        | 16         | MHz  |

| Table 5.2 | Recommended Operating Conditions (1) |

|-----------|--------------------------------------|

|-----------|--------------------------------------|

NOTES:

1. Referenced to Vcc1 = Vcc2 = 2.7 to 5.5V at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified.

2. The Average Output Current is the mean value within 100ms.

The total IoL(peak) for ports P0, P1, P2, P8\_6, P8\_7, P9 and P10 must be 80mA max. The total IoL(peak) for ports P3, P4, P5, P6, P7 and P8\_0 to P8\_4 must be 80mA max. The total IOH(peak) for ports P0, P1, and P2 must be -40mA max. The total IOH(peak) for ports P3, P4 and P5 must be -40mA max. The total IOH(peak) for ports P6, P7, and P8\_0 to P8\_4 must be -40mA max.

The total IOH(peak) for ports P8\_6, P8\_7 and P9 must be -40mA max. Set Average Output Current to 1/2 of peak.

4. Relationship between main clock oscillation frequency, and supply voltage.

#### Main clock input oscillation frequency

| Symbol  | Parameter                                                          | Measuring Condition | Standard |      |      | Unit |

|---------|--------------------------------------------------------------------|---------------------|----------|------|------|------|

| Symbol  | Falance                                                            | Measuring Condition | Min.     | Тур. | Max. | Onit |

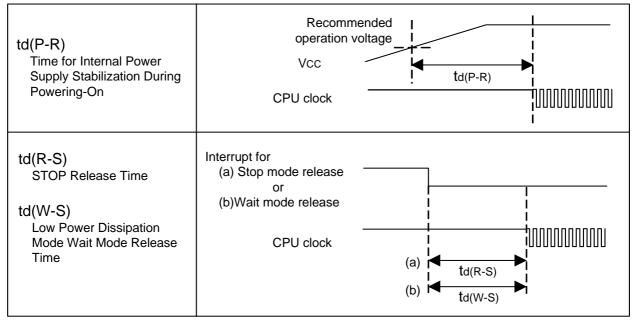

| td(P-R) | Time for Internal Power Supply Stabilization<br>During Powering-On | Vcc=2.7V to 5.5V    |          |      | 2    | ms   |

| td(R-S) | STOP Release Time                                                  |                     |          |      | 1500 | μs   |

| td(W-S) | Low Power Dissipation Mode Wait Mode<br>Release Time               |                     |          |      | 1500 | μs   |

Figure 5.1 Power Supply Circuit Timing Diagram

| Symbol | Doromot                                          | Parameter Measuring Condition Standard | Standard                                   |                                                                             | Unit |      |      |      |

|--------|--------------------------------------------------|----------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------|------|------|------|------|

| Symbol |                                                  |                                        | Measuring Condition                        |                                                                             | Min. | Тур. | Max. | Unit |

| Icc    | Power Supply Current<br>(Vcc1=Vcc2=4.0V to 5.5V) | In single-chip mode, the output        | Mask ROM                                   | f(XIN)=16MHz<br>No division                                                 |      | 10   | 15   | mA   |

|        |                                                  | pins are open and other pins are Vss   | One Time<br>Flash                          | f(XIN)=16MHz,<br>No division                                                |      | 10   | 18   | mA   |

|        |                                                  |                                        | Flash<br>Memory                            | f(XIN)=16MHz,<br>No division                                                |      | 12   | 18   | mA   |

|        |                                                  |                                        | One Time<br>Flash                          | f(XIN)=10MHz,<br>VCC1=5.0V                                                  |      | 15   |      | mA   |

|        |                                                  |                                        | Flash Memory<br>Program                    | f(XIN)=10MHz,<br>VCC1=5.0V                                                  |      | 15   |      | mA   |

|        |                                                  |                                        | Flash Memory<br>Erase                      | f(XIN)=10MHz,<br>VCC1=5.0V                                                  |      | 25   |      | mA   |

|        |                                                  |                                        | Mask ROM                                   | f(XCIN)=32kHz<br>Low power dissipation<br>mode, ROM <sup>(3)</sup>          |      | 25   |      | μA   |

|        |                                                  |                                        | One Time<br>Flash                          | f(XCIN)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |      | 25   |      | μA   |

|        |                                                  |                                        |                                            | f(XCIN)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |      | 350  |      | μA   |

|        |                                                  |                                        | Flash Memory                               | f(XCIN)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |      | 25   |      | μA   |

|        |                                                  |                                        |                                            | f(XCIN)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |      | 420  |      | μA   |

|        |                                                  |                                        | Mask ROM<br>One Time Flash<br>Flash Memory | f(XCIN)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability High  |      | 7.5  |      | μA   |

|        |                                                  |                                        | r asir memory                              | f(XCIN)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability Low   |      | 2.0  |      | μΑ   |

|        |                                                  |                                        |                                            | Stop mode<br>Topr =25°C                                                     |      | 0.8  | 3.0  | μA   |

Table 5.10 Electrical Characteristics (2) (1)

NOTES:

1. Referenced to Vcc1=Vcc2=4.2 to 5.5V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(XIN)=16MHz unless otherwise specified.

2. With one timer operated using fC32.

3. This indicates the memory in which the program to be executed exists.

# VCC1=VCC2=5V

#### **Timing Requirements**

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

#### Table 5.19 Timer B Input (Counter Input in Event Counter Mode)

| Symbol  | Parameter                                            | Star | Standard |      |  |

|---------|------------------------------------------------------|------|----------|------|--|

|         | Parameter                                            |      | Max.     | Unit |  |

| tc(TB)  | TBiIN Input Cycle Time (counted on one edge)         | 100  |          | ns   |  |

| tw(TBH) | TBiIN Input HIGH Pulse Width (counted on one edge)   | 40   |          | ns   |  |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on one edge)    | 40   |          | ns   |  |

| tc(TB)  | TBiIN Input Cycle Time (counted on both edges)       | 200  |          | ns   |  |

| tw(TBH) | TBiIN Input HIGH Pulse Width (counted on both edges) | 80   |          | ns   |  |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on both edges)  | 80   |          | ns   |  |

#### Table 5.20 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Stan | Unit |      |

|---------|------------------------------|------|------|------|

|         | Farameter                    | Min. | Max. | Unit |

| tc(TB)  | TBiIN Input Cycle Time       | 400  |      | ns   |

| tw(TBH) | TBiIN Input HIGH Pulse Width | 200  |      | ns   |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200  |      | ns   |

#### Table 5.21 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    | Stan | Unit |       |  |

|---------|------------------------------|------|------|-------|--|

| Symbol  | Falameter                    | Min. | Max. | Offic |  |

| tc(TB)  | TBiIN Input Cycle Time       | 400  |      | ns    |  |

| tw(TBH) | TBilN Input HIGH Pulse Width | 200  |      | ns    |  |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200  |      | ns    |  |

#### Table 5.22 A/D Trigger Input

| Symbol  | Parameter                   | Stan | Unit |      |

|---------|-----------------------------|------|------|------|

| Symbol  | Falameter                   |      | Max. | Unit |

| tc(AD)  | ADTRG Input Cycle Time      | 1000 |      | ns   |

| tw(ADL) | ADTRG input LOW Pulse Width | 125  |      | ns   |

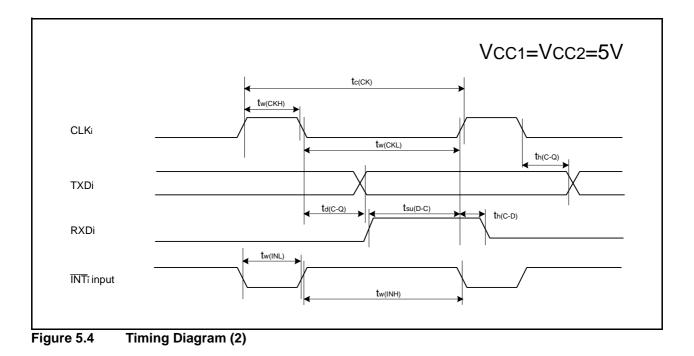

#### Table 5.23 Serial Interface

| Symbol   | Parameter                       | Stan | Unit  |       |  |

|----------|---------------------------------|------|-------|-------|--|

| Symbol   | Falametei                       | Min. | Max.  | Offic |  |

| tc(CK)   | CLKi Input Cycle Time 200       |      |       |       |  |

| tw(CKH)  | CLKi Input HIGH Pulse Width 100 |      |       |       |  |

| tw(CKL)  | CLKi Input LOW Pulse Width 100  |      |       |       |  |

| td(C-Q)  | TXDi Output Delay Time          |      | 80 ns |       |  |

| th(C-Q)  | TXDi Hold Time                  | 0    | ns    |       |  |

| tsu(D-C) | RXDi Input Setup Time           | 70   |       | ns    |  |

| th(C-D)  | RXDi Input Hold Time 90         |      |       |       |  |

### Table 5.24 External Interrupt INTi Input

| Symbol  | Parameter                   | Stan | Unit |      |

|---------|-----------------------------|------|------|------|

| Symbol  | Symbol Parameter            |      | Max. | Onit |

| tw(INH) | INTi Input HIGH Pulse Width | 250  |      | ns   |

| tw(INL) | INTi Input LOW Pulse Width  | 250  |      | ns   |

# VCC1=VCC2=5V

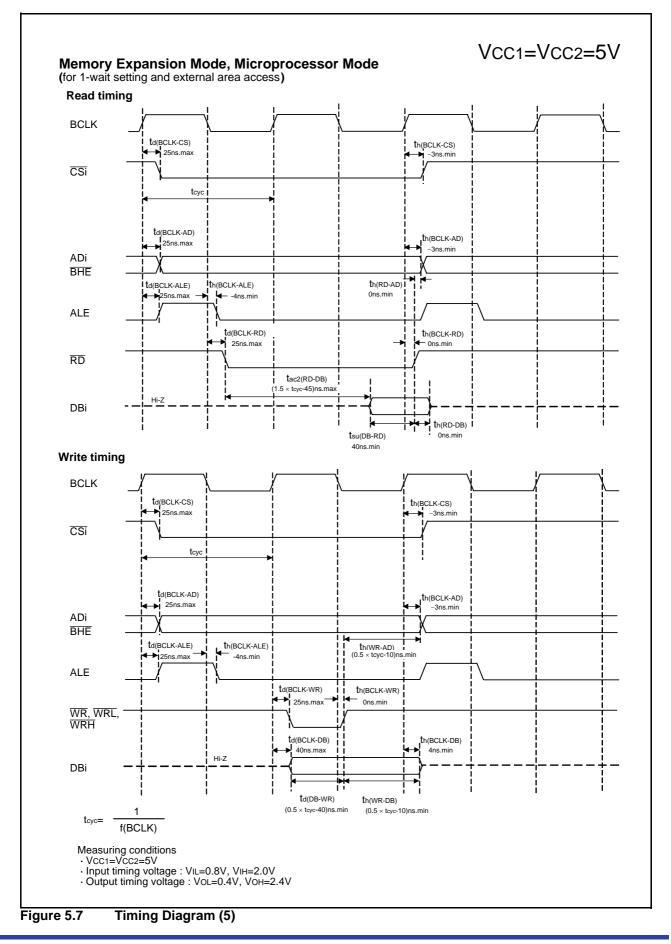

#### Switching Characteristics

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 5.26 | Memory Expansion and Microprocessor Modes (for 1 wait setting and external area |

|------------|---------------------------------------------------------------------------------|

|            | access)                                                                         |

| Cumbal        | Parameter                                                |                                  | Stan     | dard | Unit |  |  |

|---------------|----------------------------------------------------------|----------------------------------|----------|------|------|--|--|

| Symbol        | Falameter                                                |                                  | Min.     | Max. |      |  |  |

| td(BCLK-AD)   | Address Output Delay Time                                |                                  |          | 25   | ns   |  |  |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)           |                                  | -3       |      | ns   |  |  |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)             |                                  | 0        |      | ns   |  |  |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)             |                                  | (NOTE 2) |      | ns   |  |  |

| td(BCLK-CS)   | Chip Select Output Delay Time                            |                                  |          | 25   | ns   |  |  |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)       |                                  | -3       |      | ns   |  |  |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                             | 15                               |          |      |      |  |  |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                              | -4                               |          |      |      |  |  |

| td(BCLK-RD)   | RD Signal Output Delay Time                              | Durput Delay Time See Figure 5.2 |          |      |      |  |  |

| th(BCLK-RD)   | RD Signal Output Hold Time                               | i igure 5.2                      | 0        |      | ns   |  |  |

| td(BCLK-WR)   | WR Signal Output Delay Time                              |                                  | ns       |      |      |  |  |

| th(BCLK-WR)   | WR Signal Output Hold Time                               |                                  | 0        |      | ns   |  |  |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)             |                                  |          | 40   | ns   |  |  |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)          |                                  | ns       |      |      |  |  |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)               |                                  | (NOTE 1) |      | ns   |  |  |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) <sup>(3)</sup> |                                  | (NOTE 2) |      | ns   |  |  |

| td(BCLK-HLDA) | HLDA Output Delay Time                                   |                                  |          | 40   | ns   |  |  |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5)x10^9}{f(BCLK)} - 40[ns] \qquad n \text{ is ``1'' for 1-wait setting, } f(BCLK) \text{ is 12.5MHz or less.}$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

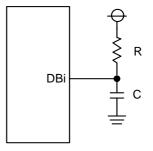

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in t = -CR X ln (1-VoL / Vcc1) by a circuit of the right figure. For example, when VoL = 0.2Vcc1, C = 30pF, R = 1kΩ, hold time of output "L" level is t = -30pF X 1kΩ X ln(1-0.2Vcc1 / Vcc1)

= 6.7ns.

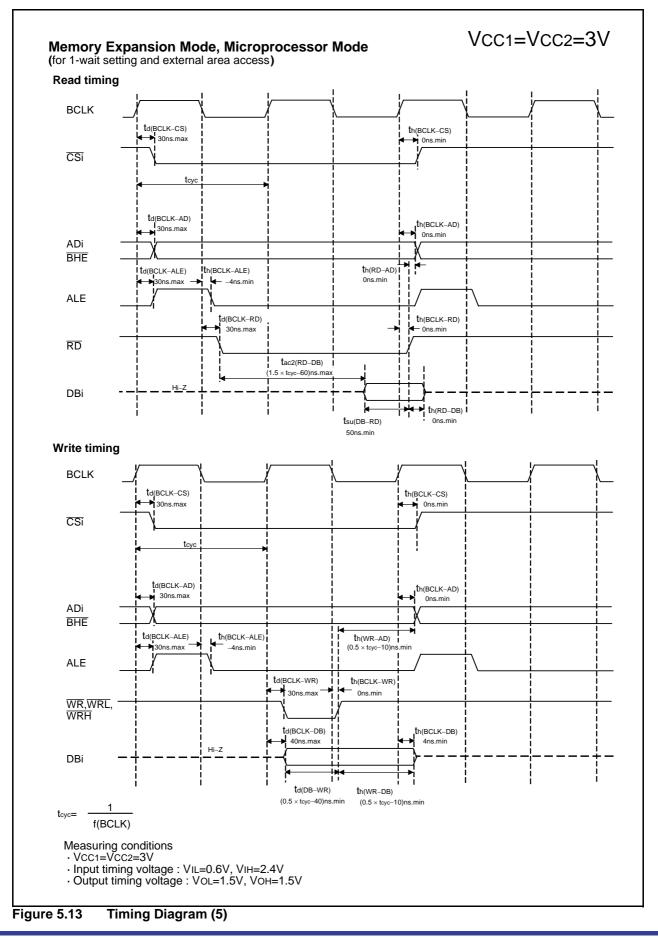

# VCC1=VCC2=3V

#### Timing Requirements

#### (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

#### Table 5.29 External Clock Input (XIN input)

| Symbol | Parameter                             | Stan     | Unit     |      |

|--------|---------------------------------------|----------|----------|------|

| Symbol | Falametei                             |          | Max.     | Onit |

| tc     | External Clock Input Cycle Time       | (NOTE 2) |          | ns   |

| ťw(H)  | External Clock Input HIGH Pulse Width | (NOTE 3) |          | ns   |

| tw(L)  | External Clock Input LOW Pulse Width  | (NOTE 3) |          | ns   |

| tr     | External Clock Rise Time              |          | (NOTE 4) | ns   |

| tr     | External Clock Fall Time              |          | (NOTE 4) | ns   |

NOTES:

- 1. The condition is Vcc1=Vcc2=2.7 to 3.0V.

- 2. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_{1} - 44}$$

[ns]

3. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_{1}-44} \times 0.4$$

[ns]

4. Calculated according to the VCC1 voltage as follows:  $-10 \times Vcc1 + 45$  [ns]

#### Table 5.30 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                                  | Stan | Unit |      |  |  |

|----------------|------------------------------------------------------------|------|------|------|--|--|

| Symbol         | Farameter                                                  | Min. | Max. | Unit |  |  |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait) (NOTE 1) |      |      |      |  |  |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait) (NOTE 2)    |      |      |      |  |  |

| tsu(DB-RD)     | Data Input Setup Time                                      | 50   | ns   |      |  |  |

| tsu(RDY-BCLK)  | RDY Input Setup Time                                       | 40   | ns   |      |  |  |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                                      | 50   | ns   |      |  |  |

| th(RD-DB)      | Data Input Hold Time                                       | 0 r  |      |      |  |  |

| th(BCLK-RDY)   | RDY Input Hold Time                                        | 0 ns |      |      |  |  |

| th(BCLK-HOLD)  | HOLD Input Hold Time                                       | 0    | ns   |      |  |  |

NOTES:

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 60[ns]$$

n is "2" for 1-wait setting

| F         | REVISION HISTORY |             | RY                                                                                                                           | M16C/30P Group Datasheet                                                                                                                        |  |  |

|-----------|------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev. Date |                  | Description |                                                                                                                              | Description                                                                                                                                     |  |  |

| Rev.      | Dale             | Page        |                                                                                                                              | Summary                                                                                                                                         |  |  |

| 1.20      | Oct 17, 2006     | 1           | Note is pa                                                                                                                   | lote is partly deleted.                                                                                                                         |  |  |

|           |                  | 2           | Table 1.1                                                                                                                    | Performance Outline of M16C/30P Group is partly added.                                                                                          |  |  |

|           |                  | 4           | Table 1.2                                                                                                                    | Product List is partly revised.                                                                                                                 |  |  |

|           |                  | 5           | Figure 1.2                                                                                                                   | 2 Type No., Memory Size, and Package is added.                                                                                                  |  |  |

|           |                  | 7           |                                                                                                                              | Product Code of One Time Flash version, Flash Memory ver-                                                                                       |  |  |

|           |                  | 17          |                                                                                                                              | ROM-less version for M16C/30P is partly added.<br>1 Memory Map is partly added.                                                                 |  |  |

|           |                  | 19          | -                                                                                                                            |                                                                                                                                                 |  |  |

|           |                  |             |                                                                                                                              | SFR Information (2) is partly added.                                                                                                            |  |  |

|           |                  | 23          |                                                                                                                              | Absolute Maximum Ratings is partly added.                                                                                                       |  |  |

|           |                  | 27          | Table 5.7                                                                                                                    | One Time Flash Version Electrical Characteristics and<br>One Time Flash Version Program Voltage and Read Operation<br>characteristics is added. |  |  |

|           |                  | 30          | Table 5.1                                                                                                                    | 0 Electrical Characteristics (2) is partly added.                                                                                               |  |  |

|           |                  | 42          | Table 5.2                                                                                                                    | 8 Electrical Characteristics (2) is partly added.                                                                                               |  |  |

| 1.21      | Nov 02 2006      | 7           | Table 1.4 Product Code of One Time Flash version, Flash Memory version, and ROM-less version for M16C/30P is partly revised. |                                                                                                                                                 |  |  |

| 1.22      | Mar 30, 2007     | 4           | Table 1.2 Product List (1) is partly revised.                                                                                |                                                                                                                                                 |  |  |

|           |                  | 5           | Table 1.3                                                                                                                    | Product List (2) is partly revised.                                                                                                             |  |  |

|           |                  | 19          | Table 4.2                                                                                                                    | SFR Information (2) is partly revised.                                                                                                          |  |  |

### RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scule as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in this document, included in this document for the purpose of military application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulations.

All information included in this document, such as product data, diagrams, charts, programs, algorithms, and application carcuit examples, is current as of the data the discovered in this document, but Renesas as an evel and inferent information in the data current for the purpose of any data programs. Algorithms, and application is activate and the data that the data discovered in this document, but Renesas as and the data different information in the data discovered in this document, but Renesas as such as the development of the purpose of any damages incurred as a set easonable care in compling the information in this document, but Renesas as and the data different information in the data discovered in the data discovered in the data discovered in the data durate internation in the data different information inclata din the data different informat

#### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

#### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

#### Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com