Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Not For New Designs                                                             |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | M16C/60                                                                         |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 16MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                             |

| Peripherals                | DMA, POR, PWM, WDT                                                              |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 96KB (96K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 4K x 8                                                                          |

| RAM Size                   | 5K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 18x10b                                                                      |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30302fapgp-u5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# RENESAS

# M16C/30P Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

# 1. Overview

The M16C/30P Group of single-chip microcomputers is built using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core and is packaged in a 100-pin plastic molded QFP.

These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, they are capable of executing instructions at high speed. In addition, these microcomputers contain a multiplier and DMAC which combined with fast instruction processing capability, make it suitable for control of various OA, communication, and industrial equipment which requires high-speed arithmetic/ logic operations.

# 1.1 Applications

Audio, cameras, TV, home appliance, office/communications/portable/industrial equipment, etc.

# **1.2** Performance Outline

Table 1.1 lists Performance Outline of M16C/30P Group.

| Table 1.1 P | Performance Ou | utline of M160 | C/30P Group |

|-------------|----------------|----------------|-------------|

|-------------|----------------|----------------|-------------|

|                        | Item                            | Performance                                                                        |  |  |  |

|------------------------|---------------------------------|------------------------------------------------------------------------------------|--|--|--|

| CPU                    | Number of Basic Instructions    | 91 instructions                                                                    |  |  |  |

|                        | Minimum Instruction             | 62.5ns(f(XIN)=16MHz, VCC1=VCC2=3.0 to 5.5V, no wait)                               |  |  |  |

|                        | Execution Time                  | 100ns(f(XIN)=10MHz, VCC1=VCC2=2.7 to 5.5V, no wait)                                |  |  |  |

|                        | Operation Mode                  | Single-chip, memory expansion and microprocessor                                   |  |  |  |

|                        |                                 | mode                                                                               |  |  |  |

|                        | Memory Space                    | 1 Mbyte                                                                            |  |  |  |

|                        | Memory Capacity                 | See Table 1.2 Product List                                                         |  |  |  |

| Peripheral             | Port                            | Input/Output : 87 pins, Input : 1 pin                                              |  |  |  |

| Function               | Multifunction Timer             | Timer A : 16 bits x 3 channels,                                                    |  |  |  |

|                        |                                 | Timer B : 16 bits x 3 channels                                                     |  |  |  |

|                        | Serial Interface                | 1 channels                                                                         |  |  |  |

|                        |                                 | Clock synchronous, UART, I <sup>2</sup> CBus <sup>(1)</sup> , IEBus <sup>(2)</sup> |  |  |  |

|                        |                                 | 2 channels                                                                         |  |  |  |

|                        |                                 | Clock synchronous, UART, I <sup>2</sup> CBus <sup>(1)</sup>                        |  |  |  |

|                        | A/D Converter                   | 10-bit A/D converter: 1 circuit, 18 channels                                       |  |  |  |

|                        | DMAC                            | 2 channels                                                                         |  |  |  |

|                        | CRC Calculation Circuit         | CCITT-CRC                                                                          |  |  |  |

| _                      | Watchdog Timer                  | 15 bits x 1 channel (with prescaler)                                               |  |  |  |

|                        | Interrupt                       | Internal: 20 sources, External: 7 sources, Software: 4                             |  |  |  |

|                        |                                 | sources, Priority level: 7 levels                                                  |  |  |  |

|                        | Clock Generating Circuit        | 2 circuits                                                                         |  |  |  |

|                        |                                 | Main clock generation circuit (*),                                                 |  |  |  |

|                        |                                 | Subclock generation circuit (*),                                                   |  |  |  |

|                        |                                 | (*)Equipped with a built-in feedback resistor.                                     |  |  |  |

| Electric               | Supply Voltage                  | VCC1=VCC2=3.0 to 5.5 V (f(XIN)=16MHz)                                              |  |  |  |

| Characteristics        |                                 | VCC1=VCC2=2.7 to 5.5 V (f(XIN)=10MHz, no wait)                                     |  |  |  |

|                        | Power Consumption               | 10 mA (VCC1=VCC2=5V, f(XIN)=16MHz)                                                 |  |  |  |

|                        |                                 | 8 mA (VCC1=VCC2=3V, f(XIN)=10MHz)                                                  |  |  |  |

|                        |                                 | 1.8 μA (VCC1=VCC2=3V, f(XCIN)=32kHz, wait mode)                                    |  |  |  |

|                        |                                 | 0.7 μA(VCC1=VCC2=3V, stop mode)                                                    |  |  |  |

| One time flash version | Program Supply Voltage          | 3.3±0.3 V or 5.0±0.5 V                                                             |  |  |  |

| Flash memory version   | Program/Erase Supply<br>Voltage | 3.3±0.3 V or 5.0±0.5 V                                                             |  |  |  |

|                        | Program and Erase<br>Endurance  | 100 times (all area)                                                               |  |  |  |

| Operating Ambi         | ent Temperature                 | -20 to 85°C, -40 to 85°C                                                           |  |  |  |

| Package                |                                 | 100-pin plastic mold QFP, LQFP                                                     |  |  |  |

NOTES:

1. I<sup>2</sup>C bus is a registered trademark of Koninklijke Philips Electronics N. V.

2. IEBus is a registered trademark of NEC Electronics Corporation.

3. Use the M16C/30P on VCC1 = VCC2.

### 1.4 **Product List**

Table 1.2 lists the M16C/30P group products and Figure 1.2 shows the Part No., Memory Size, and Package. Table 1.4 lists Product Code of MASK ROM version for M16C/30P. Figure 1.3 shows the Marking Diagram of Mask ROM Version for M16C/30P (Top View). Table 1.5 lists Product Code of One Time Flash version, Flash Memory version, and ROM-less version for M16C/30P. Figure 1.4 shows the Marking Diagram of One Time Flash version, Flash Memory version, and ROM-less Version for M16C/30P (Top View). Please specify the marking for M16C30P (MASK ROM version) when placing an order for ROM.

| Table 1.2 Proc  |       | . (1)        |              |                  | AS OF March 2007               |

|-----------------|-------|--------------|--------------|------------------|--------------------------------|

| Part No.        |       | ROM Capacity | RAM Capacity | package code (1) | Remarks                        |

| M30302MAP-XXXFF | C     | 96 Kbytes    | 5 Kbytes     | PRQP0100JB-A     | Mask ROM version               |

| M30302MAP-XXXG  | Р     |              |              | PLQP0100KB-A     |                                |

| M30302MCP-XXXF  | C     | 128 Kbytes   |              | PRQP0100JB-A     |                                |

| M30302MCP-XXXG  | Р     |              |              | PLQP0100KB-A     |                                |

| M30302MDP-XXXF  | C     | 160 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302MDP-XXXG  | P     |              |              | PLQP0100KB-A     |                                |

| M30302MEP-XXXFF | C     | 192 Kbytes   | _            | PRQP0100JB-A     |                                |

| M30302MEP-XXXG  | Р     |              |              | PLQP0100KB-A     |                                |

| M30302GAPFP     |       | 96 Kbytes    | 5 Kbytes     | PRQP0100JB-A     | One Time Flash                 |

| M30302GAPGP     | (D)   |              |              | PLQP0100KB-A     | version<br>(blank product)     |

| M30302GCPFP     |       | 128 Kbytes   |              | PRQP0100JB-A     |                                |

| M30302GCPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GDPFP     |       | 160 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GDPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30304GDPFP     | (D)   |              | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30304GDPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GEPFP     |       | 192 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GEPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30304GEPFP     | (D)   |              | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30304GEPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GGPFP     | (D)   | 256 Kbytes   | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30302GGPGP     | (D)   |              |              | PLQP0100KB-A     |                                |

| M30302GAP-XXXFF | )     | 96 Kbytes    | 5 Kbytes     | PRQP0100JB-A     | One Time Flash                 |

| M30302GAPvGP    | (D)   |              |              | PLQP0100KB-A     | version<br>(factory programmed |

| M30302GCP-XXXFF | 2     | 128 Kbytes   |              | PRQP0100JB-A     | product)                       |

| M30302GCP-XXXG  | P (D) | -            |              | PLQP0100KB-A     |                                |

| M30302GDP-XXXFF | 2     | 160 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GDP-XXXG  | P (D) |              |              | PLQP0100KB-A     |                                |

| M30304GDP-XXXFF | р (D) |              | 12 Kbytes    | PRQP0100JB-A     |                                |

| M30304GDP-XXXG  | P (D) |              |              | PLQP0100KB-A     |                                |

| M30302GEP-XXXFF | )     | 192 Kbytes   | 6 Kbytes     | PRQP0100JB-A     |                                |

| M30302GEP-XXXG  | - (D) |              |              | PLQP0100KB-A     | 1                              |

| M30304GEP-XXXFF | P (D) |              | 12 Kbytes    | PRQP0100JB-A     | 1                              |

| M30304GEP-XXXG  | > (D) |              |              | PLQP0100KB-A     | 1                              |

| M30302GGP-XXXF  | P (D) | 256 Kbytes   | 12 Kbytes    | PRQP0100JB-A     | 1                              |

| M30302GGP-XXXG  | P (D) |              |              | PLQP0100KB-A     | 1                              |

### Table 1.2 **Product List (1)**

As of March 2007

(D): Under development

(P): Under planning

NOTES:

1. Previous package codes are as follows.

PRQP0100JB-A : 100P6S-A, PLQP0100KB-A : 100P6Q-A

2. Block A (4-Kbytes space) is available in flash memory version.

RENESAS

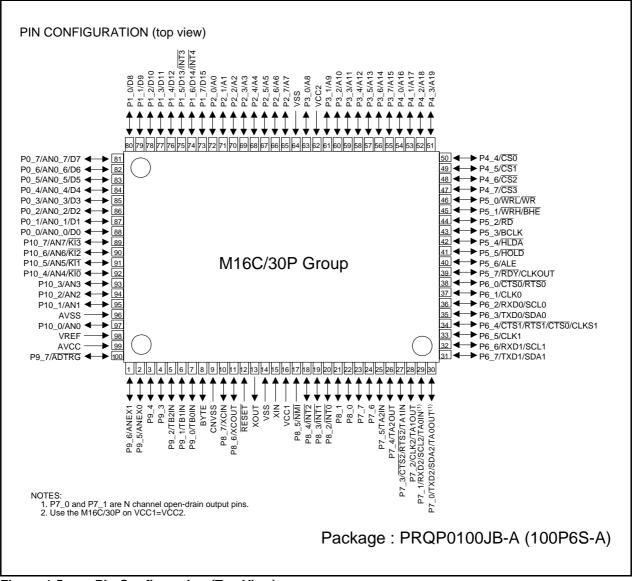

# 1.5 Pin Configuration

Figures 1.5 to 1.6 show the pin configurations (top view).

# Figure 1.5 Pin Configuration (Top View)

RENESAS

# 2.2 Address Registers (A0 and A1)

The register A0 consists of 16 bits, and is used for address register indirect addressing and address register relative addressing. They also are used for transfers and logic/logic operations. A1 is the same as A0. In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

# 2.3 Frame Base Register (FB)

FB is configured with 16 bits, and is used for FB relative addressing.

# 2.4 Interrupt Table Register (INTB)

INTB is configured with 20 bits, indicating the start address of an interrupt vector table.

# 2.5 Program Counter (PC)

PC is configured with 20 bits, indicating the address of an instruction to be executed.

# 2.6 User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

Stack pointer (SP) comes in two types: USP and ISP, each configured with 16 bits. Your desired type of stack pointer (USP or ISP) can be selected by the U flag of FLG.

# 2.7 Static Base Register (SB)

SB is configured with 16 bits, and is used for SB relative addressing.

# 2.8 Flag Register (FLG)

FLG consists of 11 bits, indicating the CPU status.

# 2.8.1 Carry Flag (C Flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

# 2.8.2 Debug Flag (D Flag)

The D flag is used exclusively for debugging purpose. During normal use, it must be set to "0".

# 2.8.3 Zero Flag (Z Flag)

This flag is set to "1" when an arithmetic operation resulted in 0; otherwise, it is "0".

# 2.8.4 Sign Flag (S Flag)

This flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, it is "0".

# 2.8.5 Register Bank Select Flag (B Flag)

Register bank 0 is selected when this flag is "0"; register bank 1 is selected when this flag is "1".

# 2.8.6 Overflow Flag (O Flag)

This flag is set to "1" when the operation resulted in an overflow; otherwise, it is "0".

# 2.8.7 Interrupt Enable Flag (I Flag)

This flag enables a maskable interrupt.

Maskable interrupts are disabled when the I flag is "0", and are enabled when the I flag is "1". The I flag is cleared to "0" when the interrupt request is accepted.

# 2.8.8 Stack Pointer Select Flag (U Flag)

ISP is selected when the U flag is "0"; USP is selected when the U flag is "1".

The U flag is cleared to "0" when a hardware interrupt request is accepted or an INT instruction for software interrupt Nos. 0 to 31 is executed.

# 2.8.9 Processor Interrupt Priority Level (IPL)

IPL is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than IPL, the interrupt is enabled.

# 2.8.10 Reserved Area

When write to this bit, write "0". When read, its content is indeterminate.

# 3. Memory

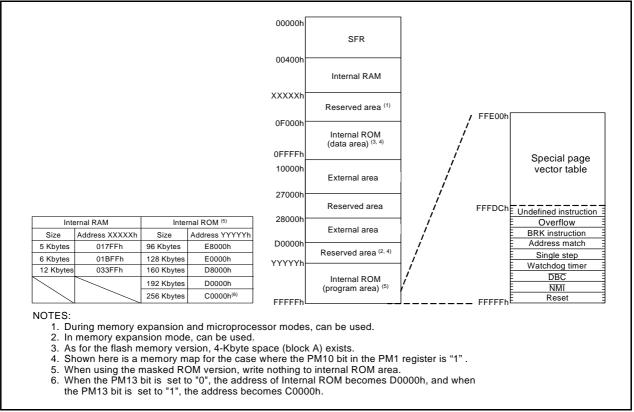

Figure 3.1 is a Memory Map of the M16C/30P group. The address space extends the 1 Mbyte from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a 64-Kbyte internal ROM is allocated to the addresses from F0000h to FFFFFh.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a 5-Kbyte internal RAM is allocated to the addresses from 00400h to 017FFh. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated. The SFR is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by the JMPS or JSRS instruction. For details, refer to the M16C/60 and M16C/20 Series Software Manual.

Figure 3.1 Memory Map

| Address | Register                                  | Symbol | After Reset |

|---------|-------------------------------------------|--------|-------------|

| 0340h   |                                           |        |             |

| 0341h   |                                           |        |             |

| 0342h   |                                           |        |             |

| 0343h   |                                           |        |             |

| 0344h   |                                           |        |             |

| 0345h   |                                           |        |             |

|         |                                           |        |             |

| 0346h   |                                           |        |             |

| 0347h   |                                           |        |             |

| 0348h   |                                           |        |             |

| 0349h   |                                           |        |             |

| 034Ah   |                                           |        |             |

| 034Bh   |                                           |        |             |

| 034Ch   |                                           |        |             |

| 034Dh   |                                           |        |             |

| 034Eh   |                                           |        |             |

| 034Fh   |                                           |        |             |

| 0350h   |                                           |        |             |

|         |                                           |        |             |

| 0351h   |                                           |        |             |

| 0352h   |                                           |        |             |

| 0353h   |                                           |        |             |

| 0354h   |                                           |        |             |

| 0355h   |                                           |        |             |

| 0356h   |                                           |        |             |

| 0357h   |                                           |        |             |

| 0358h   |                                           |        |             |

| 0359h   |                                           |        |             |

| 035Ah   |                                           |        |             |

|         |                                           |        |             |

| 035Bh   |                                           |        |             |

| 035Ch   |                                           |        |             |

| 035Dh   |                                           |        |             |

| 035Eh   | Interrupt Factor Select Register 2        | IFSR2A | 00XXXXXb    |

| 035Fh   | Interrupt Factor Select Register          | IFSR   | 00h         |

| 0360h   |                                           |        |             |

| 0361h   |                                           |        |             |

| 0362h   |                                           |        |             |

| 0363h   |                                           |        |             |

| 0364h   |                                           |        |             |

| 0365h   |                                           |        |             |

|         |                                           |        |             |

| 0366h   |                                           |        |             |

| 0367h   |                                           |        |             |

| 0368h   |                                           |        |             |

| 0369h   |                                           |        |             |

| 036Ah   |                                           |        |             |

| 036Bh   |                                           |        |             |

| 036Ch   | UART0 Special Mode Register 4             | U0SMR4 | 00h         |

| 036Dh   | UART0 Special Mode Register 3             | U0SMR3 | 000X0X0Xb   |

| 036Eh   | UARTO Special Mode Register 2             | U0SMR2 | X000000b    |

| 036Fh   | UARTO Special Mode Register               | U0SMR  | X0000000b   |

|         |                                           |        | 00h         |

| 0370h   | UART1 Special Mode Register 4             | U1SMR4 |             |

| 0371h   | UART1 Special Mode Register 3             | U1SMR3 | 000X0X0Xb   |

| 0372h   | UART1 Special Mode Register 2             | U1SMR2 | X000000b    |

| 0373h   | UART1 Special Mode Register               | U1SMR  | X000000b    |

| 0374h   | UART2 Special Mode Register 4             | U2SMR4 | 00h         |

| 0375h   | UART2 Special Mode Register 3             | U2SMR3 | 000X0X0Xb   |

| 0376h   | UART2 Special Mode Register 2             | U2SMR2 | X000000b    |

| 0377h   | UART2 Special Mode Register               | U2SMR  | X000000b    |

| 0378h   | UART2 Transmit/Receive Mode Register      | U2MR   | 00h         |

| 0379h   | UART2 Bit Rate Generator                  | U2BRG  | XXh         |

|         | UART2 Transmit Buffer Register            |        |             |

| 037Ah   | UANTZ HAISHIL DUHEL REGISLEI              | U2TB   | XXh         |

| 037Bh   |                                           |        | XXh         |

| 037Ch   | UART2 Transmit/Receive Control Register 0 | U2C0   | 00001000b   |

| 037Dh   | UART2 Transmit/Receive Control Register 1 | U2C1   | 00000010b   |

|         |                                           | 1      | <u>+ </u>   |

| 037Eh   | UART2 Receive Buffer Register             | U2RB   | XXh         |

# Table 4.3SFR Information (3) (1)

NOTES:

1. The blank areas are reserved and cannot be accessed by users.

X : Nothing is mapped to this bit

# 5. Electrical Characteristics

| Table 5.1 Absolute Maximum Ratin | gs |

|----------------------------------|----|

|----------------------------------|----|

| Symbol |                      | Parameter                                                                                                                                                                                                                         | Condition                                                    | Rated Value           | Unit |

|--------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------|------|

| Vcc    | Supply Voltage       | e(Vcc1=Vcc2)                                                                                                                                                                                                                      | Vcc1=Vcc2=AVcc                                               | -0.3 to 6.5           | V    |

| AVcc   | Analog Supply        | Voltage                                                                                                                                                                                                                           | Vcc1=Vcc2=AVcc                                               | -0.3 to 6.5           | V    |

| Vı     | Input Voltage        | RESET, CNVSS, BYTE,         P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,         P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,         P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_7,         P9_0 to P9_7, P10_0 to P10_7,         VREF, XIN |                                                              | –0.3 to Vcc+0.3       | V    |

|        |                      | P7_0, P7_1                                                                                                                                                                                                                        |                                                              | -0.3 to 6.5           | V    |

| Vo     | Output<br>Voltage    | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7,<br>P3_0 to P3_7, P4_0 to P4_7, P5_0 to P5_7,<br>P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_4,<br>P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7,<br>XOUT                                          |                                                              | –0.3 to Vcc+0.3       | V    |

|        |                      | P7_0, P7_1                                                                                                                                                                                                                        |                                                              | -0.3 to 6.5           | V    |

| Pd     | Power Dissipa        | tion                                                                                                                                                                                                                              | –40°C <topr≤85°c< td=""><td>300</td><td>mW</td></topr≤85°c<> | 300                   | mW   |

| Topr   | Operating<br>Ambient | When the Microcomputer is Operating                                                                                                                                                                                               |                                                              | -20 to 85 / -40 to 85 | °C   |

|        | Temperature          | One Time Flash Program Erase                                                                                                                                                                                                      |                                                              | 0 to 60               |      |

|        |                      | Flash Program Erase                                                                                                                                                                                                               |                                                              | 0 to 60               |      |

| Tstg   | Storage Temp         | erature                                                                                                                                                                                                                           |                                                              | -65 to 150            | °C   |

| O wash a l | Derometer                               |                                                                                                                                                                              |        | Unit   |            |      |

|------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------------|------|

| Symbol     |                                         | Parameter                                                                                                                                                                    | Min.   |        |            | Unit |

| Vcc        | Supply Voltage (\                       | bly Voltage (Vcc1=Vcc2) 2.7 5.0                                                                                                                                              |        |        |            |      |

| AVcc       | Analog Supply Vo                        | bltage                                                                                                                                                                       |        | Vcc    |            | V    |

| Vss        | Supply Voltage                          | Supply Voltage                                                                                                                                                               |        |        |            | V    |

| AVss       | Analog Supply Vo                        | bltage                                                                                                                                                                       |        | 0      |            | V    |

| Viн        | HIGH Input                              | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7                                                                                                                                     | 0.8Vcc |        | Vcc        | V    |

|            | Voltage                                 | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(during single-chip mode)                                                                                                  | 0.8Vcc |        | Vcc        | V    |

|            |                                         | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input during memory expansion and microprocessor mode)                                                               | 0.5Vcc |        | Vcc        | V    |

|            |                                         | P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_7, P9_0 to P9_7,<br>P10_0 to P10_7, XIN, RESET, CNVSS, BYTE                                                                           | 0.8Vcc |        | Vcc        | V    |

|            |                                         | P7_0, P7_1                                                                                                                                                                   | 0.8Vcc |        | 6.5        | V    |

| VIL        | LOW Input<br>Voltage                    | P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7                                                                                                                                     | 0      |        | 0.2Vcc     | V    |

|            |                                         | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(during single-chip mode)                                                                                                  | 0      |        | 0.2Vcc     | V    |

|            |                                         | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0<br>(data input during memory expansion and microprocessor mode)                                                               | 0      |        | 0.16Vcc    | V    |

|            |                                         | P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7, XIN, RESET, CNVSS, BYTE                                                                                              | 0      |        | 0.2Vcc     | V    |

| IOH(peak)  | HIGH Peak<br>Output Current             | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | -10.0      | mA   |

| IOH(avg)   | HIGH Average<br>Output Current          | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | -5.0       | mA   |

| IOL(peak)  | LOW Peak<br>Output Current              | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | 10.0       | mA   |

| IOL(avg)   | LOW Average<br>Output Current           | P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,<br>P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,<br>P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7 |        |        | 5.0        | mA   |

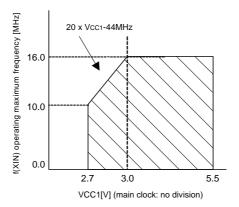

| f(XIN)     | Main Clock Input                        | VCC=3.0V to 5.5V                                                                                                                                                             | 0      |        | 16         | MHz  |

|            | Oscillation<br>Frequency <sup>(4)</sup> | VCC=2.7V to 3.0V                                                                                                                                                             | 0      |        | 20×Vcc1-44 | MHz  |

| f(XCIN)    | Sub-Clock Oscilla                       | ation Frequency                                                                                                                                                              |        | 32.768 | 50         | kHz  |

| f(BCLK)    | CPU Operation C                         | lock                                                                                                                                                                         | 0      |        | 16         | MHz  |

| Table 5.2 | Recommended Operating Conditions (1) |

|-----------|--------------------------------------|

|-----------|--------------------------------------|

NOTES:

1. Referenced to Vcc1 = Vcc2 = 2.7 to 5.5V at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified.

2. The Average Output Current is the mean value within 100ms.

The total IoL(peak) for ports P0, P1, P2, P8\_6, P8\_7, P9 and P10 must be 80mA max. The total IoL(peak) for ports P3, P4, P5, P6, P7 and P8\_0 to P8\_4 must be 80mA max. The total IOH(peak) for ports P0, P1, and P2 must be -40mA max. The total IOH(peak) for ports P3, P4 and P5 must be -40mA max. The total IOH(peak) for ports P6, P7, and P8\_0 to P8\_4 must be -40mA max.

The total IOH(peak) for ports P8\_6, P8\_7 and P9 must be -40mA max. Set Average Output Current to 1/2 of peak.

4. Relationship between main clock oscillation frequency, and supply voltage.

### Main clock input oscillation frequency

| Symbol | Parameter                                                                                            |                |                    | Unit |      |       |

|--------|------------------------------------------------------------------------------------------------------|----------------|--------------------|------|------|-------|

| Symbol | Falalletei                                                                                           | Min.           | Тур.               | Max. | Unit |       |

| -      | Program and Erase Endurance <sup>(2)</sup><br>Word Program Time (Vcc1=5.0V)<br>Lock Bit Program Time |                | 100 <sup>(3)</sup> |      |      | cycle |

| -      |                                                                                                      |                |                    | 25   | 200  | μS    |

| -      |                                                                                                      |                |                    | 25   | 200  | μS    |

| -      | Block Erase Time                                                                                     | 4-Kbyte block  |                    | 0.3  | 4    | S     |

| -      | (Vcc1=5.0V)                                                                                          | 8-Kbyte block  |                    | 0.3  | 4    | S     |

| -      |                                                                                                      | 32-Kbyte block |                    | 0.5  | 4    | S     |

| -      |                                                                                                      | 64-Kbyte block |                    | 0.8  | 4    | S     |

| tPS    | Flash Memory Circuit Stabilization Wait Time                                                         |                |                    |      | 15   | μS    |

| -      | Data Hold Time <sup>(4)</sup>                                                                        |                | 10                 |      |      | year  |

### Table 5.4 Flash Memory Version Electrical Characteristics (1)

NOTES:

1. Referenced to Vcc1=4.5 to 5.5V, 3.0 to 3.6V at Topr = 0 to 60 °C (U3, U5) unless otherwise specified.

2. Program and Erase Endurance refers to the number of times a block erase can be performed.

If the program and erase endurance is 100, each block can be erased 100 times. For example, if a 4 Kbytes block A is erased after writing 1 word data 2,048 times, each to a different address, this counts as one program and erase endurance. Data cannot be written to the same address more than once without erasing the block.

(Rewrite prohibited)3. Maximum number of E/W cycles for which operation is guaranteed.

4. Topr = -40 to 85 °C (U3) / -20 to 85 °C (U5).

# Table 5.5Flash Memory Version Program / Erase Voltage and Read Operation Voltage<br/>Characteristics

| Flash Program, Erase Voltage                                 | Flash Read Operation Voltage                 |

|--------------------------------------------------------------|----------------------------------------------|

| VCC1 = $3.3 \pm 0.3$ V or $5.0 \pm 0.5$ (Topr = 0°C to 60°C) | VCC1=2.7 to 5.5 V (Topr = -40°C to 85°C (U3) |

|                                                              | -20°C to 85°C (U5))                          |

| Symbol | Parameter                                        | or                                   | Maaa                                       | uring Condition                                                             | :            | Standard | ł   | Unit |

|--------|--------------------------------------------------|--------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------|--------------|----------|-----|------|

| Symbol | Falamet                                          |                                      | Ivieas                                     | Min.                                                                        | n. Typ. Max. | Offic    |     |      |

| Icc    | Power Supply Current<br>(Vcc1=Vcc2=4.0V to 5.5V) |                                      | Mask ROM                                   | f(XIN)=16MHz<br>No division                                                 |              | 10       | 15  | mA   |

|        |                                                  | pins are open and other pins are Vss | One Time<br>Flash                          | f(XIN)=16MHz,<br>No division                                                |              | 10       | 18  | mA   |

|        |                                                  |                                      | Flash<br>Memory                            | f(XIN)=16MHz,<br>No division                                                |              | 12       | 18  | mA   |

|        |                                                  |                                      | One Time<br>Flash                          | f(XIN)=10MHz,<br>VCC1=5.0V                                                  |              | 15       |     | mA   |

|        |                                                  |                                      | Flash Memory<br>Program                    | f(XIN)=10MHz,<br>VCC1=5.0V                                                  |              | 15       |     | mA   |

|        |                                                  |                                      | Flash Memory<br>Erase                      | f(XIN)=10MHz,<br>VCC1=5.0V                                                  |              | 25       |     | mA   |

|        |                                                  |                                      | Mask ROM                                   | f(XCIN)=32kHz<br>Low power dissipation<br>mode, ROM <sup>(3)</sup>          |              | 25       |     | μA   |

|        |                                                  |                                      | One Time<br>Flash                          | f(XCIN)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |              | 25       |     | μA   |

|        |                                                  |                                      |                                            | f(XCIN)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |              | 350      |     | μΑ   |

|        |                                                  |                                      | Flash Memory                               | f(XCIN)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |              | 25       |     | μA   |

|        |                                                  |                                      |                                            | f(XCIN)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |              | 420      |     | μA   |

|        |                                                  |                                      | Mask ROM<br>One Time Flash<br>Flash Memory | f(XCIN)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability High  |              | 7.5      |     | μΑ   |

|        |                                                  |                                      | r asir memory                              | f(XCIN)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability Low   |              | 2.0      |     | μΑ   |

|        |                                                  |                                      |                                            | Stop mode<br>Topr =25°C                                                     |              | 0.8      | 3.0 | μA   |

Table 5.10 Electrical Characteristics (2) (1)

NOTES:

1. Referenced to Vcc1=Vcc2=4.2 to 5.5V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(XIN)=16MHz unless otherwise specified.

2. With one timer operated using fC32.

3. This indicates the memory in which the program to be executed exists.

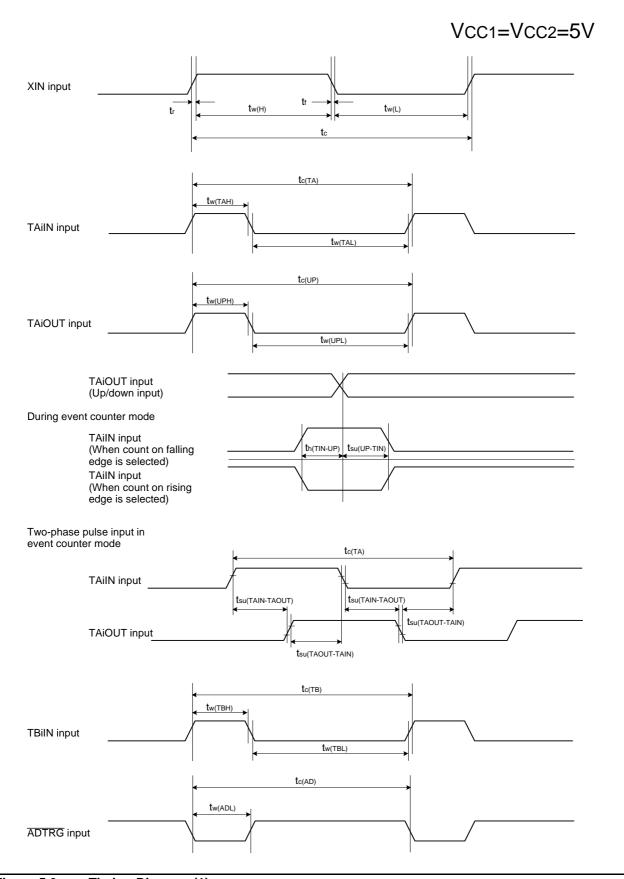

# VCC1=VCC2=5V

### **Timing Requirements**

## (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

### Table 5.19 Timer B Input (Counter Input in Event Counter Mode)

| Symbol  | Parameter                                            | Star | Standard | Unit |

|---------|------------------------------------------------------|------|----------|------|

|         | Falameter                                            | Min. | Max.     | Onit |

| tc(TB)  | TBiIN Input Cycle Time (counted on one edge)         | 100  |          | ns   |

| tw(TBH) | TBiIN Input HIGH Pulse Width (counted on one edge)   | 40   |          | ns   |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on one edge)    | 40   |          | ns   |

| tc(TB)  | TBiIN Input Cycle Time (counted on both edges)       | 200  |          | ns   |

| tw(TBH) | TBiIN Input HIGH Pulse Width (counted on both edges) | 80   |          | ns   |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on both edges)  | 80   |          | ns   |

### Table 5.20 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Standard |      | Unit |  |

|---------|------------------------------|----------|------|------|--|

|         | Farameter                    | Min.     | Max. | Unit |  |

| tc(TB)  | TBiIN Input Cycle Time       | 400      |      | ns   |  |

| tw(TBH) | TBiIN Input HIGH Pulse Width | 200      |      | ns   |  |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200      |      | ns   |  |

### Table 5.21 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    | Stan | dard | Unit |

|---------|------------------------------|------|------|------|

|         | Falameter                    | Min. | Max. | Onit |

| tc(TB)  | TBiIN Input Cycle Time       | 400  |      | ns   |

| tw(TBH) | TBilN Input HIGH Pulse Width | 200  |      | ns   |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200  |      | ns   |

### Table 5.22 A/D Trigger Input

| Symbol  | Parameter                   | Standard |      | Lipit      |

|---------|-----------------------------|----------|------|------------|

|         | Falameter                   | Min.     | Max. | Unit<br>ns |

| tc(AD)  | ADTRG Input Cycle Time      | 1000     |      | ns         |

| tw(ADL) | ADTRG input LOW Pulse Width | 125      |      | ns         |

## Table 5.23 Serial Interface

| Symbol          | Parameter                   | Stan | dard | Unit |

|-----------------|-----------------------------|------|------|------|

|                 | Falametei                   | Min. | Max. | Unit |

| tc(CK)          | CLKi Input Cycle Time       | 200  |      | ns   |

| tw(CKH)         | CLKi Input HIGH Pulse Width | 100  |      | ns   |

| tw(CKL)         | CLKi Input LOW Pulse Width  | 100  |      | ns   |

| td(C-Q)         | TXDi Output Delay Time      |      | 80   | ns   |

| <b>t</b> h(C-Q) | TXDi Hold Time              | 0    |      | ns   |

| tsu(D-C)        | RXDi Input Setup Time       | 70   |      | ns   |

| th(C-D)         | RXDi Input Hold Time        | 90   |      | ns   |

# Table 5.24 External Interrupt INTi Input

| Symbol  | Parameter                   | Standard |      | Unit |

|---------|-----------------------------|----------|------|------|

| Symbol  | Falameter                   | Min.     | Max. | Onit |

| tw(INH) | INTi Input HIGH Pulse Width | 250      |      | ns   |

| tw(INL) | INTi Input LOW Pulse Width  | 250      |      | ns   |

# VCC1=VCC2=5V

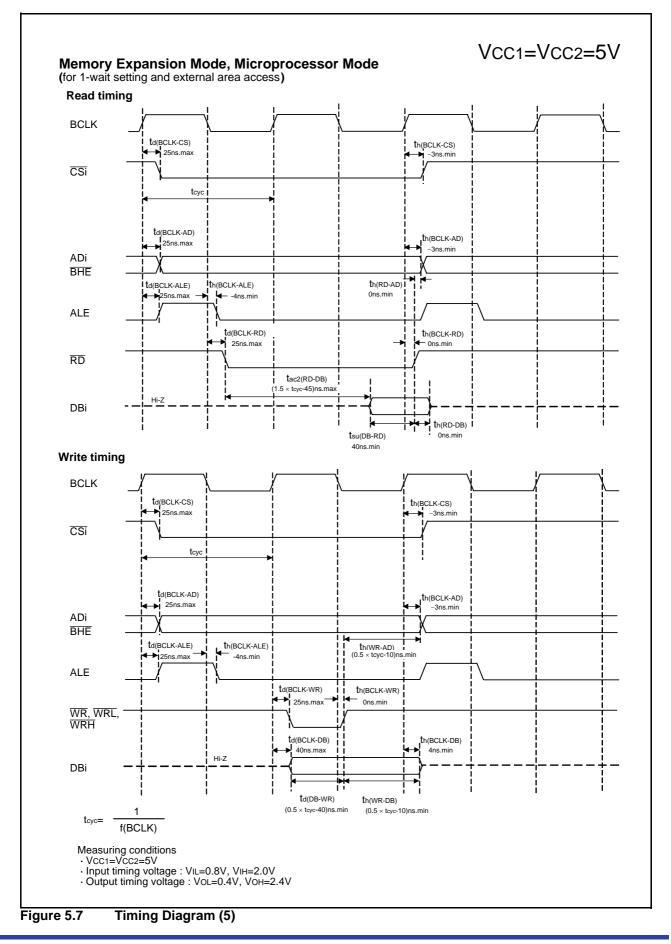

### Switching Characteristics

### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 5.26 | Memory Expansion and Microprocessor Modes (for 1 wait setting and external area |

|------------|---------------------------------------------------------------------------------|

|            | access)                                                                         |

| Cumbal        | Parameter                                                  |                | Stan     | dard | Unit |

|---------------|------------------------------------------------------------|----------------|----------|------|------|

| Symbol        | Farameter                                                  |                | Min.     | Max. | Unit |

| td(BCLK-AD)   | Address Output Delay Time                                  |                |          | 25   | ns   |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)             |                | -3       |      | ns   |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)               |                | 0        |      | ns   |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)               |                | (NOTE 2) |      | ns   |

| td(BCLK-CS)   | Chip Select Output Delay Time                              |                |          | 25   | ns   |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)         |                | -3       |      | ns   |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                               |                |          | 15   | ns   |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                                |                | -4       |      | ns   |

| td(BCLK-RD)   | RD Signal Output Delay Time                                | See Figure 5.2 |          | 25   | ns   |

| th(BCLK-RD)   | RD Signal Output Hold Time                                 | i igure 5.2    | 0        |      | ns   |

| td(BCLK-WR)   | WR Signal Output Delay Time                                |                |          | 25   | ns   |

| th(BCLK-WR)   | WR Signal Output Hold Time                                 |                | 0        |      | ns   |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)               |                |          | 40   | ns   |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) <sup>(3)</sup> |                | 4        |      | ns   |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)                 |                | (NOTE 1) |      | ns   |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) <sup>(3)</sup>   |                | (NOTE 2) |      | ns   |

| td(BCLK-HLDA) | HLDA Output Delay Time                                     |                |          | 40   | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5)x10^9}{f(BCLK)} - 40[ns] \qquad n \text{ is ``1'' for 1-wait setting, } f(BCLK) \text{ is 12.5MHz or less.}$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

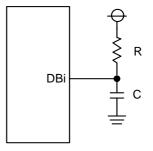

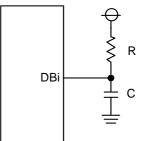

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in t = -CR X ln (1-VoL / Vcc1) by a circuit of the right figure. For example, when VoL = 0.2Vcc1, C = 30pF, R = 1kΩ, hold time of output "L" level is t = -30pF X 1kΩ X ln(1-0.2Vcc1 / Vcc1)

= 6.7ns.

Figure 5.3 Timing Diagram (1)

# VCC1=VCC2=3V

### Timing Requirements

## (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

### Table 5.29 External Clock Input (XIN input)

| Symbol | Parameter                             | Standard |          | Unit |

|--------|---------------------------------------|----------|----------|------|

|        | Falameter                             | Min.     | Max.     | Onit |

| tc     | External Clock Input Cycle Time       | (NOTE 2) |          | ns   |

| ťw(H)  | External Clock Input HIGH Pulse Width | (NOTE 3) |          | ns   |

| tw(L)  | External Clock Input LOW Pulse Width  | (NOTE 3) |          | ns   |

| tr     | External Clock Rise Time              |          | (NOTE 4) | ns   |

| tr     | External Clock Fall Time              |          | (NOTE 4) | ns   |

NOTES:

- 1. The condition is Vcc1=Vcc2=2.7 to 3.0V.

- 2. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_{1} - 44}$$

[ns]

3. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_{1}-44} \times 0.4$$

[ns]

4. Calculated according to the VCC1 voltage as follows:  $-10 \times Vcc1 + 45$  [ns]

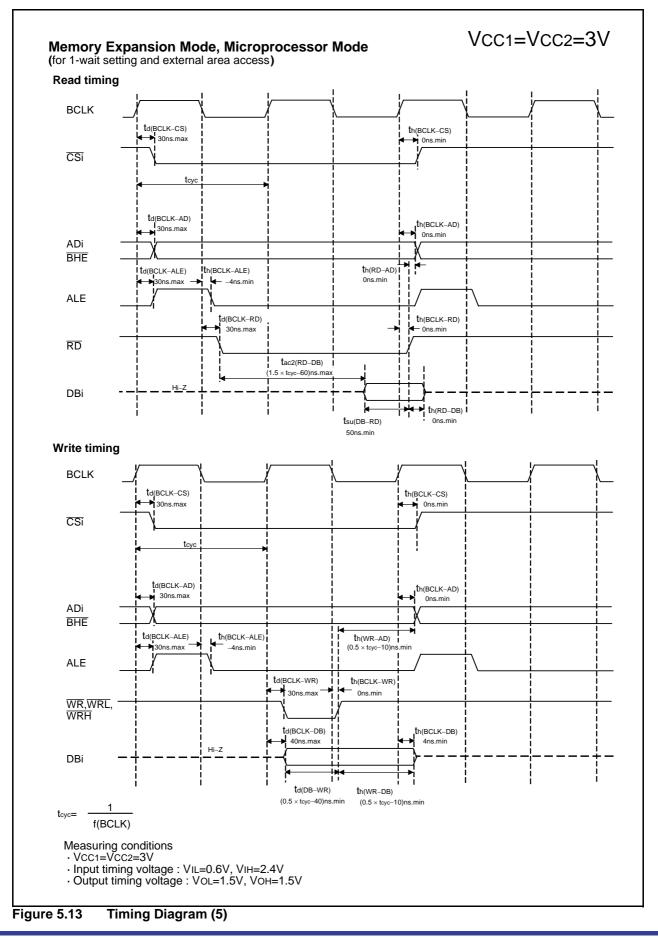

## Table 5.30 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                         | Stan | dard     | Unit |

|----------------|---------------------------------------------------|------|----------|------|

| Symbol         | Farameter                                         | Min. | Max.     | Unit |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait) |      | (NOTE 1) | ns   |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait)    |      | (NOTE 2) | ns   |

| tsu(DB-RD)     | Data Input Setup Time                             | 50   |          | ns   |

| tsu(RDY-BCLK)  | RDY Input Setup Time                              | 40   |          | ns   |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                             | 50   |          | ns   |

| th(RD-DB)      | Data Input Hold Time                              | 0    |          | ns   |

| th(BCLK-RDY)   | RDY Input Hold Time                               | 0    |          | ns   |

| th(BCLK-HOLD)  | HOLD Input Hold Time                              | 0    |          | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 60[ns]$$

n is "2" for 1-wait setting

# VCC1=VCC2=3V

### Switching Characteristics

## (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

| Table 5.43 | Memory Ex | pansion and     | Microprocessor | Modes (fo   | or setting with | n no wait) |

|------------|-----------|-----------------|----------------|-------------|-----------------|------------|

|            |           | Juli Sloll ullu | 10100100003301 | 1110405 (10 | n setting with  | i no many  |

| Cumbal        | Deremeter                                                  |                | Stan     | Standard |      |

|---------------|------------------------------------------------------------|----------------|----------|----------|------|

| Symbol        | Parameter                                                  |                | Min.     | Max.     | Unit |

| td(BCLK-AD)   | Address Output Delay Time                                  |                |          | 30       | ns   |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)             |                | 0        |          | ns   |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)               |                | 0        |          | ns   |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)               |                | (NOTE 2) |          | ns   |

| td(BCLK-CS)   | Chip Select Output Delay Time                              |                |          | 30       | ns   |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)         |                | 0        |          | ns   |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                               |                |          | 25       | ns   |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                                |                | -4       |          | ns   |

| td(BCLK-RD)   | RD Signal Output Delay Time                                | See Figure 5.8 |          | 30       | ns   |

| th(BCLK-RD)   | RD Signal Output Hold Time                                 | Figure 5.6     | 0        |          | ns   |

| td(BCLK-WR)   | WR Signal Output Delay Time                                |                |          | 30       | ns   |

| th(BCLK-WR)   | WR Signal Output Hold Time                                 |                | 0        |          | ns   |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)               |                |          | 40       | ns   |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) <sup>(3)</sup> |                | 4        |          | ns   |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)                 |                | (NOTE 1) |          | ns   |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) (3)              |                | (NOTE 2) |          | ns   |

| td(BCLK-HLDA) | HLDA Output Delay Time                                     |                |          | 40       | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 40[ns] \qquad \qquad f(BCLK) \text{ is } 12.5 \text{MHz or less.}$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

= 6.7ns.

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in t = -CR X ln (1-VoL / Vcc1) by a circuit of the right figure. For example, when VoL = 0.2Vcc1, C = 30pF, R = 1kΩ, hold time of output "L" level is t = -30pF X 1k Ω X ln(1-0.2Vcc1 / Vcc1)

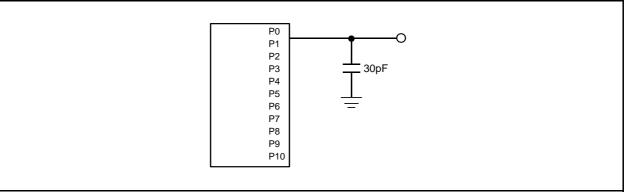

Figure 5.8 Ports P0 to P10 Measurement Circuit

# RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scule as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in this document, included in this document for the purpose of military application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulations.

All information included in this document, such as product data, diagrams, charts, programs, algorithms, and application carcuit examples, is current as of the date this document, when exporting the products or the technology described herein, you should follow the applicable export control laws and regulations, and proceedures required by such laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatsoever for any damages incurred as a fast and the internation included in this document. Dut Renesas asproaces are not essigned not the subceever on y damages incurred as a damage incurred as a disclosed by Renesas states and splications, and processes as and splication splication splication and application and application and application and application and and the second to a state of the date this document.

Renesas hall have the product specified by Renesas as subcervices in the date this document. Dut Renesas as subcervices are not designed applications, and processes in the another application and application and application and application and applic

### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, 1 Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2730-6071

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

## Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jalan Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com