#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | M16C/30                                                                        |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IEBus, UART/USART                                            |

| Peripherals                | DMA, POR, PWM, WDT                                                             |

| Number of I/O              | 87                                                                             |

| Program Memory Size        | -                                                                              |

| Program Memory Type        | ROMIess                                                                        |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 6K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                    |

| Data Converters            | A/D 18x10b                                                                     |

| Oscillator Type            | External, Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-BQFP                                                                       |

| Supplier Device Package    | 100-QFP (14x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/m30302spfp-u3 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# RENESAS

# M16C/30P Group

SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

### 1. Overview

The M16C/30P Group of single-chip microcomputers is built using the high-performance silicon gate CMOS process using a M16C/60 Series CPU core and is packaged in a 100-pin plastic molded QFP.

These single-chip microcomputers operate using sophisticated instructions featuring a high level of instruction efficiency. With 1 Mbyte of address space, they are capable of executing instructions at high speed. In addition, these microcomputers contain a multiplier and DMAC which combined with fast instruction processing capability, make it suitable for control of various OA, communication, and industrial equipment which requires high-speed arithmetic/ logic operations.

### 1.1 Applications

Audio, cameras, TV, home appliance, office/communications/portable/industrial equipment, etc.

Product Code

|                       | гаскауе             |                                                                                                 |

|-----------------------|---------------------|-------------------------------------------------------------------------------------------------|

| U1                    | Lead-free           | -20°C to 85°C                                                                                   |

| U4                    |                     | -40°C to 85°C                                                                                   |

|                       |                     |                                                                                                 |

|                       | 3-A (100P6S-A)      |                                                                                                 |

| 1. Standard R         | Renesas Mark        |                                                                                                 |

|                       | N A                 | 1 6 C                                                                                           |

| M3030                 | )2MDP-XX            |                                                                                                 |

| A                     | U 1 X X X X         | X X X — Chip version, product code and date code                                                |

|                       |                     | A : Shows chip version.<br>Henceforth, whenever it changes a version,                           |

| 0                     |                     | it continues with A, B, and C.<br>U1 : Shows Product code. (See <b>table 1.3 Product Code</b> ) |

|                       |                     | XXXXXXX : Seven digits                                                                          |

| 2. Customer's         | s Parts Number + F  | Renesas catalog name                                                                            |

|                       |                     |                                                                                                 |

| M3.0.3(               | 02MDP - XX          | X F P Part No. (See Figure 1.2 Part No., Memory Size, and Package)                              |

|                       | -                   | U 1 ——— Chip version and product code                                                           |

| M <sup>1</sup>        | 16C XXXX            | Henceforth, whenever it changes a version,                                                      |

| 0                     |                     | it continues with A, B, and C.<br>U1 : Shows Product code. (See <b>table 1.3 Product Code</b> ) |

| L                     |                     | Date code seven digits                                                                          |

|                       |                     |                                                                                                 |

| PLQP0100KE            | 3-A (100P6Q-A)      |                                                                                                 |

| 1. Standard F         | Renesas Mark        |                                                                                                 |

|                       |                     |                                                                                                 |

|                       | M16C                |                                                                                                 |

| M 3                   | 0 3 0 2 MD P        | Part No. (See Figure 1.2 Part No., Memory Size, and Package)                                    |

| A U 1                 | - XXXGP<br>XXXXXXX  | - Chip version, product code and date code                                                      |

|                       |                     | A : Shows chip version.<br>Henceforth, whenever it changes a version,                           |

| 0                     |                     | it continues with A, B, and C.                                                                  |

|                       |                     | U1 : Shows Product code. (See <b>table 1.3 Product Code</b> )<br>XXXXXXX : Seven digits         |

| 2. Customer'          | 's Parts Number + I | Renesas catalog name                                                                            |

|                       |                     |                                                                                                 |

|                       |                     |                                                                                                 |

| М 3                   | 0 3 0 2 M D P       | — Part No. (See Figure 1.2 Part No., Memory Size, and Package)                                  |

| A U 1                 | - XXXGP             | Chip version and product code     A : Shows chip version.                                       |

|                       |                     | Henceforth, whenever it changes a version,<br>it continues with A, B, and C.                    |

| 0                     |                     | U1 : Shows Product code. (See <b>table 1.3 Product Code</b> )                                   |

| L                     |                     | — Date code seven digits                                                                        |

|                       |                     |                                                                                                 |

| NOTES:<br>1. Refer to | o the mark specific | cation form for details of the Mask ROM version marking.                                        |

|                       |                     |                                                                                                 |

| ure 1.3 N             | larking Diagra      | m of Mask ROM Version for M16C/30P (Top View)                                                   |

Package

**Operating Ambient Temperature**

| Pin | No. | Control | Port                | Interrupt Pin | Timer Pin | UART Pin             | Analog Pin | Bus Control |

|-----|-----|---------|---------------------|---------------|-----------|----------------------|------------|-------------|

| FP  | GP  | Pin     |                     |               |           | UART FIII            |            | Pin         |

| 1   | 99  |         | P9_6                |               |           |                      | ANEX1      |             |

| 2   | 100 |         | P9_5                |               |           |                      | ANEX0      |             |

| 3   | 1   |         | P9_4                |               |           |                      |            |             |

| 4   | 2   |         | P9_3                |               |           |                      |            |             |

| 5   | 3   |         | P9_2                |               | TB2IN     |                      |            |             |

| 6   | 4   |         | P9_1                |               | TB1IN     |                      | _          |             |

| 7   | 5   |         | P9_0                |               | TB0IN     |                      |            |             |

| 8   | 6   | BYTE    |                     |               |           |                      |            |             |

| 9   | 7   | CNVSS   | <b>D</b> 0 <b>-</b> |               |           |                      |            |             |

| 10  | 8   | XCIN    | P8_7                |               |           |                      |            |             |

| 11  | 9   | XCOUT   | P8_6                |               |           |                      |            |             |

| 12  | 10  | RESET   |                     |               |           |                      |            |             |

| 13  | 11  | XOUT    |                     |               |           |                      |            |             |

| 14  | 12  | VSS     |                     |               |           |                      |            |             |

| 15  | 13  | XIN     |                     |               |           |                      |            |             |

| 16  | 14  | VCC1    |                     |               |           |                      |            |             |

| 17  | 15  |         | P8_5                | NMI           |           |                      |            |             |

| 18  | 16  |         | P8_4                | INT2          |           |                      |            |             |

| 19  | 17  |         | P8_3                | INT1          |           |                      |            |             |

| 20  | 18  |         | P8_2                | INT0          |           |                      |            |             |

| 21  | 19  |         | P8_1                |               |           |                      |            |             |

| 22  | 20  |         | P8_0                |               |           |                      |            |             |

| 23  | 21  |         | P7_7                |               |           |                      |            |             |

| 24  | 22  |         | P7_6                |               |           |                      |            |             |

| 25  | 23  |         | P7_5                |               | TA2IN     |                      |            |             |

| 26  | 24  |         | P7_4                |               | TA2OUT    |                      |            |             |

| 27  | 25  |         | P7_3                |               | TA1IN     | CTS2/RTS2            |            |             |

| 28  | 26  |         | P7_2                |               | TA1OUT    | CLK2                 |            |             |

| 29  | 27  |         | P7_1                |               | TAOIN     | RXD2/SCL2            |            |             |

| 30  | 28  |         | P7_0                |               | TA0OUT    | TXD2/SDA2            |            |             |

| 31  | 29  |         | P6_7                |               |           | TXD1/SDA1            |            |             |

| 32  | 30  |         | P6_6                |               |           | RXD1/SCL1            |            |             |

| 33  | 31  |         | P6_5                |               |           | CLK1                 |            |             |

| 34  | 32  |         | P6_4                |               |           | CTS1/RTS1/CTS0/CLKS1 |            |             |

| 35  | 33  |         | P6_3                |               |           | TXD0/SDA0            |            |             |

| 36  | 34  |         | P6_2                |               |           | RXD0/SCL0            |            |             |

| 37  | 35  |         | P6_1                |               |           | CLK0                 |            |             |

| 38  | 36  |         | P6_0                |               |           | CTS0/RTS0            |            |             |

| 39  | 37  |         | P5_7                |               |           |                      |            | RDY/CLKOUT  |

| 40  | 38  |         | P5_6                |               |           |                      |            | ALE         |

| 41  | 39  |         | P5_5                |               |           |                      |            | HOLD        |

| 42  | 40  |         | P5_4                |               |           |                      |            | HLDA        |

| 43  | 41  |         | P5_3                |               |           |                      |            | BCLK        |

| 44  | 42  |         | P5_2                |               |           |                      |            | RD          |

| 45  | 43  |         | P5_1                |               |           |                      |            | WRH/BHE     |

| 46  | 44  |         | P5_0                |               |           |                      |            | WRL/WR      |

| 47  | 45  |         | P4_7                |               |           |                      |            | CS3         |

| 48  | 46  |         | P4_6                |               |           |                      |            | CS2         |

| 49  | 47  |         | P4_5                |               |           |                      |            | CS1         |

| 50  | 48  |         | P4_4                |               |           |                      |            | CS0         |

Table 1.6Pin Characteristics (1)

RENESAS

### 1.6 Pin Description

| Table 1.8Pin Description (1) |

|------------------------------|

|------------------------------|

| Signal Name                             | Pin Name                | I/O Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply input                      | VCC1, VCC2<br>VSS       | I        | Apply 2.7 to 5.5 V to the VCC1 and VCC2 pins and 0 V to the Vss pin. The VCC apply condition is that VCC1 = VCC2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Analog power<br>supply input            | AVCC<br>AVSS            | I        | Applies the power supply for the A/D converter. Connect the AVCC pin to VCC1. Connect the AVSS pin to VSS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Reset input                             | RESET                   | I        | The microcomputer is in a reset state when applying "L" to the this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CNVSS                                   | CNVSS                   | I        | Switches processor mode. Connect this pin to VSS to when after<br>a reset to start up in single-chip mode. Connect this pin to VCC1 to<br>start up in microprocessor mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| External data bus<br>width select input | BYTE                    | I        | Switches the data bus in external memory space. The data bus is 16 bits long when the this pin is held "L" and 8 bits long when the this pin is held "H". Set it to either one. Connect this pin to VSS when an single-chip mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Bus control pins                        | D0 to D7                | I/O      | Inputs and outputs data (D0 to D7) when these pins are set as the separate bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                         | D8 to D15               | I/O      | Inputs and outputs data (D8 to D15) when external 16-bit data bus is set as the separate bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                         | A0 to A19               | 0        | Output address bits (A0 to A19).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         | CS0 to CS3              | 0        | Output $\overline{\text{CS0}}$ to $\overline{\text{CS3}}$ signals. $\overline{\text{CS0}}$ to $\overline{\text{CS3}}$ are chip-select signals to specify an external space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         | WRL/WR<br>WRH/BHE<br>RD | 0        | Output WRL, WRH, (WR, BHE), RD signals. WRL and WRH or<br>BHE and WR can be switched by program.<br>• WRL, WRH and RD are selected<br>The WRL signal becomes "L" by writing data to an even address in<br>an external memory space.<br>The WRH signal becomes "L" by writing data to an odd address in<br>an external memory space.<br>The RD pin signal becomes "L" by reading data in an external<br>memory space.<br>• WR, BHE and RD are selected<br>The WR signal becomes "L" by writing data in an external<br>memory space.<br>• WR, BHE and RD are selected<br>The WR signal becomes "L" by writing data in an external memory space.<br>The RD signal becomes "L" by reading data in an external memory space.<br>The RD signal becomes "L" by reading data in an external memory space.<br>Select WR, BHE and RD for an external 8-bit data bus. |

|                                         | ALE                     | 0        | ALE is a signal to latch the address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                         | HOLD                    | I        | While the $\overline{\text{HOLD}}$ pin is held "L", the microcomputer is placed in a hold state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                         | HLDA                    | 0        | In a hold state, HLDA outputs a "L" signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                         | RDY                     | I        | While applying a "L" signal to the $\overline{\text{RDY}}$ pin, the microcomputer is placed in a wait state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

I : Input O : Output I/O : Input and output

### 3. Memory

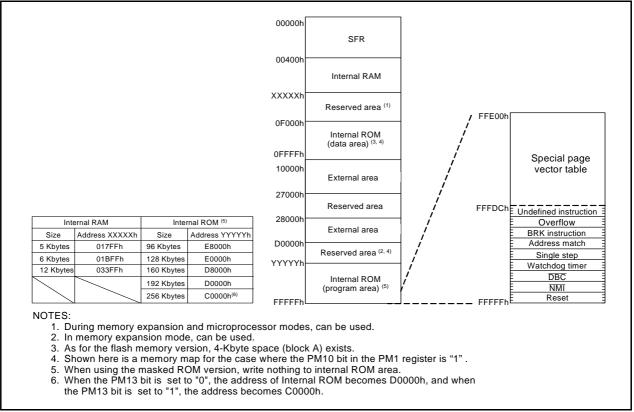

Figure 3.1 is a Memory Map of the M16C/30P group. The address space extends the 1 Mbyte from address 00000h to FFFFFh.

The internal ROM is allocated in a lower address direction beginning with address FFFFFh. For example, a 64-Kbyte internal ROM is allocated to the addresses from F0000h to FFFFFh.

The fixed interrupt vector table is allocated to the addresses from FFFDCh to FFFFFh. Therefore, store the start address of each interrupt routine here.

The internal RAM is allocated in an upper address direction beginning with address 00400h. For example, a 5-Kbyte internal RAM is allocated to the addresses from 00400h to 017FFh. In addition to storing data, the internal RAM also stores the stack used when calling subroutines and when interrupts are generated. The SFR is allocated to the addresses from 00000h to 003FFh. Peripheral function control registers are located here. Of the SFR, any area which has no functions allocated is reserved for future use and cannot be used by users.

The special page vector table is allocated to the addresses from FFE00h to FFFDBh. This vector is used by the JMPS or JSRS instruction. For details, refer to the M16C/60 and M16C/20 Series Software Manual.

Figure 3.1 Memory Map

#### **Special Function Register (SFR)** 4.

SFR(Special Function Register) is the control register of peripheral functions. Tables 4.1 to 4.5 list the SFR information.

| Address        | Register                                 | Symbol | After Reset                                                |

|----------------|------------------------------------------|--------|------------------------------------------------------------|

| 0000h          | IVEGISIEI                                | Symbol |                                                            |

| 0000h          | +                                        |        | <u> </u>                                                   |

| 0002h          | -+                                       |        | <u> </u>                                                   |

| 0002h          |                                          |        | <u> </u>                                                   |

| 0003h<br>0004h | Processor Mode Register 0 <sup>(2)</sup> | PM0    | 0000000b(CNVSS pin is "I ")                                |

|                |                                          |        | 00000000b(CNVSS pin is "L")<br>00000011b(CNVSS pin is "H") |

| 0005h          | Processor Mode Register 1                | PM1    | 00XXX0X0b                                                  |

| 0006h          | System Clock Control Register 0          | CM0    | 01001000b                                                  |

| 0007h          | System Clock Control Register 1          | CM1    | 0010000b                                                   |

| 0008h          | Chip Select Control Register             | CSR    | 0000001b                                                   |

| 0009h          | Address Match Interrupt Enable Register  | AIER   | XXXXXX00b                                                  |

| 000Ah          | Protect Register                         | PRCR   | XX000000b                                                  |

| 000Bh          |                                          |        |                                                            |

| 000Ch          |                                          |        |                                                            |

| 000Dh          |                                          |        |                                                            |

| 000Eh          | Watchdog Timer Start Register            | WDTS   | XXh                                                        |

| 000Fh          | Watchdog Timer Control Register          | WDC    | 00XXXXXb                                                   |

| 0010h          | Address Match Interrupt Register 0       | RMAD0  | 00h                                                        |

| 0011h          |                                          |        | 00h                                                        |

| 0012h          |                                          |        | X0h                                                        |

| 0013h          |                                          |        |                                                            |

| 0014h          | Address Match Interrupt Register 1       | RMAD1  | 00h                                                        |

| 0015h          |                                          |        | 00h                                                        |

| 0016h          |                                          |        | X0h                                                        |

| 0017h          |                                          |        |                                                            |

| 0018h          |                                          |        |                                                            |

| 0019h          |                                          |        |                                                            |

| 001Ah          |                                          |        |                                                            |

| 001Bh          |                                          |        |                                                            |

| 001Ch          |                                          |        |                                                            |

| 001Dh          |                                          |        |                                                            |

| 001Eh          |                                          |        |                                                            |

| 001Fh          |                                          |        |                                                            |

| 0020h          | DMA0 Source Pointer                      | SAR0   | XXh                                                        |

| 0021h          |                                          |        | XXh                                                        |

| 0022h          |                                          |        | XXh                                                        |

| 0023h          |                                          |        |                                                            |

| 0024h          | DMA0 Destination Pointer                 | DAR0   | XXh                                                        |

| 0025h          |                                          |        | XXh                                                        |

| 0026h          |                                          |        | XXh                                                        |

| 0027h          |                                          |        |                                                            |

| 0028h          | DMA0 Transfer Counter                    | TCR0   | XXh                                                        |

| 0029h          |                                          |        | XXh                                                        |

| 002Ah          |                                          |        |                                                            |

| 002Bh          |                                          |        |                                                            |

| 002Ch          | DMA0 Control Register                    | DM0CON | 00000X00b                                                  |

| 002Dh          |                                          |        |                                                            |

| 002Eh          |                                          |        |                                                            |

| 002Fh          |                                          |        |                                                            |

| 0030h          | DMA1 Source Pointer                      | SAR1   | XXh                                                        |

| 0031h          |                                          |        | XXh                                                        |

| 0032h          |                                          |        | XXh                                                        |

| 0033h          |                                          |        |                                                            |

| 0034h          | DMA1 Destination Pointer                 | DAR1   | XXh                                                        |

| 0035h          |                                          |        | XXh                                                        |

| 0036h          |                                          | I      | XXh                                                        |

| 0037h          |                                          |        |                                                            |

| 0038h          | DMA1 Transfer Counter                    | TCR1   | XXh                                                        |

| 0039h          |                                          |        | XXh                                                        |

| 003Ah          |                                          |        |                                                            |

| 003Bh          |                                          |        |                                                            |

| 003Ch          | DMA1 Control Register                    | DM1CON | 00000X00b                                                  |

| 003Dh          |                                          |        |                                                            |

| 003Eh          |                                          |        |                                                            |

| 003Fh          |                                          |        |                                                            |

|                |                                          |        |                                                            |

#### SFR Information (1)<sup>(1)</sup> Table 4.1

NOTES:

The blank areas are reserved and cannot be accessed by users.

The PM00 and PM01 bits do not change at software reset.

X : Nothing is mapped to this bit

| Address | Register                                  | Symbol | After Reset |

|---------|-------------------------------------------|--------|-------------|

| 0340h   |                                           |        |             |

| 0341h   |                                           |        |             |

| 0342h   |                                           |        |             |

| 0343h   |                                           |        |             |

| 0344h   |                                           |        |             |

| 0345h   |                                           |        |             |

|         |                                           |        |             |

| 0346h   |                                           |        |             |

| 0347h   |                                           |        |             |

| 0348h   |                                           |        |             |

| 0349h   |                                           |        |             |

| 034Ah   |                                           |        |             |

| 034Bh   |                                           |        |             |

| 034Ch   |                                           |        |             |

| 034Dh   |                                           |        |             |

| 034Eh   |                                           |        |             |

| 034Fh   |                                           |        |             |

| 0350h   |                                           |        |             |

|         |                                           |        |             |

| 0351h   |                                           |        |             |

| 0352h   |                                           |        |             |

| 0353h   |                                           |        |             |

| 0354h   |                                           |        |             |

| 0355h   |                                           |        |             |

| 0356h   |                                           |        |             |

| 0357h   |                                           |        |             |

| 0358h   |                                           |        |             |

| 0359h   |                                           |        |             |

| 035Ah   |                                           |        |             |

|         |                                           |        |             |

| 035Bh   |                                           |        |             |

| 035Ch   |                                           |        |             |

| 035Dh   |                                           |        |             |

| 035Eh   | Interrupt Factor Select Register 2        | IFSR2A | 00XXXXXb    |

| 035Fh   | Interrupt Factor Select Register          | IFSR   | 00h         |

| 0360h   |                                           |        |             |

| 0361h   |                                           |        |             |

| 0362h   |                                           |        |             |

| 0363h   |                                           |        |             |

| 0364h   |                                           |        |             |

| 0365h   |                                           |        |             |

|         |                                           |        |             |

| 0366h   |                                           |        |             |

| 0367h   |                                           |        |             |

| 0368h   |                                           |        |             |

| 0369h   |                                           |        |             |

| 036Ah   |                                           |        |             |

| 036Bh   |                                           |        |             |

| 036Ch   | UART0 Special Mode Register 4             | U0SMR4 | 00h         |

| 036Dh   | UART0 Special Mode Register 3             | U0SMR3 | 000X0X0Xb   |

| 036Eh   | UARTO Special Mode Register 2             | U0SMR2 | X000000b    |

| 036Fh   | UARTO Special Mode Register               | U0SMR  | X0000000b   |

|         |                                           |        | 00h         |

| 0370h   | UART1 Special Mode Register 4             | U1SMR4 |             |

| 0371h   | UART1 Special Mode Register 3             | U1SMR3 | 000X0X0Xb   |

| 0372h   | UART1 Special Mode Register 2             | U1SMR2 | X000000b    |

| 0373h   | UART1 Special Mode Register               | U1SMR  | X000000b    |

| 0374h   | UART2 Special Mode Register 4             | U2SMR4 | 00h         |

| 0375h   | UART2 Special Mode Register 3             | U2SMR3 | 000X0X0Xb   |

| 0376h   | UART2 Special Mode Register 2             | U2SMR2 | X000000b    |

| 0377h   | UART2 Special Mode Register               | U2SMR  | X000000b    |

| 0378h   | UART2 Transmit/Receive Mode Register      | U2MR   | 00h         |

| 0379h   | UART2 Bit Rate Generator                  | U2BRG  | XXh         |

|         | UART2 Transmit Buffer Register            |        |             |

| 037Ah   | UANTZ HAISHIL DUHEL REGISLEI              | U2TB   | XXh         |

| 037Bh   |                                           |        | XXh         |

| 037Ch   | UART2 Transmit/Receive Control Register 0 | U2C0   | 00001000b   |

| 037Dh   | UART2 Transmit/Receive Control Register 1 | U2C1   | 00000010b   |

|         |                                           | 1      | <u>+ </u>   |

| 037Eh   | UART2 Receive Buffer Register             | U2RB   | XXh         |

### Table 4.3SFR Information (3) (1)

NOTES:

1. The blank areas are reserved and cannot be accessed by users.

X : Nothing is mapped to this bit

| Symbol        | Parameter                                                   |          |                       | Measuring Condition                                              |      | Standard |      |      |

|---------------|-------------------------------------------------------------|----------|-----------------------|------------------------------------------------------------------|------|----------|------|------|

| Symbol        |                                                             |          | Measuring Condition   |                                                                  | Min. | Тур.     | Max. | Unit |

| 1             | Resolution                                                  |          | Vref=V                | /cc                                                              |      |          | 10   | Bits |

| INL           | Integral Non-Linearity<br>Error                             | 10bit    | VREF=<br>VCC=<br>5V   | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>ANEX0, ANEX1 input |      |          | ±5   | LSB  |

|               |                                                             |          | VREF=<br>VCC=<br>3.3V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>ANEX0, ANEX1 input |      |          | ±7   | LSB  |

|               |                                                             | 8bit     | Vref=V                | /cc=5V, 3.3V                                                     |      |          | ±2   | LSB  |

| -             | Absolute Accuracy                                           | 10bit    | VREF=<br>VCC=<br>5V   | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>ANEX0, ANEX1 input |      |          | ±5   | LSB  |

|               |                                                             |          | VREF=<br>VCC<br>=3.3V | AN0 to AN7 input,<br>AN0_0 to AN0_7 input,<br>ANEX0, ANEX1 input |      |          | ±7   | LSB  |

|               |                                                             | 8bit     | VREF=V                | /cc=5V, 3.3V                                                     |      |          | ±2   | LSB  |

| -             | Tolerance Level Imped                                       | ance     |                       |                                                                  |      | 3        |      | kΩ   |

| DNL           | Differential Non-Lineari                                    | ty Error |                       |                                                                  |      |          | ±2   | LSB  |

| -             | Offset Error                                                |          |                       |                                                                  |      |          | ±5   | LSB  |

| -             | Gain Error                                                  |          |                       |                                                                  |      |          | ±5   | LSB  |

| RLADDER       | Ladder Resistance                                           |          | Vref=V                | /cc                                                              | 10   |          | 40   | kΩ   |

| <b>t</b> CONV | 10-bit Conversion Time, Sample & Hold<br>Function Available |          | Vref=V                | /cc=5V,                                                          | 3.3  |          |      | μS   |

| <b>t</b> CONV | 8-bit Conversion Time, Sample & Hold<br>Function Available  |          | Vref=V                | /cc=5V,                                                          | 2.8  |          |      | μS   |

| <b>t</b> SAMP | Sampling Time                                               |          |                       |                                                                  | 0.3  |          |      | μS   |

| Vref          | Reference Voltage                                           |          |                       |                                                                  | 3.0  |          | Vcc  | V    |

| VIA           | Analog Input Voltage                                        |          |                       |                                                                  | 0    |          | Vref | V    |

| Table 5.3 | <b>A/D Conversion</b> | Characteristics (1) |

|-----------|-----------------------|---------------------|

|-----------|-----------------------|---------------------|

NOTES:

1. Referenced to Vcc=AVcc=VREF=3.3 to 5.5V, Vss=AVss=0V at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified.

2.  $\phi AD$  frequency must be 10 MHz or less.

3. When sample & hold function is disabled,  $\phi$ AD frequency must be 250 kHz or more, in addition to the limitation in Note 2.

4. When sample & hold function is enabled,  $\phi$ AD frequency must be 1MHz or more, in addition to the limitation in Note 2.

## VCC1=VCC2=5V

#### **Timing Requirements**

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

#### Table 5.11 External Clock Input (XIN input) (1)

| Symbol | Parameter                             | Stan | Unit |      |

|--------|---------------------------------------|------|------|------|

| Symbol | Falametei                             |      | Max. | Onit |

| tc     | External Clock Input Cycle Time       | 62.5 |      | ns   |

| tw(H)  | External Clock Input HIGH Pulse Width | 25   |      | ns   |

| tw(L)  | External Clock Input LOW Pulse Width  | 25   |      | ns   |

| tr     | External Clock Rise Time              |      | 15   | ns   |

| tf     | External Clock Fall Time              |      | 15   | ns   |

NOTES:

1. The condition is Vcc1=Vcc2=3.0 to 5.0V.

#### Table 5.12 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                         | Stan | Unit     |       |

|----------------|---------------------------------------------------|------|----------|-------|

| Symbol         | Parameter                                         |      | Max.     | Offic |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait) |      | (NOTE 1) | ns    |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait)    |      | (NOTE 2) | ns    |

| tsu(DB-RD)     | Data Input Setup Time                             | 40   |          | ns    |

| tsu(RDY-BCLK)  | RDY Input Setup Time                              | 30   |          | ns    |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                             | 40   |          | ns    |

| th(RD-DB)      | Data Input Hold Time                              | 0    |          | ns    |

| th(BCLK-RDY)   | RDY Input Hold Time                               | 0    |          | ns    |

| th(BCLK-HOLD)  | HOLD Input Hold Time                              | 0    |          | ns    |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 45[ns]$$

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)X10^9}{f(BCLK)} - 45[ns] \qquad n \text{ is "2" for 1-wait setting.}$$

## VCC1=VCC2=5V

#### **Timing Requirements**

#### (VCC1 = VCC2 = 5V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

#### Table 5.19 Timer B Input (Counter Input in Event Counter Mode)

| Symbol  | Parameter                                            | Star | Standard |      |

|---------|------------------------------------------------------|------|----------|------|

|         | Falameter                                            | Min. | Max.     | Unit |

| tc(TB)  | TBiIN Input Cycle Time (counted on one edge)         | 100  |          | ns   |

| tw(TBH) | TBiIN Input HIGH Pulse Width (counted on one edge)   | 40   |          | ns   |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on one edge)    | 40   |          | ns   |

| tc(TB)  | TBiIN Input Cycle Time (counted on both edges)       | 200  |          | ns   |

| tw(TBH) | TBiIN Input HIGH Pulse Width (counted on both edges) | 80   |          | ns   |

| tw(TBL) | TBiIN Input LOW Pulse Width (counted on both edges)  | 80   |          | ns   |

#### Table 5.20 Timer B Input (Pulse Period Measurement Mode)

| Symbol  | Parameter                    | Stan | dard | Unit  |

|---------|------------------------------|------|------|-------|

| Symbol  | Farameter                    | Min. | Max. | Offic |

| tc(TB)  | TBiIN Input Cycle Time       | 400  |      | ns    |

| tw(TBH) | TBiIN Input HIGH Pulse Width | 200  |      | ns    |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200  |      | ns    |

#### Table 5.21 Timer B Input (Pulse Width Measurement Mode)

| Symbol  | Parameter                    | Stan | dard | Unit  |

|---------|------------------------------|------|------|-------|

|         | Falameter                    | Min. | Max. | Offic |

| tc(TB)  | TBiIN Input Cycle Time       | 400  |      | ns    |

| tw(TBH) | TBilN Input HIGH Pulse Width | 200  |      | ns    |

| tw(TBL) | TBiIN Input LOW Pulse Width  | 200  |      | ns    |

#### Table 5.22 A/D Trigger Input

| Symbol Parameter | Parameter                   | Stan | Unit |      |

|------------------|-----------------------------|------|------|------|

| Symbol           | Falameter                   | Min. | Max. | Onit |

| tc(AD)           | ADTRG Input Cycle Time      | 1000 |      | ns   |

| tw(ADL)          | ADTRG input LOW Pulse Width | 125  |      | ns   |

#### Table 5.23 Serial Interface

| Symbol          | Parameter                   | Stan | Standard | Unit  |  |

|-----------------|-----------------------------|------|----------|-------|--|

| Symbol          | Farameter                   | Min. | Max.     | Offit |  |

| tc(CK)          | CLKi Input Cycle Time       | 200  |          | ns    |  |

| tw(CKH)         | CLKi Input HIGH Pulse Width | 100  |          | ns    |  |

| tw(CKL)         | CLKi Input LOW Pulse Width  | 100  |          | ns    |  |

| td(C-Q)         | TXDi Output Delay Time      |      | 80       | ns    |  |

| th(C-Q)         | TXDi Hold Time              | 0    |          | ns    |  |

| tsu(D-C)        | RXDi Input Setup Time       | 70   |          | ns    |  |

| <b>t</b> h(C-D) | RXDi Input Hold Time        | 90   |          | ns    |  |

#### Table 5.24 External Interrupt INTi Input

| Symbol  | Parameter                   | Stan | dard | Unit |

|---------|-----------------------------|------|------|------|

| Symbol  | Falanetei                   | Min. | Max. | Onit |

| tw(INH) | INTi Input HIGH Pulse Width | 250  |      | ns   |

| tw(INL) | INTi Input LOW Pulse Width  | 250  |      | ns   |

| Symbol | Paramet                                          | or                                   | Mea                                        | suring Condition                                                            |      | Standar | d    | Unit |

|--------|--------------------------------------------------|--------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------|------|---------|------|------|

| Symbol | i didilici                                       | ei                                   | Wed.                                       |                                                                             | Min. | Тур.    | Max. | Onit |

| Icc    | Power Supply Current<br>(Vcc1=Vcc2=2.7V to 3.6V) | In single-chip<br>mode, the output   | Mask ROM                                   | f(XIN)=10MHz<br>No division                                                 |      | 8       | 11   | mA   |

|        |                                                  | pins are open and other pins are Vss | One Time<br>Flash                          | f(XIN)=10MHz,<br>No division                                                |      | 8       | 13   | mA   |

|        |                                                  |                                      | Flash<br>Memory                            | f(XIN)=10MHz,<br>No division                                                |      | 8       | 13   | mA   |

|        |                                                  |                                      | Flash Memory<br>Program                    | f(XIN)=10MHz,<br>VCC1=3.0V                                                  |      | 12      |      | mA   |

|        |                                                  |                                      | One Time<br>Flash Program                  | f(XIN)=10MHz,<br>VCC1=3.0V                                                  |      | 12      |      | mA   |

|        |                                                  |                                      | Flash Memory<br>Erase                      | f(XIN)=10MHz,<br>VCC1=3.0V                                                  |      | 22      |      | mA   |

|        |                                                  |                                      | Mask ROM                                   | f(XCIN)=32kHz<br>Low power dissipation<br>mode, ROM <sup>(3)</sup>          |      | 25      |      | μΑ   |

|        |                                                  |                                      | One Time<br>Flash                          | f(XCIN)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |      | 25      |      | μΑ   |

|        |                                                  |                                      |                                            | f(XCIN)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |      | 350     |      | μΑ   |

|        |                                                  |                                      | Flash Memory                               | f(XCIN)=32kHz<br>Low power dissipation<br>mode, RAM <sup>(3)</sup>          |      | 25      |      | μA   |

|        |                                                  |                                      |                                            | f(XCIN)=32kHz<br>Low power dissipation<br>mode, Flash Memory <sup>(3)</sup> |      | 420     |      | μΑ   |

|        |                                                  |                                      | Mask ROM<br>One Time Flash<br>Flash Memory | f(XCIN)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability High  |      | 6.0     |      | μΑ   |

|        |                                                  |                                      |                                            | f(XCIN)=32kHz<br>Wait mode <sup>(2)</sup> ,<br>Oscillation capability Low   |      | 1.8     |      | μΑ   |

|        |                                                  |                                      |                                            | Stop mode<br>Topr =25°C                                                     |      | 0.7     | 3.0  | μΑ   |

| Table 5.28 | Electrical Characteristics | s (2) <sup>(1)</sup> |

|------------|----------------------------|----------------------|

|------------|----------------------------|----------------------|

NOTES:

1. Referenced to Vcc1=Vcc2=2.7 to 3.3V, Vss = 0V at Topr = -20 to 85°C / -40 to 85°C, f(XIN)=10MHz unless otherwise Specified.

With one timer operated using fC32.

This indicates the memory in which the program to be executed exists.

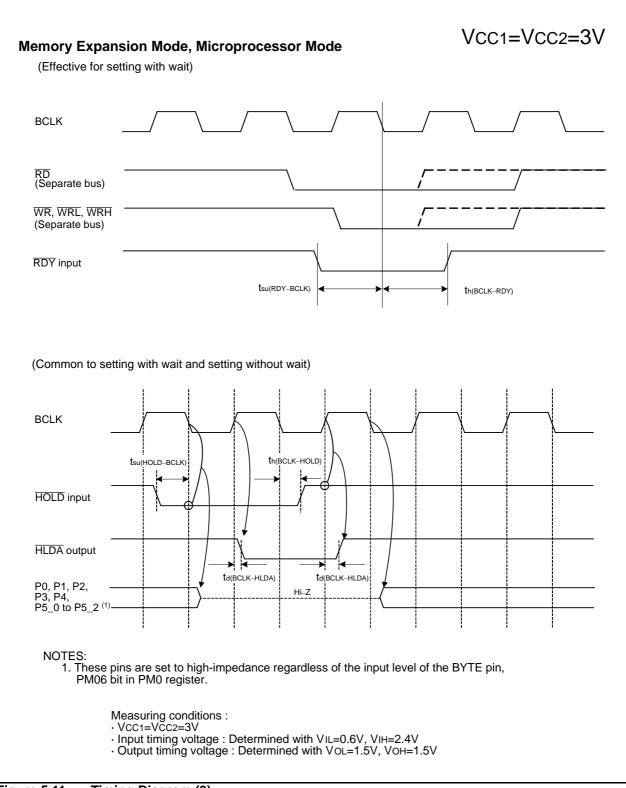

## VCC1=VCC2=3V

#### Timing Requirements

#### (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to 85°C / -40 to 85°C unless otherwise specified)

#### Table 5.29 External Clock Input (XIN input)

| Symbol | Parameter                             | Stan     | dard     | Unit |

|--------|---------------------------------------|----------|----------|------|

| Symbol | Falameter                             | Min.     | Max.     | Onit |

| tc     | External Clock Input Cycle Time       | (NOTE 2) |          | ns   |

| ťw(H)  | External Clock Input HIGH Pulse Width | (NOTE 3) |          | ns   |

| tw(L)  | External Clock Input LOW Pulse Width  | (NOTE 3) |          | ns   |

| tr     | External Clock Rise Time              |          | (NOTE 4) | ns   |

| tr     | External Clock Fall Time              |          | (NOTE 4) | ns   |

NOTES:

- 1. The condition is Vcc1=Vcc2=2.7 to 3.0V.

- 2. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_{1} - 44}$$

[ns]

3. Calculated according to the Vcc1 voltage as follows:

$$\frac{10^{-6}}{20 \times Vcc_{1}-44} \times 0.4$$

[ns]

4. Calculated according to the VCC1 voltage as follows:  $-10 \times Vcc1 + 45$  [ns]

#### Table 5.30 Memory Expansion Mode and Microprocessor Mode

| Symbol         | Parameter                                         | Stan | dard     | Unit |

|----------------|---------------------------------------------------|------|----------|------|

| Symbol         | Farameter                                         | Min. | Max.     | Unit |

| tac1(RD-DB)    | Data Input Access Time (for setting with no wait) |      | (NOTE 1) | ns   |

| tac2(RD-DB)    | Data Input Access Time (for setting with wait)    |      | (NOTE 2) | ns   |

| tsu(DB-RD)     | Data Input Setup Time                             | 50   |          | ns   |

| tsu(RDY-BCLK)  | RDY Input Setup Time                              | 40   |          | ns   |

| tsu(HOLD-BCLK) | HOLD Input Setup Time                             | 50   |          | ns   |

| th(RD-DB)      | Data Input Hold Time                              | 0    |          | ns   |

| th(BCLK-RDY)   | RDY Input Hold Time                               | 0    |          | ns   |

| th(BCLK-HOLD)  | HOLD Input Hold Time                              | 0    |          | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

2. Calculated according to the BCLK frequency as follows:

$$\frac{(n-0.5)x10^9}{f(BCLK)} - 60[ns]$$

n is "2" for 1-wait setting

## VCC1=VCC2=3V

#### Switching Characteristics

#### (VCC1 = VCC2 = 3V, VSS = 0V, at Topr = -20 to $85^{\circ}$ C / -40 to $85^{\circ}$ C unless otherwise specified)

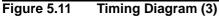

| Table 5.44 | Memory Expansion and Microprocessor Modes (for 1 wait setting and external area |

|------------|---------------------------------------------------------------------------------|

|            | access)                                                                         |

| Cumbal        | Parameter                                                |                   | Stan     | dard | Unit |

|---------------|----------------------------------------------------------|-------------------|----------|------|------|

| Symbol        | Parameter                                                |                   | Min.     | Max. | Unit |

| td(BCLK-AD)   | Address Output Delay Time                                |                   |          | 30   | ns   |

| th(BCLK-AD)   | Address Output Hold Time (in relation to BCLK)           |                   | 0        |      | ns   |

| th(RD-AD)     | Address Output Hold Time (in relation to RD)             |                   | 0        |      | ns   |

| th(WR-AD)     | Address Output Hold Time (in relation to WR)             |                   | (NOTE 2) |      | ns   |

| td(BCLK-CS)   | Chip Select Output Delay Time                            |                   |          | 30   | ns   |

| th(BCLK-CS)   | Chip Select Output Hold Time (in relation to BCLK)       |                   | 0        |      | ns   |

| td(BCLK-ALE)  | ALE Signal Output Delay Time                             |                   |          | 25   | ns   |

| th(BCLK-ALE)  | ALE Signal Output Hold Time                              | _                 | -4       |      | ns   |

| td(BCLK-RD)   | RD Signal Output Delay Time                              | See<br>Figure 5.8 |          | 30   | ns   |

| th(BCLK-RD)   | RD Signal Output Hold Time                               | i igure 5.0       | 0        |      | ns   |

| td(BCLK-WR)   | WR Signal Output Delay Time                              |                   |          | 30   | ns   |

| th(BCLK-WR)   | WR Signal Output Hold Time                               |                   | 0        |      | ns   |

| td(BCLK-DB)   | Data Output Delay Time (in relation to BCLK)             |                   |          | 40   | ns   |

| th(BCLK-DB)   | Data Output Hold Time (in relation to BCLK) (3)          |                   | 4        |      | ns   |

| td(DB-WR)     | Data Output Delay Time (in relation to WR)               |                   | (NOTE 1) |      | ns   |

| th(WR-DB)     | Data Output Hold Time (in relation to WR) <sup>(3)</sup> |                   | (NOTE 2) |      | ns   |

| td(BCLK-HLDA) | HLDA Output Delay Time                                   |                   |          | 40   | ns   |

NOTES:

1. Calculated according to the BCLK frequency as follows:

$\frac{(n-0.5)x10^9}{f(BCLK)} - 40[ns]$  n is "1" for 1-wait setting, f(BCLK) is 12.5MHz or less.

2. Calculated according to the BCLK frequency as follows:

$$\frac{0.5 \times 10^9}{f(BCLK)} - 10[ns]$$

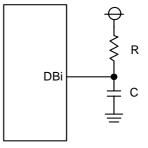

3. This standard value shows the timing when the output is off, and does not show hold time of data bus. Hold time of data bus varies with capacitor volume and pull-up (pull-down) resistance value. Hold time of data bus is expressed in t = -CR X ln (1-VoL / Vcc1) by a circuit of the right figure. For example, when VoL = 0.2Vcc1, C = 30pF, R = 1kΩ, hold time of output "L" level is t = -30pF X 1kΩ X ln(1-0.2Vcc1 / Vcc1)

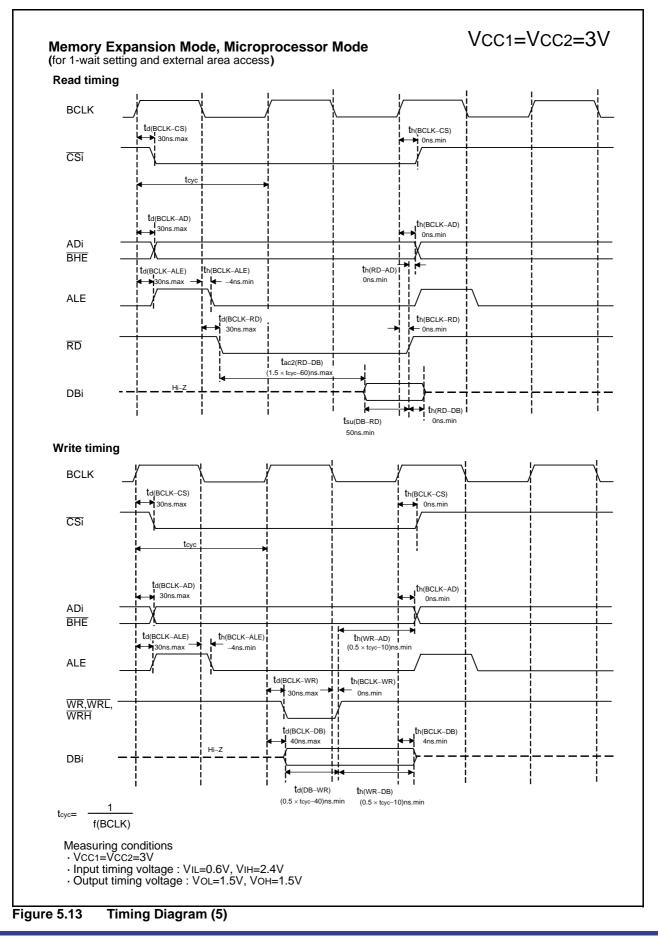

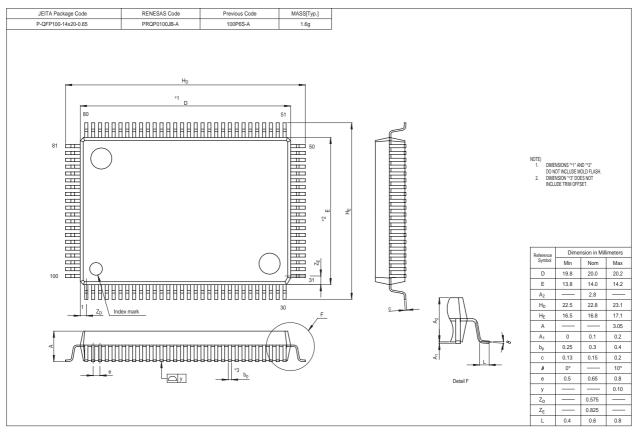

### Appendix 1. Package Dimensions

Diagrams showing the latest package dimensions and mounting information are available in the "Packages" section of the Renesas Technology website.

Rev.1.22 Mar 30, 2007 Page 53 of 53 REJ03B0088-0122

RENESAS

### **REVISION HISTORY**

## M16C/30P Group Datasheet

| Rev. | Date         | Description |                                                                                                                         |  |  |

|------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

|      |              | Page        | Summary                                                                                                                 |  |  |

| 0.70 | Aug 26, 2004 | 1           | First Edition issued                                                                                                    |  |  |

| 0.80 | Mar 18, 2005 | -           | development support tools -> development tools                                                                          |  |  |

|      |              | _           | BCLK -> CPU clock                                                                                                       |  |  |

|      |              | 2           | Table 1.1 Performance Outline of M16C/30P GroupSerial interface is revised.                                             |  |  |

|      |              | 4           | Figure 1.2 Type., Memory Size, and Package is partly revised.                                                           |  |  |

|      |              | 8           | Table 1.4 Pin Detection (2) is partly revised.                                                                          |  |  |

|      |              | 20          | Note 2 Table 5.3 A/D Conversion Characteristics is partly revised.                                                      |  |  |

|      |              | 21          | Symbol of Table 5.4 Power Supply Circuit Timing Characteristics is partly revised.                                      |  |  |

|      |              | 22          | Table 5.5 Electrical Characteristics is revised.                                                                        |  |  |

|      |              | 28          | Table 5.19 Electrical Characteristics is revised.                                                                       |  |  |

| 1.00 | Sep 01, 2005 | 2           | Table 1.1 Performance Outline of M16C/30P Group is partly revised.                                                      |  |  |

|      |              | 4           | Table 1.2 Product List is partly revised.                                                                               |  |  |

|      |              |             | Figure 1.2 Type No., Memory Size, and Package is partly revised.                                                        |  |  |

|      |              | 5           | Figure 1.3 Pin Configuration is partly revised.                                                                         |  |  |

|      |              | 6           | Figure 1.4 Pin Configuration is partly revised.                                                                         |  |  |

|      |              | 7-8         | Tables 1.3 to 1.4 Pin Characteristics are added.                                                                        |  |  |

|      |              | 9           | Table 1.5 Pin Description is revised.                                                                                   |  |  |

|      |              | 14          | 3. Memory is partly revised.                                                                                            |  |  |

|      |              | 15          | Table 4.1 SFR Information is partly revised.                                                                            |  |  |

|      |              | 19          | Table 4.5 SFR Information is partly revised                                                                             |  |  |

|      |              | 21          | Table 5.2 Recommended Operating Conditions is partly revised.                                                           |  |  |

|      |              | 22          | Table 5.3 A/D Conversion Characteristics is partly revised.                                                             |  |  |

|      |              | 25          | Note 1 is added in Table 5.6 External Clock Input (XIN input)                                                           |  |  |

|      |              |             | Table 5.7 Memory Expansion Mode and Microprocessor Mode is added.                                                       |  |  |

|      | 28           |             | Table 5.20 Memory Expansion Mode and Microprocessor Modes (for setting with no wait) is added.                          |  |  |

|      |              |             | Figure 5.2 Ports P0 to P10 Measurement Circuit is added.                                                                |  |  |

|      |              | 29          | Table 5.21 Memory Expansion Mode and Microprocessor Modes (for 1- to 3-wait setting and external area access) is added. |  |  |

|      |              | 32          | Figure 5.5 Timing Diagram (3) is added.                                                                                 |  |  |

|      |              | 33          | Figure 5.6 Timing Diagram (4) is added.                                                                                 |  |  |

|      |              | 34          | Figure 5.7 Timing Diagram (5) is added.                                                                                 |  |  |

|      |              | 36          | Note 1 to 4 are added in Table 5.23 External Clock Input (XIN input)                                                    |  |  |

|      |              |             | Table 5.24 Memory Expansion Mode and Microprocessor Mode is added.                                                      |  |  |

|      |              | 39          | Table 5.37 Memory Expansion Mode and Microprocessor Modes (for setting with no wait) is added.                          |  |  |

|      |              |             | Figure 5.8 Ports P0 to P10 Measurement Circuit is added.                                                                |  |  |

|      |              | 40          | Table 5.38 Memory Expansion Mode and Microprocessor Modes (for 1- to 3-wait setting and external area access) is added. |  |  |

|      |              | 43          | Figure 5.11 Timing Diagram (3) is added.                                                                                |  |  |

**REVISION HISTORY**

## M16C/30P Group Datasheet

| Davi | Dete         |      | Description                                                                                                      |  |

|------|--------------|------|------------------------------------------------------------------------------------------------------------------|--|