Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4011-30i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

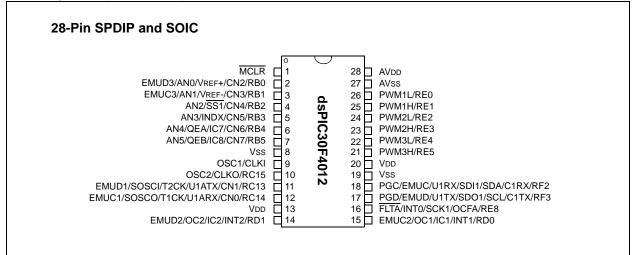

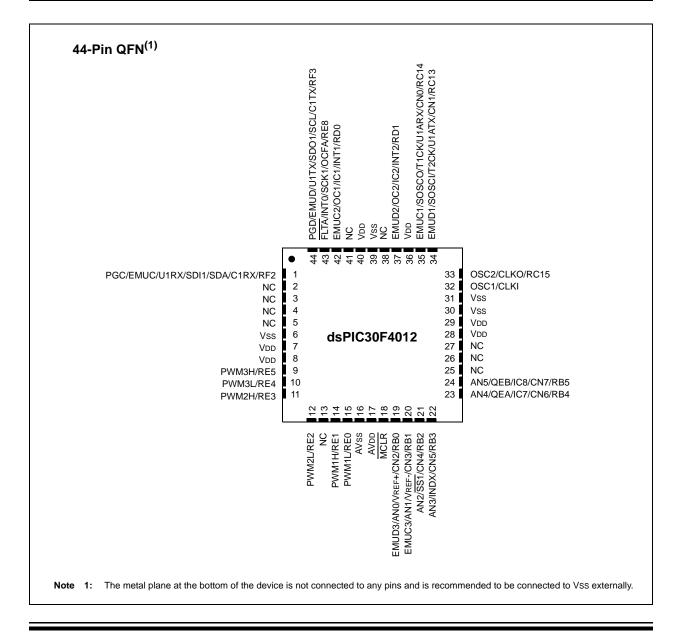

# Pin Diagrams (Continued)

# 2.4.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space may also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly. For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF. For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000. The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

# 2.4.3 BARREL SHIFTER

The barrel shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 to 31 for right shifts, and bit positions 0 to 15 for left shifts.

# 5.3.1.2 Address Error Trap

This trap is initiated when any of the following circumstances occurs:

- 1. A misaligned data word access is attempted.

- 2. A data fetch from an unimplemented data memory location is attempted.

- 3. A data access of an unimplemented program memory location is attempted.

- 4. An instruction fetch from vector space is attempted.

Note: In the MAC class of instructions, wherein the data space is split into X and Y data space, unimplemented X space includes all of Y space and unimplemented Y space includes all of X space.

- 5. Execution of a "BRA #literal" instruction, or a "GOTO #literal" instruction, where literal is an unimplemented program memory address.

- 6. Executing instructions after modifying the PC to point to unimplemented program memory addresses. The PC may be modified by loading a value into the stack and executing a RETURN instruction.

### 5.3.1.3 Stack Error Trap

This trap is initiated under the following conditions:

- 1. The Stack Pointer is loaded with a value which is greater than the (user-programmable) limit value written into the SPLIM register (stack overflow).

- 2. The Stack Pointer is loaded with a value which is less than 0x0800 (simple stack underflow).

#### 5.3.1.4 Oscillator Fail Trap

This trap is initiated if the external oscillator fails and operation becomes reliant on an internal RC backup.

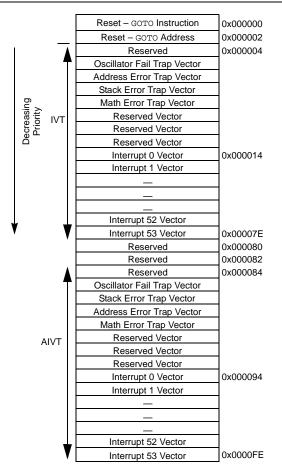

# 5.3.2 HARD AND SOFT TRAPS

It is possible that multiple traps can become active within the same cycle (e.g., a misaligned word stack write to an overflowed address). In such a case, the fixed priority shown in Figure 5-2 is implemented, which may require the user to check if other traps are pending in order to completely correct the Fault.

'Soft' traps include exceptions of priority level 8 through level 11, inclusive. The arithmetic error trap (level 11) falls into this category of traps.

'Hard' traps include exceptions of priority level 12 through level 15, inclusive. The address error (level 12), stack error (level 13) and oscillator error (level 14) traps fall into this category.

Each hard trap that occurs must be acknowledged before code execution of any type may continue. If a lower priority hard trap occurs while a higher priority trap is pending, acknowledged or is being processed, a hard trap conflict will occur.

The device is automatically Reset in a hard trap conflict condition. The TRAPR status bit (RCON<15>) is set when the Reset occurs, so that the condition may be detected in software.

# FIGURE 5-1: TRAP VECTORS

# 7.0 DATA EEPROM MEMORY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

The data EEPROM memory is readable and writable during normal operation over the entire VDD range. The data EEPROM memory is directly mapped in the program memory address space.

The four SFRs used to read and write the program Flash memory are used to access data EEPROM memory, as well. As described in **Section 6.0 "Flash Program Memory"**, these registers are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

The EEPROM data memory allows read and write of single words and 16-word blocks. When interfacing to data memory, NVMADR, in conjunction with the NVMADRU register, is used to address the EEPROM location being accessed. TBLRDL and TBLWTL instructions are used to read and write data EEPROM. The dsPIC30F4011/4012 devices have 1 Kbyte (512 words) of data EEPROM, with an address range from 0x7FFC00 to 0x7FFFE.

A word write operation should be preceded by an erase of the corresponding memory location(s). The write typically requires 2 ms to complete, but the write time will vary with voltage and temperature. A program or erase operation on the data EEPROM does not stop the instruction flow. The user is responsible for waiting for the appropriate duration of time before initiating another data EEPROM write/erase operation. Attempting to read the data EEPROM while a programming or erase operation is in progress results in unspecified data.

Control bit, WR, initiates write operations, similar to program Flash writes. This bit cannot be cleared, only set, in software. This bit is cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a  $\overline{\text{MCLR}}$  Reset, or a WDT Time-out Reset, during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The address register, NVMADR, remains unchanged.

Note: Interrupt flag bit, NVMIF in the IFS0 register, is set when write is complete. It must be cleared in software.

# 7.1 Reading the Data EEPROM

A TBLRD instruction reads a word at the current program word address. This example uses W0 as a pointer to data EEPROM. The result is placed in register W4, as shown in Example 7-1.

#### EXAMPLE 7-1: DATA EEPROM READ

| MOV    | #LOW_ADDR_WORD,W0  | ; | Init | Pointer     |

|--------|--------------------|---|------|-------------|

| MOV    | #HIGH_ADDR_WORD,W1 |   |      |             |

| MOV    | W1,TBLPAG          |   |      |             |

| TBLRDL | [ WO ], W4         | ; | read | data EEPROM |

# 7.2 Erasing Data EEPROM

7.2.1 ERASING A BLOCK OF DATA EEPROM

In order to erase a block of data EEPROM, the NVMADRU and NVMADR registers must initially point to the block of memory to be erased. Configure NVMCON for erasing a block of data EEPROM and set the WR and WREN bits in the NVMCON register. Setting the WR bit initiates the erase, as shown in Example 7-2.

#### EXAMPLE 7-2: DATA EEPROM BLOCK ERASE

```

; Select data EEPROM block, WR, WREN bits

MOV

#0x4045,W0

MOV

W0 NVMCON

; Initialize NVMCON SFR

; Start erase cycle by setting WR after writing key sequence

DISI

; Block all interrupts with priority < 7

#5

; for next 5 instructions

MOV

#0x55,W0

;

W0 NVMKEY

MOV

; Write the 0x55 key

#0xAA,W1

MOV

MOV

W1 NVMKEY

; Write the OxAA key

BSET

NVMCON, #WR

; Initiate erase sequence

NOP

NOP

; Erase cycle will complete in 2mS. CPU is not stalled for the Data Erase Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine erasure complete

```

#### 7.2.2 ERASING A WORD OF DATA EEPROM

The TBLPAG and NVMADR registers must point to the block. Select erase a block of data Flash and set the WR and WREN bits in the NVMCON register. Setting the WR bit initiates the erase, as shown in Example 7-3.

# EXAMPLE 7-3: DATA EEPROM WORD ERASE

```

; Select data EEPROM word, WR, WREN bits

#0x4044,W0

MOV

MOV

W0 NVMCON

; Start erase cycle by setting WR after writing key sequence

; Block all interrupts with priority <7

DISI

#5

; for next 5 instructions

#0x55,W0

MOV

;

MOV

W0 NVMKEY

; Write the 0x55 key

MOV

#0xAA,W1

;

W1 NVMKEY

MOV

; Write the OxAA key

; Initiate erase sequence

BSET

NVMCON, #WR

NOP

NOP

; Erase cycle will complete in 2mS. CPU is not stalled for the Data Erase Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine erasure complete

```

# dsPIC30F4011/4012

NOTES:

# TABLE 14-1: QEI REGISTER MAP<sup>(1)</sup>

| SFR<br>Name | Addr.                          | Bit 15 | Bit 14              | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6               | Bit 5               | Bit 4   | Bit 3   | Bit 2  | Bit 1 | Bit 0    | Reset State         |

|-------------|--------------------------------|--------|---------------------|---------|--------|--------|--------|-------|-------|-------|---------------------|---------------------|---------|---------|--------|-------|----------|---------------------|

| QEICON      | 0122                           | CNTERR | _                   | QEISIDL | INDX   | UPDN   | QEIM2  | QEIM1 | QEIM0 | SWPAB | -                   | TQGATE              | TQCKPS1 | TQCKPS0 | POSRES | TQCS  | UPDN_SRC | 0000 0000 0000 0000 |

| DFLTCON     | 0124                           |        | —                   |         |        | Ι      | IMV1   | IMV0  | CEID  | QEOUT | QECK2               | QECK1               | QECK0   | _       | _      | _     | _        | 0000 0000 0000 0000 |

| POSCNT      | VT 0126 Position Counter<15:0> |        |                     |         |        |        |        |       |       |       | 0000 0000 0000 0000 |                     |         |         |        |       |          |                     |

| MAXCNT      | 0128                           |        | Maximun Count<15:0> |         |        |        |        |       |       |       |                     | 1111 1111 1111 1111 |         |         |        |       |          |                     |

| ADPCFG      | 02A8                           | _      | —                   | _       | —      | _      | —      | _     | PCFG8 | PCFG7 | PCFG6               | PCFG5               | PCFG4   | PCFG3   | PCFG2  | PCFG1 | PCFG0    | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

# 15.0 MOTOR CONTROL PWM MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

This module simplifies the task of generating multiple, synchronized Pulse-Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- Three-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

The PWM module has the following features:

- 6 PWM I/O pins with 3 duty cycle generators

- Up to 16-bit resolution

- 'On-the-Fly' PWM frequency changes

- Edge and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation

- 'Special Event' comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

This module contains 3 duty cycle generators, numbered 1 through 3. The module has 6 PWM output pins, numbered PWM1H/PWM1L through PWM3H/PWM3L. The six I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

The PWM module allows several modes of operation which are beneficial for specific power control applications.

# 15.1.4 DOUBLE UPDATE MODE

In the Double Update mode (PTMOD<1:0> = 11), an interrupt event is generated each time the PTMR register is equal to zero, as well as each time a period match occurs. The postscaler selection bits have no effect in this mode of the timer.

The Double Update mode provides two additional functions to the user. First, the control loop bandwidth is doubled because the PWM duty cycles can be updated, twice per period. Second, asymmetrical center-aligned PWM waveforms can be generated which are useful for minimizing output waveform distortion in certain motor control applications.

**Note:** Programming a value of 0x0001 in the Period register could generate a continuous interrupt pulse, and hence, must be avoided.

# 15.1.5 PWM TIME BASE PRESCALER

The input clock to PTMR (Fosc/4) has prescaler options of 1:1, 1:4, 1:16 or 1:64, selected by control bits, PTCKPS<1:0>, in the PTCON SFR. The prescaler counter is cleared when any of the following occurs:

- A write to the PTMR register

- A write to the PTCON register

- Any device Reset

The PTMR register is not cleared when PTCON is written.

#### 15.1.6 PWM TIME BASE POSTSCALER

The match output of PTMR can optionally be postscaled through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling).

The postscaler counter is cleared when any of the following occurs:

- A write to the PTMR register

- A write to the PTCON register

- Any device Reset

The PTMR register is not cleared when the PTCON register is written.

# 15.2 PWM Period

PTPER is a 15-bit register and is used to set the counting period for the PWM time base. PTPER is a double-buffered register. The PTPER buffer contents are loaded into the PTPER register at the following instants:

- <u>Free-Running and Single-Shot modes:</u> When the PTMR register is reset to zero after a match with the PTPER register.

- Continuous Up/Down Count modes: When the PTMR register is zero.

The value held in the PTPER buffer is automatically loaded into the PTPER register when the PWM time base is disabled (PTEN = 0).

The PWM period can be determined using Equation 15-1:

### EQUATION 15-1: PWM PERIOD

$$T_{PWM} = T_{CY} \bullet (PTPER + 1) \bullet PTMR Prescale Value$$

If the PWM time base is configured for one of the Continuous Up/Down Count modes, the PWM period is provided by Equation 15-2.

#### EQUATION 15-2: PWM PERIOD (CENTER-ALIGNED MODE)

$T_{PWM} = T_{CY} \bullet 2 \bullet PTPER + 1) \bullet PTMR Prescale Value$

The maximum resolution (in bits) for a given device oscillator and PWM frequency can be determined using Equation 15-3:

# EQUATION 15-3: PWM RESOLUTION

$Resolution = \frac{\log (2 \bullet TPWM/TCY)}{\log (2)}$

# 18.3.4 TRANSMIT INTERRUPT

The Transmit Interrupt Flag (U1TXIF or U2TXIF) is located in the corresponding interrupt flag register.

The transmitter generates an edge to set the UxTXIF bit. The condition for generating the interrupt depends on UTXISEL control bit:

- a) If UTXISEL = 0, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR). This implies that the transmit buffer has at least one empty word.

- b) If UTXISEL = 1, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR) and the transmit buffer is empty.

Switching between the two interrupt modes during operation is possible and sometimes offers more flexibility.

#### 18.3.5 TRANSMIT BREAK

Setting the UTXBRK bit (UxSTA<11>) will cause the UxTX line to be driven to logic '0'. The UTXBRK bit overrides all transmission activity. Therefore, the user should generally wait for the transmitter to be Idle before setting UTXBRK.

To send a Break character, the UTXBRK bit must be set by software and must remain set for a minimum of 13 baud clock cycles. The UTXBRK bit is then cleared by software to generate Stop bits. The user must wait for a duration of at least one or two baud clock cycles in order to ensure a valid Stop bit(s) before reloading the UxTXB or starting other transmitter activity. Transmission of a Break character does not generate a transmit interrupt.

# 18.4 Receiving Data

#### 18.4.1 RECEIVING IN 8-BIT OR 9-BIT DATA MODE

The following steps must be performed while receiving 8-bit or 9-bit data:

- 1. Set up the UART (see Section 18.3.1 "Transmitting in 8-bit Data Mode").

- 2. Enable the UART (see Section 18.3.1 "Transmitting in 8-bit Data Mode").

- A receive interrupt will be generated when one or more data words have been received, depending on the receive interrupt settings specified by the URXISEL bits (UxSTA<7:6>).

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- Read the received data from UxRXREG. The act of reading UxRXREG will move the next word to the top of the receive FIFO and the PERR and FERR values will be updated.

### 18.4.2 RECEIVE BUFFER (UXRXB)

The receive buffer is 4 words deep. Including the Receive Shift register (UxRSR), the user effectively has a 5-word deep FIFO buffer.

URXDA (UxSTA<0>) = 1 indicates that the receive buffer has data available. URXDA = 0 implies that the buffer is empty. If a user attempts to read an empty buffer, the old values in the buffer will be read and no data shift will occur within the FIFO.

The FIFO is reset during any device Reset. It is not affected when the device enters or wakes up from a power-saving mode.

# 18.4.3 RECEIVE INTERRUPT

The Receive Interrupt Flag (U1RXIF or U2RXIF) can be read from the corresponding interrupt flag register. The interrupt flag is set by an edge generated by the receiver. The condition for setting the receive interrupt flag depends on the settings specified by the URXISEL<1:0> (UxSTA<7:6>) control bits.

- a) If URXISEL<1:0> = 00 or 01, an interrupt is generated every time a data word is transferred from the Receive Shift register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:0> = 10, an interrupt is generated when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer which, as a result of the transfer, contains 3 characters.

- c) If URXISEL<1:0> = 11, an interrupt is set when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer which, as a result of the transfer, contains 4 characters (i.e., becomes full).

Switching between the interrupt modes during operation is possible, though generally not advisable during normal operation.

# 18.5 Reception Error Handling

#### 18.5.1 RECEIVE BUFFER OVERRUN ERROR (OERR BIT)

The OERR bit (UxSTA<1>) is set if all of the following conditions occur:

- a) The receive buffer is full.

- b) The Receive Shift register is full, but unable to transfer the character to the receive buffer.

- c) The Stop bit of the character in the UxRSR is detected, indicating that the UxRSR needs to transfer the character to the buffer.

Once OERR is set, no further data is shifted in UxRSR (until the OERR bit is cleared in software or a Reset occurs). The data held in UxRSR and UxRXREG remains valid.

# 18.9 Auto-Baud Support

To allow the system to determine baud rates of received characters, the input can be optionally linked to a selected capture input (IC1 for UART1, IC2 for UART2). To enable this mode, the user must program the input capture module to detect the falling and rising edges of the Start bit.

# 18.10 UART Operation During CPU Sleep and Idle Modes

#### 18.10.1 UART OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'. If entry into Sleep mode occurs while a transmission is in progress, then the transmission is aborted. The UxTX pin is driven to logic '1'. Similarly, if entry into Sleep mode occurs while a reception is in progress, then the reception is aborted. The UxSTA, UxMODE, UxBRG, transmit and receive registers and buffers, are not affected by Sleep mode.

If the WAKE bit (UxMODE<7>) is set before the device enters Sleep mode, then a falling edge on the UxRX pin will generate a receive interrupt. The Receive Interrupt Select Mode bit (URXISEL) has no effect for this function. If the receive interrupt is enabled, then this will wake-up the device from Sleep. The UARTEN bit must be set in order to generate a wake-up interrupt.

# 18.10.2 UART OPERATION DURING CPU IDLE MODE

For the UART, the USIDL bit selects if the module will stop operation when the device enters Idle mode, or whether the module will continue on Idle. If USIDL = 0, the module will continue operation during Idle mode. If USIDL = 1, the module will stop on Idle.

# TABLE 19-1: CAN1 REGISTER MAP<sup>(1)</sup>

| SFR Name   | Addr. | Bit 15                   | Bit 14        | Bit 13        | Bit 12     | Bit 11      | Bit 10 | Bit 9      | Bit 8                    | Bit 7                                       | Bit 6      | Bit 5       | Bit 4       | Bit 3        | Bit 2 | Bit 1               | Bit 0               | Reset State         |

|------------|-------|--------------------------|---------------|---------------|------------|-------------|--------|------------|--------------------------|---------------------------------------------|------------|-------------|-------------|--------------|-------|---------------------|---------------------|---------------------|

| C1RXF0SID  | 0300  | _                        | _             | _             |            |             | F      | Receive Ad | cceptance                | Filter 0 Stand                              | dard Iden  | tifier<10:0 | >           |              |       | -                   | EXIDE               | 000u uuuu uuuu uu0u |

| C1RXF0EIDH | 0302  | _                        | _             | _             | _          |             |        |            | Receiv                   | e Acceptance                                | e Filter 0 | Extended    | Identifier- | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXF0EIDL | 0304  | Rece                     | ive Accepta   | nce Filter 0  | Extended   | Identifier< | 5:0>   | —          | —                        | —                                           | —          | —           | _           | —            | —     | _                   | —                   | uuuu uu00 0000 0000 |

| C1RXF1SID  | 0308  | _                        | —             | —             |            |             | F      | Receive Ad | cceptance                | Filter 1 Stand                              | dard Iden  | tifier<10:0 | >           |              |       | _                   | EXIDE               | 000u uuuu uuuu uu0u |

| C1RXF1EIDH | 030A  | _                        | _             | _             | _          |             |        |            | Receiv                   | e Acceptance                                | e Filter 1 | Extended    | Identifier- | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXF1EIDL | 030C  | Rece                     | ive Accepta   | nce Filter 1  | Extended   | Identifier< | 5:0>   | —          | —                        | —                                           | —          | —           | —           | —            | —     | _                   | —                   | uuuu uu00 0000 0000 |

| C1RXF2SID  | 0310  | —                        | _             | _             |            |             | F      | Receive Ad | cceptance                | Filter 2 Stand                              | dard Iden  | tifier<10:0 | >           |              |       | _                   | EXIDE               | 000u uuuu uuuu uu0u |

| C1RXF2EIDH | 0312  | _                        | _             | _             | —          |             |        |            | Receiv                   | e Acceptance                                | e Filter 2 | Extended    | Identifier- | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXF2EIDL | 0314  | Rece                     | ive Accepta   | nce Filter 2  | Extended   | Identifier< | 5:0>   | —          | _                        | _                                           | _          | _           | _           | _            | —     | _                   | _                   | uuuu uu00 0000 0000 |

| C1RXF3SID  | 0318  | _                        | _             | _             |            |             | F      | Receive Ad | cceptance                | Filter 3 Stand                              | dard Iden  | tifier<10:0 | >           |              |       |                     | EXIDE               | 000u uuuu uuuu uu0u |

| C1RXF3EIDH | 031A  | _                        | _             | _             | —          |             |        |            | Receiv                   | e Acceptance                                | e Filter 3 | Extended    | Identifier- | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXF3EIDL | 031C  | Rece                     | ive Accepta   | nce Filter 3  | Extended   | Identifier< | 5:0>   | —          | _                        | _                                           | _          | _           | _           | _            | —     | _                   | _                   | uuuu uu00 0000 0000 |

| C1RXF4SID  | 0320  | _                        | _             | _             |            |             | F      | Receive Ad | cceptance                | Filter 4 Stand                              | dard Iden  | tifier<10:0 | >           |              |       |                     | EXIDE               | 000u uuuu uuuu uu0u |

| C1RXF4EIDH | 0322  | _                        | _             | _             | —          |             |        |            | Receiv                   | e Acceptance                                | e Filter 4 | Extended    | Identifier- | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXF4EIDL | 0324  | Rece                     | ive Accepta   | nce Filter 4  | Extended   | Identifier< | 5:0>   | —          | —                        | —                                           | —          | —           | —           | —            | —     | _                   | —                   | uuuu uu00 0000 0000 |

| C1RXF5SID  | 0328  | —                        | _             | _             |            |             | F      | Receive Ad | cceptance                | Filter 5 Stand                              | dard Iden  | tifier<10:0 | >           |              |       | _                   | EXIDE               | 000u uuuu uuuu uu0u |

| C1RXF5EIDH | 032A  | _                        | _             | _             | —          |             |        |            | Receiv                   | e Acceptance                                | e Filter 5 | Extended    | Identifier- | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXF5EIDL | 032C  | Rece                     | ive Accepta   | nce Filter 5  | Extended   | Identifier< | 5:0>   | —          | _                        | —                                           | —          | _           | _           | _            | —     | _                   | _                   | uuuu uu00 0000 0000 |

| C1RXM0SID  | 0330  | _                        | _             | _             |            |             | R      | eceive Ac  | ceptance                 | Mask 0 Stan                                 | dard Ider  | tifier<10:0 | >           |              |       |                     | MIDE                | 000u uuuu uuuu uu0u |

| C1RXM0EIDH | 0332  | _                        | _             | _             | _          |             |        |            | Receiv                   | e Acceptance                                | e Mask 0   | Extended    | Identifier  | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXM0EIDL | 0334  | Recei                    | ive Accepta   | nce Mask 0    | Extended   | Identifier< | 5:0>   | —          | —                        | —                                           | —          | —           | —           | —            | —     | _                   | —                   | uuuu uu00 0000 0000 |

| C1RXM1SID  | 0338  | _                        | _             | _             |            |             | R      | eceive Ac  | ceptance                 | Mask 1 Stand                                | dard Ider  | tifier<10:0 | >           |              |       |                     | MIDE                | 000u uuuu uuuu uu0u |

| C1RXM1EIDH | 033A  | _                        | _             | _             | _          |             |        |            | Receiv                   | e Acceptance                                | e Mask 1   | Extended    | Identifier  | <17:6>       |       |                     |                     | 0000 uuuu uuuu uuuu |

| C1RXM1EIDL | 033C  | Recei                    | ive Accepta   | nce Mask 1    | Extended   | Identifier< | 5:0>   | —          | —                        | —                                           | —          | —           | —           | —            | —     | _                   | —                   | uuuu uu00 0000 0000 |

| C1TX2SID   | 0340  | Trans                    | smit Buffer   | 2 Standard I  | dentifier< | 0:6>        | —      | —          | —                        | Tra                                         | insmit Bu  | ffer 2 Star | dard Ider   | ntifier<5:0> |       | SRR                 | TXIDE               | uuuu u000 uuuu uuuu |

| C1TX2EID   | 0342  | Transmit B               | Buffer 2 Exte | nded Identifi | er<17:14>  | —           | _      | _          | _                        | Transmit Buffer 2 Extended Identifier<13:6> |            |             |             |              |       |                     | uuuu 0000 uuuu uuuu |                     |

| C1TX2DLC   | 0344  |                          | Transmit B    | uffer 2 Exter | nded Ident | fier<5:0>   |        | TXRTR      | TXRB1                    | TXRB0                                       |            | DLO         | C<3:0>      |              | —     | _                   | _                   | uuuu uuuu uuuu u000 |

| C1TX2B1    | 0346  | Transmit Buffer 2 Byte 1 |               |               |            |             |        |            | Transmit Buffer 2 Byte 0 |                                             |            |             |             |              |       | uuuu uuuu uuuu uuuu |                     |                     |

| C1TX2B2    | 0348  | Transmit Buffer 2 Byte 3 |               |               |            |             |        |            | Transmit Buffer 2 Byte 2 |                                             |            |             |             |              |       | uuuu uuuu uuuu uuuu |                     |                     |

| C1TX2B3    | 034A  | Transmit Buffer 2 Byte 5 |               |               |            |             |        |            | Transmit Buffer 2 Byte 4 |                                             |            |             |             |              |       | uuuu uuuu uuuu uuuu |                     |                     |

| C1TX2B4    | 034C  |                          |               | Tran          | smit Buffe | r 2 Byte 7  |        |            |                          |                                             |            | Trar        | smit Buff   | er 2 Byte 6  |       |                     |                     | uuuu uuuu uuuu uuuu |

| C1TX2CON   | 034E  | —                        | —             | —             | —          | —           | —      | —          | —                        | —                                           | TXABT      | TXLARB      | TXERR       | TXREQ        | —     | TXPF                | RI<1:0>             | 0000 0000 0000 0000 |

| C1TX1SID   | 0350  | Trans                    | smit Buffer   | 1 Standard I  | dentifier< | 0:6>        | —      | _          | —                        | Tra                                         | Insmit Bu  | ffer 1 Star | Idard Ider  | tifier<5:0>  |       | SRR                 | TXIDE               | uuuu u000 uuuu uuuu |

| C1TX1EID   | 0352  | Transmit B               | Buffer 1 Exte | nded Identifi | er<17:14>  | _           | _      | _          | _                        | Transmit Buffer 1 Extended Identifier<13:6> |            |             |             |              |       |                     | uuuu 0000 uuuu uuuu |                     |

| C1TX1DLC   | 0354  |                          | Transmit B    | uffer 1 Exter | nded Ident | fier<5:0>   |        | TXRTR      | TXRB1                    | TXRB0                                       |            | DLO         | C<3:0>      |              | _     | _                   | —                   | uuuu uuuu uuuu u000 |

| C1TX1B1    | 0356  |                          |               | Tran          | smit Buffe | r 1 Byte 1  |        | •          |                          |                                             |            | Trar        | smit Buff   | er 1 Byte 0  |       |                     |                     | uuuu uuuu uuuu uuuu |

u = uninitialized bit; — = unimplemented bit, read as '0'

Legend: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Note 1:

### 21.2.3 LP OSCILLATOR CONTROL

Enabling the LP oscillator is controlled with two elements:

- Current oscillator group bits, COSC<1:0>

- LPOSCEN bit (OSCCON<1>)

The LP oscillator is on (even during Sleep mode) if LPOSCEN = 1. The LP oscillator is the device clock if:

- COSC<1:0> = 00 (LP selected as main osc.) and

- LPOSCEN = 1

Keeping the LP oscillator on at all times allows for a fast switch to the 32 kHz system clock for lower power operation. Returning to the faster main oscillator still requires a start-up time.

# 21.2.4 PHASE LOCKED LOOP (PLL)

The PLL multiplies the clock which is generated by the primary oscillator. The PLL is selectable to have either gains of x4, x8 or x16. Input and output frequency ranges are summarized in Table 21-3.

| TABLE 21-3: PLL FREQUENCY RANGE |

|---------------------------------|

|---------------------------------|

| Fin           | PLL<br>Multiplier | Fout           |

|---------------|-------------------|----------------|

| 4 MHz-10 MHz  | x4                | 16 MHz-40 MHz  |

| 4 MHz-10 MHz  | x8                | 32 MHz-80 MHz  |

| 4 MHz-7.5 MHz | x16               | 64 MHz-120 MHz |

The PLL features a lock output which is asserted when the PLL enters a phase locked state. Should the loop fall out of lock (e.g., due to noise), the lock signal is rescinded. The state of this signal is reflected in the read-only LOCK bit in the OSCCON register.

# 21.2.5 FAST RC OSCILLATOR (FRC)

The FRC oscillator is a fast (7.37 MHz,  $\pm 2\%$  nominal), internal RC oscillator. This oscillator is intended to provide reasonable device operating speeds without the use of an external crystal, ceramic resonator or RC network. Using the x4, x8 and x16 PLL options, higher operational frequencies can be generated.

The dsPIC30F operates from the FRC oscillator whenever the Current Oscillator Selection (COSC<1:0>) control bits in the OSCCON register (OSCCON<13:12>) are set to '01'.

There are four tuning bits (TUN<3:0>) for the FRC oscillator in the OSCCON register. These tuning bits allow the FRC oscillator frequency to be adjusted as close to 7.37 MHz as possible, depending on the device operating conditions. The FRC oscillator frequency has been calibrated during factory testing. Table 21-4 describes the adjustment range of the TUN<3:0> bits.

| Note: | OSCTUN functionality has been provided      |

|-------|---------------------------------------------|

|       | to help customers compensate for            |

|       | temperature effects on the FRC frequency    |

|       | over a wide range of temperatures. The      |

|       | tuning step size is an approximation and is |

|       | neither characterized nor tested.           |

# TABLE 21-4: FRC TUNING

| TUN<3:0><br>Bits | FRC Frequency                                                       |

|------------------|---------------------------------------------------------------------|

| 0111             | +10.5%                                                              |

| 0110             | +9.0%                                                               |

| 0101             | +7.5%                                                               |

| 0100             | +6.0%                                                               |

| 0011             | +4.5%                                                               |

| 0010             | +3.0%                                                               |

| 0001             | +1.5%                                                               |

| 0000             | Center Frequency (oscillator is<br>running at calibrated frequency) |

| 1111             | -1.5%                                                               |

| 1110             | -3.0%                                                               |

| 1101             | -4.5%                                                               |

| 1100             | -6.0%                                                               |

| 1011             | -7.5%                                                               |

| 1010             | -9.0%                                                               |

| 1001             | -10.5%                                                              |

| 1000             | -12.0%                                                              |

# 21.2.6 LOW-POWER RC OSCILLATOR (LPRC)

The LPRC oscillator is a component of the Watchdog Timer (WDT) and oscillates at a nominal frequency of 512 kHz. The LPRC oscillator is the clock source for the Power-up Timer (PWRT) circuit, WDT and clock monitor circuits. It may also be used to provide a lowfrequency clock source option for applications where power consumption is critical and timing accuracy is not required.

The LPRC oscillator is always enabled at a POR because it is the clock source for the PWRT. After the PWRT expires, the LPRC oscillator remains on if one of the following is true:

- The Fail-Safe Clock Monitor is enabled

- The WDT is enabled

- The LPRC oscillator is selected as the system clock via the COSC<1:0> control bits in the OSCCON register

If one of the above conditions is not true, the LPRC shuts off after the PWRT expires.

- Note 1: OSC2 pin function is determined by the Primary Oscillator mode selection (FPR<3:0>).

- 2: Note that OSC1 pin cannot be used as an I/O pin, even if the secondary oscillator or an internal clock source is selected at all times.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction, require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or twoword instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

| Note: | For more details on the instruction set, |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|

|       | refer to the "16-bit MCU and DSC         |  |  |  |  |  |  |

|       | Reference Manual" (DS70157).             |  |  |  |  |  |  |

| TABLE 22-1: | SYMBOLS | USED IN | OPCODE D | DESCRIPTIONS |  |

|-------------|---------|---------|----------|--------------|--|

|             |         |         |          |              |  |

| Field           | Description                                                                   |  |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| #text           | Means literal defined by "text"                                               |  |  |  |  |  |  |  |

| (text)          | Means "content of text"                                                       |  |  |  |  |  |  |  |

| [text]          | Means "the location addressed by text"                                        |  |  |  |  |  |  |  |

| { }             | Optional field or operation                                                   |  |  |  |  |  |  |  |

| <n:m></n:m>     | Register bit field                                                            |  |  |  |  |  |  |  |

| .b              | Byte mode selection                                                           |  |  |  |  |  |  |  |

| .d              | Double-Word mode selection                                                    |  |  |  |  |  |  |  |

| .S              | Shadow register select                                                        |  |  |  |  |  |  |  |

| . W             | Word mode selection (default)                                                 |  |  |  |  |  |  |  |

| Acc             | One of two accumulators {A, B}                                                |  |  |  |  |  |  |  |

| AWB             | Accumulator Write-Back Destination Address register ∈ {W13, [W13]+=2}         |  |  |  |  |  |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$ |  |  |  |  |  |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Zero                 |  |  |  |  |  |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                |  |  |  |  |  |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                        |  |  |  |  |  |  |  |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                          |  |  |  |  |  |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                |  |  |  |  |  |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                |  |  |  |  |  |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                               |  |  |  |  |  |  |  |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode        |  |  |  |  |  |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                            |  |  |  |  |  |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                            |  |  |  |  |  |  |  |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be 0                           |  |  |  |  |  |  |  |

| None            | Field does not require an entry, may be blank                                 |  |  |  |  |  |  |  |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate   |  |  |  |  |  |  |  |

| PC              | Program Counter                                                               |  |  |  |  |  |  |  |

| Slit10          | 10-bit signed literal $\in$ {-512511}                                         |  |  |  |  |  |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                         |  |  |  |  |  |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                |  |  |  |  |  |  |  |

# 23.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 23.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 23.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 24.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

# TABLE 24-12: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)                                                                                                                       |  |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended<br>Operating voltage VDD range as described in <b>Section 24.1 "DC</b><br><b>Characteristics</b> ". |  |  |  |  |  |

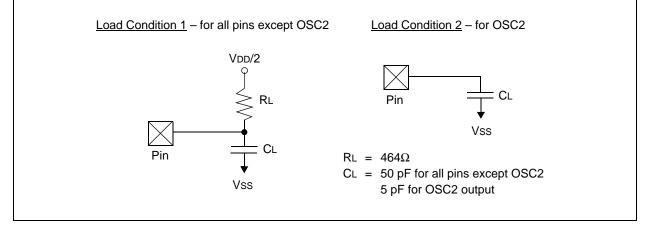

### FIGURE 24-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

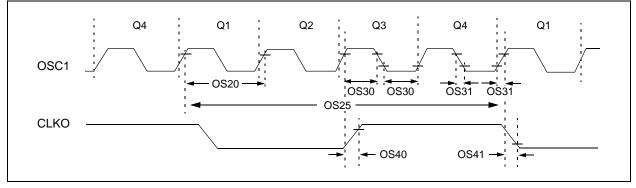

### FIGURE 24-3: EXTERNAL CLOCK TIMING

# dsPIC30F4011/4012

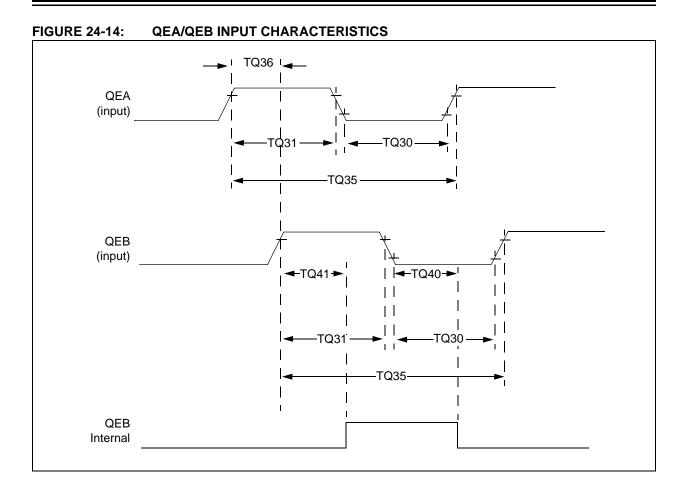

# TABLE 24-30: QUADRATURE DECODER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |       |                                                         |

|--------------------|--------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                        | Тур <sup>(2)</sup>                                                                                                                                                                       | Max | Units | Conditions                                              |

| TQ30               | TQUL   | Quadrature Input Low Time                            | 6 Tcy                                                                                                                                                                                    | —   | ns    |                                                         |

| TQ31               | ΤουΗ   | Quadrature Input High Time                           | 6 Tcy                                                                                                                                                                                    | —   | ns    |                                                         |

| TQ35               | ΤουΙΝ  | Quadrature Input Period                              | 12 TCY                                                                                                                                                                                   | —   | ns    |                                                         |

| TQ36               | ΤουΡ   | Quadrature Phase Period                              | 3 TCY                                                                                                                                                                                    | —   | ns    |                                                         |

| TQ40               | TQUFL  | Filter Time to Recognize Low,<br>with Digital Filter | 3 * N * Tcy                                                                                                                                                                              | —   | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 2)</b> |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter   | 3 * N * Tcy                                                                                                                                                                              | —   | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 2)</b> |

Note 1: These parameters are characterized but not tested in manufacturing.

2: N = Index Channel Digital Filter Clock Divide Select bits. Refer to Section 16. "Quadrature Encoder Interface (QEI)" in the "dsPIC30F Family Reference Manual" (DS70046).

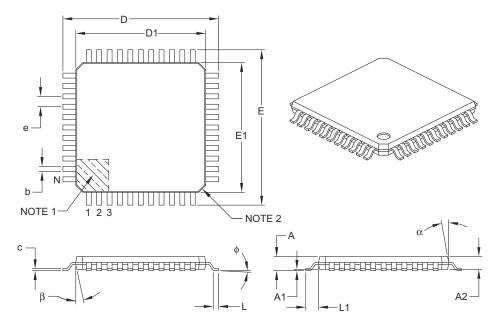

# 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |      |      |  |

|--------------------------|-------------|-----------|------|------|--|

| Dimensi                  | ion Limits  | MIN       | NOM  | MAX  |  |

| Number of Leads          | Ν           | 44        |      |      |  |

| Lead Pitch               | е           | 0.80 BSC  |      |      |  |

| Overall Height           | A           | —         | -    | 1.20 |  |

| Molded Package Thickness | A2          | 0.95      | 1.00 | 1.05 |  |

| Standoff                 | A1          | 0.05      | -    | 0.15 |  |

| Foot Length              | L           | 0.45      | 0.60 | 0.75 |  |

| Footprint                | L1          | 1.00 REF  |      |      |  |

| Foot Angle               | φ           | 0°        | 3.5° | 7°   |  |

| Overall Width            | E           | 12.00 BSC |      |      |  |

| Overall Length           | D           | 12.00 BSC |      |      |  |

| Molded Package Width     | E1          | 10.00 BSC |      |      |  |

| Molded Package Length    | D1          | 10.00 BSC |      |      |  |

| Lead Thickness           | С           | 0.09      | -    | 0.20 |  |

| Lead Width               | b           | 0.30      | 0.37 | 0.45 |  |

| Mold Draft Angle Top     | α           | 11°       | 12°  | 13°  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°  | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B

# INDEX

| Numerics                                                  |  |  |  |  |

|-----------------------------------------------------------|--|--|--|--|

| 10-Bit, High-Speed Analog-to-Digital Converter (ADC) Mod- |  |  |  |  |

| ule                                                       |  |  |  |  |

| 16-bit Up/Down Position Counter Mode90                    |  |  |  |  |

| Count Direction Status90                                  |  |  |  |  |

| Counter Reset90                                           |  |  |  |  |

| Error Checking90                                          |  |  |  |  |

| Α                                                         |  |  |  |  |

| AC Characteristics                                        |  |  |  |  |

| Load Conditions                                           |  |  |  |  |

| Temperature and Voltage Specifications                    |  |  |  |  |

| ADC                                                       |  |  |  |  |

| 1 Msps Configuration Guideline142                         |  |  |  |  |

| 600 ksps Configuration Guideline 143                      |  |  |  |  |

| 750 ksps Configuration Guideline 143                      |  |  |  |  |

| Aborting a Conversion140                                  |  |  |  |  |

| Acquisition Requirements144                               |  |  |  |  |

| ADCHS 137                                                 |  |  |  |  |

| ADCON1                                                    |  |  |  |  |

| ADCON2137                                                 |  |  |  |  |

| ADCON3                                                    |  |  |  |  |

| ADCSSL                                                    |  |  |  |  |

| ADPCFG                                                    |  |  |  |  |

| Configuring Analog Port Pins                              |  |  |  |  |

| Connection Considerations                                 |  |  |  |  |

| Conversion Operation                                      |  |  |  |  |

| Conversion Rate Parameters                                |  |  |  |  |

| Conversion Speeds                                         |  |  |  |  |

| Effects of a Reset                                        |  |  |  |  |

| Operation During CPU Idle Mode                            |  |  |  |  |

| Output Formats                                            |  |  |  |  |

| Power-Down Modes                                          |  |  |  |  |

| Programming the Start of Conversion Trigger               |  |  |  |  |

| Register Map                                              |  |  |  |  |

| Result Buffer                                             |  |  |  |  |

| Selecting the Conversion Clock                            |  |  |  |  |

| Selecting the Conversion Sequence                         |  |  |  |  |

| Voltage Reference Schematic                               |  |  |  |  |

| Address Generator Units                                   |  |  |  |  |

| Alternate 16-bit Timer/Counter                            |  |  |  |  |

| Alternate Interrupt Vector Table                          |  |  |  |  |

| Assembler                                                 |  |  |  |  |

| MPASM Assembler                                           |  |  |  |  |

# В

| Barrel Shifter                  |     |

|---------------------------------|-----|

| Bit-Reversed Addressing         |     |

| Example                         |     |

| Implementation                  |     |

| Modifier Values (table)         |     |

| Sequence Table (16-Entry)       |     |

| Block Diagrams                  |     |

| 10-Bit, High-Speed ADC          |     |

| 16-bit Timer1 Module            |     |

| 16-bit Timer4                   | 76  |

| 16-bit Timer5                   |     |

| 32-bit Timer4/5                 | 75  |

| ADC Analog Input Model          | 144 |

| CAN Buffers and Protocol Engine | 128 |

| Dedicated Port Structure        |     |

| DSP Engine                      |     |

| -                               |     |

| dsPIC30F4011                    |     |

|---------------------------------|-----|

| dsPIC30F4012                    | 11  |

| External Power-on Reset Circuit | 157 |

| I <sup>2</sup> C                | 112 |

| Input Capture Mode              |     |

| Oscillator System               |     |

| Output Compare Mode             |     |

| PWM Module                      |     |

| Quadrature Encoder Interface    |     |

| Reset System                    |     |

| Shared Port Structure           |     |

| SPI                             |     |

| SPI Master/Slave Connection     |     |

| UART Receiver                   |     |

| UART Transmitter                |     |

| BOR. See Brown-out Reset.       |     |

| Brown-out Reset                 |     |

|                                 | 400 |

| Characteristics                 | 182 |

# С

| C Compilers                          |     |

|--------------------------------------|-----|

| MPLAB C18                            | 172 |

| CAN Module                           | 127 |

| Baud Rate Setting                    | 132 |

| CAN1 Register Map                    | 134 |

| Frame Types                          |     |

| Message Reception                    | 130 |

| Message Transmission                 | 131 |

| Modes of Operation                   | 129 |

| Overview                             | 127 |

| Center-Aligned PWM                   | 99  |

| Code Examples                        |     |

| Data EEPROM Block Erase              | 56  |

| Data EEPROM Block Write              | 58  |

| Data EEPROM Read                     | 55  |

| Data EEPROM Word Erase               | 56  |

| Data EEPROM Word Write               | 57  |

| Erasing a Row of Program Memory      | 51  |

| Initiating a Programming Sequence    | 52  |

| Loading Write Latches                | 52  |

| Port Write/Read                      | 60  |

| Code Protection                      | 149 |

| Complementary PWM Operation          | 100 |

| Configuring Analog Port Pins         | 60  |

| Core Overview                        | 17  |

| Core Register Map                    |     |

| Customer Change Notification Service | 235 |

| Customer Notification Service        | 235 |

| Customer Support                     | 235 |

|                                      |     |

# D

| Data Access from Program Memory              |      |

|----------------------------------------------|------|

| Using Program Space Visibility               | . 28 |

| Data Accumulators and Adder/Subtracter       | . 22 |

| Data Space Write Saturation                  | . 24 |

| Overflow and Saturation                      | . 22 |

| Round Logic                                  | . 23 |

| Write-Back                                   | . 23 |

| Data Address Space                           | . 29 |

| Alignment                                    | . 32 |

| Alignment (Figure)                           |      |

| Data Spaces                                  | . 32 |

| Effect of Invalid Memory Accesses            | . 32 |

| MCU and DSP (MAC Class) Instructions Example |      |

|                                              |      |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: | Technical Publications Manager<br>Reader Response                                        | Total Pages Sent                 |  |  |

|------------|------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Fron       |                                                                                          |                                  |  |  |

| FIUI       |                                                                                          |                                  |  |  |

|            | Company<br>Address                                                                       |                                  |  |  |

|            | City / State / ZIP / Country                                                             |                                  |  |  |

|            | Telephone: ()                                                                            | FAX: ()                          |  |  |

| Appl       | ication (optional):                                                                      |                                  |  |  |

| Wou        | ld you like a reply? Y N                                                                 |                                  |  |  |

|            | ce: dsPIC30F4011/4012                                                                    | Literature Number: DS70135G      |  |  |

| Que        | stions:                                                                                  |                                  |  |  |

| 1.         | What are the best features of this document?                                             |                                  |  |  |

| •          |                                                                                          |                                  |  |  |

| 2.         | 2. How does this document meet your hardware and software development needs?             |                                  |  |  |

| -          |                                                                                          |                                  |  |  |

| 3.         | . Do you find the organization of this document easy to follow? If not, why?             |                                  |  |  |

| -          |                                                                                          |                                  |  |  |

| 4.         | What additions to the document do you think would en                                     | nance the structure and subject? |  |  |

| -          |                                                                                          |                                  |  |  |

| 5.         | What deletions from the document could be made without affecting the overall usefulness? |                                  |  |  |

| -          |                                                                                          |                                  |  |  |

| 6.         | Is there any incorrect or misleading information (what a                                 | nd where)?                       |  |  |

| •          |                                                                                          |                                  |  |  |

| 7.         | How would you improve this document?                                                     |                                  |  |  |

| •          |                                                                                          |                                  |  |  |