#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                        |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 30 MIPs                                                                      |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 48KB (16K x 24)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                     |

| Supplier Device Package    | 40-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4011-30i-p |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

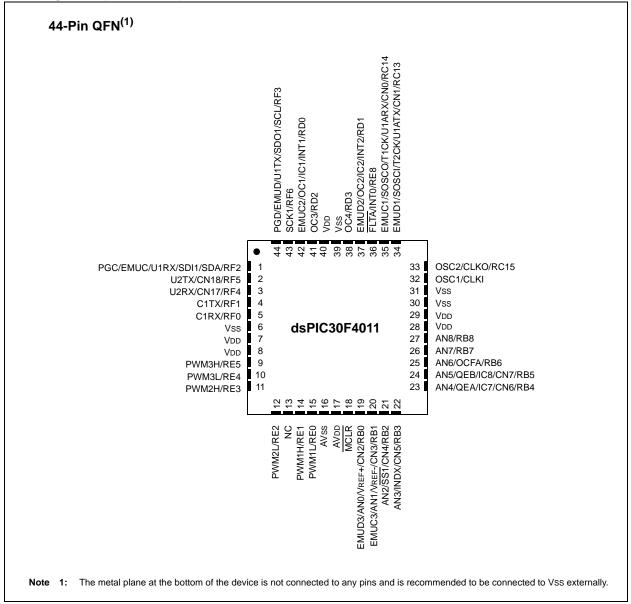

## **Pin Diagrams (Continued)**

| Pin Name        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                             |  |  |  |  |  |  |  |  |

|-----------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| OSC1            | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                         |  |  |  |  |  |  |  |  |

| OSC2            | I/O         | —              | Scillator crystal output. Connects to crystal or resonator in Crystal Oscillator node. Optionally functions as CLKO in RC and EC modes. |  |  |  |  |  |  |  |  |

| PGD             | I/O         | ST             | -Circuit Serial Programming™ data input/output pin.                                                                                     |  |  |  |  |  |  |  |  |

| PGC             | I           | ST             | In-Circuit Serial Programming clock input pin.                                                                                          |  |  |  |  |  |  |  |  |

| RB0-RB8         | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                      |  |  |  |  |  |  |  |  |

| RC13-RC15       | I/O         | ST             | PORTC is a bidirectional I/O port.                                                                                                      |  |  |  |  |  |  |  |  |

| RD0-RD3         | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                      |  |  |  |  |  |  |  |  |

| RE0-RE5,<br>RE8 | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                      |  |  |  |  |  |  |  |  |

| RF0-RF6         | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                      |  |  |  |  |  |  |  |  |

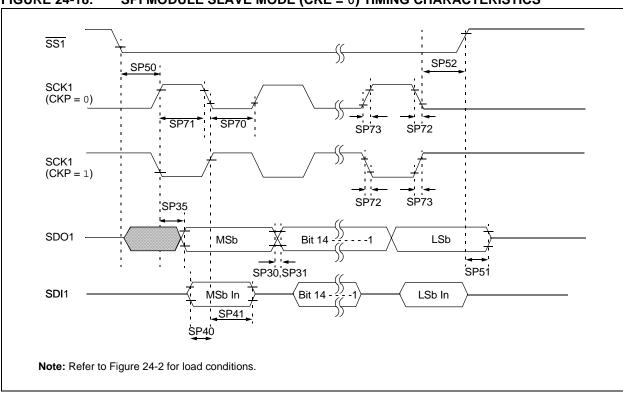

| SCK1            | I/O         | ST             | Synchronous serial clock input/output for SPI1.                                                                                         |  |  |  |  |  |  |  |  |

| SDI1            | I           | ST             | SPI1 data in.                                                                                                                           |  |  |  |  |  |  |  |  |

| SDO1            | 0           | —              | SPI1 data out.                                                                                                                          |  |  |  |  |  |  |  |  |

| SS1             | I           | ST             | SPI1 slave synchronization.                                                                                                             |  |  |  |  |  |  |  |  |

| SCL             | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C <sup>™</sup> .                                                               |  |  |  |  |  |  |  |  |

| SDA             | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                              |  |  |  |  |  |  |  |  |

| SOSCO           | 0           | —              | 32 kHz low-power oscillator crystal output.                                                                                             |  |  |  |  |  |  |  |  |

| SOSCI           | I           | ST/CMOS        | 32 kHz low-power oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                        |  |  |  |  |  |  |  |  |

| T1CK            | I           | ST             | Timer1 external clock input.                                                                                                            |  |  |  |  |  |  |  |  |

| T2CK            | I           | ST             | Timer2 external clock input.                                                                                                            |  |  |  |  |  |  |  |  |

| U1RX            | I           | ST             | UART1 receive.                                                                                                                          |  |  |  |  |  |  |  |  |

| U1TX            | 0           | —              | UART1 transmit.                                                                                                                         |  |  |  |  |  |  |  |  |

| U1ARX           |             | ST             | UART1 alternate receive.                                                                                                                |  |  |  |  |  |  |  |  |

| U1ATX           | 0           |                | UART1 alternate transmit.                                                                                                               |  |  |  |  |  |  |  |  |

| U2RX            |             | ST             | UART2 receive.                                                                                                                          |  |  |  |  |  |  |  |  |

| U2TX            | O<br>P      |                | UART2 transmit.                                                                                                                         |  |  |  |  |  |  |  |  |

| VDD             | -           |                | Positive supply for logic and I/O pins.                                                                                                 |  |  |  |  |  |  |  |  |

| Vss             | P           |                | Ground reference for logic and I/O pins.                                                                                                |  |  |  |  |  |  |  |  |

| VREF+           | <br>        | Analog         | Analog voltage reference (high) input.                                                                                                  |  |  |  |  |  |  |  |  |

| VREF-           | I           | Analog         | Analog voltage reference (low) input.                                                                                                   |  |  |  |  |  |  |  |  |

| Legend: CM      |             |                | tible input or output Analog = Analog input                                                                                             |  |  |  |  |  |  |  |  |

| ST              |             | 00             | r input with CMOS levels O = Output                                                                                                     |  |  |  |  |  |  |  |  |

| I               | = Inj       | put            | P = Power                                                                                                                               |  |  |  |  |  |  |  |  |

TABLE 1-1: dsPIC30F4011 I/O PIN DESCRIPTIONS (CONTINUED)

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

#### 3.2.5 NEAR DATA SPACE

An 8-Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

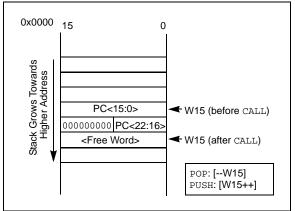

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC contains a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 3-9. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing concatenates the SRL register to the MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0', because all stack operations must be word-aligned. Whenever an Effective Address (EA) is generated, using W15 as a source or destination pointer, the address thus generated is compared with the value in the SPLIM register. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

## FIGURE 3-9: CALL STACK FRAME

## 4.1.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (register offset) field is shared between both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not   | all                                     | instructions  | support    | all   | the  |  |  |  |  |

|-------|-------|-----------------------------------------|---------------|------------|-------|------|--|--|--|--|

|       | addr  | essir                                   | ng modes give | n above. I | ndivi | dual |  |  |  |  |

|       | instr | instructions may support different subs |               |            |       |      |  |  |  |  |

|       | of th | ese a                                   | addressing mo | odes.      |       |      |  |  |  |  |

#### 4.1.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC and MSC), also referred to as MAC instructions, utilize a simplified set of addressing modes to allow the user to effectively manipulate the Data Pointers through register indirect tables.

The two source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 will always be directed to the X RAGU, and W10 and W11 will always be directed to the Y AGU. The Effective Addresses (EA) generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9, and Y data space for W10 and W11.

Note: Register Indirect with Register Offset Addressing is only available for W9 (in X data space) and W11 (in Y data space). In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.1.5 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

## 4.2 Modulo Addressing

Modulo Addressing is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either data or program space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into program space) and Y data spaces. Modulo Addressing can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing, since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers) based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers which have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a Bidirectional mode (i.e., address boundary checks will be performed on both the lower and upper address boundaries).

## 7.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

Together, the write initiate sequence and the WREN bit help prevent an accidental write during brown-out, power glitch or software malfunction.

## TABLE 10-1: TIMER2/3 REGISTER MAP<sup>(1)</sup>

| SFR Name                  | Addr. | Bit 15                                                     | Bit 14          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7        | Bit 6 | Bit 5  | Bit 4               | Bit 3               | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|---------------------------|-------|------------------------------------------------------------|-----------------|--------|--------|--------|--------|-------|-------|--------------|-------|--------|---------------------|---------------------|-------|-------|-------|---------------------|

| TMR2 0106 Timer2 Register |       |                                                            |                 |        |        |        |        |       |       |              |       |        | uuuu uuuu uuuu uuuu |                     |       |       |       |                     |

| TMR3HLD                   | 0108  | Timer3 Holding Register (For 32-bit timer operations only) |                 |        |        |        |        |       |       |              |       |        | uuuu uuuu uuuu uuuu |                     |       |       |       |                     |

| TMR3                      | 010A  |                                                            | Timer3 Register |        |        |        |        |       |       |              |       |        |                     | uuuu uuuu uuuu uuuu |       |       |       |                     |

| PR2                       | 010C  |                                                            |                 |        |        |        |        |       | Per   | riod Registe | r 2   |        |                     |                     |       |       |       | 1111 1111 1111 1111 |

| PR3                       | 010E  |                                                            |                 |        |        |        |        |       | Per   | riod Registe | r 3   | _      |                     |                     |       | -     |       | 1111 1111 1111 1111 |

| T2CON                     | 0110  | TON                                                        | —               | TSIDL  | —      | _      | —      | Ι     |       |              | TGATE | TCKPS1 | TCKPS0              | T32                 | _     | TCS   | —     | 0000 0000 0000 0000 |

| T3CON                     | 0112  | TON                                                        | _               | TSIDL  | —      | _      | _      | -     |       | _            | TGATE | TCKPS1 | TCKPS0              |                     | _     | TCS   | —     | 0000 0000 0000 0000 |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Note

1:

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## 12.1 Simple Capture Event Mode

The simple capture events in the dsPIC30F product family are:

- Capture every falling edge

- · Capture every rising edge

- Capture every 4th rising edge

- Capture every 16th rising edge

- · Capture every rising and falling edge

These simple Input Capture modes are configured by setting the appropriate bits ICM<2:0> (ICxCON<2:0>).

#### 12.1.1 CAPTURE PRESCALER

There are four input capture prescaler settings, specified by bits, ICM<2:0> (ICxCON<2:0>). Whenever the capture channel is turned off, the prescaler counter will be cleared. In addition, any Reset will clear the prescaler counter.

#### 12.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer which is four, 16-bit words deep. There are two status flags which provide status on the FIFO buffer:

- ICBNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBNE bit will be set on the first input capture event and remain set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events, and a fifth capture event occurs prior to a read of the FIFO, an overflow condition will occur and the ICOV bit will be set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events will be captured till all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

## 12.1.3 TIMER2 AND TIMER3 SELECTION MODE

Each capture channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit, ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

#### 12.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored, since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

#### 12.2 Input Capture Operation During Sleep and Idle Modes

An input capture event will generate a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module will wake-up from the CPU Sleep or Idle mode when a capture event occurs, if ICM<2:0> = 111 and the interrupt enable bit is asserted. The same wake-up can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

#### 12.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable, and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on the rising edge (ICM<2:0> = 111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

#### 12.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the interrupt mode selected by the ICI<1:0> bits are applicable, as well as the 4:1 and 16:1 capture prescale settings which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin will serve only as an external interrupt pin.

## 12.3 Input Capture Interrupts

The input capture channels have the ability to generate an interrupt, based upon the selected number of capture events. The selection number is set by control bits, ICI<1:0> (ICxCON<6:5>).

Each channel provides an interrupt flag (ICxIF) bit. The respective capture channel interrupt flag is located in the corresponding IFSx register.

Enabling an interrupt is accomplished via the respective Capture Channel Interrupt Enable (ICxIE) bit. The capture interrupt enable bit is located in the corresponding IECx register.

## TABLE 13-1: OUTPUT COMPARE REGISTER MAP<sup>(1)</sup>

| SFR Name              | Addr.                                      | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8     | Bit 7     | Bit 6      | Bit 5               | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | Reset State         |

|-----------------------|--------------------------------------------|--------|--------|--------|--------|--------|--------|-------|-----------|-----------|------------|---------------------|-------|--------|-------|----------|-------|---------------------|

| OC1RS                 | S 0180 Output Compare 1 Secondary Register |        |        |        |        |        |        |       |           |           |            | 0000 0000 0000 0000 |       |        |       |          |       |                     |

| OC1R                  | 0182                                       |        |        |        |        |        |        | O     | utput Com | pare 1 Ma | in Registe | r                   |       |        |       |          |       | 0000 0000 0000 0000 |

| OC1CON                | 0184                                       | —      | _      | OCSIDL | —      | _      | _      | _     | -         | _         | _          | _                   | OCFLT | OCTSEL |       | OCM<2:0: | >     | 0000 0000 0000 0000 |

| OC2RS                 | 0186                                       |        |        |        |        |        |        | Outp  | ut Compar | e 2 Secon | dary Regi  | ster                |       |        |       |          |       | 0000 0000 0000 0000 |

| OC2R                  | 0188                                       |        |        |        |        |        |        | O     | utput Com | pare 2 Ma | in Registe | r                   |       |        |       |          |       | 0000 0000 0000 0000 |

| OC2CON                | 018A                                       | —      | _      | OCSIDL | —      | _      | _      | _     | -         | _         | _          | _                   | OCFLT | OCTSE  |       | OCM<2:0; | >     | 0000 0000 0000 0000 |

| OC3RS <sup>(2)</sup>  | 018C                                       |        |        |        |        |        |        | Outp  | ut Compar | e 3 Secon | dary Regi  | ster                |       |        |       |          |       | 0000 0000 0000 0000 |

| OC3R <sup>(2)</sup>   | 018E                                       |        |        |        |        |        |        | O     | utput Com | pare 3 Ma | in Registe | r                   |       |        |       |          |       | 0000 0000 0000 0000 |

| OC3CON <sup>(2)</sup> | 0190                                       | —      | _      | OCSIDL | —      | _      | _      | _     | -         | _         | _          | _                   | OCFLT | OCTSEL |       | OCM<2:0: | >     | 0000 0000 0000 0000 |

| OC4RS <sup>(2)</sup>  | 0192                                       |        |        |        |        |        |        | Outp  | ut Compar | e 4 Secon | dary Regi  | ster                |       |        |       |          |       | 0000 0000 0000 0000 |

| OC4R <sup>(2)</sup>   | 0194                                       |        |        |        |        |        |        | O     | utput Com | pare 4 Ma | in Registe | r                   |       |        |       |          |       | 0000 0000 0000 0000 |

| OC4CON <sup>(2)</sup> | 0196                                       | —      | _      | OCSIDL | _      |        | _      |       | _         | _         | _          | _                   | OCFLT | OCTSEL |       | OCM<2:0: | >     | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

2: These registers are not available on dsPIC30F4012 devices.

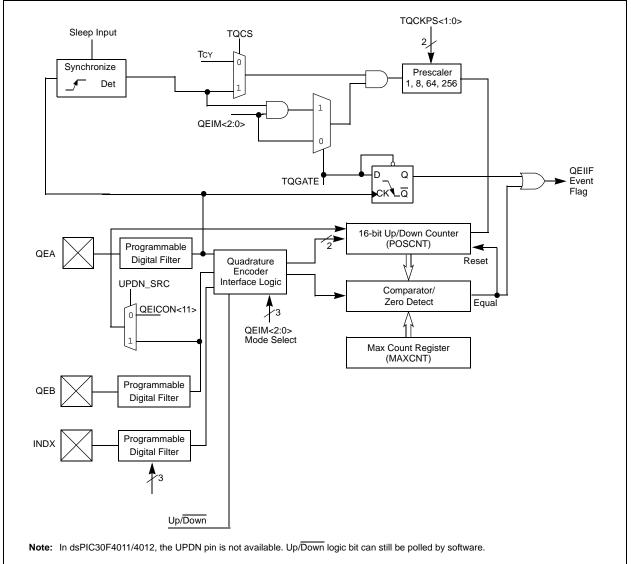

## 14.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

This section describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data. The operational features of the QEI include:

- Three input channels for two phase signals and index pulse

- 16-bit up/down position counter

- Count direction status

- Position Measurement (x2 and x4) mode

- Programmable digital noise filters on inputs

- Alternate 16-bit Timer/Counter mode

- Quadrature Encoder Interface interrupts

These operating modes are determined by setting the appropriate bits QEIM<2:0> (QEICON<10:8>). Figure 14-1 depicts the Quadrature Encoder Interface block diagram.

## FIGURE 14-1: QUADRATURE ENCODER INTERFACE BLOCK DIAGRAM

#### 14.3 Position Measurement Mode

There are two Measurement modes which are supported and are termed x2 and x4. These modes are selected by the QEIM<2:0> (QEICON<10:8>) mode select bits.

When control bits, QEIM<2:0> = 100 or 101, the x2 Measurement mode is selected and the QEI logic only looks at the Phase A input for the position counter increment rate. Every rising and falling edge of the Phase A signal causes the position counter to be incremented or decremented. The Phase B signal is still utilized for the determination of the counter direction just as in the x4 mode.

Within the x2 Measurement mode, there are two variations of how the position counter is reset:

- 1. Position counter reset by detection of index pulse, QEIM<2:0> = 100.

- Position counter reset by match with MAXCNT, QEIM<2:0> = 101.

When control bits, QEIM<2:0> = 110 or 111, the x4 Measurement mode is selected and the QEI logic looks at both edges of the Phase A and Phase B input signals. Every edge of both signals causes the position counter to increment or decrement.

Within the x4 Measurement mode, there are two variations of how the position counter is reset:

- 1. Position counter reset by detection of index pulse, QEIM<2:0> = 110.

- Position counter reset by match with MAXCNT, QEIM<2:0> = 111.

The x4 Measurement mode provides for finer resolution data (more position counts) for determining motor position.

#### 14.4 Programmable Digital Noise Filters

The digital noise filter section is responsible for rejecting noise on the incoming quadrature signals. Schmitt Trigger inputs and a three-clock cycle delay filter combine to reject low-level noise and large, short duration, noise spikes that typically occur in noise prone applications, such as a motor system.

The filter ensures that the filtered output signal is not permitted to change until a stable value has been registered for three consecutive clock cycles.

For the QEA, QEB and INDX pins, the clock divide frequency for the digital filter is programmed by bits QECK<2:0> (DFLTCON<6:4>) and are derived from the base instruction cycle TcY.

To enable the filter output for channels QEA, QEB and INDX, the QEOUT bit must be '1'. The filter network for all channels is disabled on POR and BOR.

### 14.5 Alternate 16-bit Timer/Counter

When the QEI module is not configured for the QEI mode, QEIM<2:0> = 001, the module can be configured as a simple 16-bit timer/counter. The setup and control of the auxiliary timer is accomplished through the QEICON SFR register. This timer functions identically to Timer1. The QEA pin is used as the timer clock input.

When configured as a timer, the POSCNT register serves as the Timer Count register and the MAXCNT register serves as the Period register. When a Timer/ Period register match occurs, the QEI interrupt flag will be asserted.

The only exception between the general purpose timers and this timer is the added feature of external up/ down input select. When the UPDN pin is asserted high, the timer will increment up. When the UPDN pin is asserted low, the timer will be decremented.

| Note: | Changing the operational mode (i.e., from       |

|-------|-------------------------------------------------|

|       | QEI to timer or vice versa) will not affect the |

|       | Timer/Position Count register contents.         |

The UPDN control/status bit (QEICON<11>) can be used to select the count direction state of the Timer register. When UPDN = 1, the timer will count up. When UPDN = 0, the timer will count down.

In addition, control bit, UPDN\_SRC (QEICON<0>), determines whether the timer count direction state is based on the logic state written into the UPDN control/ status bit (QEICON<11>) or the QEB pin state. When UPDN\_SRC = 1, the timer count direction is controlled from the QEB pin. Likewise, when UPDN\_SRC = 0, the timer count direction is controlled by the UPDN bit.

**Note:** This timer does not support the External Asynchronous Counter mode of operation. If using an external clock source, the clock will automatically be synchronized to the internal instruction cycle.

#### 14.6 QEI Module Operation During CPU Sleep Mode

#### 14.6.1 QEI OPERATION DURING CPU SLEEP MODE

The QEI module will be halted during the CPU Sleep mode.

#### 14.6.2 TIMER OPERATION DURING CPU SLEEP MODE

During CPU Sleep mode, the timer will not operate because the internal clocks are disabled.

## 15.0 MOTOR CONTROL PWM MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

This module simplifies the task of generating multiple, synchronized Pulse-Width Modulated (PWM) outputs. In particular, the following power and motion control applications are supported by the PWM module:

- Three-Phase AC Induction Motor

- Switched Reluctance (SR) Motor

- Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

The PWM module has the following features:

- 6 PWM I/O pins with 3 duty cycle generators

- Up to 16-bit resolution

- 'On-the-Fly' PWM frequency changes

- Edge and Center-Aligned Output modes

- Single Pulse Generation mode

- Interrupt support for asymmetrical updates in Center-Aligned mode

- Output override control for Electrically Commutative Motor (ECM) operation

- 'Special Event' comparator for scheduling other peripheral events

- Fault pins to optionally drive each of the PWM output pins to a defined state

This module contains 3 duty cycle generators, numbered 1 through 3. The module has 6 PWM output pins, numbered PWM1H/PWM1L through PWM3H/PWM3L. The six I/O pins are grouped into high/low numbered pairs, denoted by the suffix H or L, respectively. For complementary loads, the low PWM pins are always the complement of the corresponding high I/O pin.

The PWM module allows several modes of operation which are beneficial for specific power control applications.

## 15.13 PWM Update Lockout

For a complex PWM application, the user may need to write up to three duty cycle registers and the Time Base Period register, PTPER, at a given time. In some applications, it is important that all buffer registers be written before the new duty cycle and period values are loaded for use by the module.

The PWM update lockout feature is enabled by setting the UDIS control bit in the PWMCON2 SFR. The UDIS bit affects all duty cycle buffer registers and the PWM Time Base Period buffer, PTPER. No duty cycle changes or period value changes will have effect while UDIS = 1.

## 15.14 PWM Special Event Trigger

The PWM module has a special event trigger that allows A/D conversions to be synchronized to the PWM time base. The A/D sampling and conversion time may be programmed to occur at any point within the PWM period. The special event trigger allows the user to minimize the delay between the time when A/D conversion results are acquired and the time when the duty cycle value is updated.

The PWM special event trigger has an SFR named SEVTCMP and five control bits to control its operation. The PTMR value for which a special event trigger should occur is loaded into the SEVTCMP register. When the PWM time base is in a Continuous Up/Down Count mode, an additional control bit is required to specify the counting phase for the special event trigger. The count phase is selected using the SEVTDIR control bit in the SEVTCMP SFR. If the SEVTDIR bit is cleared, the special event trigger will occur on the upward counting cycle of the PWM time base. If the SEVTDIR bit is set, the special event trigger will occur on the downward count cycle of the PWM time base. The SEVTDIR control bit has no effect unless the PWM time base is configured for a Continuous Up/Down Count mode.

#### 15.14.1 SPECIAL EVENT TRIGGER POSTSCALER

The PWM special event trigger has a postscaler that allows a 1:1 to 1:16 postscale ratio. The postscaler is configured by writing the SEVOPS<3:0> control bits in the PWMCON2 SFR.

The special event output postscaler is cleared on the following events:

- Any write to the SEVTCMP register

- · Any device Reset

#### 15.15 PWM Operation During CPU Sleep Mode

The Fault A input pin has the ability to wake the CPU from Sleep mode. The PWM module generates an interrupt if the Fault pin is driven low while in Sleep.

## 15.16 PWM Operation During CPU Idle Mode

The PTCON SFR contains a PTSIDL control bit. This bit determines if the PWM module will continue to operate or stop when the device enters Idle mode. If PTSIDL = 0, the module will continue to operate. If PTSIDL = 1, the module will stop operation as long as the CPU remains in Idle mode.

#### 17.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion, with the full 10-bit address (we will refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation.

17.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

## 17.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

## 17.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed, irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an ACK on the falling edge of the ninth clock, and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- 2: The SCLREL bit can be set in software regardless of the state of the TBF bit.

## 17.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

#### 17.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7-bit and 10-bit Addressing modes. Clock stretching takes place following the ninth clock of the receive sequence. On the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I2CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- 2: The SCLREL bit can be set in software, regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

## 17.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

## 17.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set and all other devices on the I<sup>2</sup>C bus have deasserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

## TABLE 17-2: I<sup>2</sup>C<sup>™</sup> REGISTER MAP<sup>(1)</sup>

| SFR Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                        | Bit 8                 | Bit 7 | Bit 6 | Bit 5  | Bit 4      | Bit 3 | Bit 2               | Bit 1               | Bit 0 | Reset State         |

|----------|-------|---------|--------|---------|--------|--------|--------|------------------------------|-----------------------|-------|-------|--------|------------|-------|---------------------|---------------------|-------|---------------------|

| I2CRCV   | 0200  | _       | _      |         | _      | _      |        | _                            | Receive Register      |       |       |        |            |       |                     |                     |       | 0000 0000 0000 0000 |

| I2CTRN   | 0202  |         |        | _       | _      | _      | —      | _                            | — — Transmit Register |       |       |        |            |       |                     | 0000 0000 1111 1111 |       |                     |

| I2CBRG   | 0204  |         |        | _       | _      | _      | —      | _                            |                       |       |       | Baud F | Rate Gener | rator | _                   |                     |       | 0000 0000 0000 0000 |

| I2CCON   | 0206  | I2CEN   |        | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                       | SMEN                  | GCEN  | STREN | ACKDT  | ACKEN      | RCEN  | PEN                 | RSEN                | SEN   | 0001 0000 0000 0000 |

| I2CSTAT  | 0208  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                       | ADD10                 | IWCOL | I2COV | D_A    | Р          | S     | R_W                 | RBF                 | TBF   | 0000 0000 0000 0000 |

| I2CADD   | 020A  | —       | _      |         | _      | _      | —      | Address Register 0000 0000 0 |                       |       |       |        |            |       | 0000 0000 0000 0000 |                     |       |                     |

Legend:

--= unimplemented bit, read as '0'

Note

1:

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

# dsPIC30F4011/4012

NOTES:

## 19.4 Message Reception

#### 19.4.1 RECEIVE BUFFERS

The CAN bus module has 3 receive buffers. However, one of the receive buffers is always committed to monitoring the bus for incoming messages. This buffer is called the message assembly buffer (MAB). There are two receive buffers, visibly denoted as RXB0 and RXB1, that can essentially instantaneously receive a complete message from the protocol engine.

All messages are assembled by the MAB, and are transferred to the RXBn buffers only if the acceptance filter criterion is met. When a message is received, the RXxIF flag (C1INTF<0> or C1INIF<1>) will be set. This bit can only be set by the module when a message is received. The bit is cleared by the CPU when it has completed processing the message in the buffer. If the RXxIE bit (C1INTE<0> or C1INTE<1>) is set, an interrupt will be generated when a message is received.

RXF0 and RXF1 filters with the RXM0 mask are associated with RXB0. The filters, RXF2, RXF3, RXF4 and RXF5, and the mask, RXM1, are associated with RXB1.

## 19.4.2 MESSAGE ACCEPTANCE FILTERS

The message acceptance filters and masks are used to determine if a message in the message assembly buffer should be loaded into either of the receive buffers. Once a valid message has been received into the Message Assembly Buffer (MAB), the identifier fields of the message are compared to the filter values. If there is a match, that message will be loaded into the appropriate receive buffer.

The acceptance filter looks at incoming messages for the RXIDE bit (CiRXnSID<0>) to determine how to compare the identifiers. If the RXIDE bit is clear, the message is a standard frame and only filters with the EXIDE bit (C1RXFxSID<0>) clear are compared. If the RXIDE bit is set, the message is an extended frame and only filters with the EXIDE bit set are compared.

#### 19.4.3 MESSAGE ACCEPTANCE FILTER MASKS

The mask bits essentially determine which bits to apply the filter to. If any mask bit is set to a zero, then that bit will automatically be accepted regardless of the filter bit. There are 2 programmable acceptance filter masks associated with the receive buffers, one for each buffer.

#### 19.4.4 RECEIVE OVERRUN

An overrun condition occurs when the Message Assembly Buffer (MAB) has assembled a valid received message, the message is accepted through the acceptance filters, and when the receive buffer associated with the filter has not been designated as clear of the previous message.

The overrun error flag, RXxOVR (C1INTF<15> or C1INTF<14>) and the ERRIF bit (C1INTF<5>) will be set and the message in the MAB will be discarded.

If the DBEN bit is clear, RXB1 and RXB0 operate independently. When this is the case, a message intended for RXB0 will not be diverted into RXB1 if RXB0 contains an unread message and the RX00VR bit will be set.

If the DBEN bit is set, the overrun for RXB0 is handled differently. If a valid message is received for RXB0 and RXFUL = 1, it indicates that RXB0 is full and RXFUL = 0 indicates that RXB1 is empty, the message for RXB0 will be loaded into RXB1. An overrun error will not be generated for RXB0. If a valid message is received for RXB0 and RXFUL = 1, and RXFUL = 1 indicates that both RXB0 and RXB1 are full, the message will be lost and an overrun will be indicated for RXB1.

#### 19.4.5 RECEIVE ERRORS

The CAN module will detect the following receive errors:

- Cyclic Redundancy Check (CRC) Error

- Bit Stuffing Error

- Invalid Message Receive Error

The receive error counter is incremented by one in case one of these errors occur. The RXWAR bit (C1INTF<9>) indicates that the receive error counter has reached the CPU warning limit of 96 and an interrupt is generated.

#### 19.4.6 RECEIVE INTERRUPTS

Receive interrupts can be divided into 3 major groups, each including various conditions that generate interrupts:

#### 19.4.6.1 Receive Interrupt

A message has been successfully received and loaded into one of the receive buffers. This interrupt is activated immediately after receiving the End-of-Frame (EOF) field. Reading the RXxIF flag will indicate which receive buffer caused the interrupt.

#### 19.4.6.2 Wake-up Interrupt

The CAN module has woken up from Disable mode or the device has woken up from Sleep mode.

| DC CHARACT                             | ERISTICS                 |     |                  | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise state         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |       |                |  |  |  |  |  |  |

|----------------------------------------|--------------------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|--|--|--|--|--|--|

| Parameter<br>No.                       | Typical <sup>(1,2)</sup> | Max | Units Conditions |                                                                                                                                                                                |       |                |  |  |  |  |  |  |

| Operating Current (IDD) <sup>(3)</sup> |                          |     |                  |                                                                                                                                                                                |       |                |  |  |  |  |  |  |

| DC51a                                  | 1.3                      | 3   | mA               | +25°C                                                                                                                                                                          |       |                |  |  |  |  |  |  |

| DC51b                                  | 1.3                      | 3   | mA               | +85°C                                                                                                                                                                          | 3.3V  |                |  |  |  |  |  |  |

| DC51c                                  | 1.3                      | 3   | mA               | +125°C                                                                                                                                                                         |       | 0.128 MIPS     |  |  |  |  |  |  |

| DC51e                                  | 2.7                      | 5   | mA               | +25°C                                                                                                                                                                          |       | LPRC (512 kHz) |  |  |  |  |  |  |

| DC51f                                  | 2.7                      | 5   | mA               | +85°C                                                                                                                                                                          | 5V    |                |  |  |  |  |  |  |

| DC51g                                  | 2.7                      | 5   | mA               | +125°C                                                                                                                                                                         |       |                |  |  |  |  |  |  |

| DC50a                                  | 4                        | 6   | mA               | +25°C                                                                                                                                                                          |       |                |  |  |  |  |  |  |

| DC50b                                  | 4                        | 6   | mA               | +85°C                                                                                                                                                                          | 3.3V  |                |  |  |  |  |  |  |

| DC50c                                  | 4                        | 6   | mA               | +125°C                                                                                                                                                                         |       | (1.8 MIPS)     |  |  |  |  |  |  |

| DC50e                                  | 7                        | 11  | mA               | +25°C                                                                                                                                                                          |       | FRC (7.37 MHz) |  |  |  |  |  |  |

| DC50f                                  | 7                        | 11  | mA               | +85°C                                                                                                                                                                          | 5V    |                |  |  |  |  |  |  |

| DC50g                                  | 7                        | 11  | mA               | +125°C                                                                                                                                                                         |       |                |  |  |  |  |  |  |

| DC43a                                  | 7                        | 11  | mA               | +25°C                                                                                                                                                                          |       |                |  |  |  |  |  |  |

| DC43b                                  | 7                        | 11  | mA               | +85°C                                                                                                                                                                          | 3.3V  |                |  |  |  |  |  |  |

| DC43c                                  | 7                        | 11  | mA               | +125°C                                                                                                                                                                         |       |                |  |  |  |  |  |  |

| DC43e                                  | 12                       | 17  | mA               | +25°C                                                                                                                                                                          |       | 4 MIPS         |  |  |  |  |  |  |

| DC43f                                  | 12                       | 17  | mA               | +85°C                                                                                                                                                                          | 5V    |                |  |  |  |  |  |  |

| DC43g                                  | 12                       | 17  | mA               | +125°C                                                                                                                                                                         |       |                |  |  |  |  |  |  |

| DC44a                                  | 15                       | 22  | mA               | +25°C                                                                                                                                                                          |       |                |  |  |  |  |  |  |

| DC44b                                  | 15                       | 22  | mA               | +85°C                                                                                                                                                                          | 3.3V  |                |  |  |  |  |  |  |

| DC44c                                  | 16                       | 22  | mA               | +125°C                                                                                                                                                                         |       |                |  |  |  |  |  |  |

| DC44e                                  | 26                       | 36  | mA               | +25°C                                                                                                                                                                          |       | 10 MIPS        |  |  |  |  |  |  |

| DC44f                                  | 27                       | 36  | mA               | +85°C                                                                                                                                                                          | 5V    |                |  |  |  |  |  |  |

| DC44g                                  | 27                       | 36  | mA               | +125°C                                                                                                                                                                         |       |                |  |  |  |  |  |  |

| DC47a                                  | 30                       | 40  | mA               | +25°C                                                                                                                                                                          | 2.2)/ |                |  |  |  |  |  |  |

| DC47b                                  | 30                       | 40  | mA               | +85°C                                                                                                                                                                          | 3.3V  |                |  |  |  |  |  |  |

| DC47d                                  | 50                       | 65  | mA               | +25°C                                                                                                                                                                          |       | 20 MIPS        |  |  |  |  |  |  |

| DC47e                                  | 50                       | 65  | mA               | +85°C                                                                                                                                                                          | 5∨    |                |  |  |  |  |  |  |

| DC47f                                  | 51                       | 65  | mA               | +125°C                                                                                                                                                                         | ]     |                |  |  |  |  |  |  |

| DC49a                                  | 72                       | 95  | mA               | +25°C                                                                                                                                                                          | E) (  |                |  |  |  |  |  |  |

| DC49b                                  | 73                       | 95  | mA               | +85°C                                                                                                                                                                          | 5V    | 30 MIPS        |  |  |  |  |  |  |

Note 1: Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IIDLE current is measured with core off, clock on and all modules turned off.

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com