#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4011-30i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name        | Pin<br>Type | Buffer<br>Type | Description                                                                                                                              |  |  |  |  |  |  |  |

|-----------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| OSC1            | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                          |  |  |  |  |  |  |  |

| OSC2            | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |  |  |  |  |  |  |  |

| PGD             | I/O         | ST             | In-Circuit Serial Programming™ data input/output pin.                                                                                    |  |  |  |  |  |  |  |

| PGC             | I           | ST             | In-Circuit Serial Programming clock input pin.                                                                                           |  |  |  |  |  |  |  |

| RB0-RB8         | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |  |

| RC13-RC15       | I/O         | ST             | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |  |

| RD0-RD3         | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |  |

| RE0-RE5,<br>RE8 | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |  |

| RF0-RF6         | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                       |  |  |  |  |  |  |  |

| SCK1            | I/O         | ST             | Synchronous serial clock input/output for SPI1.                                                                                          |  |  |  |  |  |  |  |

| SDI1            | I           | ST             | SPI1 data in.                                                                                                                            |  |  |  |  |  |  |  |

| SDO1            | 0           | —              | SPI1 data out.                                                                                                                           |  |  |  |  |  |  |  |

| SS1             | I           | ST             | SPI1 slave synchronization.                                                                                                              |  |  |  |  |  |  |  |

| SCL             | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C™.                                                                             |  |  |  |  |  |  |  |

| SDA             | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                               |  |  |  |  |  |  |  |

| SOSCO           | 0           | —              | 32 kHz low-power oscillator crystal output.                                                                                              |  |  |  |  |  |  |  |

| SOSCI           | I           | ST/CMOS        | 32 kHz low-power oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                         |  |  |  |  |  |  |  |

| T1CK            | I           | ST             | Timer1 external clock input.                                                                                                             |  |  |  |  |  |  |  |

| T2CK            | I           | ST             | Timer2 external clock input.                                                                                                             |  |  |  |  |  |  |  |

| U1RX            | I           | ST             | UART1 receive.                                                                                                                           |  |  |  |  |  |  |  |

| U1TX            | 0           | —              | UART1 transmit.                                                                                                                          |  |  |  |  |  |  |  |

| U1ARX           |             | ST             | UART1 alternate receive.                                                                                                                 |  |  |  |  |  |  |  |

| U1ATX           | 0           | —<br>CT        | UART1 alternate transmit.                                                                                                                |  |  |  |  |  |  |  |

| U2RX<br>U2TX    | <br>  0     | ST             | UART2 receive.<br>UART2 transmit.                                                                                                        |  |  |  |  |  |  |  |

| VDD             | P           |                | Positive supply for logic and I/O pins.                                                                                                  |  |  |  |  |  |  |  |

| Vss             | P           |                |                                                                                                                                          |  |  |  |  |  |  |  |

| VSS<br>VREF+    |             | Analaa         | Ground reference for logic and I/O pins.                                                                                                 |  |  |  |  |  |  |  |

| VREF+<br>VREF-  | <br>        | Analog         | Analog voltage reference (high) input.                                                                                                   |  |  |  |  |  |  |  |

|                 |             | Analog         | Analog voltage reference (low) input.                                                                                                    |  |  |  |  |  |  |  |

| Legend: CM      |             |                | ible input or output Analog = Analog input                                                                                               |  |  |  |  |  |  |  |

| ST              |             | 00             | r input with CMOS levels O = Output                                                                                                      |  |  |  |  |  |  |  |

| I               | = Inj       | put            | P = Power                                                                                                                                |  |  |  |  |  |  |  |

TABLE 1-1: dsPIC30F4011 I/O PIN DESCRIPTIONS (CONTINUED)

# 2.3 Divide Support

The dsPIC DSCs feature a 16/16-bit signed fractional divide operation, as well as 32/16-bit and 16/16-bit signed and unsigned integer divide operations, in the form of single instruction iterative divides. The following instructions and data sizes are supported:

- 1. DIVF 16/16 signed fractional divide

- 2. DIV.sd 32/16 signed divide

- 3. DIV.ud 32/16 unsigned divide

- 4. DIV.s 16/16 signed divide

- 5. DIV.u 16/16 unsigned divide

The divide instructions must be executed within a REPEAT loop. Any other form of execution (e.g. a series of discrete divide instructions) will not function correctly because the instruction flow depends on RCOUNT. The divide instruction does not automatically set up the RCOUNT value and it must, therefore, be explicitly and correctly specified in the REPEAT instruction, as shown in Table 2-1 (REPEAT executes the target instruction {operand value + 1} times). The REPEAT loop count must be set up for 18 iterations of the DIV/DIVF instruction. Thus, a complete divide operation requires 19 cycles.

**Note:** The divide flow is interruptible. However, the user needs to save the context as appropriate.

| Instruction | Function                                                               |  |  |  |  |  |

|-------------|------------------------------------------------------------------------|--|--|--|--|--|

| DIVF        | Signed fractional divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |  |  |  |  |  |

| DIV.sd      | Signed divide: (Wm + 1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1   |  |  |  |  |  |

| DIV.s       | Signed divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1            |  |  |  |  |  |

| DIV.ud      | Unsigned divide: (Wm + 1:Wm)/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1 |  |  |  |  |  |

| DIV.u       | Unsigned divide: Wm/Wn $\rightarrow$ W0; Rem $\rightarrow$ W1          |  |  |  |  |  |

#### TABLE 2-1: DIVIDE INSTRUCTIONS

### 2.4 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/ subtracter (with two target accumulators, round and saturation logic).

The dsPIC30F devices have a single instruction flow which can execute either DSP or MCU instructions. Many of the hardware resources are shared between the DSP and MCU instructions. For example, the instruction set has both DSP and MCU multiply instructions which use the same hardware multiplier.

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DS0 engine has various options selected through various bits in the CPU Core Configuration register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF).

- 2. Signed or unsigned DSP multiply (US).

- 3. Conventional or convergent rounding (RND).

- 4. Automatic saturation on/off for ACCA (SATA).

- 5. Automatic saturation on/off for ACCB (SATB).

- 6. Automatic saturation on/off for writes to data memory (SATDW).

- 7. Accumulator Saturation mode selection (ACCSAT).

Note: For CORCON layout, see Table 3-3.

A block diagram of the DSP engine is shown in Figure 2-2.

TABLE 2-2: DSP INSTRUCTION SUMMARY

| Instruction | Algebraic Operation |

|-------------|---------------------|

| CLR         | A = 0               |

| ED          | $A = (x - y)^2$     |

| EDAC        | $A = A + (x - y)^2$ |

| MAC         | A = A + (x * y)     |

| MOVSAC      | No change in A      |

| MPY         | A = x * y           |

| MPY.N       | A = - x * y         |

| MSC         | A = A - x * y       |

### 2.4.1 MULTIPLIER

The 17x17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17x17-bit multiplier/ scaler is a 33-bit value, which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the MSB is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ . For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,645 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSB is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to  $(1-2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF), including 0, and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, a 16x16 multiply operation generates a 1.31 product, which has a precision of 4.65661x10<sup>-10</sup>.

The same multiplier is used to support the DSC multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word-sized operands. Byte operands direct a 16-bit result, and word operands direct a 32-bit result to the specified register(s) in the W array.

# 2.4.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter, prior to accumulation.

# 2.4.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input. In the case of addition, the carry/borrow input is active-high and the other input is true data (not complemented), whereas in the case of subtraction, the carry/borrow input is active-low and the other input is complemented. The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register.

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described above, and the SATA/B (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits have been provided to support saturation and overflow; they are:

- 1. OA: ACCA overflowed into guard bits.

- 2. OB: ACCB overflowed into guard bits.

- 3. SA: ACCA saturated (bit 31 overflow and saturation). *or*

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation).

SB: ACCB saturated (bit 31 overflow and saturation).

or ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation).

5. OAB: Logical OR of OA and OB.

4

6. SAB: Logical OR of SA and SB.

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). Also, the OA and OB bits can optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bit (OVATE, OVBTE) in the INTCON1 register (refer to **Section 5.0 "Interrupts"**) is set. This allows the user to take immediate action, for example, to correct system gain.

#### 4.2.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a start and end address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 3-3).

| Note: | Y space Modulo Addressing EA calcula- |  |  |  |  |  |  |

|-------|---------------------------------------|--|--|--|--|--|--|

|       | tions assume word-sized data (LSb of  |  |  |  |  |  |  |

|       | every EA is always clear).            |  |  |  |  |  |  |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

### 4.2.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing are disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 3-3). Modulo Addressing is enabled for X data space when XWM is set to any value other than 15 and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than 15 and the YMODEN bit is set at MODCON<14>.

| JNE <del>4</del> -1. |                                                           |                                          |                                                                                        |                                                                                                                                                                         |

|----------------------|-----------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte<br>Address      |                                                           | MOV<br>MOV<br>MOV<br>MOV                 | #0x1100,W0<br>W0, XMODSRT<br>#0x1163,W0<br>W0,MODEND                                   | ;set modulo start address<br>;set modulo end address                                                                                                                    |

| 0x1100               |                                                           | MOV<br>MOV<br>MOV<br>DO<br>MOV<br>AGAIN: | <pre>#0x8001,W0 W0,MODCON #0x0000,W0 #0x1110,W1 AGAIN,#0x31 W0, [W1++] INC W0,W0</pre> | <pre>;enable W1, X AGU for modulo ;W0 holds buffer fill value ;point W1 to buffer ;fill the 50 buffer locations ;fill the next location ;increment the fill value</pre> |

| End                  | rt Addr = 0x1100<br>d Addr = 0x1163<br>gth = 0x0032 words |                                          |                                                                                        |                                                                                                                                                                         |

#### FIGURE 4-1: MODULO ADDRESSING OPERATION EXAMPLE

NOTES:

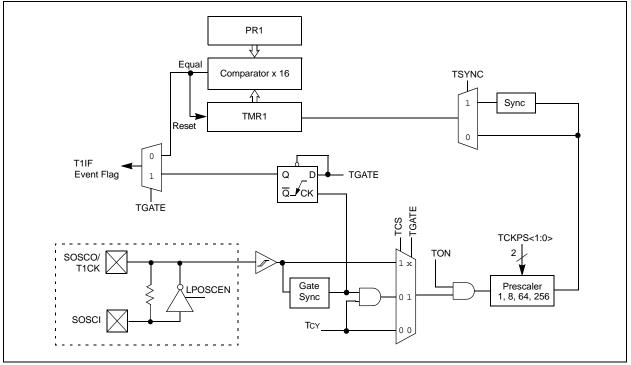

#### FIGURE 9-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM (TYPE A TIMER)

# 9.1 Timer Gate Operation

The 16-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T1CK pin) is asserted high. Control bit, TGATE (T1CON<6>), must be set to enable this mode. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

When the CPU goes into the Idle mode, the timer will stop incrementing unless TSIDL = 0. If TSIDL = 1, the timer will resume the incrementing sequence upon termination of the CPU Idle mode.

# 9.2 Timer Prescaler

The input clock (FOSC/4 or external clock) to the 16-bit Timer has a prescale option of 1:1, 1:8, 1:64 and 1:256 selected by control bits, TCKPS<1:0> (T1CON<5:4>). The prescaler counter is cleared when any of the following occurs:

- · A write to the TMR1 register

- Clearing of the TON bit (T1CON<15>)

- A device Reset, such as a POR and BOR

However, if the timer is disabled (TON = 0), then the timer prescaler cannot be reset since the prescaler clock is halted.

The TMR1 register is not cleared when the T1CON register is written. It is cleared by writing to the TMR1 register.

### 9.3 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will operate if:

- The timer module is enabled (TON = 1) and

- The timer clock source is selected as external (TCS = 1) and

- The TSYNC bit (T1CON<2>) is asserted to a logic '0', which defines the external clock source as asynchronous

When all three conditions are true, the timer will continue to count up to the Period register and be reset to 0x0000.

When a match between the timer and the Period register occurs, an interrupt can be generated if the respective timer interrupt enable bit is asserted.

# 10.1 Timer Gate Operation

The 32-bit timer can be placed in the Gated Time Accumulation mode. This mode allows the internal TCY to increment the respective timer when the gate input signal (T2CK pin) is asserted high. Control bit, TGATE (T2CON<6>), must be set to enable this mode. When in this mode, Timer2 is the originating clock source. The TGATE setting is ignored for Timer3. The timer must be enabled (TON = 1) and the timer clock source set to internal (TCS = 0).

The falling edge of the external signal terminates the count operation but does not reset the timer. The user must reset the timer in order to start counting from zero.

# 10.2 ADC Event Trigger

When a match occurs between the 32-bit timer (TMR3/ TMR2) and the 32-bit combined Period register (PR3/ PR2), a special ADC trigger event signal is generated by Timer3.

# 10.3 Timer Prescaler

The input clock (FOSC/4 or external clock) to the timer has a prescale option of 1:1, 1:8, 1:64 and 1:256, selected by control bits, TCKPS<1:0> (T2CON<5:4> and T3CON<5:4>). For the 32-bit timer operation, the originating clock source is Timer2. The prescaler operation for Timer3 is not applicable in this mode. The prescaler counter is cleared when any of the following occurs:

- A write to the TMR2/TMR3 register

- Clearing either of the TON bits (T2CON<15> or T3CON<15>) to '0'

- A device Reset, such as a POR and BOR

However, if the timer is disabled (TON = 0), then the Timer 2 prescaler cannot be reset, since the prescaler clock is halted.

The TMR2/TMR3 register is not cleared when the T2CON/T3CON register is written.

# 10.4 Timer Operation During Sleep Mode

During CPU Sleep mode, the timer will not operate because the internal clocks are disabled.

# 10.5 Timer Interrupt

The 32-bit timer module can generate an interrupt on period match, or on the falling edge of the external gate signal. When the 32-bit timer count matches the respective 32-bit Period register, or the falling edge of the external "gate" signal is detected, the T3IF bit (IFS0<7>) is asserted and an interrupt will be generated, if enabled. In this mode, the T3IF interrupt flag is used as the source of the interrupt. The T3IF bit must be cleared in software.

Enabling an interrupt is accomplished via the respective Timer Interrupt Enable bit, T3IE (IEC0<7>).

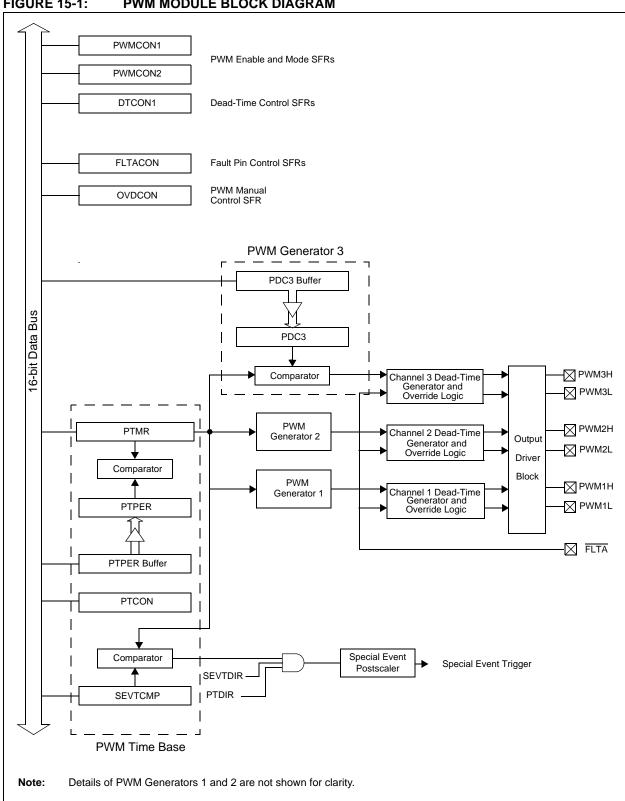

#### **FIGURE 15-1: PWM MODULE BLOCK DIAGRAM**

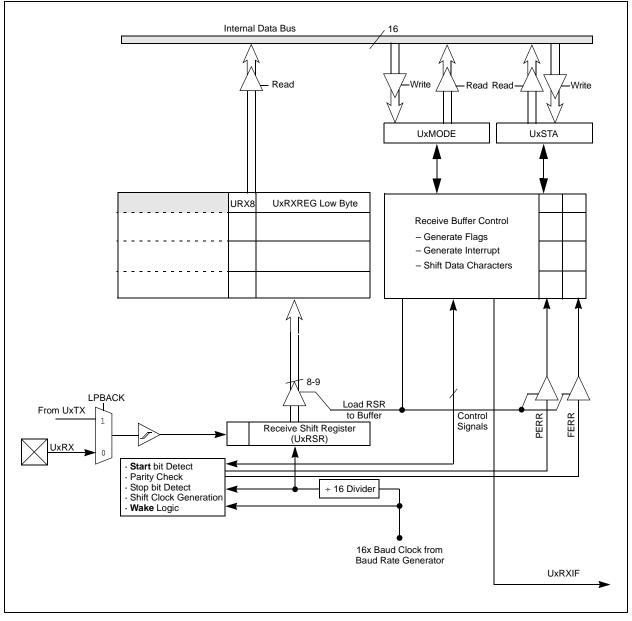

### FIGURE 18-2: UART RECEIVER BLOCK DIAGRAM

#### 18.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1', otherwise FERR will be set. The read-only FERR bit is buffered along with the received data; it is cleared on any Reset.

#### 18.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes; it is cleared on any Reset.

#### 18.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

#### 18.5.5 RECEIVE BREAK

The receiver will count and expect a certain number of bit times based on the values programmed in the PDSEL<1:0> (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the Break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated, if appropriate and the RIDLE bit is set.

When the module receives a long Break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the Break condition on the line is the next Start bit.

Break is regarded as a character containing all '0's, with the FERR bit set. The Break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not been received yet.

#### 18.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables this special mode in which a 9th bit (URX8) value of '1' identifies the received word as an address, rather than data. This mode is only applicable for 9-bit data communication. The URXISELx control bit does not have any impact on interrupt generation in this mode, since an interrupt (if enabled) will be generated every time the received word has the 9th bit set.

### 18.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in **Section 18.3** "**Transmitting Data**".

### 18.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

- BRG = 16-bit value held in UxBRG register (0 through 65535)

- FCY = Instruction Clock Rate (1/TCY)

The baud rate is given by Equation 18-1.

# EQUATION 18-1: BAUD RATE

Baud Rate = FCY/(16 \* (BRG + 1))

Therefore, maximum baud rate possible is:

FCY/16 (if BRG = 0),

and the minimum baud rate possible is:

FCY/(16 \* 65536).

With a full, 16-bit Baud Rate Generator, at 30 MIPS operation, the minimum baud rate achievable is 28.5 bps.

#### 19.6.2 PRESCALER SETTING

There is a programmable prescaler with integral values ranging from 1 to 64 in addition to a fixed divide-by-2 for clock generation. The Time Quantum (TQ) is a fixed unit of time derived from the oscillator period, shown in Equation 19-1, where FCAN is FCY (if the CANCKS bit is set) or 4 FCY (if CANCKS is cleared).

| Note: | FCAN must not exceed 30 MHz. If     |

|-------|-------------------------------------|

|       | CANCKS = 0, FCY must not exceed 7.5 |

|       | MHz.                                |

#### EQUATION 19-1: TIME QUANTUM FOR CLOCK GENERATION

TQ = 2 (BRP < 5:0 > + 1)/FCAN

#### 19.6.3 PROPAGATION SEGMENT

This part of the bit time is used to compensate physical delay times within the network. These delay times consist of the signal propagation time on the bus line and the internal delay time of the nodes. The propagation segment can be programmed from  $1 \text{ T}_Q$  to  $8 \text{ T}_Q$  by setting the PRSEG<2:0> bits (C1CFG2<2:0>).

#### 19.6.4 PHASE SEGMENTS

The phase segments are used to optimally locate the sampling of the received bit within the transmitted bit time. The sampling point is between Phase1 Seg and Phase2 Seg. These segments are lengthened or shortened by resynchronization. The end of the Phase1 Seg determines the sampling point within a bit period. The segment is programmable from 1 TQ to 8 TQ. Phase2 Seg provides delay to the next transmitted data transition. The segment is programmable from 1 TQ to 8 TQ, or it may be defined to be equal to the greater of Phase1 Seg or the information processing time (2 TQ). The Phase1 Seg is initialized by setting bits SEG1PH<2:0> (C1CFG2<5:3>), and Phase2 Seg is initialized by setting SEG2PH<2:0> (C1CFG2<10:8>).

The following requirement must be fulfilled while setting the lengths of the phase segments:

Propagation Segment + Phase1 Seg > = Phase2 Seg

#### 19.6.5 SAMPLE POINT

The sample point is the point of time at which the bus level is read and interpreted as the value of that respective bit. The location is at the end of Phase1 Seg. If the bit timing is slow and contains many TQ, it is possible to specify multiple sampling of the bus line at the sample point. The level determined by the CAN bus then corresponds to the result from the majority decision of three values. The majority samples are taken at the sample point and twice before with a distance of TQ/2. The CAN module allows the user to choose between sampling three times at the same point, or once at the same point, by setting or clearing the SAM bit (C1CFG2<6>).

Typically, the sampling of the bit should take place at about 60-70% through the bit time depending on the system parameters.

#### 19.6.6 SYNCHRONIZATION

To compensate for phase shifts between the oscillator frequencies of the different bus stations, each CAN controller must be able to synchronize to the relevant signal edge of the incoming signal. When an edge in the transmitted data is detected, the logic will compare the location of the edge to the expected time (synchronous segment). The circuit will then adjust the values of Phase1 Seg and Phase2 Seg. There are 2 mechanisms used to synchronize.

#### 19.6.6.1 Hard Synchronization

Hard synchronization is only done whenever there is a 'recessive' to 'dominant' edge during bus ldle, indicating the start of a message. After hard synchronization, the bit time counters are restarted with the synchronous segment. Hard synchronization forces the edge which has caused the hard synchronization to lie within the synchronization segment of the restarted bit time. If a hard synchronization is done, there will not be a resynchronization within that bit time.

### 19.6.6.2 Resynchronization

As a result of resynchronization, Phase1 Seg may be lengthened or Phase2 Seg may be shortened. The amount of lengthening or shortening of the phase buffer segment has an upper bound known as the synchronization jump width, and is specified by the SJW<1:0> bits (C1CFG1<7:6>). The value of the synchronization jump width will be added to Phase1 Seg or subtracted from Phase2 Seg. The resynchronization jump width is programmable between 1 Tq and 4 Tq.

The following requirement must be fulfilled while setting the SJW<1:0> bits:

Phase2 Seg > Synchronization Jump Width

# 21.0 SYSTEM INTEGRATION

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Power-Saving Modes (Sleep and Idle)

- Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer which is permanently enabled via the Configuration bits, or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active, but the CPU is shut off. The RC oscillator option saves system cost, while the LP crystal option saves power.

### 21.1 Oscillator System Overview

The dsPIC30F oscillator system has the following modules and features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Oscillator Control register (OSCCON)

- · Configuration bits for main oscillator selection

Table 21-1 provides a summary of the dsPIC30F oscillator operating modes. A simplified diagram of the oscillator system is shown in Figure 21-1.

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

### 23.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

# 23.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

# 23.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

### 23.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 23.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### TABLE 24-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACT       | ERISTICS                  |     | Standard Operating te | emperature | -40°C ≤TA ≤+85 | <b>5.5V (unless otherwise stated)</b><br>5°C for Industrial<br>25°C for Extended |

|------------------|---------------------------|-----|-----------------------|------------|----------------|----------------------------------------------------------------------------------|

| Parameter<br>No. | Typical <sup>(1)</sup>    | Мах | Units                 |            | Co             | nditions                                                                         |

| Operating Cur    | rent (IDD) <sup>(2)</sup> |     | ·                     | ·          |                |                                                                                  |

| DC31a            | 2                         | 4   | mA                    | +25°C      |                |                                                                                  |

| DC31b            | 2                         | 4   | mA                    | +85°C      | 3.3V           |                                                                                  |

| DC31c            | 2                         | 4   | mA                    | +125°C     |                | 0.128 MIPS                                                                       |

| DC31e            | 3                         | 5   | mA                    | +25°C      |                | LPRC (512 kHz)                                                                   |

| DC31f            | 3                         | 5   | mA                    | +85°C      | 5V             |                                                                                  |

| DC31g            | 3                         | 5   | mA                    | +125°C     |                |                                                                                  |

| DC30a            | 4                         | 6   | mA                    | +25°C      |                |                                                                                  |

| DC30b            | 4                         | 6   | mA                    | +85°C      | 3.3V           |                                                                                  |

| DC30c            | 4                         | 6   | mA                    | +125°C     |                | (1.8 MIPS)                                                                       |

| DC30e            | 7                         | 10  | mA                    | +25°C      |                | FRC (7.37 MHz)                                                                   |

| DC30f            | 7                         | 10  | mA                    | +85°C      | 5V             |                                                                                  |

| DC30g            | 7                         | 10  | mA                    | +125°C     |                |                                                                                  |

| DC23a            | 12                        | 19  | mA                    | +25°C      |                | 4 MIPS                                                                           |

| DC23b            | 12                        | 19  | mA                    | +85°C      | 3.3V           |                                                                                  |

| DC23c            | 13                        | 19  | mA                    | +125°C     |                |                                                                                  |

| DC23e            | 19                        | 31  | mA                    | +25°C      |                |                                                                                  |

| DC23f            | 20                        | 31  | mA                    | +85°C      | 5V             |                                                                                  |

| DC23g            | 20                        | 31  | mA                    | +125°C     |                |                                                                                  |

| DC24a            | 28                        | 39  | mA                    | +25°C      |                |                                                                                  |

| DC24b            | 28                        | 39  | mA                    | +85°C      | 3.3V           |                                                                                  |

| DC24c            | 29                        | 39  | mA                    | +125°C     |                |                                                                                  |

| DC24e            | 46                        | 64  | mA                    | +25°C      |                | 10 MIPS                                                                          |

| DC24f            | 46                        | 64  | mA                    | +85°C      | 5V             |                                                                                  |

| DC24g            | 47                        | 64  | mA                    | +125°C     |                |                                                                                  |

| DC27a            | 53                        | 72  | mA                    | +25°C      | 2.01/          |                                                                                  |

| DC27b            | 53                        | 72  | mA                    | +85°C      | 3.3V           |                                                                                  |

| DC27d            | 87                        | 120 | mA                    | +25°C      |                | 20 MIPS                                                                          |

| DC27e            | 87                        | 120 | mA                    | +85°C      | 5V             |                                                                                  |

| DC27f            | 87                        | 120 | mA                    | +125°C     | ]              |                                                                                  |

| DC29a            | 124                       | 170 | mA                    | +25°C      | 5)/            |                                                                                  |

| DC29b            | 125                       | 170 | mA                    | +85°C      | 5V             | 30 MIPS                                                                          |

**Note 1:** Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows: OSC1 driven with external square wave from rail to rail. All I/O pins are configured as inputs and pulled to VDD. MCLR = VDD, WDT, FSCM, LVD and BOR are disabled. CPU, SRAM, program memory and data memory are operational. No peripheral modules are operating.

#### TABLE 24-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |                            |                | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |      |   |      |       |                        |  |

|--------------------|----------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|------|-------|------------------------|--|

| Param<br>No.       | Symbol                     | Character      | Characteristic                                                                                                                                                                   |      |   | Max  | Units | Conditions             |  |

| BO10               | VBOR                       | BOR Voltage on | BORV = 11 <sup>(3)</sup>                                                                                                                                                         |      | _ | _    | V     | Not in operating range |  |

|                    |                            | VDD Transition | BORV = 10                                                                                                                                                                        | 2.6  | — | 2.71 | V     |                        |  |

|                    | High-to-Low <sup>(2)</sup> |                | BORV = 01                                                                                                                                                                        | 4.1  | — | 4.4  | V     |                        |  |

|                    |                            |                | BORV = 00                                                                                                                                                                        | 4.58 | — | 4.73 | V     |                        |  |

| BO15               | VBHYS                      |                |                                                                                                                                                                                  | _    | 5 | _    | mV    |                        |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** These parameters are characterized but not tested in manufacturing.

**3:** '11' values not in usable operating range.

| DC CHARACTERISTICS |        |                                     |                                  | rd Opera<br>ing temp | -   | -40°C : | <b>: 2.5V to 5.5V (unless otherwise stated)</b><br>≤TA ≤+85°C for Industrial<br>≤TA ≤+125°C for Extended |

|--------------------|--------|-------------------------------------|----------------------------------|----------------------|-----|---------|----------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                      | Min Typ <sup>(1)</sup> Max Units |                      |     | Units   | Conditions                                                                                               |

|                    |        | Data EEPROM Memory <sup>(2)</sup>   |                                  |                      |     |         |                                                                                                          |

| D120               | ED     | Byte Endurance                      | 100K                             | 1M                   | —   | E/W     | -40° C ≤TA ≤+85°C                                                                                        |

| D121               | Vdrw   | VDD for Read/Write                  | Vmin                             | _                    | 5.5 | V       | Using EECON to read/write,<br>Vмм = Minimum operating voltage                                            |

| D122               | TDEW   | Erase/Write Cycle Time              | 0.8                              | 2                    | 2.6 | ms      | RTSP                                                                                                     |

| D123               | Tretd  | Characteristic Retention            | 40                               | 100                  | —   | Year    | Provided no other specifications are violated                                                            |

| D124               | IDEW   | IDD During Programming              | —                                | 10                   | 30  | mA      | Row Erase                                                                                                |

|                    |        | Program Flash Memory <sup>(2)</sup> |                                  |                      |     |         |                                                                                                          |

| D130               | Eр     | Cell Endurance                      | 10K                              | 100K                 | —   | E/W     | -40° C ≤TA ≤+85°C                                                                                        |

| D131               | Vpr    | VDD for Read                        | VMIN                             |                      | 5.5 | V       | VMIN = Minimum operating voltage                                                                         |

| D132               | VEB    | VDD for Bulk Erase                  | 4.5                              |                      | 5.5 | V       |                                                                                                          |

| D133               | VPEW   | VDD for Erase/Write                 | 3.0                              |                      | 5.5 | V       |                                                                                                          |

| D134               | TPEW   | Erase/Write Cycle Time              | 0.8                              | 2                    | 2.6 | ms      | RTSP                                                                                                     |

| D135               | Tretd  | Characteristic Retention            | 40                               | 100                  | —   | Year    | Provided no other specifications are violated                                                            |

| D137               | IPEW   | IDD During Programming              | —                                | 10                   | 30  | mA      | Row Erase                                                                                                |

| D138               | lев    | IDD During Programming              | —                                | 10                   | 30  | mA      | Bulk Erase                                                                                               |

#### TABLE 24-11: DC CHARACTERISTICS: PROGRAM AND EEPROM

Note 1: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

2: These parameters are characterized but not tested in manufacturing.

# TABLE 24-20: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| AC CHARACTERISTICS |                         |                                                             | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                   |                   |                |                                                  |  |

|--------------------|-------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|----------------|--------------------------------------------------|--|

| Param<br>No.       | Symbol                  | Characteristic <sup>(1)</sup>                               | Min Typ <sup>(2)</sup> Max Units Conditions                                                                                                                                              |                   |                   |                |                                                  |  |

| SY10               | TmcL                    | MCLR Pulse Width (low)                                      | 2                                                                                                                                                                                        | —                 | _                 | μs             | -40°C to +85°C                                   |  |

| SY11               | TPWRT                   | Power-up Timer Period                                       | 2<br>8<br>32                                                                                                                                                                             | 4<br>16<br>64     | 6<br>24<br>96     | ms             | -40°C to +85°C, VDD = 5V<br>User programmable    |  |

| SY12               | TPOR                    | Power-on Reset Delay                                        | 3                                                                                                                                                                                        | 10                | 30                | μs             | -40°C to +85°C                                   |  |

| SY13               | Tioz                    | I/O High-Impedance from MCLR<br>Low or Watchdog Timer Reset |                                                                                                                                                                                          | 0.8               | 1.0               | μs             |                                                  |  |

| SY20               | Twdt1<br>Twdt2<br>Twdt3 | Watchdog Timer Time-out<br>Period<br>(No Prescaler)         | 0.6<br>0.8<br>1.0                                                                                                                                                                        | 2.0<br>2.0<br>2.0 | 3.4<br>3.2<br>3.0 | ms<br>ms<br>ms | VDD = 2.5V<br>VDD = 3.3V, ±10%<br>VDD = 5V, ±10% |  |

| SY25               | TBOR                    | Brown-out Reset Pulse Width <sup>(3)</sup>                  | 100                                                                                                                                                                                      | —                 | _                 | μs             | Vdd ⊴Vbor (D034)                                 |  |

| SY30               | Tost                    | Oscillation Start-up Timer Period                           | _                                                                                                                                                                                        | 1024 Tosc         |                   | _              | Tosc = OSC1 period                               |  |

| SY35               | TFSCM                   | Fail-Safe Clock Monitor Delay                               | _                                                                                                                                                                                        | 500               | 900               | μs             | -40°C to +85°C                                   |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**3:** Refer to Figure 24-1 and Table 24-10 for BOR.

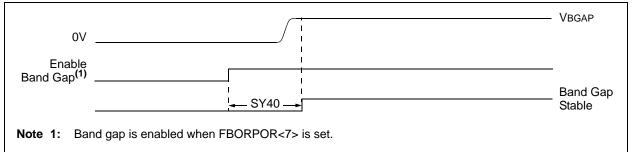

### FIGURE 24-6: BAND GAP START-UP TIME CHARACTERISTICS

### TABLE 24-21: BAND GAP START-UP TIME REQUIREMENTS

| AC CHARACTERISTICS |        |                               |                                             | ard Oper<br>ting temp |    | -40°C | ns: 2.5V to 5.5V (unless otherwise stated)<br>C ≤TA ≤+85°C for Industrial<br>C ≤TA ≤+125°C for Extended                                                          |

|--------------------|--------|-------------------------------|---------------------------------------------|-----------------------|----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min Typ <sup>(2)</sup> Max Units Conditions |                       |    |       |                                                                                                                                                                  |

| SY40               | Tbgap  | Band Gap<br>Start-up Time     | _                                           | 40                    | 65 | μs    | Defined as the time between the instant<br>that the band gap is enabled and the<br>moment that the band gap reference<br>voltage is stable (RCON<13> status bit) |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated.

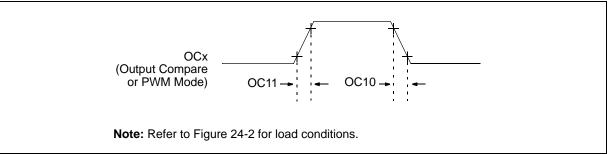

### FIGURE 24-10: OUTPUT COMPARE MODULE TIMING CHARACTERISTICS

### TABLE 24-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                    |

|--------------------|--------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Мах | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                        | _                  |     | ns    | See parameter DO32 |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO31 |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

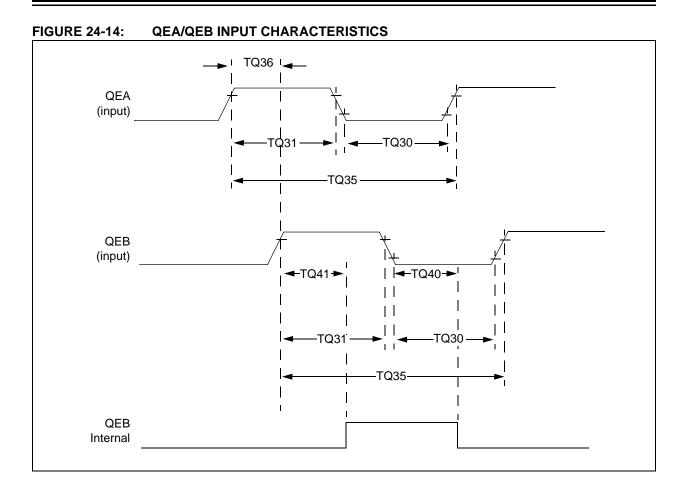

### TABLE 24-30: QUADRATURE DECODER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |     |       |                                                         |

|--------------------|--------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|---------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                        | Тур <sup>(2)</sup>                                                                                                                                                                       | Max | Units | Conditions                                              |

| TQ30               | TQUL   | Quadrature Input Low Time                            | 6 Tcy                                                                                                                                                                                    | —   | ns    |                                                         |

| TQ31               | ΤουΗ   | Quadrature Input High Time                           | 6 Tcy                                                                                                                                                                                    | —   | ns    |                                                         |

| TQ35               | ΤουΙΝ  | Quadrature Input Period                              | 12 TCY                                                                                                                                                                                   | —   | ns    |                                                         |

| TQ36               | ΤουΡ   | Quadrature Phase Period                              | 3 TCY                                                                                                                                                                                    | —   | ns    |                                                         |

| TQ40               | TQUFL  | Filter Time to Recognize Low,<br>with Digital Filter | 3 * N * Tcy                                                                                                                                                                              | —   | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 2)</b> |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter   | 3 * N * Tcy                                                                                                                                                                              | —   | ns    | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 2)</b> |

Note 1: These parameters are characterized but not tested in manufacturing.

2: N = Index Channel Digital Filter Clock Divide Select bits. Refer to Section 16. "Quadrature Encoder Interface (QEI)" in the "dsPIC30F Family Reference Manual" (DS70046).

# TABLE 24-37: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| АС СНА       | RACTERIS | STICS             | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |             |      |       |                                             |  |

|--------------|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------|---------------------------------------------|--|

| Param<br>No. | Symbol   | Charac            | teristic                                                                                                                                                                         | Min         | Max  | Units | Conditions                                  |  |

| IS10         | TLO:SCL  | Clock Low Time    | 100 kHz mode                                                                                                                                                                     | 4.7         | _    | μs    | Device must operate at a minimum of 1.5 MHz |  |

|              |          |                   | 400 kHz mode                                                                                                                                                                     | 1.3         | —    | μs    | Device must operate at a minimum of 10 MHz. |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.5         | —    | μs    |                                             |  |

| IS11         | THI:SCL  | Clock High Time   | 100 kHz mode                                                                                                                                                                     | 4.0         | _    | μs    | Device must operate at a minimum of 1.5 MHz |  |

|              |          |                   | 400 kHz mode                                                                                                                                                                     | 0.6         | _    | μs    | Device must operate at a minimum of 10 MHz  |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.5         |      | μs    |                                             |  |

| IS20         | TF:SCL   | SDA and SCL       | 100 kHz mode                                                                                                                                                                     | —           | 300  | ns    | CB is specified to be from                  |  |

|              |          | Fall Time         | 400 kHz mode                                                                                                                                                                     | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | —           | 100  | ns    |                                             |  |

| IS21         | TR:SCL   | SDA and SCL       | 100 kHz mode                                                                                                                                                                     | —           | 1000 | ns    | CB is specified to be from                  |  |

|              |          | Rise Time         | 400 kHz mode                                                                                                                                                                     | 20 + 0.1 Св | 300  | ns    | 10 to 400 pF                                |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | —           | 300  | ns    |                                             |  |

| IS25         | TSU:DAT  | Data Input        | 100 kHz mode                                                                                                                                                                     | 250         |      | ns    |                                             |  |

|              |          | Setup Time        | 400 kHz mode                                                                                                                                                                     | 100         | —    | ns    |                                             |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 100         | —    | ns    |                                             |  |

| IS26         | THD:DAT  | Data Input        | 100 kHz mode                                                                                                                                                                     | 0           | —    | ns    |                                             |  |

|              |          | Hold Time         | 400 kHz mode                                                                                                                                                                     | 0           | 0.9  | μs    |                                             |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0           | 0.3  | μs    |                                             |  |

| IS30         | TSU:STA  | Start Condition   | 100 kHz mode                                                                                                                                                                     | 4.7         |      | μs    | Only relevant for Repeated                  |  |

|              |          | Setup Time        | 400 kHz mode                                                                                                                                                                     | 0.6         | _    | μs    | Start condition                             |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.25        | _    | μs    |                                             |  |

| IS31         | THD:STA  | Start Condition   | 100 kHz mode                                                                                                                                                                     | 4.0         |      | μs    | After this period, the first                |  |

|              |          | Hold Time         | 400 kHz mode                                                                                                                                                                     | 0.6         |      | μs    | clock pulse is generated                    |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.25        | —    | μs    |                                             |  |

| IS33         | TSU:STO  | Stop Condition    | 100 kHz mode                                                                                                                                                                     | 4.7         | —    | μs    |                                             |  |

|              |          | Setup Time        | 400 kHz mode                                                                                                                                                                     | 0.6         | —    | μs    |                                             |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.6         |      | μs    |                                             |  |

| IS34         | THD:STO  | Stop Condition    | 100 kHz mode                                                                                                                                                                     | 4000        | —    | ns    |                                             |  |

|              |          | Hold Time         | 400 kHz mode                                                                                                                                                                     | 600         |      | ns    |                                             |  |

|              |          |                   | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 250         |      | ns    |                                             |  |

| IS40         | TAA:SCL  | Output Valid      | 100 kHz mode                                                                                                                                                                     | 0           | 3500 | ns    |                                             |  |