Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                  |

| Number of I/O              | 30                                                                             |

| Program Memory Size        | 48KB (16K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 2K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4011t-20e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

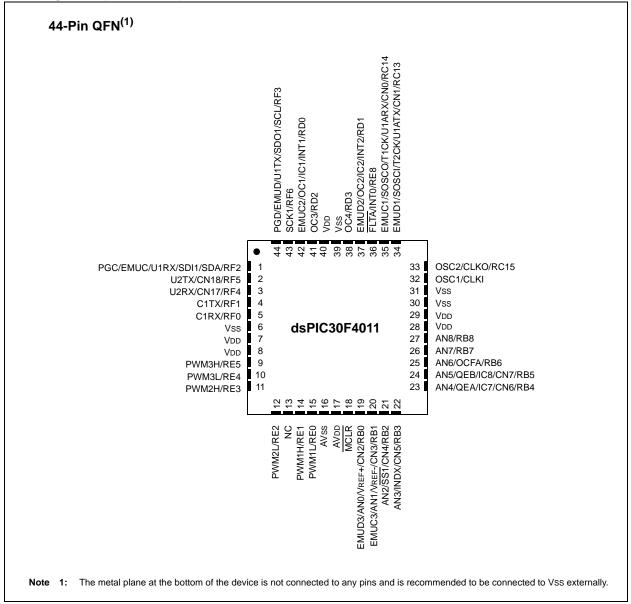

## **Pin Diagrams (Continued)**

Table 1-2 provides a brief description of the device I/O pinout and the functions that are multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

| Pin Name                                                           | Pin<br>Type                                          | Buffer<br>Type                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AN0-AN5                                                            | I                                                    | Analog                                 | Analog input channels. AN0 and AN1 are also used for device programming data and clock inputs, respectively.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| AVdd                                                               | Р                                                    | Р                                      | Positive supply for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| AVss                                                               | Р                                                    | Р                                      | Ground reference for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| CLKI<br>CLKO                                                       | - 0                                                  | ST/CMOS<br>—                           | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| CN0-CN7                                                            | I                                                    | ST                                     | nput change notification inputs. Can be software programmed for internal<br>reak pull-ups on all inputs.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| C1RX<br>C1TX                                                       | <br>0                                                | ST<br>—                                | CAN1 bus receive pin.<br>CAN1 bus transmit pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUD2<br>EMUC2<br>EMUD3<br>EMUC3 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST | ICD Primary Communication Channel data input/output pin.<br>ICD Primary Communication Channel clock input/output pin.<br>ICD Secondary Communication Channel data input/output pin.<br>ICD Secondary Communication Channel clock input/output pin.<br>ICD Tertiary Communication Channel data input/output pin.<br>ICD Tertiary Communication Channel clock input/output pin.<br>ICD Quaternary Communication Channel clock input/output pin.<br>ICD Quaternary Communication Channel clock input/output pin. |  |  |  |  |  |  |

| IC1, IC2, IC7,<br>IC8                                              | I                                                    | ST                                     | Capture inputs 1, 2, 7 and 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| INDX<br>QEA                                                        |                                                      | ST<br>ST                               | Quadrature Encoder Index Pulse input.<br>Quadrature Encoder Phase A input in QEI mode.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| QEB                                                                | Ι                                                    | ST                                     | Auxiliary Timer External Clock/Gate input in Timer mode.<br>Quadrature Encoder Phase B input in QEI mode.<br>Auxiliary Timer External Clock/Gate input in Timer mode.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| INT0<br>INT1<br>INT2                                               |                                                      | ST<br>ST<br>ST                         | External interrupt 0.<br>External interrupt 1.<br>External interrupt 2.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| FLTA<br>PWM1L<br>PWM1H                                             | <br>0<br>0                                           | ST<br>—<br>—                           | PWM Fault A input.<br>PWM1 low output.<br>PWM1 high output.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| PWM2L<br>PWM2H<br>PWM3L                                            | 0<br>0<br>0                                          |                                        | PWM2 low output.<br>PWM2 high output.<br>PWM3 low output.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| PWM3H                                                              | Ō                                                    | —                                      | PWM3 high output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| MCLR                                                               | I/P                                                  | ST                                     | Master Clear (Reset) input or programming voltage input. This pin is an active-low Reset to the device.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| OCFA<br>OC1, OC2                                                   | <br>0                                                | ST<br>—                                | Compare Fault A input (for Compare channels 1, 2, 3 and 4).<br>Compare outputs 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Legend: CM<br>ST<br>I                                              | = Sc                                                 |                                        | tible input or outputAnalog =Analog inputr input with CMOS levelsO=OutputP=Power                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

TABLE 1-2: dsPIC30F4012 I/O PIN DESCRIPTIONS

### 2.4.1 MULTIPLIER

The 17x17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17x17-bit multiplier/ scaler is a 33-bit value, which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the MSB is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1} - 1$ . For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF), including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,645 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSB is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to  $(1-2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF), including 0, and has a precision of 3.01518x10<sup>-5</sup>. In Fractional mode, a 16x16 multiply operation generates a 1.31 product, which has a precision of 4.65661x10<sup>-10</sup>.

The same multiplier is used to support the DSC multiply instructions, which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word-sized operands. Byte operands direct a 16-bit result, and word operands direct a 32-bit result to the specified register(s) in the W array.

## 2.4.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/ subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter, prior to accumulation.

## 2.4.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side and either true or complement data into the other input. In the case of addition, the carry/borrow input is active-high and the other input is true data (not complemented), whereas in the case of subtraction, the carry/borrow input is active-low and the other input is complemented. The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register.

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described above, and the SATA/B (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits have been provided to support saturation and overflow; they are:

- 1. OA: ACCA overflowed into guard bits.

- 2. OB: ACCB overflowed into guard bits.

- 3. SA: ACCA saturated (bit 31 overflow and saturation). *or*

ACCA overflowed into guard bits and saturated (bit 39 overflow and saturation).

SB: ACCB saturated (bit 31 overflow and saturation).

or ACCB overflowed into guard bits and saturated (bit 39 overflow and saturation).

5. OAB: Logical OR of OA and OB.

4

6. SAB: Logical OR of SA and SB.

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). Also, the OA and OB bits can optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bit (OVATE, OVBTE) in the INTCON1 register (refer to **Section 5.0 "Interrupts"**) is set. This allows the user to take immediate action, for example, to correct system gain.

# dsPIC30F4011/4012

All byte loads into any W register are loaded into the LSB; the MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

#### 3.2.5 NEAR DATA SPACE

An 8-Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support Memory Direct Addressing with a 16-bit address field.

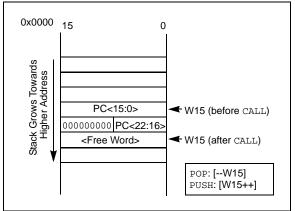

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC contains a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 3-9. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing concatenates the SRL register to the MSB of the PC prior to the push.

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0', because all stack operations must be word-aligned. Whenever an Effective Address (EA) is generated, using W15 as a source or destination pointer, the address thus generated is compared with the value in the SPLIM register. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 3-9: CALL STACK FRAME

# dsPIC30F4011/4012

NOTES:

## 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt on period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt will be generated, if enabled. The T1IF bit must be cleared in software. The Timer Interrupt Flag, T1IF, is located in the IFS0 control register in the interrupt controller.

When the Gated Time Accumulation mode is enabled, an interrupt will also be generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective Timer Interrupt Enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

## 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time-of-day and event time-stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- Real-Time Clock interrupts

These operating modes are determined by setting the appropriate bit(s) in the T1CON Control register

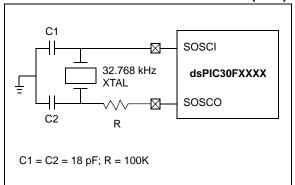

#### FIGURE 9-2: RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR REAL-TIME CLOCK (RTC)

### 9.5.1 RTC OSCILLATOR OPERATION

When TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register, and is then reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling LPOSCEN (OSCCON<1>) will disable the normal Timer and Counter modes and enable a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC will continue to operate, provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

#### 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective Timer Interrupt Flag, T1IF, is asserted and an interrupt will be generated, if enabled. The T1IF bit must be cleared in software. The respective Timer Interrupt Flag, T1IF, is located in the IFS0 Status register in the interrupt controller.

Enabling an interrupt is accomplished via the respective Timer Interrupt Enable bit, T1IE. The Timer Interrupt Enable bit is located in the IEC0 control register in the interrupt controller.

### 12.1 Simple Capture Event Mode

The simple capture events in the dsPIC30F product family are:

- Capture every falling edge

- · Capture every rising edge

- Capture every 4th rising edge

- Capture every 16th rising edge

- · Capture every rising and falling edge

These simple Input Capture modes are configured by setting the appropriate bits ICM<2:0> (ICxCON<2:0>).

#### 12.1.1 CAPTURE PRESCALER

There are four input capture prescaler settings, specified by bits, ICM<2:0> (ICxCON<2:0>). Whenever the capture channel is turned off, the prescaler counter will be cleared. In addition, any Reset will clear the prescaler counter.

#### 12.1.2 CAPTURE BUFFER OPERATION

Each capture channel has an associated FIFO buffer which is four, 16-bit words deep. There are two status flags which provide status on the FIFO buffer:

- ICBNE Input Capture Buffer Not Empty

- ICOV Input Capture Overflow

The ICBNE bit will be set on the first input capture event and remain set until all capture events have been read from the FIFO. As each word is read from the FIFO, the remaining words are advanced by one position within the buffer.

In the event that the FIFO is full with four capture events, and a fifth capture event occurs prior to a read of the FIFO, an overflow condition will occur and the ICOV bit will be set to a logic '1'. The fifth capture event is lost and is not stored in the FIFO. No additional events will be captured till all four events have been read from the buffer.

If a FIFO read is performed after the last read and no new capture event has been received, the read will yield indeterminate results.

## 12.1.3 TIMER2 AND TIMER3 SELECTION MODE

Each capture channel can select between one of two timers for the time base, Timer2 or Timer3.

Selection of the timer resource is accomplished through SFR bit, ICTMR (ICxCON<7>). Timer3 is the default timer resource available for the input capture module.

#### 12.1.4 HALL SENSOR MODE

When the input capture module is set for capture on every edge, rising and falling, ICM<2:0> = 001, the following operations are performed by the input capture logic:

- The input capture interrupt flag is set on every edge, rising and falling.

- The interrupt on Capture mode setting bits, ICI<1:0>, is ignored, since every capture generates an interrupt.

- A capture overflow condition is not generated in this mode.

#### 12.2 Input Capture Operation During Sleep and Idle Modes

An input capture event will generate a device wake-up or interrupt, if enabled, if the device is in CPU Idle or Sleep mode.

Independent of the timer being enabled, the input capture module will wake-up from the CPU Sleep or Idle mode when a capture event occurs, if ICM<2:0> = 111 and the interrupt enable bit is asserted. The same wake-up can generate an interrupt if the conditions for processing the interrupt have been satisfied. The wake-up feature is useful as a method of adding extra external pin interrupts.

#### 12.2.1 INPUT CAPTURE IN CPU SLEEP MODE

CPU Sleep mode allows input capture module operation with reduced functionality. In the CPU Sleep mode, the ICI<1:0> bits are not applicable, and the input capture module can only function as an external interrupt source.

The capture module must be configured for interrupt only on the rising edge (ICM<2:0> = 111) in order for the input capture module to be used while the device is in Sleep mode. The prescale settings of 4:1 or 16:1 are not applicable in this mode.

#### 12.2.2 INPUT CAPTURE IN CPU IDLE MODE

CPU Idle mode allows input capture module operation with full functionality. In the CPU Idle mode, the interrupt mode selected by the ICI<1:0> bits are applicable, as well as the 4:1 and 16:1 capture prescale settings which are defined by control bits ICM<2:0>. This mode requires the selected timer to be enabled. Moreover, the ICSIDL bit must be asserted to a logic '0'.

If the input capture module is defined as ICM<2:0> = 111 in CPU Idle mode, the input capture pin will serve only as an external interrupt pin.

# dsPIC30F4011/4012

NOTES:

## 18.2 Enabling and Setting Up UART

#### 18.2.1 ENABLING THE UART

The UART module is enabled by setting the UARTEN bit in the UxMODE register (where x = 1 or 2). Once enabled, the UxTX and UxRX pins are configured as an output and an input, respectively, overriding the TRIS and LATCH register bit settings for the corresponding I/O port pins. The UxTX pin is at logic '1' when no transmission is taking place.

#### 18.2.2 DISABLING THE UART

The UART module is disabled by clearing the UARTEN bit in the UxMODE register. This is the default state after any Reset. If the UART is disabled, all I/O pins operate as port pins under the control of the LATCH and TRIS bits of the corresponding port pins.

Disabling the UART module resets the buffers to empty states. Any data characters in the buffers are lost and the baud rate counter is reset.

All error and status flags associated with the UART module are reset when the module is disabled. The URXDA, OERR, FERR, PERR, UTXEN, UTXBRK and UTXBF bits are cleared, whereas RIDLE and TRMT are set. Other control bits, including ADDEN, URXISEL<1:0>, UTXISEL, as well as the UxMODE and UxBRG registers, are not affected.

Clearing the UARTEN bit while the UART is active will abort all pending transmissions and receptions and reset the module as defined above. Re-enabling the UART will restart the UART in the same configuration.

#### 18.2.3 ALTERNATE I/O

The alternate I/O function is enabled by setting the ALTIO bit (UxMODE<10>). If ALTIO = 1, the UxATX and UxARX pins (alternate transmit and alternate receive pins, respectively) are used by the UART module instead of the UxTX and UxRX pins. If ALTIO = 0, the UxTX and UxRX pins are used by the UART module.

## 18.2.4 SETTING UP DATA, PARITY AND STOP BIT SELECTIONS

Control bits, PDSEL<1:0> in the UxMODE register, are used to select the data length and parity used in the transmission. The data length may either be 8 bits with even, odd or no parity, or 9-bits with no parity.

The STSEL bit determines whether one or two Stop bits will be used during data transmission.

The default (power-on) setting of the UART is 8 bits, no parity and 1 Stop bit (typically represented as 8, N, 1).

#### 18.3 Transmitting Data

#### 18.3.1 TRANSMITTING IN 8-BIT DATA MODE

The following steps must be performed in order to transmit 8-bit data:

- 1. Set up the UART:

- First, the data length, parity and number of Stop bits must be selected. Then, the transmit and receive interrupt enable and priority bits are set up in the UxMODE and UxSTA registers. Also, the appropriate baud rate value must be written to the UxBRG register.

- Enable the UART by setting the UARTEN bit (UxMODE<15>).

- 3. Set the UTXEN bit (UxSTA<10>), thereby enabling a transmission.

- 4. Write the byte to be transmitted to the lower byte of UxTXREG. The value will be transferred to the Transmit Shift register (UxTSR) immediately and the serial bit stream will start shifting out during the next rising edge of the baud clock. Alternatively, the data byte may be written while UTXEN = 0, following which, the user may set UTXEN. This will cause the serial bit stream to begin immediately because the baud clock will start from a cleared state.

- 5. A transmit interrupt will be generated depending on the value of the interrupt control bit UTXISEL (UxSTA<15>).

#### 18.3.2 TRANSMITTING IN 9-BIT DATA MODE

The sequence of steps involved in the transmission of 9-bit data is similar to 8-bit transmission, except that a 16-bit data word (of which the upper 7 bits are always clear) must be written to the UxTXREG register.

#### 18.3.3 TRANSMIT BUFFER (UXTXB)

The transmit buffer is 9 bits wide and 4 characters deep. Including the Transmit Shift register (UxTSR), the user effectively has a 5-deep FIFO (First In First Out) buffer. The UTXBF Status bit (UxSTA<9>) indicates whether the transmit buffer is full.

If a user attempts to write to a full buffer, the new data will not be accepted into the FIFO, and no data shift will occur within the buffer. This enables recovery from a buffer overrun condition.

The FIFO is reset during any device Reset, but is not affected when the device enters or wakes up from a power-saving mode.

#### 18.3.4 TRANSMIT INTERRUPT

The Transmit Interrupt Flag (U1TXIF or U2TXIF) is located in the corresponding interrupt flag register.

The transmitter generates an edge to set the UxTXIF bit. The condition for generating the interrupt depends on UTXISEL control bit:

- a) If UTXISEL = 0, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR). This implies that the transmit buffer has at least one empty word.

- b) If UTXISEL = 1, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR) and the transmit buffer is empty.

Switching between the two interrupt modes during operation is possible and sometimes offers more flexibility.

#### 18.3.5 TRANSMIT BREAK

Setting the UTXBRK bit (UxSTA<11>) will cause the UxTX line to be driven to logic '0'. The UTXBRK bit overrides all transmission activity. Therefore, the user should generally wait for the transmitter to be Idle before setting UTXBRK.

To send a Break character, the UTXBRK bit must be set by software and must remain set for a minimum of 13 baud clock cycles. The UTXBRK bit is then cleared by software to generate Stop bits. The user must wait for a duration of at least one or two baud clock cycles in order to ensure a valid Stop bit(s) before reloading the UxTXB or starting other transmitter activity. Transmission of a Break character does not generate a transmit interrupt.

#### 18.4 Receiving Data

#### 18.4.1 RECEIVING IN 8-BIT OR 9-BIT DATA MODE

The following steps must be performed while receiving 8-bit or 9-bit data:

- 1. Set up the UART (see Section 18.3.1 "Transmitting in 8-bit Data Mode").

- 2. Enable the UART (see Section 18.3.1 "Transmitting in 8-bit Data Mode").

- A receive interrupt will be generated when one or more data words have been received, depending on the receive interrupt settings specified by the URXISEL bits (UxSTA<7:6>).

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- Read the received data from UxRXREG. The act of reading UxRXREG will move the next word to the top of the receive FIFO and the PERR and FERR values will be updated.

#### 18.4.2 RECEIVE BUFFER (UXRXB)

The receive buffer is 4 words deep. Including the Receive Shift register (UxRSR), the user effectively has a 5-word deep FIFO buffer.

URXDA (UxSTA<0>) = 1 indicates that the receive buffer has data available. URXDA = 0 implies that the buffer is empty. If a user attempts to read an empty buffer, the old values in the buffer will be read and no data shift will occur within the FIFO.

The FIFO is reset during any device Reset. It is not affected when the device enters or wakes up from a power-saving mode.

#### 18.4.3 RECEIVE INTERRUPT

The Receive Interrupt Flag (U1RXIF or U2RXIF) can be read from the corresponding interrupt flag register. The interrupt flag is set by an edge generated by the receiver. The condition for setting the receive interrupt flag depends on the settings specified by the URXISEL<1:0> (UxSTA<7:6>) control bits.

- a) If URXISEL<1:0> = 00 or 01, an interrupt is generated every time a data word is transferred from the Receive Shift register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:0> = 10, an interrupt is generated when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer which, as a result of the transfer, contains 3 characters.

- c) If URXISEL<1:0> = 11, an interrupt is set when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer which, as a result of the transfer, contains 4 characters (i.e., becomes full).

Switching between the interrupt modes during operation is possible, though generally not advisable during normal operation.

### 18.5 Reception Error Handling

#### 18.5.1 RECEIVE BUFFER OVERRUN ERROR (OERR BIT)

The OERR bit (UxSTA<1>) is set if all of the following conditions occur:

- a) The receive buffer is full.

- b) The Receive Shift register is full, but unable to transfer the character to the receive buffer.

- c) The Stop bit of the character in the UxRSR is detected, indicating that the UxRSR needs to transfer the character to the buffer.

Once OERR is set, no further data is shifted in UxRSR (until the OERR bit is cleared in software or a Reset occurs). The data held in UxRSR and UxRXREG remains valid.

#### 18.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1', otherwise FERR will be set. The read-only FERR bit is buffered along with the received data; it is cleared on any Reset.

#### 18.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes; it is cleared on any Reset.

#### 18.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

#### 18.5.5 RECEIVE BREAK

The receiver will count and expect a certain number of bit times based on the values programmed in the PDSEL<1:0> (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the Break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated, if appropriate and the RIDLE bit is set.

When the module receives a long Break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the Break condition on the line is the next Start bit.

Break is regarded as a character containing all '0's, with the FERR bit set. The Break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not been received yet.

#### 18.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables this special mode in which a 9th bit (URX8) value of '1' identifies the received word as an address, rather than data. This mode is only applicable for 9-bit data communication. The URXISELx control bit does not have any impact on interrupt generation in this mode, since an interrupt (if enabled) will be generated every time the received word has the 9th bit set.

#### 18.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in **Section 18.3** "**Transmitting Data**".

#### 18.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

- BRG = 16-bit value held in UxBRG register (0 through 65535)

- FCY = Instruction Clock Rate (1/TCY)

The baud rate is given by Equation 18-1.

### EQUATION 18-1: BAUD RATE

Baud Rate = FCY/(16 \* (BRG + 1))

Therefore, maximum baud rate possible is:

FCY/16 (if BRG = 0),

and the minimum baud rate possible is:

FCY/(16 \* 65536).

With a full, 16-bit Baud Rate Generator, at 30 MIPS operation, the minimum baud rate achievable is 28.5 bps.

## 19.0 CAN MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

#### 19.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or digital signal controller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC30F4011/4012 devices have 1 CAN module.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- · Support for remote frames

- Double-buffered receiver with two prioritized received message storage buffers (each buffer may contain up to 8 bytes of data)

- 6 full (standard/extended identifier), acceptance filters, 2 associated with the high priority receive buffer and 4 associated with the low priority receive buffer

- 2 full, acceptance filter masks, one each associated with the high and low priority receive buffers

- Three transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to input capture module (IC2, for both CAN1 and CAN2) for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

### 19.2 Frame Types

The CAN module transmits various types of frames which include data messages or remote transmission requests, initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

#### 19.2.1 STANDARD DATA FRAME

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID) but not an 18-bit Extended Identifier (EID).

#### 19.2.2 EXTENDED DATA FRAME

An extended data frame is similar to a standard data frame but includes an extended identifier as well.

#### 19.2.3 REMOTE FRAME

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

#### 19.2.4 ERROR FRAME

An error frame is generated by any node that detects a bus error. An error frame consists of 2 fields: an error flag field and an error delimiter field.

#### 19.2.5 OVERLOAD FRAME

An overload frame can be generated by a node as a result of 2 conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

#### 19.2.6 INTERFRAME SPACE

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

#### 20.4 Programming the Start of the Conversion Trigger

The conversion trigger terminates acquisition and starts the requested conversions.

The SSRC<2:0> bits select the source of the conversion trigger.

The SSRC bits provide for up to five alternate sources of conversion trigger.

When SSRC<2:0> = 000, the conversion trigger is under software control. Clearing the SAMP bit causes the conversion trigger.

When SSRC<2:0> = 111 (Auto-Start mode), the conversion trigger is under A/D clock control. The SAMC bits select the number of A/D clocks between the start of acquisition and the start of conversion. This provides the fastest conversion rates on multiple channels. SAMC must always be at least one clock cycle.

Other trigger sources can come from timer modules, motor control PWM module or external interrupts.

Note: To operate the ADC at the maximum specified conversion speed, the autoconvert trigger option should be selected (SSRC = 111) and the auto-sample time bits should be set to '1' TAD (SAMC = 00001). This configuration gives a total conversion period (sample + convert) of 13 TAD.

The use of any other conversion trigger results in additional TAD cycles to synchronize the external event to the ADC.

## 20.5 Aborting a Conversion

Clearing the ADON bit during a conversion aborts the current conversion and stops the sampling sequencing. The ADCBUFx is not updated with the partially completed A/D conversion sample. That is, the ADCBUFx will continue to contain the value of the last completed conversion (or the last value written to the ADCBUFx register).

If the clearing of the ADON bit coincides with an auto-start, the clearing has a higher priority.

After the A/D conversion is aborted, a 2 TAD wait is required before the next sampling may be started by setting the SAMP bit.

If sequential sampling is specified, the A/D continues at the next sample pulse, which corresponds with the next channel converted. If simultaneous sampling is specified, the A/D continues with the next multichannel group conversion sequence.

### 20.6 Selecting the A/D Conversion Clock

The A/D conversion requires 12 TAD. The source of the A/D conversion clock is software selected using a 6-bit counter. There are 64 possible options for TAD.

#### EQUATION 20-1: A/D CONVERSION CLOCK

TAD = TCY \*

$$(0.5 * (ADCS < 5:0 > + 1))$$

ADCS < 5:0 > = 2  $\frac{TAD}{TCY} - 1$

The internal RC oscillator is selected by setting the ADRC bit.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 83.33 nsec (for VDD = 5V). Refer to **Section 24.0 "Electrical Characteristics"** for minimum TAD under other operating conditions.

Example 20-1 shows a sample calculation for the ADCS<5:0> bits, assuming a device operating speed of 30 MIPS.

## EXAMPLE 20-1: A/D CONVERSION CLOCK CALCULATION

$$TAD = 154 \text{ nsec}$$

$$TCY = 33 \text{ nsec } (30 \text{ MIPS})$$

$$ADCS < 5:0 > = 2 \frac{TAD}{TCY} - 1$$

$$= 2 \cdot \frac{154 \text{ nsec}}{33 \text{ nsec}} - 1$$

$$= 8.33$$

$$Therefore,$$

$$Set ADCS < 5:0 > = 9$$

$$Actual TAD = \frac{TCY}{2} (ADCS < 5:0 > + 1)$$

$$= \frac{33 \text{ nsec}}{2} (9 + 1)$$

$$= 165 \text{ nsec}$$

#### 20.9 Module Power-Down Modes

The module has 3 internal power modes. When the ADON bit is '1', the module is in Active mode; it is fully powered and functional. When ADON is '0', the module is in Off mode. The digital and analog portions of the circuit are disabled for maximum current savings. In order to return to the Active mode from Off mode, the user must wait for the ADC circuitry to stabilize.

#### 20.10 A/D Operation During CPU Sleep and Idle Modes

#### 20.10.1 A/D OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'.

If Sleep occurs in the middle of a conversion, the conversion is aborted. The converter will not continue with a partially completed conversion on exit from Sleep mode.

Register contents are not affected by the device entering or leaving Sleep mode.

The ADC module can operate during Sleep mode if the A/D clock source is set to RC (ADRC = 1). When the RC clock source is selected, the ADC module waits one instruction cycle before starting the conversion. This allows the SLEEP instruction to be executed, which eliminates all digital switching noise from the conversion. When the conversion is complete, the DONE bit is set and the result is loaded into the ADCBUFx register.

If the A/D interrupt is enabled, the device wakes up from Sleep. If the A/D interrupt is not enabled, the ADC module is then turned off, although the ADON bit remains set.

## 20.10.2 A/D OPERATION DURING CPU IDLE MODE

The ADSIDL bit selects if the module stops on Idle or continues on Idle. If ADSIDL = 0, the module continues operation on assertion of Idle mode. If ADSIDL = 1, the module stops on Idle.

#### 20.11 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the ADC module to be turned off, and any conversion and acquisition sequence is aborted. The values that are in the ADCBUFx registers are not modified. The A/D Result register contains unknown data after a Power-on Reset.

#### 20.12 Output Formats

The A/D result is 10 bits wide. The data buffer RAM is also 10 bits wide. The 10-bit data can be read in one of four different formats. The FORM<1:0> bits select the format. Each of the output formats translates to a 16-bit result on the data bus.

Write data will always be in right justified (integer) format.

| RAM Contents:            |         |     |     |     |     | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|--------------------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Read to Bus:             |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Fractional (1.15) | d09 d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Fractional (1.15)        | d09 d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 | 0   | 0   | 0   | 0   | 0   | 0   |

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Signed Integer           | d09 d09 | d09 | d09 | d09 | d09 | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

|                          |         |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Integer                  | 0 0     | 0   | 0   | 0   | 0   | d09 | d08 | d07 | d06 | d05 | d04 | d03 | d02 | d01 | d00 |

FIGURE 20-4: A/D OUTPUT DATA FORMATS

| Field | Description                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Wb    | Base W register ∈ {W0W15}                                                                                                                                                                                                      |  |  |  |  |  |  |

| Wd    | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                                              |  |  |  |  |  |  |

| Wdo   | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                                           |  |  |  |  |  |  |

| Wm,Wn | Dividend, Divisor working register pair (Direct Addressing)                                                                                                                                                                    |  |  |  |  |  |  |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4*W4, W5*W5, W6*W6, W7*W7}                                                                                                                       |  |  |  |  |  |  |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈ {W4*W5, W4*W6, W4*W7, W5*W6, W5*W7, W6*W7}                                                                                                            |  |  |  |  |  |  |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                          |  |  |  |  |  |  |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                              |  |  |  |  |  |  |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                   |  |  |  |  |  |  |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                       |  |  |  |  |  |  |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                   |  |  |  |  |  |  |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                |  |  |  |  |  |  |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8]+=6, [W8]+=4, [W8]+=2, [W8], [W8]-=6, [W8]-=4, [W8]-=2,<br>[W9]+=6, [W9]+=4, [W9]+=2, [W9], [W9]-=6, [W9]-=4, [W9]-=2,<br>[W9+W12],none}                 |  |  |  |  |  |  |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                       |  |  |  |  |  |  |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10]+=6, [W10]+=4, [W10]+=2, [W10], [W10]-=6, [W10]-=4, [W10]-=2,<br>[W11]+=6, [W11]+=4, [W11]+=2, [W11], [W11]-=6, [W11]-=4, [W11]-=2,<br>[W11+W12], none} |  |  |  |  |  |  |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                       |  |  |  |  |  |  |

## TABLE 22-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| DC CHARACTERISTICS |                            |     | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |        |            |                |  |  |  |  |

|--------------------|----------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----------------|--|--|--|--|

| Parameter<br>No.   | Typical <sup>(1,2)</sup>   | Max | Units                                                                                                                                                                            |        | Conditions |                |  |  |  |  |

| Operating Cu       | rrent (IDD) <sup>(3)</sup> |     |                                                                                                                                                                                  |        |            |                |  |  |  |  |

| DC51a              | 1.3                        | 3   | mA                                                                                                                                                                               | +25°C  |            |                |  |  |  |  |

| DC51b              | 1.3                        | 3   | mA                                                                                                                                                                               | +85°C  | 3.3V       | 0.128 MIPS     |  |  |  |  |

| DC51c              | 1.3                        | 3   | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC51e              | 2.7                        | 5   | mA                                                                                                                                                                               | +25°C  |            | LPRC (512 kHz) |  |  |  |  |

| DC51f              | 2.7                        | 5   | mA                                                                                                                                                                               | +85°C  | 5V         |                |  |  |  |  |

| DC51g              | 2.7                        | 5   | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC50a              | 4                          | 6   | mA                                                                                                                                                                               | +25°C  |            |                |  |  |  |  |

| DC50b              | 4                          | 6   | mA                                                                                                                                                                               | +85°C  | 3.3V       |                |  |  |  |  |

| DC50c              | 4                          | 6   | mA                                                                                                                                                                               | +125°C |            | (1.8 MIPS)     |  |  |  |  |

| DC50e              | 7                          | 11  | mA                                                                                                                                                                               | +25°C  |            | FRC (7.37 MHz) |  |  |  |  |

| DC50f              | 7                          | 11  | mA                                                                                                                                                                               | +85°C  | 5V         |                |  |  |  |  |

| DC50g              | 7                          | 11  | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC43a              | 7                          | 11  | mA                                                                                                                                                                               | +25°C  |            | 4 MIPS         |  |  |  |  |

| DC43b              | 7                          | 11  | mA                                                                                                                                                                               | +85°C  | 3.3V       |                |  |  |  |  |

| DC43c              | 7                          | 11  | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC43e              | 12                         | 17  | mA                                                                                                                                                                               | +25°C  |            |                |  |  |  |  |

| DC43f              | 12                         | 17  | mA                                                                                                                                                                               | +85°C  | 5V         |                |  |  |  |  |

| DC43g              | 12                         | 17  | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC44a              | 15                         | 22  | mA                                                                                                                                                                               | +25°C  |            |                |  |  |  |  |

| DC44b              | 15                         | 22  | mA                                                                                                                                                                               | +85°C  | 3.3V       |                |  |  |  |  |

| DC44c              | 16                         | 22  | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC44e              | 26                         | 36  | mA                                                                                                                                                                               | +25°C  |            | 10 MIPS        |  |  |  |  |

| DC44f              | 27                         | 36  | mA                                                                                                                                                                               | +85°C  | 5V         |                |  |  |  |  |

| DC44g              | 27                         | 36  | mA                                                                                                                                                                               | +125°C |            |                |  |  |  |  |

| DC47a              | 30                         | 40  | mA                                                                                                                                                                               | +25°C  | 0.01/      |                |  |  |  |  |

| DC47b              | 30                         | 40  | mA                                                                                                                                                                               | +85°C  | 3.3V       |                |  |  |  |  |

| DC47d              | 50                         | 65  | mA                                                                                                                                                                               | +25°C  |            | 20 MIPS        |  |  |  |  |

| DC47e              | 50                         | 65  | mA                                                                                                                                                                               | +85°C  | 5∨         |                |  |  |  |  |

| DC47f              | 51                         | 65  | mA                                                                                                                                                                               | +125°C | ]          |                |  |  |  |  |

| DC49a              | 72                         | 95  | mA                                                                                                                                                                               | +25°C  | E) (       |                |  |  |  |  |

| DC49b              | 73                         | 95  | mA                                                                                                                                                                               | +85°C  | 5V         | 30 MIPS        |  |  |  |  |

Note 1: Data in "Typical" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Base IIDLE current is measured with core off, clock on and all modules turned off.

## **Revision G (December 2010)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                             | Update Description                                                                                                                                                        |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-Bit<br>Digital Signal Controllers" | Added Note 1 to all QFN pin diagrams (see "Pin Diagrams").                                                                                                                |

| Section 15.0 "Motor Control<br>PWM Module"               | Added the IUE bit (PWMCON2<2>) to the PWM Register Map (see Table 15-1).<br>Updated the PWM Period equations (see Equation 15-1 and Equation 15-2).                       |

| Section 21.0 "System<br>Integration"                     | Added a shaded note on OSCTUN functionality in Section 21.2.5 "Fast RC Oscillator (FRC)".                                                                                 |

| Section 24.0 "Electrical<br>Characteristics"             | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 24-8).                               |

|                                                          | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 24-11). |

| "Product Identification System"                          | Added the "ML" package definition.                                                                                                                                        |

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

- Development Systems Information Line

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://support.microchip.com

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sygney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung Tel: 886-7-213-7830 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

08/04/10