#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 6x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4012-20e-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

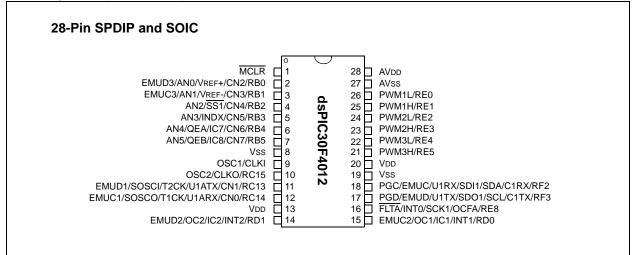

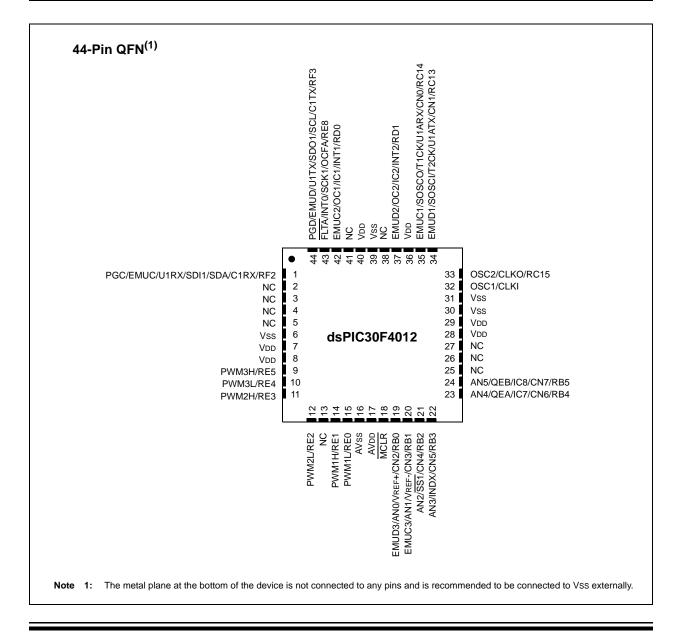

## Pin Diagrams (Continued)

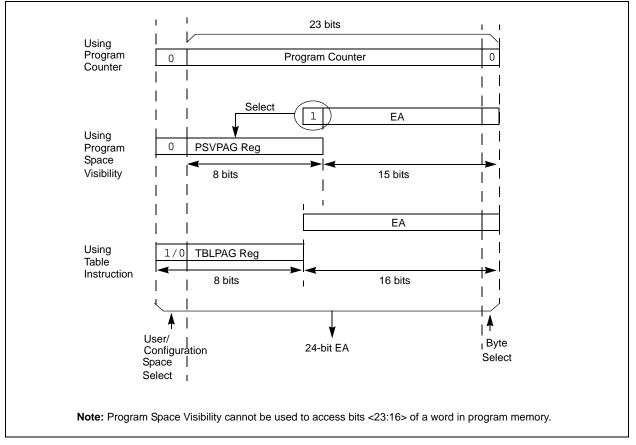

## TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access                           | Program Space Address |            |        |               |      |  |  |  |  |  |

|--------------------------|----------------------------------|-----------------------|------------|--------|---------------|------|--|--|--|--|--|

| Access Type              | Space                            | <23>                  | <22:16>    | <14:1> | <0>           |      |  |  |  |  |  |

| Instruction Access       | User                             | 0                     | 0 PC<22:1> |        |               |      |  |  |  |  |  |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)          | TBL                   | PAG<7:0>   |        | Data EA<15:0> |      |  |  |  |  |  |

| TBLRD/TBLWT              | Configuration<br>(TBLPAG<7> = 1) | TBL                   | .PAG<7:0>  |        | Data EA<15:0> |      |  |  |  |  |  |

| Program Space Visibility | User                             | 0                     | PSVPAG<    | 7:0>   | Data EA<1     | 4:0> |  |  |  |  |  |

## FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

## 6.6 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. A programming operation is nominally 2 msec in duration and the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

#### 6.6.1 PROGRAMMING ALGORITHM FOR PROGRAM FLASH

The user can erase or program one row of program Flash memory at a time. The general process is:

- 1. Read one row of program Flash (32 instruction words) and store into data RAM as a data "image".

- 2. Update the data image with the desired new data.

- 3. Erase program Flash row.

- a) Set up NVMCON register for multi-word, program Flash, erase and set WREN bit.

- b) Write address of row to be erased into NVMADRU/NVMDR.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit. This will begin erase cycle.

- f) CPU will stall for the duration of the erase cycle.

- g) The WR bit is cleared when erase cycle ends.

- Write 32 instruction words of data from data RAM "image" into the program Flash write latches.

- 5. Program 32 instruction words into program Flash.

- a) Set up NVMCON register for multi-word, program Flash, program and set WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. This will begin program cycle.

- e) CPU will stall for duration of the program cycle.

- f) The WR bit is cleared by the hardware when program cycle ends.

- 6. Repeat steps 1 through 5 as needed to program desired amount of program Flash memory.

## 6.6.2 ERASING A ROW OF PROGRAM MEMORY

Example 6-1 shows a code sequence that can be used to erase a row (32 instructions) of program memory.

## EXAMPLE 6-1: ERASING A ROW OF PROGRAM MEMORY

|   | -     |         | for erase operation, multi wor                |   | write                                    |

|---|-------|---------|-----------------------------------------------|---|------------------------------------------|

| i | progr | MOV     | ry selected, and writes enabled<br>#0x4041,W0 | ; |                                          |

|   |       | MOV     | W0,NVMCON                                     | ; | Init NVMCON SFR                          |

| ; | Init  | pointer | to row to be ERASED                           |   |                                          |

|   |       | MOV     | <pre>#tblpage(PROG_ADDR),W0</pre>             | ; |                                          |

|   |       | MOV     | W0 NVMADRU                                    | ; | Initialize PM Page Boundary SFR          |

|   |       | MOV     | <pre>#tbloffset(PROG_ADDR),W0</pre>           | ; | Intialize in-page EA[15:0] pointer       |

|   |       | MOV     | W0, NVMADR                                    | ; | Intialize NVMADR SFR                     |

|   |       | DISI    | #5                                            | ; | Block all interrupts with priority < $7$ |

|   |       |         |                                               | ; | for next 5 instructions                  |

|   |       | MOV     | #0x55,W0                                      |   |                                          |

|   |       | MOV     | WONVMKEY                                      | ; | Write the 0x55 key                       |

|   |       | MOV     | #0xAA,W1                                      | ; |                                          |

|   |       | MOV     | W1 NVMKEY                                     | ; | Write the OxAA key                       |

|   |       | BSET    | NVMCON, #WR                                   | ; | Start the erase sequence                 |

|   |       | NOP     |                                               | ; | Insert two NOPs after the erase          |

|   |       | NOP     |                                               | ; | command is asserted                      |

|   |       |         |                                               |   |                                          |

## TABLE 8-2: dsPIC30F4012 PORT REGISTER MAP<sup>(1)</sup>

|             | • =.  |         | 0001 40 |         |        |        |        |       |        |       |       |        |        |        |        |        |        |                     |

|-------------|-------|---------|---------|---------|--------|--------|--------|-------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

| TRISB       | 02C6  | —       | —       | _       | -      | -      | —      | —     | —      |       | —     | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0000 0011 1111 |

| PORTB       | 02C8  | _       | _       | _       | _      | _      | _      | _     | —      | _     | _     | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CB  | _       | _       | _       | _      | _      | _      | _     | —      | _     | —     | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

| TRISC       | 02CC  | TRISC15 | TRISC14 | TRISC13 | _      | _      | _      | _     | —      | _     | —     | _      | _      | _      | _      | _      | —      | 1110 0000 0000 0000 |

| PORTC       | 02CE  | RC15    | RC14    | RC13    | _      | _      | _      | _     | —      | _     | _     | —      | _      | _      | _      | _      | _      | 0000 0000 0000 0000 |

| LATC        | 02D0  | LATC15  | LATC14  | LATC13  | _      | _      | _      | _     | —      | _     | _     | —      | _      | _      | _      | _      | _      | 0000 0000 0000 0000 |

| TRISD       | 02D2  | _       | _       | _       | _      | _      | _      | _     | —      | _     | _     | —      | _      | _      | _      | TRISD1 | TRISD0 | 0000 0000 0000 0011 |

| PORTD       | 02D4  | _       | _       | _       | _      | _      | _      | _     | —      | _     | _     | —      | _      | _      | _      | RD1    | RD0    | 0000 0000 0000 0000 |

| LATD        | 02D6  | _       | _       | _       | _      | _      | _      | _     | —      | _     | _     | —      | _      | _      | _      | LATD1  | LATD0  | 0000 0000 0000 0000 |

| TRISE       | 02D8  | _       | _       | _       | _      | _      | _      | _     | TRISE8 | _     | _     | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 0000 0001 0011 1111 |

| PORTE       | 02DA  | _       | _       | _       | _      | _      | _      | _     | RE8    | _     | _     | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | 0000 0000 0000 0000 |

| LATE        | 02DC  | _       | _       | _       | _      | _      | _      | _     | LATE8  | _     | _     | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | 0000 0000 0000 0000 |

| TRISF       | 02EE  | —       | —       | _       |        |        |        | —     | _      |       |       | _      | —      | TRISF3 | TRISF2 | —      | _      | 0000 0000 0000 1100 |

| PORTF       | 02E0  | —       | —       | _       |        |        |        | —     | —      | _     | _     | _      | _      | RF3    | RF2    | —      | —      | 0000 0000 0000 0000 |

| LATF        | 02E2  | —       | —       | _       |        | _      |        | —     | _      | _     | _     | _      | _      | LATF3  | LATF2  | —      | —      | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## TABLE 11-1: TIMER4/5 REGISTER MAP<sup>(1)</sup>

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13                                               | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7        | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2               | Bit 1               | Bit 0 | Reset State         |

|----------|-------|--------|--------|------------------------------------------------------|--------|--------|--------|-------|-------|--------------|-------|--------|--------|-------|---------------------|---------------------|-------|---------------------|

| TMR4     | 0114  |        |        |                                                      |        |        |        |       | Tir   | mer4 Regis   | ter   |        |        |       |                     |                     |       | uuuu uuuu uuuu uuuu |

| TMR5HLD  | 0116  |        |        | Timer5 Holding Register (For 32-bit operations only) |        |        |        |       |       |              |       |        |        |       | uuuu uuuu uuuu uuuu |                     |       |                     |

| TMR5     | 0118  |        |        |                                                      |        |        |        |       | Tir   | ner5 Regis   | ter   |        |        |       |                     |                     |       | uuuu uuuu uuuu uuuu |

| PR4      | 011A  |        |        |                                                      |        |        |        |       | Pe    | riod Registe | er 4  |        |        |       |                     |                     |       | 1111 1111 1111 1111 |

| PR5      | 011C  |        | _      |                                                      |        |        |        |       | Pe    | riod Registe | er 5  |        |        |       |                     |                     |       | 1111 1111 1111 1111 |

| T4CON    | 011E  | TON    | _      | - TSIDL TGATE TCKPS1 TCKPS0 T45 - TCS                |        |        |        |       |       |              |       |        |        |       |                     | 0000 0000 0000 0000 |       |                     |

| T5CON    | 0120  | TON    | _      | TSIDL                                                | —      | _      | _      |       | _     | —            | TGATE | TCKPS1 | TCKPS0 | —     | —                   | TCS                 | -     | 0000 0000 0000 0000 |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0'

Note

1:

Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## TABLE 14-1: QEI REGISTER MAP<sup>(1)</sup>

|             |       | -      |        |         |        |        |        |       |         |           |        |        |         |         |        |       |          |                     |

|-------------|-------|--------|--------|---------|--------|--------|--------|-------|---------|-----------|--------|--------|---------|---------|--------|-------|----------|---------------------|

| SFR<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8   | Bit 7     | Bit 6  | Bit 5  | Bit 4   | Bit 3   | Bit 2  | Bit 1 | Bit 0    | Reset State         |

| QEICON      | 0122  | CNTERR | _      | QEISIDL | INDX   | UPDN   | QEIM2  | QEIM1 | QEIM0   | SWPAB     | -      | TQGATE | TQCKPS1 | TQCKPS0 | POSRES | TQCS  | UPDN_SRC | 0000 0000 0000 0000 |

| DFLTCON     | 0124  |        | —      |         |        | Ι      | IMV1   | IMV0  | CEID    | QEOUT     | QECK2  | QECK1  | QECK0   | _       | _      | _     | _        | 0000 0000 0000 0000 |

| POSCNT      | 0126  |        |        |         |        |        |        |       | Positio | n Counter | <15:0> |        |         |         |        |       |          | 0000 0000 0000 0000 |

| MAXCNT      | 0128  |        |        |         |        |        |        |       | Maxim   | un Count< | :15:0> |        | _       |         |        | _     |          | 1111 1111 1111 1111 |

| ADPCFG      | 02A8  | _      | —      | _       | —      | _      | —      | _     | PCFG8   | PCFG7     | PCFG6  | PCFG5  | PCFG4   | PCFG3   | PCFG2  | PCFG1 | PCFG0    | 0000 0000 0000 0000 |

Legend: — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

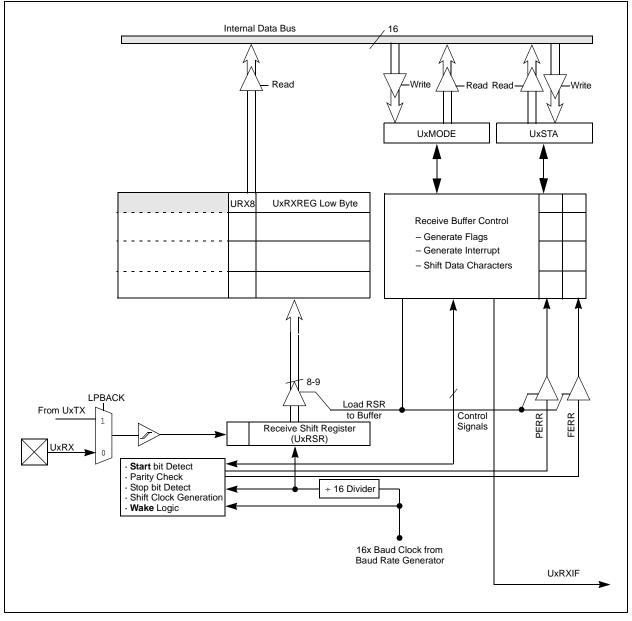

## FIGURE 18-2: UART RECEIVER BLOCK DIAGRAM

### 19.4.6.3 Receive Error Interrupts

A receive error interrupt will be indicated by the ERRIF bit. This bit shows that an error condition occurred. The source of the error can be determined by checking the bits in the CAN Interrupt Status register, C1INTF.

- Invalid message received.

- If any type of error occurred during reception of the last message, an error will be indicated by the IVRIF bit.

- Receiver overrun.

- The RXxOVR bit indicates that an overrun condition occurred.

- Receiver warning.

- The RXWAR bit indicates that the Receive Error Counter (RERRCNT<7:0>) has reached the warning limit of 96.

- Receiver error passive.

- The RXEP bit indicates that the Receive Error Counter has exceeded the error passive limit of 127 and the module has gone into error passive state.

## 19.5 Message Transmission

## 19.5.1 TRANSMIT BUFFERS

The CAN module has three transmit buffers. Each of the three buffers occupies 14 bytes of data. Eight of the bytes are the maximum 8 bytes of the transmitted message. Five bytes hold the standard and extended identifiers and other message arbitration information.

## 19.5.2 TRANSMIT MESSAGE PRIORITY

Transmit priority is a prioritization within each node of the pending transmittable messages. There are 4 levels of transmit priority. If TXPRI<1:0> (C1TXxCON<1:0>, where x = 0, 1 or 2, represents a particular transmit buffer) for a particular message buffer is set to '11', that buffer has the highest priority. If TXPRI<1:0> for a particular message buffer is set to '10' or '01', that buffer has an intermediate priority. If TXPRI<1:0> for a particular message buffer is set to '10' or '01', that buffer has an intermediate priority. If TXPRI<1:0> for a particular message buffer is '00', that buffer has the lowest priority.

## 19.5.3 TRANSMISSION SEQUENCE

To initiate transmission of the message, the TXREQ bit (C1TXxCON<3>) must be set. The CAN bus module resolves any timing conflicts between setting of the TXREQ bit and the Start-of-Frame (SOF), ensuring that if the priority was changed, it is resolved correctly before the SOF occurs. When TXREQ is set, the TXABT (C1TXxCON<6>), TXLARB (C1TXxCON<5>) and TXERR (C1TXxCON<4>) flag bits are automatically cleared.

Setting TXREQ bit simply flags a message buffer as enqueued for transmission. When the module detects an available bus, it begins transmitting the message which has been determined to have the highest priority.

If the transmission completes successfully on the first attempt, the TXREQ bit is cleared automatically and an interrupt is generated if TXxIE was set.

If the message transmission fails, one of the error condition flags will be set and the TXREQ bit will remain set, indicating that the message is still pending for transmission. If the message encountered an error condition during the transmission attempt, the TXERR bit will be set and the error condition may cause an interrupt. If the message loses arbitration during the transmission attempt, the TXLARB bit is set. No interrupt is generated to signal the loss of arbitration.

### 19.5.4 ABORTING MESSAGE TRANSMISSION

The system can also abort a message by clearing the TXREQ bit associated with each message buffer. Setting the ABAT bit (C1CTRL<12>) will request an abort of all pending messages. If the message has not yet started transmission, or if the message started but is interrupted by loss of arbitration or an error, the abort will be processed. The abort is indicated when the module sets the TXABT bit, and the TXxIF flag is not automatically set.

## 19.5.5 TRANSMISSION ERRORS

The CAN module will detect the following transmission errors:

- Acknowledge Error

- Form Error

- Bit Error

These transmission errors will not necessarily generate an interrupt but are indicated by the transmission error counter. However, each of these errors will cause the transmission error counter to be incremented by one. Once the value of the error counter exceeds the value of 96, the ERRIF (C1INTF<5>) and the TXWAR bit (C1INTF<10>) are set. Once the value of the error counter exceeds the value of 96, an interrupt is generated and the TXWAR bit in the error flag register is set.

## TABLE 20-2: ADC REGISTER MAP<sup>(1)</sup>

| ADCBUF1       0282       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |       | 1.20   |         |         |        |        |          |        |                                        |          |                      |            | -         |        |       |                     |                     |                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|--------|---------|---------|--------|--------|----------|--------|----------------------------------------|----------|----------------------|------------|-----------|--------|-------|---------------------|---------------------|---------------------|

| ADCBUF1       0282       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                               | SFR Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12 | Bit 11 | Bit 10   | Bit 9  | Bit 8                                  | Bit 7    | Bit 6                | Bit 5      | Bit 4     | Bit 3  | Bit 2 | Bit 1               | Bit 0               | Reset State         |

| ADCBUF20284ADCData Buffer 2UADC Data Buffer 3U000000uu uuu uu<br>uuuu uu<br>ADCBUF4000000uu uuu uu<br>uuuu uu<br>ADCBUF4000000uu uuu uu<br>uuuu uu<br>ADCBUF4000000uu uuu uu<br>uuuu uu<br>ADCBUF4000000uu uuuu uu<br>uuuu<br>ADCBUF4000000uu uuuu uu<br>uuuuu<br>ADCBUF4000000uu uuuu uu<br>uuuuu<br>ADCBUF40000<                                                                                                                                                       | ADCBUF0  | 0280  | _      | —       | _       | _      | —      | _        |        |                                        |          |                      | ADC Data   | Buffer 0  |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUF3       0.286       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th< td=""><td>ADCBUF1</td><td>0282</td><td>_</td><td>_</td><td>_</td><td>—</td><td>_</td><td>_</td><td></td><td></td><td></td><td></td><td>ADC Data</td><td>Buffer 1</td><td></td><td></td><td></td><td></td><td>0000 00uu uuuu uuuu</td></th<>                                                                                                                                                                                             | ADCBUF1  | 0282  | _      | _       | _       | —      | _      | _        |        |                                        |          |                      | ADC Data   | Buffer 1  |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ACCBUF4       0.28       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADCBUF2  | 0284  | Ι      |         |         | Ι      | Ι      |          |        | ADC Data Buffer 2                      |          |                      |            |           |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ACCBUFS       028       -       -       -       -       -       -       -       -       -       ACCBUFS       ADC Data Buffer 1       -       ADC Data Buffer 1       -       0000       00uu uuuu uu       ADC Dut uuuu uu       ADC Du | ADCBUF3  | 0286  |        | _       | _       | _      | -      | _        |        | ADC Data Buffer 3                      |          |                      |            |           |        |       |                     | 0000 00uu uuuu uuuu |                     |

| ADCBUFG       0.28C       -       -       -       -       -       -       -       -       ADC BUFS       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000       0.000                                                                                                                                                                                                                                           | ADCBUF4  | 0288  |        | —       | _       | -      | _      |          |        | ADC Data Buffer 4                      |          |                      |            |           |        |       |                     | 0000 00uu uuuu uuuu |                     |

| ADCBUF7       0.288       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th< td=""><td>ADCBUF5</td><td>028A</td><td> </td><td>—</td><td>_</td><td>-</td><td>_</td><td></td><td></td><td colspan="8">ADC Data Buffer 5</td><td>0000 00uu uuuu uuuu</td></th<>                                                                                                                                                                                                                                                         | ADCBUF5  | 028A  |        | —       | _       | -      | _      |          |        | ADC Data Buffer 5                      |          |                      |            |           |        |       |                     | 0000 00uu uuuu uuuu |                     |

| ADCBUFR9       0.209       -       -       -       -       -       -       -       -       ADC       -       ADC DUG       -       ADC DUG       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADCBUF6  | 028C  |        | —       | _       | -      | _      |          |        |                                        |          |                      | ADC Data   | Buffer 6  |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUF9       0292       -       -       -       -       -       -       -       -       ADCBUFA       0293       -       -       -       -       -       -       -       -       ADCBUFA       0293       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <th< td=""><td>ADCBUF7</td><td>028E</td><td> </td><td>—</td><td>_</td><td>-</td><td>_</td><td></td><td></td><td></td><td></td><td></td><td>ADC Data</td><td>Buffer 7</td><td></td><td></td><td></td><td></td><td>0000 00uu uuuu uuuu</td></th<>                                                                                                                                                                                     | ADCBUF7  | 028E  |        | —       | _       | -      | _      |          |        |                                        |          |                      | ADC Data   | Buffer 7  |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUFA       0294       -       -       -       -       -       -       -       -       ADC       -       ADC Data       -       ADC Data       -       -       0000       000u       uuuu       0000       00uu       00uu       00uu       00uu       00uu       00uu       00uu       00uu       0000       0                                                                                                                                                                                                                                                                                        | ADCBUF8  | 0290  |        | —       | _       | -      | _      |          |        |                                        |          |                      | ADC Data   | Buffer 8  |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUFB       0290              ADCBUFC       0290       0290              ADCBUFC       0290       0             ADC BUFC       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       00                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADCBUF9  | 0292  | _      | —       | _       | _      | —      | -        |        |                                        |          |                      | ADC Data   | Buffer 9  |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUFC       0298                DCBUFC       0298         000       00uu       uuuu       uuuuu       uuuu       uuuu       uuuu       uuuu       uuuu       uuuuu       uuuu       uuuu       uuuu       uuuuu                                                                                                                                                                                                                                                                                                                                                            | ADCBUFA  | 0294  | _      | —       | _       | _      | —      | -        |        |                                        |          |                      | ADC Data E | Buffer 10 |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUFD       029A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADCBUFB  | 0296  | —      | —       | —       | —      | —      | —        |        |                                        |          |                      | ADC Data E | Buffer 11 |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUFE       029C               Description       Description <thdescription< th=""> <thdescription< th=""></thdescription<></thdescription<>                                                                                   | ADCBUFC  | 0298  | —      | —       | —       | —      | —      | —        |        |                                        |          |                      | ADC Data E | Buffer 12 |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCBUFF       029E       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       0000       00                                                                                                                                                                                                                                                                                                                                                                 | ADCBUFD  | 029A  | —      | —       | —       | —      | —      | —        |        |                                        |          |                      | ADC Data E | Buffer 13 |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCON1       02A0       ADON       —       ADSIDL       —       —       FORM<1:0>       SRC<2:0>       —       SIMSAM       ASAM       SAMP       DONE       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000                                                                                                                                                                                                                                                                              | ADCBUFE  | 029C  | —      | —       | —       | —      | —      | —        |        |                                        |          |                      | ADC Data E | Buffer 14 |        |       |                     |                     | 0000 00uu uuuu uuuu |

| ADCON2       02A2       VCFG<2:>       -       -       CSCNA       CHPS-1:>       BUFS       -       SMPI-3:O>       BUFM       ALTS       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       00000       00000       00000       00000                                                                                                                                                                                                                                                                      | ADCBUFF  | 029E  | —      | —       | _       | —      | _      | —        |        |                                        | -        |                      | ADC Data E | Buffer 15 |        | -     |                     |                     | 0000 00uu uuuu uuuu |

| ADCON3       02A4          SAMC<4:0>       ADRC        ADRC        ADRCS        ADRCS       ADRCS        ADRCS       ADRCS        ADRCS       ADRCS        ADRCS       ADRCS        ADRCS       ADRCS        ADRCS       ADRCS        ADRCS       ADRCS        ADRCS        CH123NA<1:0>       CH123NA       CH02NS       CH02NS        00:0:0:0:0:0:0:0:0:0:0:0:0:0:0:0:0:0:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADCON1   | 02A0  | ADON   | —       | ADSIDL  | —      | _      | —        | FOR    | M<1:0>                                 |          | SSRC<2:0             | >          | —         | SIMSAM | ASAM  | SAMP                | DONE                | 0000 0000 0000 0000 |

| ADCHS       02A6       CH123WB       CH123SB       CH0NB       CH0SB       CH123SB       CH123SB       CH0NA       CH0SA                                                                                                                                                                                                                                 | ADCON2   | 02A2  |        | VCFG<2: | 0>      | —      | —      | CSCNA    | CHP    | CHPS<1:0> BUFS — SMPI<3:0> BUFM ALTS ( |          |                      |            |           |        |       | 0000 0000 0000 0000 |                     |                     |

| ADPCFG 02A8 PCFG8 <sup>(2)</sup> PCFG7 <sup>(2)</sup> PCFG6 <sup>(2)</sup> PCFG5 PCFG4 PCFG3 PCFG2 PCFG1 PCFG0 0000 0000 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ADCON3   | 02A4  | —      | —       | —       |        | S      | SAMC<4:0 | >      |                                        | ADRC     | —                    |            |           | ADCS<  | 5:0>  |                     |                     | 0000 0000 0000 0000 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADCHS    | 02A6  | CH123N | IB<1:0> | CH123SB | CH0NB  |        | CHOSE    | B<3:0> |                                        | CH123    | VA<1:0>              | CH123SA    | CH0NA     |        | CH0SA | <3:0>               |                     | 0000 0000 0000 0000 |

| ADCSSL 02AA CSSL8 <sup>(2)</sup> CSSL7 <sup>(2)</sup> CSSL7 <sup>(2)</sup> CSSL5 <sup>(2)</sup> CSSL4 CSSL3 CSSL2 CSSL1 CSSL0 0000 0000 0000 0000 0000 0000 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADPCFG   | 02A8  | —      | —       | _       | —      | —      | _        |        |                                        |          |                      | PCFG5      | PCFG4     | PCFG3  | PCFG2 | PCFG1               | PCFG0               | 0000 0000 0000 0000 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADCSSL   | 02AA  | _      | —       | _       | —      | —      | _        | —      | CSSL8 <sup>(2)</sup>                   | CSSL7(2) | CSSL6 <sup>(2)</sup> | CSSL5      | CSSL4     | CSSL3  | CSSL2 | CSSL1               | CSSL0               | 0000 0000 0000 0000 |

Legend:

u = uninitialized bit; — = unimplemented bit, read as '0' Refer to the "*dsPIC30F Family Reference Manual*" (DS70046) for descriptions of register bit fields. Note 1:

2: These bits are not available on dsPIC30F4012 devices.

## 21.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. When the device has this feature enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

one of four pairs of debug I/O pins may be selected by the user using configuration options in MPLAB IDE. These pin pairs are named EMUD/EMUC, EMUD1/ EMUC1, EMUD2/EMUC2 and EMUD3/EMUC3. In each case, the selected EMUD pin is the emulation/ debug data line and the EMUC pin is the emulation/ debug clock line. These pins interface to the MPLAB ICD 2 module available from Microchip. The selected pair of debug I/O pins is used by MPLAB ICD 2 to send commands and receive responses, as well as to send and receive data. To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGC, PGD and the selected EMUDx/EMUCx pin pair.

This gives rise to two possibilities:

- If EMUD/EMUC is selected as the debug I/O pin pair, then only a 5-pin interface is required as the EMUD and EMUC pin functions are multiplexed with the PGD and PGC pin functions in all dsPIC30F devices.

- If EMUD1/EMUC1, EMUD2/EMUC2 or EMUD3/ EMUC3 is selected as the debug I/O pin pair, then a 7-pin interface is required as the EMUDx/ EMUCx pin functions (x = 1, 2 or 3) are not multiplexed with the PGD and PGC pin functions.

| DC CHA       | ARACTER | RISTICS                                  | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |         |       |                                           |  |  |  |  |

|--------------|---------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------|-------|-------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol  | Characteristic                           | Min                                                                                                                                                                                      | Typ <sup>(1)</sup> | Мах     | Units | Conditions                                |  |  |  |  |

|              | VIL     | Input Low Voltage <sup>(2)</sup>         |                                                                                                                                                                                          |                    |         |       |                                           |  |  |  |  |

| DI10         |         | I/O pins:                                |                                                                                                                                                                                          |                    |         |       |                                           |  |  |  |  |

|              |         | with Schmitt Trigger buffer              | Vss                                                                                                                                                                                      | —                  | 0.2 Vdd | V     |                                           |  |  |  |  |

| DI15         |         | MCLR                                     | Vss                                                                                                                                                                                      | —                  | 0.2 Vdd | V     |                                           |  |  |  |  |

| DI16         |         | OSC1 (in XT, HS and LP modes)            | Vss                                                                                                                                                                                      | —                  | 0.2 Vdd | V     |                                           |  |  |  |  |

| DI17         |         | OSC1 (in RC mode) <sup>(3)</sup>         | Vss                                                                                                                                                                                      | —                  | 0.3 Vdd | V     |                                           |  |  |  |  |

| DI18         |         | SDA, SCL                                 | Vss                                                                                                                                                                                      | —                  | 0.3 Vdd | V     | SMBus disabled                            |  |  |  |  |

| DI19         |         | SDA, SCL                                 | Vss                                                                                                                                                                                      | —                  | 0.8     | V     | SMBus enabled                             |  |  |  |  |

|              | Vih     | Input High Voltage <sup>(2)</sup>        |                                                                                                                                                                                          |                    |         |       |                                           |  |  |  |  |

| DI20         |         | I/O pins:<br>with Schmitt Trigger buffer | 0.8 Vdd                                                                                                                                                                                  | _                  | Vdd     | V     |                                           |  |  |  |  |

| DI25         |         | MCLR                                     | 0.8 Vdd                                                                                                                                                                                  | _                  | Vdd     | V     |                                           |  |  |  |  |

| DI26         |         | OSC1 (in XT, HS and LP modes)            | 0.7 Vdd                                                                                                                                                                                  | _                  | Vdd     | V     |                                           |  |  |  |  |

| DI27         |         | OSC1 (in RC mode) <sup>(3)</sup>         | 0.9 Vdd                                                                                                                                                                                  | _                  | Vdd     | V     |                                           |  |  |  |  |

| DI28         |         | SDA, SCL                                 | 0.7 Vdd                                                                                                                                                                                  | _                  | Vdd     | V     | SMBus disabled                            |  |  |  |  |

| DI29         |         | SDA, SCL                                 | 2.1                                                                                                                                                                                      | —                  | Vdd     | V     | SMBus enabled                             |  |  |  |  |

| DI30         | ICNPU   | CNxx Pull-up Current <sup>(2)</sup>      | 50                                                                                                                                                                                       | 250                | 400     | μA    | VDD = 5V, VPIN = VSS                      |  |  |  |  |

|              | lı∟     | Input Leakage Current <sup>(2,4,5)</sup> |                                                                                                                                                                                          |                    |         |       |                                           |  |  |  |  |

| DI50         |         | I/O ports                                | —                                                                                                                                                                                        | 0.01               | ±1      | μA    | Vss ≤VPIN ≤VDD,<br>Pin at high-impedance  |  |  |  |  |

| DI51         |         | Analog input pins                        | —                                                                                                                                                                                        | 0.50               | _       | μA    | Vss ≤VPIN ≤VDD,<br>Pin at high-impedance  |  |  |  |  |

| DI55         |         | MCLR                                     | —                                                                                                                                                                                        | 0.05               | ±5      | μA    | Vss ⊴Vpin ⊴Vdd                            |  |  |  |  |

| DI56         |         | OSC1                                     | _                                                                                                                                                                                        | 0.05               | ±5      | μA    | Vss ⊴VPIN ⊴VDD,<br>XT, HS and LP Osc mode |  |  |  |  |

#### TABLE 24-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**2:** These parameters are characterized but not tested in manufacturing.

**3:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the dsPIC30F device be driven with an external clock while in RC mode.

4: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

5: Negative current is defined as current sourced by the pin.

### TABLE 24-23: TIMER2 AND TIMER4 EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | ARACTERIS                                                          | TICS                 |                      | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+85°C for Industrial-40°C ≤TA ≤+125°C for Extended |                                         |     |         |       |                               |  |  |  |

|--------------|--------------------------------------------------------------------|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|-------------------------------|--|--|--|

| Param<br>No. | Symbol                                                             | Charact              | eristic              |                                                                                                                                                        | Min                                     | Тур | Max     | Units | Conditions                    |  |  |  |

| TB10         | B10 TTXH TxCK High Time Synchr<br>no pres                          |                      |                      |                                                                                                                                                        | 0.5 Tcy + 20                            | —   | _       | ns    | Must also meet parameter TB15 |  |  |  |

|              |                                                                    |                      | Synchro<br>with pres |                                                                                                                                                        | 10                                      | —   | _       | ns    |                               |  |  |  |

| TB11         | ΤτxL                                                               | TxCK Low Time        | Synchro<br>no preso  |                                                                                                                                                        | 0.5 TCY + 20                            |     | _       | ns    | Must also meet parameter TB15 |  |  |  |

|              |                                                                    |                      | Synchro<br>with pres |                                                                                                                                                        | 10                                      | —   | —       | ns    |                               |  |  |  |

| TB15         | ΤτχΡ                                                               | TxCK Input<br>Period | Synchro<br>no preso  |                                                                                                                                                        | Tcy + 10                                | —   | —       | ns    | N = prescale<br>value         |  |  |  |

|              | Synch<br>with pr                                                   |                      |                      |                                                                                                                                                        | Greater of:<br>20 ns or<br>(TCY + 40)/N |     |         |       | (1, 8, 64, 256)               |  |  |  |

| TB20         | TB20 TCKEXTMRL Delay from External TxCK<br>Edge to Timer Increment |                      |                      | Clock                                                                                                                                                  | 0.5 TCY                                 | —   | 1.5 TCY | —     |                               |  |  |  |

#### TABLE 24-24: TIMER3 AND TIMER5 EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | ARACTERIS | TICS                                      |                      | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                         |     |         |       |                               |  |  |  |

|--------------|-----------|-------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|-------------------------------|--|--|--|

| Param<br>No. | Symbol    | Characte                                  | eristic              |                                                                                                                                                                                          | Min                                     | Тур | Max     | Units | Conditions                    |  |  |  |

| TC10         | TtxH      | TxCK High Time                            | Synchro              | nous                                                                                                                                                                                     | 0.5 TCY + 20                            |     |         | ns    | Must also meet parameter TC15 |  |  |  |

| TC11         | TtxL      | TxCK Low Time                             | Synchro              | nous                                                                                                                                                                                     | 0.5 TCY + 20                            | _   | —       | ns    | Must also meet parameter TC15 |  |  |  |

| TC15         | TtxP      | TxCK Input Period                         | Synchro<br>no preso  |                                                                                                                                                                                          | Tcy + 10                                | —   | —       | ns    | N = prescale<br>value         |  |  |  |

|              |           |                                           | Synchro<br>with pres |                                                                                                                                                                                          | Greater of:<br>20 ns or<br>(Tcy + 40)/N |     |         |       | (1, 8, 64, 256)               |  |  |  |

| TC20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre |                      | lock                                                                                                                                                                                     | 0.5 TCY                                 |     | 1.5 TCY | _     |                               |  |  |  |

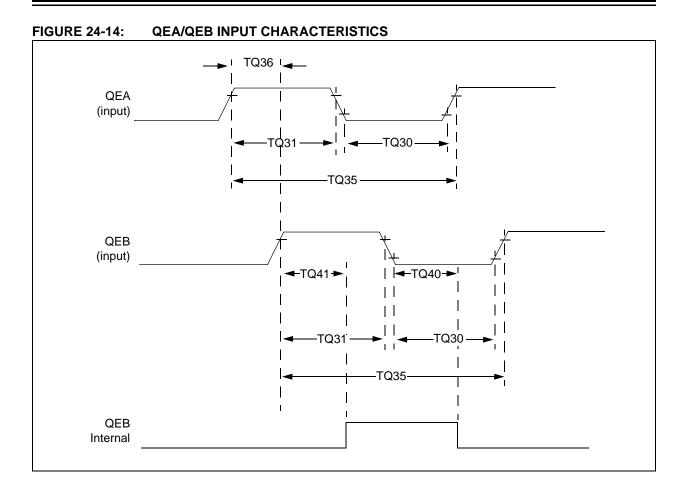

## TABLE 24-30: QUADRATURE DECODER TIMING REQUIREMENTS

| АС СНА       | ARACTER | ISTICS                                               | Standard Ope<br>(unless other<br>Operating terr | wise state | ed)<br>-40°C ≤ | 2 <b>.5V to 5.5V</b><br>ΓA ≤+85°C for Industrial<br>ΓA ≤+125°C for Extended |

|--------------|---------|------------------------------------------------------|-------------------------------------------------|------------|----------------|-----------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic <sup>(1)</sup>                        | Тур <sup>(2)</sup>                              | Max        | Units          | Conditions                                                                  |

| TQ30         | TQUL    | Quadrature Input Low Time                            | 6 Tcy                                           | —          | ns             |                                                                             |

| TQ31         | ΤουΗ    | Quadrature Input High Time                           | 6 Tcy                                           | —          | ns             |                                                                             |

| TQ35         | ΤουΙΝ   | Quadrature Input Period                              | 12 TCY                                          | —          | ns             |                                                                             |

| TQ36         | ΤουΡ    | Quadrature Phase Period                              | 3 TCY                                           | —          | ns             |                                                                             |

| TQ40         | TQUFL   | Filter Time to Recognize Low,<br>with Digital Filter | 3 * N * Tcy                                     | —          | ns             | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 2)</b>                     |

| TQ41         | TQUFH   | Filter Time to Recognize High, with Digital Filter   | 3 * N * Tcy                                     | —          | ns             | N = 1, 2, 4, 16, 32, 64, 128<br>and 256 <b>(Note 2)</b>                     |

Note 1: These parameters are characterized but not tested in manufacturing.

2: N = Index Channel Digital Filter Clock Divide Select bits. Refer to Section 16. "Quadrature Encoder Interface (QEI)" in the "dsPIC30F Family Reference Manual" (DS70046).

| AC CHARACTERISTICS |                 |                                                          | Standard Operating Conditions: 2.5V to 5.5V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |         |         |       |                               |

|--------------------|-----------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|-------------------------------|

| Param<br>No.       | Symbol          | Characteristic                                           | Min.                                                                                                                                                                                     | Тур     | Max.    | Units | Conditions                    |

| Clock P            | aramete         | rs                                                       |                                                                                                                                                                                          | •       |         |       | -                             |

| AD50               | TAD             | A/D Clock Period                                         | _                                                                                                                                                                                        | 84      | _       | ns    | See Table 20-2 <sup>(1)</sup> |