Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 30 MIPs                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 20                                                                            |

| Program Memory Size        | 48KB (16K x 24)                                                               |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 2K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 6x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f4012-30i-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

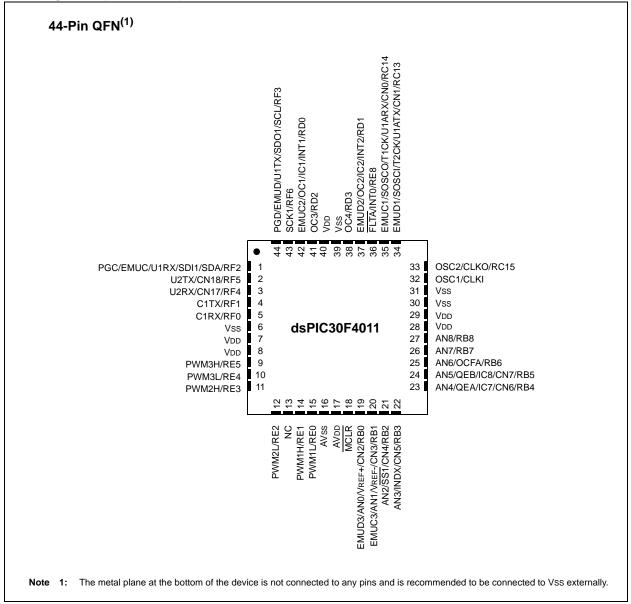

### **Pin Diagrams (Continued)**

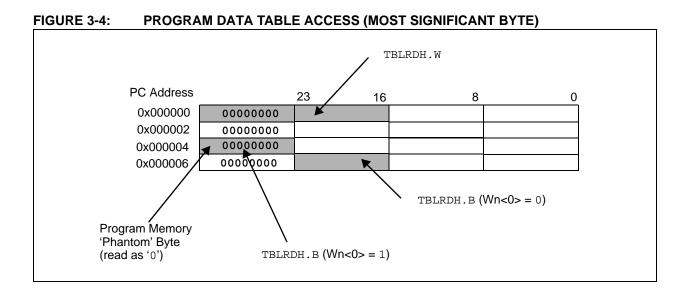

#### 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MSb of the data space EA is set and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in **Section 2.4** "**DSP Engine**".

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 3-5), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. For information on instruction encoding, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

Note that by incrementing the PC by 2 for each program memory word, the Least Significant 15 bits of data space addresses directly map to the Least Significant 15 bits in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-5.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand prefetch

- MOV instructions

- MOV.D instructions

- All other instructions require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a REPEAT loop:

- The following instances require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop allows the instruction, accessing data using PSV, to execute in a single cycle.

#### 7.2 Erasing Data EEPROM

7.2.1 ERASING A BLOCK OF DATA EEPROM

In order to erase a block of data EEPROM, the NVMADRU and NVMADR registers must initially point to the block of memory to be erased. Configure NVMCON for erasing a block of data EEPROM and set the WR and WREN bits in the NVMCON register. Setting the WR bit initiates the erase, as shown in Example 7-2.

#### EXAMPLE 7-2: DATA EEPROM BLOCK ERASE

```

; Select data EEPROM block, WR, WREN bits

MOV

#0x4045,W0

MOV

W0 NVMCON

; Initialize NVMCON SFR

; Start erase cycle by setting WR after writing key sequence

DISI

; Block all interrupts with priority < 7

#5

; for next 5 instructions

MOV

#0x55,W0

;

W0 NVMKEY

MOV

; Write the 0x55 key

#0xAA,W1

MOV

MOV

W1 NVMKEY

; Write the OxAA key

BSET

NVMCON, #WR

; Initiate erase sequence

NOP

NOP

; Erase cycle will complete in 2mS. CPU is not stalled for the Data Erase Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine erasure complete

```

#### 7.2.2 ERASING A WORD OF DATA EEPROM

The TBLPAG and NVMADR registers must point to the block. Select erase a block of data Flash and set the WR and WREN bits in the NVMCON register. Setting the WR bit initiates the erase, as shown in Example 7-3.

#### EXAMPLE 7-3: DATA EEPROM WORD ERASE

```

; Select data EEPROM word, WR, WREN bits

#0x4044,W0

MOV

MOV

W0 NVMCON

; Start erase cycle by setting WR after writing key sequence

; Block all interrupts with priority <7

DISI

#5

; for next 5 instructions

#0x55,W0

MOV

;

MOV

W0 NVMKEY

; Write the 0x55 key

MOV

#0xAA,W1

;

W1 NVMKEY

MOV

; Write the OxAA key

; Initiate erase sequence

BSET

NVMCON, #WR

NOP

NOP

; Erase cycle will complete in 2mS. CPU is not stalled for the Data Erase Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine erasure complete

```

#### 7.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

Together, the write initiate sequence and the WREN bit help prevent an accidental write during brown-out, power glitch or software malfunction.

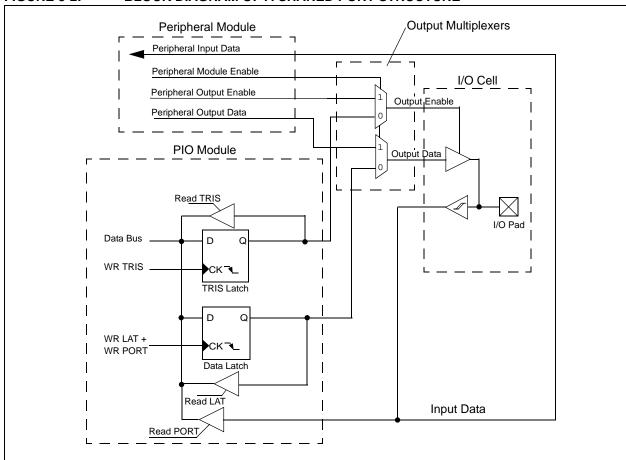

#### FIGURE 8-2: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

### 8.2 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins), may cause the input buffer to consume current that exceeds the device specifications.

#### 8.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

# EXAMPLE 8-1: PORT WRITE/READ

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8>     |

|------|------------|-----------------------------|

|      |            | ; as inputs                 |

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs |

| NOP  |            | ; Delay 1 cycle             |

| BTSS | PORTB, #13 | ; Next Instruction          |

|      |            |                             |

NOTES:

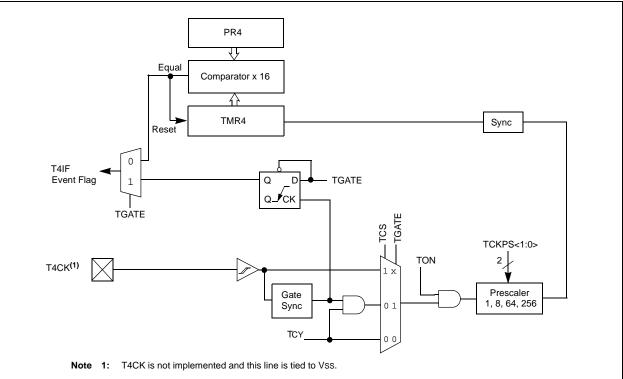

#### FIGURE 11-2: 16-BIT TIMER4 BLOCK DIAGRAM

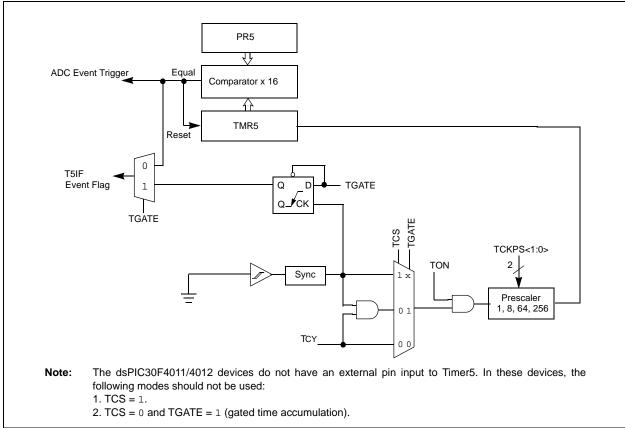

#### FIGURE 11-3: 16-BIT TIMER5 BLOCK DIAGRAM

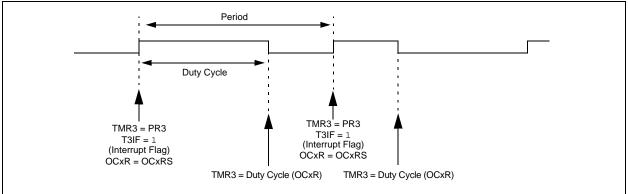

#### 13.4.2 PWM PERIOD

The PWM period is specified by writing to the PRx register. The PWM period can be calculated using Equation 13-1.

#### EQUATION 13-1: PWM PERIOD

$PWM \ period = [(PRx) + 1] \cdot 4 \cdot Tosc \cdot$  $(TMRx \ prescale \ value)$

PWM frequency is defined as 1/[PWM period].

When the selected TMRx is equal to its respective Period register, PRx, the following four events occur on the next increment cycle:

- TMRx is cleared

- The OCx pin is set

- Exception 1: If PWM duty cycle is 0x0000, the OCx pin will remain low.

- Exception 2: If duty cycle is greater than PRx, the pin will remain high.

- The PWM duty cycle is latched from OCxRS into OCxR

- The corresponding timer interrupt flag is set

See Figure 13-1 for key PWM period comparisons. Timer3 is referred to in the figure for clarity.

#### 18.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1', otherwise FERR will be set. The read-only FERR bit is buffered along with the received data; it is cleared on any Reset.

#### 18.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes; it is cleared on any Reset.

#### 18.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

#### 18.5.5 RECEIVE BREAK

The receiver will count and expect a certain number of bit times based on the values programmed in the PDSEL<1:0> (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the Break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated, if appropriate and the RIDLE bit is set.

When the module receives a long Break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the Break condition on the line is the next Start bit.

Break is regarded as a character containing all '0's, with the FERR bit set. The Break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not been received yet.

#### 18.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables this special mode in which a 9th bit (URX8) value of '1' identifies the received word as an address, rather than data. This mode is only applicable for 9-bit data communication. The URXISELx control bit does not have any impact on interrupt generation in this mode, since an interrupt (if enabled) will be generated every time the received word has the 9th bit set.

#### 18.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in **Section 18.3** "**Transmitting Data**".

#### 18.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

- BRG = 16-bit value held in UxBRG register (0 through 65535)

- FCY = Instruction Clock Rate (1/TCY)

The baud rate is given by Equation 18-1.

### EQUATION 18-1: BAUD RATE

Baud Rate = FCY/(16 \* (BRG + 1))

Therefore, maximum baud rate possible is:

FCY/16 (if BRG = 0),

and the minimum baud rate possible is:

FCY/(16 \* 65536).

With a full, 16-bit Baud Rate Generator, at 30 MIPS operation, the minimum baud rate achievable is 28.5 bps.

#### 18.9 Auto-Baud Support

To allow the system to determine baud rates of received characters, the input can be optionally linked to a selected capture input (IC1 for UART1, IC2 for UART2). To enable this mode, the user must program the input capture module to detect the falling and rising edges of the Start bit.

#### 18.10 UART Operation During CPU Sleep and Idle Modes

#### 18.10.1 UART OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shut down and stay at logic '0'. If entry into Sleep mode occurs while a transmission is in progress, then the transmission is aborted. The UxTX pin is driven to logic '1'. Similarly, if entry into Sleep mode occurs while a reception is in progress, then the reception is aborted. The UxSTA, UxMODE, UxBRG, transmit and receive registers and buffers, are not affected by Sleep mode.

If the WAKE bit (UxMODE<7>) is set before the device enters Sleep mode, then a falling edge on the UxRX pin will generate a receive interrupt. The Receive Interrupt Select Mode bit (URXISEL) has no effect for this function. If the receive interrupt is enabled, then this will wake-up the device from Sleep. The UARTEN bit must be set in order to generate a wake-up interrupt.

# 18.10.2 UART OPERATION DURING CPU IDLE MODE

For the UART, the USIDL bit selects if the module will stop operation when the device enters Idle mode, or whether the module will continue on Idle. If USIDL = 0, the module will continue operation during Idle mode. If USIDL = 1, the module will stop on Idle.

# 19.0 CAN MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the *dsPIC30F Family Reference Manual* (DS70046). For more information on the device instruction set and programming, refer to the *"16-bit MCU and DSC Reference Manual"* (DS70157).

#### 19.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or digital signal controller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC30F4011/4012 devices have 1 CAN module.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- · Support for remote frames

- Double-buffered receiver with two prioritized received message storage buffers (each buffer may contain up to 8 bytes of data)

- 6 full (standard/extended identifier), acceptance filters, 2 associated with the high priority receive buffer and 4 associated with the low priority receive buffer

- 2 full, acceptance filter masks, one each associated with the high and low priority receive buffers

- Three transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to input capture module (IC2, for both CAN1 and CAN2) for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

### 19.2 Frame Types

The CAN module transmits various types of frames which include data messages or remote transmission requests, initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

#### 19.2.1 STANDARD DATA FRAME

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit Standard Identifier (SID) but not an 18-bit Extended Identifier (EID).

#### 19.2.2 EXTENDED DATA FRAME

An extended data frame is similar to a standard data frame but includes an extended identifier as well.

#### 19.2.3 REMOTE FRAME

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

#### 19.2.4 ERROR FRAME

An error frame is generated by any node that detects a bus error. An error frame consists of 2 fields: an error flag field and an error delimiter field.

#### 19.2.5 OVERLOAD FRAME

An overload frame can be generated by a node as a result of 2 conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

#### 19.2.6 INTERFRAME SPACE

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

# 21.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap occurs. The device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

#### 21.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device exits rapidly from Reset on power-up. If the clock source is FRC, LPRC, ERC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

#### 21.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points (see Table 24-10):

- 2.6V-2.71V

- 4.1V-4.4V

- 4.58V-4.73V

**Note:** The BOR voltage trip points indicated here are nominal values provided for design guidance only.

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FOS<1:0> and FPR<3:0>). Furthermore, if an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) are applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit, if enabled, continues to operate while in Sleep or Idle modes and resets the device if VDD falls below the BOR threshold voltage.

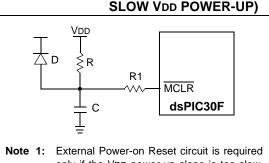

#### FIGURE 21-6: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R should be suitably chosen so as to make sure that the voltage drop across R does not violate the device's electrical specification.

- **3:** R1 should be suitably chosen so as to limit any current flowing into MCLR from external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit.

### 21.4 Watchdog Timer (WDT)

#### 21.4.1 WATCHDOG TIMER OPERATION

The primary function of the Watchdog Timer (WDT) is to reset the processor in the event of a software malfunction. The WDT is a free-running timer that runs off an on-chip RC oscillator, requiring no external component. Therefore, the WDT timer continues to operate even if the main processor clock (e.g., the crystal oscillator) fails.

#### 21.4.2 ENABLING AND DISABLING THE WDT

The Watchdog Timer can be "Enabled" or "Disabled" only through a Configuration bit (FWDTEN) in the Configuration register, FWDT.

Setting FWDTEN = 1 enables the Watchdog Timer. The enabling is done when programming the device. By default, after chip erase, FWDTEN bit = 1. Any device programmer capable of programming dsPIC30F devices allows programming of this and other Configuration bits.

If enabled, the WDT increments until it overflows or "times out". A WDT time-out forces a device Reset (except during Sleep). To prevent a WDT time-out, the user must clear the Watchdog Timer using a CLRWDT instruction.

If a WDT times out during Sleep, the device wakes-up. The WDTO bit in the RCON register is cleared to indicate a wake-up resulting from a WDT time-out.

Setting FWDTEN = 0 allows user software to enable/ disable the Watchdog Timer via the SWDTEN (RCON<5>) control bit.

### 21.5 Power-Saving Modes

There are two power-saving states that can be entered through the execution of a special instruction, PWRSAV.

These are: Sleep and Idle.

The format of the PWRSAV instruction is as follows:

PWRSAV <parameter>

where,

'parameter' defines Idle or Sleep mode.

#### 21.5.1 SLEEP MODE

In Sleep mode, the clock to the CPU and peripherals is shut down. If an on-chip oscillator is being used, it is shut down.

The Fail-Safe Clock Monitor is not functional during Sleep, since there is no clock to monitor. However, the LPRC clock remains active if WDT is operational during Sleep.

The Brown-out Reset protection circuit and the Low-Voltage Detect (LVD) circuit, if enabled, remain functional during Sleep.

The processor wakes up from Sleep if at least one of the following conditions has occurred:

- Any interrupt that is individually enabled and meets the required priority level

- Any Reset (POR, BOR and MCLR)

- WDT time-out

On waking up from Sleep mode, the processor restarts the same clock that was active prior to entry into Sleep mode. When clock switching is enabled, bits COSC<1:0> determine the oscillator source to be used on wake-up. If clock switch is disabled, then there is only one system clock.

Note: If a POR or BOR occurred, the selection of the oscillator is based on the FOS<1:0> and FPR<3:0> Configuration bits.

If the clock source is an oscillator, the clock to the device is held off until OST times out (indicating a stable oscillator). If PLL is used, the system clock is held off until LOCK = 1 (indicating that the PLL is stable). In either case, TPOR, TLOCK and TPWRT delays are applied.

If EC, FRC, LPRC or ERC oscillators are used, then a delay of TPOR (~10  $\mu s$ ) is applied. This is the smallest delay possible on wake-up from Sleep.

Moreover, if the LP oscillator was active during Sleep, and LP is the oscillator used on wake-up, then the startup delay is equal to TPOR. PWRT and OST delays are not applied. In order to have the smallest possible startup delay when waking up from Sleep, one of these faster wake-up options should be selected before entering Sleep.

#### TABLE 24-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| DC CHARACI       | FERISTICS                  |     |       | perating Co<br>emperature | -40°C ≦Ta ≤ | 5V to 5.5V (unless otherwise stated)<br>∺85°C for Industrial<br>∺125°C for Extended |  |  |

|------------------|----------------------------|-----|-------|---------------------------|-------------|-------------------------------------------------------------------------------------|--|--|

| Parameter<br>No. | Typical <sup>(1)</sup>     | Мах | Units | Conditions                |             |                                                                                     |  |  |

| Power-Down       | Current (IPD) <sup>(</sup> | 2)  |       |                           |             |                                                                                     |  |  |

| DC60a            | 0.3                        | —   | μA    | 25°C                      |             |                                                                                     |  |  |

| DC60b            | 1                          | 30  | μA    | 85°C                      | 3.3V        |                                                                                     |  |  |

| DC60c            | 12                         | 60  | μA    | 125°C                     |             | Base power-down current <sup>(3)</sup>                                              |  |  |

| DC60e            | 0.5                        | —   | μA    | 25°C                      |             | Base power-down currents ?                                                          |  |  |

| DC60f            | 2                          | 45  | μA    | 85°C                      | 5V          |                                                                                     |  |  |

| DC60g            | 17                         | 90  | μA    | 125°C                     |             |                                                                                     |  |  |

| DC61a            | 5                          | 8   | μA    | 25°C                      |             |                                                                                     |  |  |

| DC61b            | 5                          | 8   | μA    | 85°C                      | 3.3V        |                                                                                     |  |  |

| DC61c            | 6                          | 9   | μA    | 125°C                     |             | – Watchdog Timer current: ∆IwDT <sup>(3)</sup>                                      |  |  |

| DC61e            | 10                         | 15  | μΑ    | 25°C                      |             |                                                                                     |  |  |

| DC61f            | 10                         | 15  | μΑ    | 85°C                      | 5V          |                                                                                     |  |  |

| DC61g            | 11                         | 17  | μΑ    | 125°C                     |             |                                                                                     |  |  |

| DC62a            | 4                          | 10  | μΑ    | 25°C                      |             |                                                                                     |  |  |

| DC62b            | 5                          | 10  | μA    | 85°C                      | 3.3V        |                                                                                     |  |  |

| DC62c            | 4                          | 10  | μA    | 125°C                     |             | Timer1 w/32 kHz crystal: ΔΙτι32 <sup>(3)</sup>                                      |  |  |

| DC62e            | 4                          | 15  | μΑ    | 25°C                      |             |                                                                                     |  |  |

| DC62f            | 6                          | 15  | μΑ    | 85°C                      | 5V          |                                                                                     |  |  |

| DC62g            | 5                          | 15  | μA    | 125°C                     |             |                                                                                     |  |  |

| DC63a            | 32                         | 48  | μA    | 25°C                      |             |                                                                                     |  |  |

| DC63b            | 35                         | 53  | μΑ    | 85°C                      | 3.3V        |                                                                                     |  |  |

| DC63c            | 37                         | 56  | μA    | 125°C                     |             | BOR on: ∆lBOR <sup>(3)</sup>                                                        |  |  |

| DC63e            | 37                         | 56  | μA    | 25°C                      |             |                                                                                     |  |  |

| DC63f            | 41                         | 62  | μΑ    | 85°C                      | 5V          |                                                                                     |  |  |

| DC63g            | 57                         | 86  | μA    | 125°C                     | ]           |                                                                                     |  |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

### 24.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

#### TABLE 24-12: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)                                                                                                                       |  |  |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤TA ≤+85°C for Industrial<br>-40°C ≤TA ≤+125°C for Extended<br>Operating voltage VDD range as described in <b>Section 24.1 "DC</b><br><b>Characteristics</b> ". |  |  |  |  |

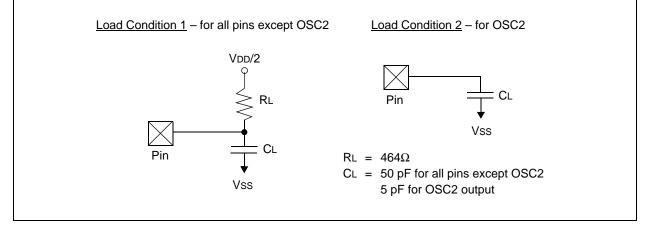

#### FIGURE 24-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

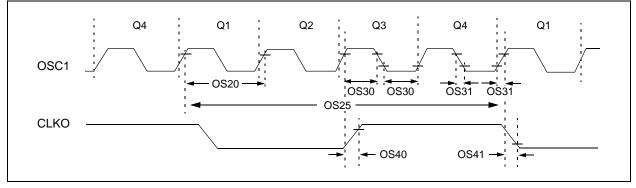

#### FIGURE 24-3: EXTERNAL CLOCK TIMING

| Clock<br>Oscillator<br>Mode | Fosc<br>(MHz) <sup>(1)</sup> | Τ <b>Ϲ</b> Υ (μsec) <sup>(2)</sup> | MIPS<br>w/o PLL <sup>(3)</sup> | MIPS<br>w/PLL x4 <sup>(3)</sup> | MIPS<br>w/PLL x8 <sup>(3)</sup> | MIPS<br>w/PLL x16 <sup>(3)</sup> |  |  |  |

|-----------------------------|------------------------------|------------------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|--|--|--|

| EC                          | 0.200                        | 20.0                               | 0.05                           | _                               | _                               |                                  |  |  |  |

|                             | 4                            | 1.0                                | 1.0                            | 4.0                             | 8.0                             | 16.0                             |  |  |  |

|                             | 10                           | 0.4                                | 2.5                            | 10.0                            | 20.0                            | —                                |  |  |  |

|                             | 25                           | 0.16                               | 6.25                           | _                               | —                               | —                                |  |  |  |

| ХТ                          | 4                            | 1.0                                | 1.0                            | 4.0                             | 8.0                             | 16.0                             |  |  |  |

|                             | 10                           | 0.4                                | 2.5                            | 10.0                            | 20.0                            | —                                |  |  |  |

TABLE 24-16: INTERNAL CLOCK TIMING EXAMPLES

**Note 1:** Assumption: Oscillator postscaler is divide by 1.

**2:** Instruction Execution Cycle Time: TCY = 1/MIPS.

3: Instruction Execution Frequency: MIPS = (Fosc \* PLLx)/4, since there are 4 Q clocks per instruction cycle.

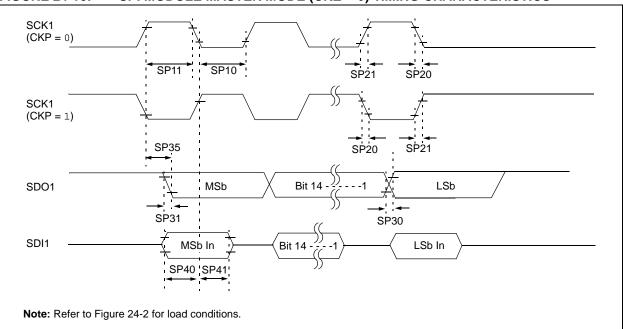

#### FIGURE 24-16: SPI MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 24-32: SPI MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                                    |                                              | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature-40°C ≤TA ≤+85°C for Industrial-40°C ≤TA ≤+125°C for Extended |                    |     |       |                    |

|--------------------|------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|

| Param<br>No.       | Symbol Characteristic <sup>1</sup> |                                              |                                                                                                                                                        | Тур <sup>(2)</sup> | Max | Units | Conditions         |

| SP10               | TscL                               | SCK1 Output Low Time <sup>(3)</sup>          | Tcy/2                                                                                                                                                  | _                  | _   | ns    |                    |

| SP11               | TscH                               | SCK1 Output High Time <sup>(3)</sup>         | TCY/2                                                                                                                                                  |                    |     | ns    |                    |

| SP20               | TscF                               | SCK1 Output Fall Time <sup>(4</sup>          | —                                                                                                                                                      | —                  | _   | ns    | See parameter DO32 |

| SP21               | TscR                               | SCK1 Output Rise Time <sup>(4)</sup>         | —                                                                                                                                                      |                    |     | ns    | See parameter DO31 |

| SP30               | TdoF                               | SDO1 Data Output Fall Time <sup>(4)</sup>    | —                                                                                                                                                      | —                  | _   | ns    | See parameter DO32 |

| SP31               | TdoR                               | SDO1 Data Output Rise<br>Time <sup>(4)</sup> | —                                                                                                                                                      | _                  | _   | ns    | See parameter DO31 |

| SP35               | TscH2doV,<br>TscL2doV              | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                                                                                                                                      | —                  | 30  | ns    |                    |

| SP40               | TdiV2scH,<br>TdiV2scL              | Setup Time of SDI1 Data Input to SCK1 Edge   | 20                                                                                                                                                     | —                  | _   | ns    |                    |

| SP41               | TscH2diL,<br>TscL2diL              | Hold Time of SDI1 Data Input to SCK1 Edge    | 20                                                                                                                                                     | —                  |     | ns    |                    |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCK1 is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPI pins.

### TABLE 24-37: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| АС СНА       | RACTERIS | STICS                    | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |              |      |       |                                             |                          |

|--------------|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------|--------------------------|

| Param<br>No. | Symbol   | Charac                   | teristic                                                                                                                                                                         | Min          | Max  | Units | Conditions                                  |                          |

| IS10         | TLO:SCL  | Clock Low Time           | 100 kHz mode                                                                                                                                                                     | 4.7          | _    | μs    | Device must operate at a minimum of 1.5 MHz |                          |

|              |          |                          | 400 kHz mode                                                                                                                                                                     | 1.3          | —    | μs    | Device must operate at a minimum of 10 MHz. |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.5          | —    | μs    |                                             |                          |

| IS11         | THI:SCL  | Clock High Time          | 100 kHz mode                                                                                                                                                                     | 4.0          | _    | μs    | Device must operate at a minimum of 1.5 MHz |                          |

|              |          |                          | 400 kHz mode                                                                                                                                                                     | 0.6          | _    | μs    | Device must operate at a minimum of 10 MHz  |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.5          |      | μs    |                                             |                          |

| IS20         | TF:SCL   | SDA and SCL              | 100 kHz mode                                                                                                                                                                     | —            | 300  | ns    | CB is specified to be from                  |                          |

|              |          | Fall Time                | 400 kHz mode                                                                                                                                                                     | 20 + 0.1 Св  | 300  | ns    | 10 to 400 pF                                |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | —            | 100  | ns    |                                             |                          |

| IS21         | TR:SCL   | SDA and SCL              | 100 kHz mode                                                                                                                                                                     | —            | 1000 | ns    | CB is specified to be from                  |                          |

|              |          | Rise Time                | 400 kHz mode                                                                                                                                                                     | 20 + 0.1 Св  | 300  | ns    | 10 to 400 pF                                |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | —            | 300  | ns    |                                             |                          |

| IS25         | TSU:DAT  | Data Input<br>Setup Time | 100 kHz mode                                                                                                                                                                     | 250          |      | ns    |                                             |                          |

|              |          |                          | 400 kHz mode                                                                                                                                                                     | 100          | —    | ns    |                                             |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 100          | —    | ns    |                                             |                          |

| IS26 THD:D/  | THD:DAT  | Data Input<br>Hold Time  | 100 kHz mode                                                                                                                                                                     | 0            | —    | ns    |                                             |                          |

|              |          |                          | 400 kHz mode                                                                                                                                                                     | 0            | 0.9  | μs    |                                             |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0            | 0.3  | μs    |                                             |                          |

| IS30         | TSU:STA  | Start Condition          | 100 kHz mode                                                                                                                                                                     | 4.7          |      | μs    | Only relevant for Repeated                  |                          |

|              |          | Setup Time               | 400 kHz mode                                                                                                                                                                     | 0.6          | _    | μs    | Start condition                             |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.25         | _    | μs    |                                             |                          |

| IS31         | THD:STA  | Start Condition          | 100 kHz mode                                                                                                                                                                     | 4.0          |      | μs    | After this period, the first                |                          |

|              |          |                          | Hold Time                                                                                                                                                                        | 400 kHz mode | 0.6  |       | μs                                          | clock pulse is generated |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.25         | —    | μs    |                                             |                          |

| IS33         | Tsu:sto  | Stop Condition           | 100 kHz mode                                                                                                                                                                     | 4.7          | —    | μs    |                                             |                          |

|              |          | Setup Time               | 400 kHz mode                                                                                                                                                                     | 0.6          | —    | μs    |                                             |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.6          |      | μs    |                                             |                          |

| IS34         | THD:STO  | Stop Condition           | 100 kHz mode                                                                                                                                                                     | 4000         | —    | ns    |                                             |                          |

|              |          | Hold Time                | 400 kHz mode                                                                                                                                                                     | 600          |      | ns    |                                             |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 250          |      | ns    |                                             |                          |

| IS40         | TAA:SCL  | Output Valid             | 100 kHz mode                                                                                                                                                                     | 0            | 3500 | ns    |                                             |                          |

|              |          | From Clock               | 400 kHz mode                                                                                                                                                                     | 0            | 1000 | ns    |                                             |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0            | 350  | ns    |                                             |                          |

| IS45         | TBF:SDA  | Bus Free Time            | 100 kHz mode                                                                                                                                                                     | 4.7          | —    | μs    | Time the bus must be free                   |                          |

|              |          |                          | 400 kHz mode                                                                                                                                                                     | 1.3          |      | μs    | before a new transmission                   |                          |

|              |          |                          | 1 MHz mode <sup>(1)</sup>                                                                                                                                                        | 0.5          |      | μs    | can start                                   |                          |

| IS50         | Св       | Bus Capacitive Lo        | ading                                                                                                                                                                            |              | 400  | pF    |                                             |                          |

**Note 1:** Maximum pin capacitance = 10 pF for all I<sup>2</sup>C pins (for 1 MHz mode only).

# APPENDIX A: REVISION HISTORY

## Revision D (August 2006)

Previous versions of this data sheet contained Advance or Preliminary Information. They were distributed with incomplete characterization data.

This revision reflects these changes:

- Revised I<sup>2</sup>C Slave Addresses (see Table 17-1)

- Updated Section 20.0 "10-bit, High-Speed Analog-to-Digital Converter (ADC) Module" to more fully describe configuration guidelines

- Base Instruction CP1 removed from instruction set (see Table 22-2)

- Revised Electrical Characteristics:

- Operating Current (IDD) Specifications (seeTable 24-5)

- Idle Current (IIDLE) Specifications (see Table 24-6)

- Power-Down Current (IPD) Specifications (see Table 24-7)

- I/O Pin Input Specifications (see Table 24-8)

- BOR Voltage Limits (see Table 24-11)

- Watchdog Timer Time-out Limits (see Table 24-21)

### Revision E (January 2007)

- This revision includes updates to the packaging diagrams.

#### **Revision F (March 2008)**

This revision reflects these updates:

- Added Note 1 to 32-bit Timer4/5 Block Diagram (see Figure 11-1) and 16-bit Timer4/5 Block Diagram (see Figure 11-2)

- Changed the location of the input reference in the 10-bit High-Speed ADC Functional Block Diagram (see Figure 20-1)

- Added FUSE Configuration Register (FICD) details (see Section 21.6 "Device Configuration Registers" and Table 21-8)

- Removed erroneous statement regarding generation of CAN receive errors (see Section 19.4.5 "Receive Errors")

- Electrical Specifications:

- Resolved TBD values for parameters DO10, DO16, DO20, and DO26 (see Table 24-9)

- 10-bit High-Speed ADC tPDU timing parameter (time to stabilize) has been updated from 20 µs typical to 20 µs maximum (see Table 24-40)

- Parameter OS65 (Internal RC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 24-18)

- Parameter DC12 (RAM Data Retention Voltage) has been updated to include a Min value (see Table 24-4)

- Parameter D134 (Erase/Write Cycle Time) has been updated to include Min and Max values and the Typ value has been removed (see Table 24-11)

- Removed parameters OS62 (Internal FRC Jitter) and OS64 (Internal FRC Drift) and Note 2 from AC Characteristics (see Table 24-17)

- Parameter OS63 (Internal FRC Accuracy) has been expanded to reflect multiple Min and Max values for different temperatures (see Table 24-17)

- Updated Min and Max values and Conditions for parameter SY11 and updated Min, Typ, and Max values and Conditions for parameter SY20 (see Table 24-20)

- Corrected erroneous device number (see "Product Identification System")

- Additional minor corrections throughout the document

# INDEX

| Numerics                                                  |  |  |  |  |  |  |

|-----------------------------------------------------------|--|--|--|--|--|--|

| 10-Bit, High-Speed Analog-to-Digital Converter (ADC) Mod- |  |  |  |  |  |  |

| ule                                                       |  |  |  |  |  |  |

| 16-bit Up/Down Position Counter Mode90                    |  |  |  |  |  |  |

| Count Direction Status90                                  |  |  |  |  |  |  |

| Counter Reset90                                           |  |  |  |  |  |  |

| Error Checking90                                          |  |  |  |  |  |  |

| Α                                                         |  |  |  |  |  |  |

| AC Characteristics                                        |  |  |  |  |  |  |

| Load Conditions                                           |  |  |  |  |  |  |

| Temperature and Voltage Specifications                    |  |  |  |  |  |  |

| ADC                                                       |  |  |  |  |  |  |

| 1 Msps Configuration Guideline142                         |  |  |  |  |  |  |

| 600 ksps Configuration Guideline 143                      |  |  |  |  |  |  |

| 750 ksps Configuration Guideline 143                      |  |  |  |  |  |  |

| Aborting a Conversion140                                  |  |  |  |  |  |  |

| Acquisition Requirements144                               |  |  |  |  |  |  |

| ADCHS 137                                                 |  |  |  |  |  |  |

| ADCON1                                                    |  |  |  |  |  |  |

| ADCON2                                                    |  |  |  |  |  |  |

| ADCON3                                                    |  |  |  |  |  |  |

| ADCSSL                                                    |  |  |  |  |  |  |

| ADPCFG                                                    |  |  |  |  |  |  |

| Configuring Analog Port Pins                              |  |  |  |  |  |  |

| Connection Considerations                                 |  |  |  |  |  |  |

| Conversion Operation                                      |  |  |  |  |  |  |

| Conversion Speeds                                         |  |  |  |  |  |  |

| Effects of a Reset                                        |  |  |  |  |  |  |

| Operation During CPU Idle Mode                            |  |  |  |  |  |  |

| Operation During CPU Sleep Mode                           |  |  |  |  |  |  |

| Output Formats                                            |  |  |  |  |  |  |

| Power-Down Modes                                          |  |  |  |  |  |  |

| Programming the Start of Conversion Trigger               |  |  |  |  |  |  |

| Register Map                                              |  |  |  |  |  |  |

| Result Buffer                                             |  |  |  |  |  |  |

| Selecting the Conversion Clock                            |  |  |  |  |  |  |

| Selecting the Conversion Sequence                         |  |  |  |  |  |  |

| Voltage Reference Schematic                               |  |  |  |  |  |  |

| Address Generator Units                                   |  |  |  |  |  |  |

| Alternate 16-bit Timer/Counter                            |  |  |  |  |  |  |

| Alternate Interrupt Vector Table                          |  |  |  |  |  |  |

| Assembler                                                 |  |  |  |  |  |  |

| MPASM Assembler172                                        |  |  |  |  |  |  |

### В

| Barrel Shifter                  |     |

|---------------------------------|-----|

| Bit-Reversed Addressing         |     |

| Example                         |     |

| Implementation                  |     |

| Modifier Values (table)         |     |

| Sequence Table (16-Entry)       |     |

| Block Diagrams                  |     |

| 10-Bit, High-Speed ADC          |     |

| 16-bit Timer1 Module            |     |

| 16-bit Timer4                   | 76  |

| 16-bit Timer5                   |     |

| 32-bit Timer4/5                 | 75  |

| ADC Analog Input Model          | 144 |

| CAN Buffers and Protocol Engine | 128 |

| Dedicated Port Structure        |     |

| DSP Engine                      | 21  |

| -                               |     |

| dsPIC30F4011                    |     |

|---------------------------------|-----|

| dsPIC30F4012                    | 11  |

| External Power-on Reset Circuit | 157 |

| I <sup>2</sup> C                | 112 |

| Input Capture Mode              |     |

| Oscillator System               |     |

| Output Compare Mode             |     |

| PWM Module                      |     |

| Quadrature Encoder Interface    |     |

| Reset System                    |     |

| Shared Port Structure           |     |

| SPI                             |     |

| SPI Master/Slave Connection     |     |

| UART Receiver                   |     |

| UART Transmitter                |     |

| BOR. See Brown-out Reset.       |     |

| Brown-out Reset                 |     |

| Characteristics                 | 182 |

| CHARACIEUSUCS                   | 10/ |

### С

| C Compilers                          |     |

|--------------------------------------|-----|

| MPLAB C18                            | 172 |

| CAN Module                           | 127 |

| Baud Rate Setting                    | 132 |

| CAN1 Register Map                    | 134 |

| Frame Types                          |     |

| Message Reception                    | 130 |

| Message Transmission                 | 131 |

| Modes of Operation                   | 129 |

| Overview                             | 127 |

| Center-Aligned PWM                   | 99  |

| Code Examples                        |     |

| Data EEPROM Block Erase              | 56  |

| Data EEPROM Block Write              | 58  |

| Data EEPROM Read                     | 55  |

| Data EEPROM Word Erase               | 56  |

| Data EEPROM Word Write               | 57  |

| Erasing a Row of Program Memory      | 51  |

| Initiating a Programming Sequence    | 52  |

| Loading Write Latches                | 52  |

| Port Write/Read                      | 60  |

| Code Protection                      | 149 |

| Complementary PWM Operation          | 100 |

| Configuring Analog Port Pins         | 60  |

| Core Overview                        | 17  |

| Core Register Map                    |     |

| Customer Change Notification Service | 235 |

| Customer Notification Service        | 235 |

| Customer Support                     | 235 |

|                                      |     |

# D

| Data Access from Program Memory              |      |

|----------------------------------------------|------|

| Using Program Space Visibility               | . 28 |

| Data Accumulators and Adder/Subtracter       | . 22 |

| Data Space Write Saturation                  | . 24 |

| Overflow and Saturation                      | . 22 |

| Round Logic                                  | . 23 |

| Write-Back                                   | . 23 |

| Data Address Space                           | . 29 |

| Alignment                                    | . 32 |

| Alignment (Figure)                           |      |

| Data Spaces                                  | . 32 |

| Effect of Invalid Memory Accesses            | . 32 |

| MCU and DSP (MAC Class) Instructions Example |      |

|                                              |      |