Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFL

| Product StatusObsoleteCore ProcessorC166SV2Core Size16/32-BitSpeed80MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPripheralsVS, POR, PWM, WDTNumber of I/O40Program Memory Size576KB (576K × 8)Program Memory TypeFLASHEERPOM Size-NufszeS0 × 8Voltage Supply (Vcc/Vd)3V ~ 5.5VDataConvertersAID 9x10bOperating Temperature40° < ~ 85°C (TA)Mounting TypeSufface MountProcessor64-OFPSupplier Persters64-OFPSupplier Device Package96-OFP-64-13Purchase URLMtsv:-exfl.com/product-detin/infino-technologies/c236a72f80/afs/usit | Details                    |                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------|

| Core Size16/32-BitSpeed80MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O40Program Memory Size576KB (576K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPNumber of Low Per Add State MountNorthing TypeNert Add State MountPackage / Case64-LQFP                                                         | Product Status             | Obsolete                                                                         |

| Speed80MHzConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O40Program Memory Size576KB (576K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackageNot the the the the the the the the the th                                                                                                 | Core Processor             | C166SV2                                                                          |

| ConnectivityCANbus, EBI/EMI, I²C, LINbus, SPI, SSC, UART/USART, USIPeripheralsI²S, POR, PWM, WDTNumber of I/O40Program Memory Size576KB (576K x 8)Program Memory TypeFLASHEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                         | Core Size                  | 16/32-Bit                                                                        |

| PeripheralsPS, POR, PWM, WDTNumber of I/O40Program Memory Size576KB (576K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                       | Speed                      | 80MHz                                                                            |

| Number of I/O40Program Memory Size576KB (576K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type64-LQFPSupplier Device Package9c-LQFP-64-13                                                                                                                                                                                                                                                                   | Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Program Memory Size576KB (576K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting Type64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                  | Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Program Memory TypeFLASHEEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                          | Number of I/O              | 40                                                                               |

| EEPROM Size-RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                                                  | Program Memory Size        | 576KB (576K x 8)                                                                 |

| RAM Size50K x 8Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                                                              | Program Memory Type        | FLASH                                                                            |

| Voltage - Supply (Vcc/Vdd)3V ~ 5.5VData ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                             | EEPROM Size                | -                                                                                |

| Data ConvertersA/D 9x10bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                                                                | RAM Size                   | 50K x 8                                                                          |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                                                                                        | Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device PackagePG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                                                                                                               | Data Converters            | A/D 9x10b                                                                        |

| Mounting Type     Surface Mount       Package / Case     64-LQFP       Supplier Device Package     PG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                                                                                                                        | Oscillator Type            | Internal                                                                         |

| Package / Case     64-LQFP       Supplier Device Package     PG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Supplier Device Package PG-LQFP-64-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mounting Type              | Surface Mount                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Package / Case             | 64-LQFP                                                                          |

| Purchase URL https://www.e-xfl.com/product-detail/infineon-technologies/xc2336a72f80laafxuma1                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Supplier Device Package    | PG-LQFP-64-13                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2336a72f80laafxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

# **Table of Contents**

| Summary of Features         Basic Device Types         Special Device Types         Definition of Feature Variants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 9<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General Device Information           Pin Configuration and Definition           Identification Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Functional Description         Memory Subsystem and Organization         Central Processing Unit (CPU)         Memory Protection Unit (MPU)         Memory Checker Module (MCHK)         Interrupt System         On-Chip Debug Support (OCDS)         Capture/Compare Unit (CAPCOM2)         Capture/Compare Units CCU6x         General Purpose Timer (GPT12E) Unit         Real Time Clock         A/D Converters         Universal Serial Interface Channel Modules (USIC)         MultiCAN Module         System Timer         Watchdog Timer         Clock Generation         Parallel Ports         Instruction Set Summary | 28<br>31<br>33<br>34<br>35<br>36<br>39<br>41<br>45<br>47<br>48<br>50<br>51<br>52<br>52<br>53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Electrical Parameters<br>General Parameters<br>Absolut Maximum Rating Conditions<br>Operating Conditions<br>Pad Timing Definition<br>Parameter Interpretation<br>DC Parameters<br>DC Parameters<br>DC Parameters for Lower Voltage Area<br>Power Consumption<br>Analog/Digital Converter Parameters<br>System Parameters                                                                                                                                                                                                                                                                                                           | 57<br>57<br>58<br>60<br>60<br>61<br>63<br>65<br>67<br>72<br>76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Special Device Types         Definition of Feature Variants         General Device Information         Pin Configuration and Definition         Identification Registers         Functional Description         Memory Subsystem and Organization         Central Processing Unit (CPU)         Memory Protection Unit (MPU)         Memory Checker Module (MCHK)         Interrupt System         On-Chip Debug Support (OCDS)         Capture/Compare Unit (CAPCOM2)         Capture/Compare Units CCU6x         General Purpose Timer (GPT12E) Unit         Real Time Clock         A/D Converters         Universal Serial Interface Channel Modules (USIC)         MultiCAN Module         System Timer         Watchdog Timer         Clock Generation         Parallel Ports         Instruction Set Summary         Electrical Parameters         Absolut Maximum Rating Conditions         Operating Conditions         Parameter Interpretation         DC Parameters         DC Parameters |

## **General Device Information**

# 2 General Device Information

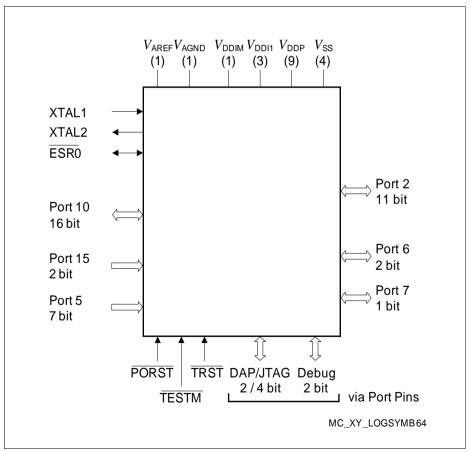

The XC233xA series (16/32-Bit Single-Chip Microcontroller with 32-Bit Performance) is a part of the Infineon XC2000 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

Figure 2 XC233xA Logic Symbol

# **General Device Information**

| Pin | Symbol            | Ctrl.  | Туре | Function                                       |

|-----|-------------------|--------|------|------------------------------------------------|

| 7   | P6.0              | O0 / I | DA/A | Bit 0 of Port 6, General Purpose Input/Output  |

|     | EMUX0             | O1     | DA/A | External Analog MUX Control Output 0 (ADC0)    |

|     | BRKOUT            | O3     | DA/A | OCDS Break Signal Output                       |

|     | ADCx_REQG<br>TyG  | I      | DA/A | External Request Gate Input for ADC0/1         |

|     | U1C1_DX0E         | I      | DA/A | USIC1 Channel 1 Shift Data Input               |

| 8   | P6.1              | O0 / I | DA/A | Bit 1 of Port 6, General Purpose Input/Output  |

|     | EMUX1             | O1     | DA/A | External Analog MUX Control Output 1 (ADC0)    |

|     | T3OUT             | O2     | DA/A | GPT12E Timer T3 Toggle Latch Output            |

|     | U1C1_DOUT         | O3     | DA/A | USIC1 Channel 1 Shift Data Output              |

|     | ADCx_REQT<br>RyE  | 1      | DA/A | External Request Trigger Input for ADC0/1      |

|     | ESR1_6            | I      | DA/A | ESR1 Trigger Input 6                           |

| 10  | P15.0             | I      | In/A | Bit 0 of Port 15, General Purpose Input        |

|     | ADC1_CH0          | I      | In/A | Analog Input Channel 0 for ADC1                |

| 11  | P15.4             | I      | In/A | Bit 4 of Port 15, General Purpose Input        |

|     | ADC1_CH4          | I      | In/A | Analog Input Channel 4 for ADC1                |

|     | T6INA             | I      | In/A | GPT12E Timer T6 Count/Gate Input               |

| 12  | V <sub>AREF</sub> | -      | PS/A | Reference Voltage for A/D Converters ADC0/1    |

| 13  | V <sub>AGND</sub> | -      | PS/A | Reference Ground for A/D Converters ADC0/1     |

| 14  | P5.0              | I      | In/A | Bit 0 of Port 5, General Purpose Input         |

|     | ADC0_CH0          | I      | In/A | Analog Input Channel 0 for ADC0                |

| 15  | P5.2              | I      | In/A | Bit 2 of Port 5, General Purpose Input         |

|     | ADC0_CH2          | I      | In/A | Analog Input Channel 2 for ADC0                |

|     | TDI_A             | I      | In/A | JTAG Test Data Input                           |

| 19  | P5.4              | I      | In/A | Bit 4 of Port 5, General Purpose Input         |

|     | ADC0_CH4          | I      | In/A | Analog Input Channel 4 for ADC0                |

|     | T3EUDA            | I      | In/A | GPT12E Timer T3 External Up/Down Control Input |

|     | TMS_A             | 1      | In/A | JTAG Test Mode Selection Input                 |

# 3 Functional Description

The architecture of the XC233xA combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources (see **Figure 4**). This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC233xA.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC233xA.

Figure 4 Block Diagram

**8 Kbytes of on-chip Stand-By SRAM (SBRAM)** provide storage for system-relevant user data that must be preserved while the major part of the device is powered down. The SBRAM is accessed via a specific interface and is powered in domain M.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word-wide registers which are used to control and monitor functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC2000 Family. In order to ensure upward compatibility they should either not be accessed or written with zeros.

**The on-chip Flash memory** stores code, constant data, and control data. The on-chip Flash memory consists of 1 module of 64 Kbytes (preferably for data storage) and modules with a maximum capacity of 256 Kbytes each. Each module is organized in sectors of 4 Kbytes.

The uppermost 4-Kbyte sector of segment 0 (located in Flash module 0) is used internally to store operation control parameters and protection information.

Note: The actual size of the Flash memory depends on the chosen device type.

Each sector can be separately write protected<sup>1)</sup>, erased and programmed (in blocks of 128 Bytes). The complete Flash area can be read-protected. A user-defined password sequence temporarily unlocks protected areas. The Flash modules combine 128-bit read access with protected and efficient writing algorithms for programming and erasing. Dynamic error correction provides extremely high read data security for all read access operations. Access to different Flash modules can be executed in parallel. For Flash parameters, please see Section 4.5.

## **Memory Content Protection**

The contents of on-chip memories can be protected against soft errors (induced e.g. by radiation) by activating the parity mechanism or the Error Correction Code (ECC).

The parity mechanism can detect a single-bit error and prevent the software from using incorrect data or executing incorrect instructions.

The ECC mechanism can detect and automatically correct single-bit errors. This supports the stable operation of the system.

It is strongly recommended to activate the ECC mechanism wherever possible because this dramatically increases the robustness of an application against such soft errors.

To save control bits, sectors are clustered for protection purposes, they remain separate for programming/erasing.

# 3.5 Interrupt System

The architecture of the XC233xA supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Where in a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed, just one cycle is 'stolen' from the current CPU activity to perform a PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XC233xA has eight PEC channels, each whith fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XC233xA can react quickly to the occurrence of non-deterministic events.

#### Interrupt Nodes and Source Selection

The interrupt system provides 96 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

## External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

## Trap Processing

The XC233xA provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Depending on the package option up to 3 External Service Request (ESR) pins are provided. The ESR unit processes their input values and allows to implement user controlled trap functions (System Requests SR0 and SR1). In this way reset, wakeup and power control can be efficiently realized.

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number. Alternatively to emulate an interrupt by software a program can trigger interrupt requests by writing the Interrupt Request (IR) bit of an interrupt control register.

# 3.6 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XC233xA provides a broad range of debug and emulation features. User software running on the XC233xA can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This either consists of the 2-pin Device Access Port (DAP) or of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (DAP or JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing data can be obtained via the debug interface, or via the external bus interface for increased performance.

Tracing of program execution is supported by the XC2000 Family emulation device.

The DAP interface uses two interface signals, the JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

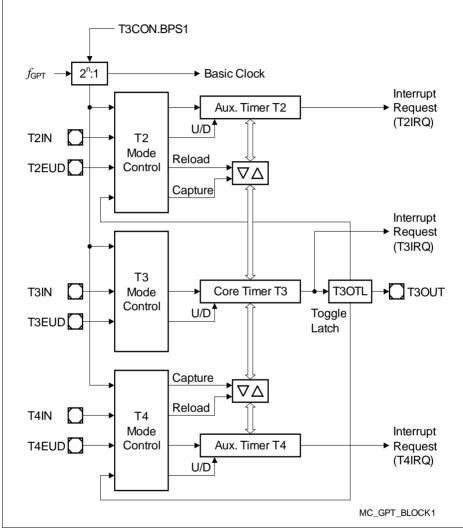

Figure 8 Block Diagram of GPT1

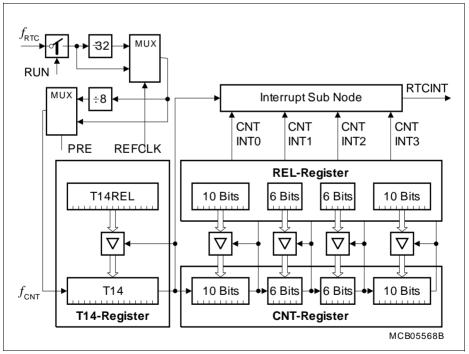

# 3.10 Real Time Clock

The Real Time Clock (RTC) module of the XC233xA can be clocked with a clock signal selected from internal sources or external sources (pins).

The RTC basically consists of a chain of divider blocks:

- Selectable 32:1 and 8:1 dividers (on off)

- The reloadable 16-bit timer T14

- The 32-bit RTC timer block (accessible via registers RTCH and RTCL) consisting of: – a reloadable 10-bit timer

- a reloadable 6-bit timer

- a reloadable 6-bit timer

- a reloadable 10-bit timer

All timers count up. Each timer can generate an interrupt request. All requests are combined to a common node request.

# Figure 10 RTC Block Diagram

Note: The registers associated with the RTC are only affected by a power reset.

# 3.11 A/D Converters

For analog signal measurement, up to two 10-bit A/D converters (ADC0, ADC1) with 7 + 2 multiplexed input channels and a sample and hold circuit have been integrated onchip. 2 inputs can be converted by both A/D converters. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements. Both modules can be synchronized to allow parallel sampling of two input channels.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XC233xA support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

## **Target Protocols**

Each USIC channel can receive and transmit data frames with a selectable data word width from 1 to 16 bits in each of the following protocols:

- UART (asynchronous serial channel)

- module capability: maximum baud rate =  $f_{SYS}$  / 4

- data frame length programmable from 1 to 63 bits

- MSB or LSB first

- LIN Support (Local Interconnect Network)

- module capability: maximum baud rate =  $f_{SYS}$  / 16

- checksum generation under software control

- baud rate detection possible by built-in capture event of baud rate generator

- SSC/SPI (synchronous serial channel with or without data buffer)

- module capability: maximum baud rate =  $f_{SYS}$  / 2, limited by loop delay

- number of data bits programmable from 1 to 63, more with explicit stop condition

- MSB or LSB first

- optional control of slave select signals

- IIC (Inter-IC Bus)

- supports baud rates of 100 kbit/s and 400 kbit/s

- IIS (Inter-IC Sound Bus)

- module capability: maximum baud rate =  $f_{SYS}$  / 2

- Note: Depending on the selected functions (such as digital filters, input synchronization stages, sample point adjustment, etc.), the maximum achievable baud rate can be limited. Please note that there may be additional delays, such as internal or external propagation delays and driver delays (e.g. for collision detection in UART mode, for IIC, etc.).

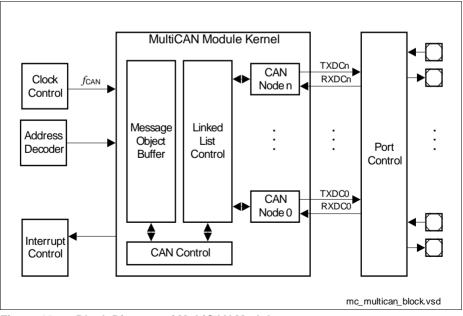

# 3.13 MultiCAN Module

The MultiCAN module contains independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

All CAN nodes share a common set of message objects. Each message object can be individually allocated to one of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

Note: The number of CAN nodes and message objects depends on the selected device type.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 12 Block Diagram of MultiCAN Module

# 4.1.3 Pad Timing Definition

If not otherwise noted, all timing parameters are tested and are valid for the corresponding output pins operating in strong driver, fast edge mode. See also "Pad Properties" on Page 89.

## 4.1.4 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XC233xA and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

**CC** (Controller Characteristics):

The logic of the XC233xA provides signals with the specified characteristics.

#### SR (System Requirement):

The external system must provide signals with the specified characteristics to the XC233xA.

# 4.2 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC233xA are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.6.4**.

## Supply Voltage Restrictions

The XC233xA can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

During power-on sequences, the supply voltages may only change with a maximum speed of dV/dt < 5 V/ $\mu$ s, i.e. the target supply voltage may be reached earliest after approx. 1  $\mu$ s.

Note: To limit the speed of supply voltage changes, the employment of external buffer capacitors at pins  $V_{DDPA}/V_{DDPB}$  is recommended.

# 4.2.1 DC Parameters

Keeping signal levels within the limits specified in this table ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{\text{OV}}$ .

Note: Operating Conditions apply.

Table 14 is valid under the following conditions:

$V_{\text{DDP}} \ge 4.5 \text{ V}; V_{\text{DDPtvp}} = 5 \text{ V}; V_{\text{DDP}} \le 5.5 \text{ V}$

| Parameter                                                                                            | Symbol                   |                                   | Values | 5                                 | Unit | Note /                                                                                             |

|------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------|--------|-----------------------------------|------|----------------------------------------------------------------------------------------------------|

|                                                                                                      |                          | Min. Typ. M                       |        | Max.                              |      | Test Condition                                                                                     |

| Pin capacitance (digital<br>inputs/outputs). To be<br>doubled for double bond<br>pins. <sup>1)</sup> | C <sub>IO</sub> CC       | -                                 | -      | 10                                | pF   | not subject to production test                                                                     |

| Input Hysteresis <sup>2)</sup>                                                                       | HYS CC                   | 0.11  x<br>$V_{\text{DDP}}$       | _      | -                                 | V    | $R_{\rm S} = 0$ Ohm                                                                                |

| Absolute input leakage current on pins of analog ports <sup>3)</sup>                                 | I <sub>OZ1</sub>  <br>CC | -                                 | 10     | 200                               | nA   | $V_{\rm IN}$ > 0 V;<br>$V_{\rm IN}$ < $V_{\rm DDP}$                                                |

| Absolute input leakage<br>current for all other pins.<br>To be doubled for double                    | I <sub>OZ2</sub>  <br>CC | -                                 | 0.2    | 5                                 | μA   | $T_{\rm J} \leq 110 ~^{\circ}{\rm C};$<br>$V_{\rm IN} < V_{\rm DDP};$<br>$V_{\rm IN} > V_{\rm SS}$ |

| bond pins. <sup>3)1)4)</sup>                                                                         |                          | -                                 | 0.2    | 15                                | μΑ   | $T_{ m J} \leq$ 150 °C;<br>$V_{ m IN} < V_{ m DDP};$<br>$V_{ m IN} > V_{ m SS}$                    |

| Pull Level Force Current <sup>5)</sup>                                                               | $ I_{PLF} $ SR           | 250                               | -      | -                                 | μA   | 6)                                                                                                 |

| Pull Level Keep Current <sup>7)</sup>                                                                | I <sub>PLK</sub>  <br>SR | -                                 | -      | 30                                | μA   | 6)                                                                                                 |

| Input high voltage<br>(all except XTAL1)                                                             | $V_{\rm IH}{\rm SR}$     | $0.7 	ext{ x}$<br>$V_{	ext{DDP}}$ | -      | V <sub>DDP</sub><br>+ 0.3         | V    |                                                                                                    |

| Input low voltage<br>(all except XTAL1)                                                              | $V_{\rm IL}{ m SR}$      | -0.3                              | -      | $0.3 	ext{ x}$<br>$V_{	ext{DDP}}$ | V    |                                                                                                    |

| Output High voltage <sup>8)</sup>                                                                    | V <sub>OH</sub> CC       | V <sub>DDP</sub><br>- 1.0         | _      | -                                 | V    | $I_{\rm OH} \ge I_{\rm OHmax}$                                                                     |

|                                                                                                      |                          | V <sub>DDP</sub><br>- 0.4         | _      | -                                 | V    | $I_{\rm OH} \ge I_{\rm OHnom}^{9)}$                                                                |

# Table 14 DC Characteristics for Upper Voltage Range

# XC2336A XC2000 Family / Base Line

## **Electrical Parameters**

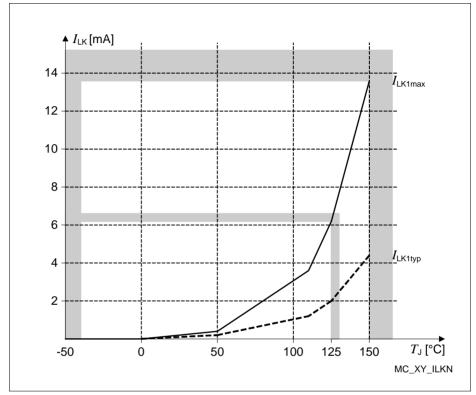

Figure 15 Leakage Supply Current as a Function of Temperature

# 4.6.3 External Clock Input Parameters

These parameters specify the external clock generation for the XC233xA. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2

- By supplying an external clock signal

- This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain)

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . If connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

Note: Operating Conditions apply.

| Parameter                                      | Symbol                  |                                    | Values | 5    | Unit | Note /<br>Test Condition                   |

|------------------------------------------------|-------------------------|------------------------------------|--------|------|------|--------------------------------------------|

|                                                |                         | Min.                               | Тур.   | Max. |      |                                            |

| Oscillator frequency                           | $f_{\rm OSC}{\rm SR}$   | 4                                  | -      | 40   | MHz  | Input = clock<br>signal                    |

|                                                |                         | 4                                  | -      | 16   | MHz  | Input = crystal<br>or ceramic<br>resonator |

| XTAL1 input current absolute value             | I <sub>IL</sub>   CC    | -                                  | -      | 20   | μA   |                                            |

| Input clock high time                          | t <sub>1</sub> SR       | 6                                  | -      | -    | ns   |                                            |

| Input clock low time                           | $t_2$ SR                | 6                                  | -      | -    | ns   |                                            |

| Input clock rise time                          | $t_3$ SR                | -                                  | -      | 8    | ns   |                                            |

| Input clock fall time                          | $t_4$ SR                | -                                  | -      | 8    | ns   |                                            |

| Input voltage amplitude on XTAL1 <sup>1)</sup> | $V_{\rm AX1}  {\rm SR}$ | $0.3 	ext{ x}$<br>$V_{	ext{DDIM}}$ | -      | -    | V    | 4 to 16 MHz                                |

|                                                |                         | $0.4 	ext{ x}$<br>$V_{	ext{DDIM}}$ | -      | -    | V    | 16 to 25 MHz                               |

|                                                |                         | $0.5 	ext{ x}$<br>$V_{	ext{DDIM}}$ | -      | -    | V    | 25 to 40 MHz                               |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}$ SR        | -1.7 +<br>V <sub>DDIM</sub>        | -      | 1.7  | V    | 2)                                         |

Table 25 External Clock Input Characteristics

Table 27 is valid under the following conditions:

$V_{\text{DDP}} \ge 3.0 \text{ V}; V_{\text{DDPtyp}} = 3.3 \text{ V}; V_{\text{DDP}} \le 4.5 \text{ V}; C_{\text{L}} \ge 20 \text{ pF}; C_{\text{L}} \le 100 \text{ pF};$

| Table 27         Standard Pad Parameters for Lower Voltage Range |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| Parameter                              | Symbol             | Values |      |                                          | Unit | Note /                        |

|----------------------------------------|--------------------|--------|------|------------------------------------------|------|-------------------------------|

|                                        |                    | Min.   | Тур. | Max.                                     | 1    | Test Condition                |

| Maximum output driver                  | I <sub>Omax</sub>  | -      | -    | 10                                       | mA   | Strong driver                 |

| current (absolute value) <sup>1)</sup> | CC                 | _      | -    | 2.5                                      | mA   | Medium driver                 |

|                                        |                    | -      | -    | 0.5                                      | mA   | Weak driver                   |

| Nominal output driver                  | I <sub>Onom</sub>  | -      | -    | 2.5                                      | mA   | Strong driver                 |

| current (absolute value)               | CC                 | _      | -    | 1.0                                      | mA   | Medium driver                 |

|                                        |                    | -      | -    | 0.1                                      | mA   | Weak driver                   |

| Rise and Fall times (10% -<br>90%)     | t <sub>RF</sub> CC | -      | -    | 6.2 +<br>0.24 x<br><i>C</i> <sub>L</sub> | ns   | Strong driver;<br>Sharp edge  |

|                                        |                    | -      | -    | 24 +<br>0.3 x<br><i>C</i> <sub>L</sub>   | ns   | Strong driver;<br>Medium edge |

|                                        |                    | -      | -    | 34 +<br>0.3 x<br>C <sub>L</sub>          | ns   | Strong driver;<br>Slow edge   |

|                                        |                    | -      | -    | 37 +<br>0.65 x<br><i>C</i> <sub>L</sub>  | ns   | Medium driver                 |

|                                        |                    | -      | -    | 500 +<br>2.5 x<br><i>C</i> <sub>L</sub>  | ns   | Weak driver                   |

The total output current that may be drawn at a given time must be limited to protect the supply rails from damage. For any group of 16 neighboring output pins, the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

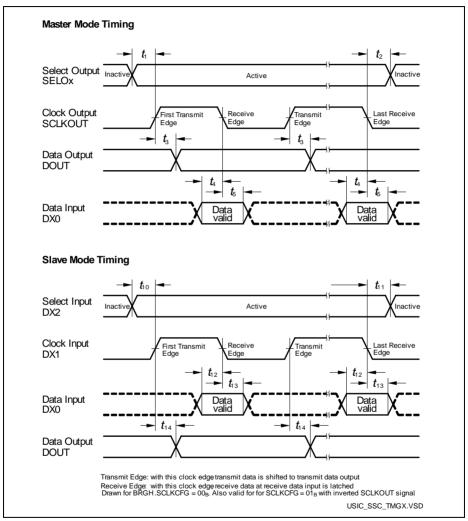

## Table 31 USIC SSC Slave Mode Timing for Lower Voltage Range

|                                                                                   |                           | •      |      |      | 0    | 0              |

|-----------------------------------------------------------------------------------|---------------------------|--------|------|------|------|----------------|

| Parameter                                                                         | Symbol                    | Values |      |      | Unit | Note /         |

|                                                                                   |                           | Min.   | Тур. | Max. | 1    | Test Condition |

| Select input DX2 setup to first clock input DX1 transmit edge <sup>1)</sup>       | <i>t</i> <sub>10</sub> SR | 7      | -    | -    | ns   |                |

| Select input DX2 hold after<br>last clock input DX1<br>receive edge <sup>1)</sup> | <i>t</i> <sub>11</sub> SR | 7      | -    | -    | ns   |                |

| Receive data input setup<br>time to shift clock receive<br>edge <sup>1)</sup>     | <i>t</i> <sub>12</sub> SR | 7      | -    | -    | ns   |                |

| Data input DX0 hold time<br>from clock input DX1<br>receive edge <sup>1)</sup>    | <i>t</i> <sub>13</sub> SR | 5      | -    | _    | ns   |                |

| Data output DOUT valid time                                                       | <i>t</i> <sub>14</sub> CC | 8      | -    | 41   | ns   |                |

1) These input timings are valid for asynchronous input signal handling of slave select input, shift clock input, and receive data input (bits DXnCR.DSEN = 0).

Figure 22 USIC - SSC Master/Slave Mode Timing

Note: This timing diagram shows a standard configuration where the slave select signal is low-active and the serial clock signal is not shifted and not inverted.