Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |  |

|----------------------------|----------------------------------------------------------------------|--|

| Product Status             | Active                                                               |  |

| Core Processor             | STM8                                                                 |  |

| Core Size                  | 8-Bit                                                                |  |

| Speed                      | 24MHz                                                                |  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                      |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                |  |

| Number of I/O              | 38                                                                   |  |

| Program Memory Size        | 64KB (64K x 8)                                                       |  |

| Program Memory Type        | FLASH                                                                |  |

| EEPROM Size                | 1.5K x 8                                                             |  |

| RAM Size                   | 6K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                         |  |

| Data Converters            | A/D 10x10b                                                           |  |

| Oscillator Type            | Internal                                                             |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |  |

| Mounting Type              | Surface Mount                                                        |  |

| Package / Case             | 48-LQFP                                                              |  |

| Supplier Device Package    | -                                                                    |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207c8t6 |  |

## **Contents**

| 1 | Intro | Introduction 9                                            |    |  |  |  |  |

|---|-------|-----------------------------------------------------------|----|--|--|--|--|

| 2 | Desc  | cription                                                  | 10 |  |  |  |  |

| 3 | Bloc  | k diagram                                                 | 12 |  |  |  |  |

| 4 | Prod  | luct overview                                             | 13 |  |  |  |  |

|   | 4.1   | Central processing unit STM8                              | 13 |  |  |  |  |

|   | 4.2   | Single wire interface module (SWIM) and debug module (DM) | 14 |  |  |  |  |

|   | 4.3   | Interrupt controller                                      | 14 |  |  |  |  |

|   | 4.4   | Flash program and data EEPROM memory                      | 14 |  |  |  |  |

|   | 4.5   | Clock controller                                          | 16 |  |  |  |  |

|   | 4.6   | Power management                                          | 17 |  |  |  |  |

|   | 4.7   | Watchdog timers                                           | 17 |  |  |  |  |

|   | 4.8   | Auto wakeup counter                                       | 18 |  |  |  |  |

|   | 4.9   | Beeper                                                    | 18 |  |  |  |  |

|   | 4.10  | TIM1 - 16-bit advanced control timer                      | 18 |  |  |  |  |

|   | 4.11  | TIM2, TIM3 - 16-bit general purpose timers                | 18 |  |  |  |  |

|   | 4.12  | TIM4 - 8-bit basic timer                                  | 19 |  |  |  |  |

|   | 4.13  | Analog-to-digital converter (ADC2)                        | 19 |  |  |  |  |

|   | 4.14  | Communication interfaces                                  | 19 |  |  |  |  |

|   |       | 4.14.1 UART1                                              | 20 |  |  |  |  |

|   |       | 4.14.2 UART3                                              | 20 |  |  |  |  |

|   |       | 4.14.3 SPI                                                | 21 |  |  |  |  |

|   |       | 4.14.4 I <sup>2</sup> C                                   | 22 |  |  |  |  |

|   |       | 4.14.5 beCAN                                              | 22 |  |  |  |  |

| 5 | Pino  | uts and pin description                                   | 23 |  |  |  |  |

|   | 5.1   | Package pinouts                                           | 23 |  |  |  |  |

|   | 5.2   | Alternate function remapping                              | 32 |  |  |  |  |

| 6 | Mem   | ory and register map                                      | 34 |  |  |  |  |

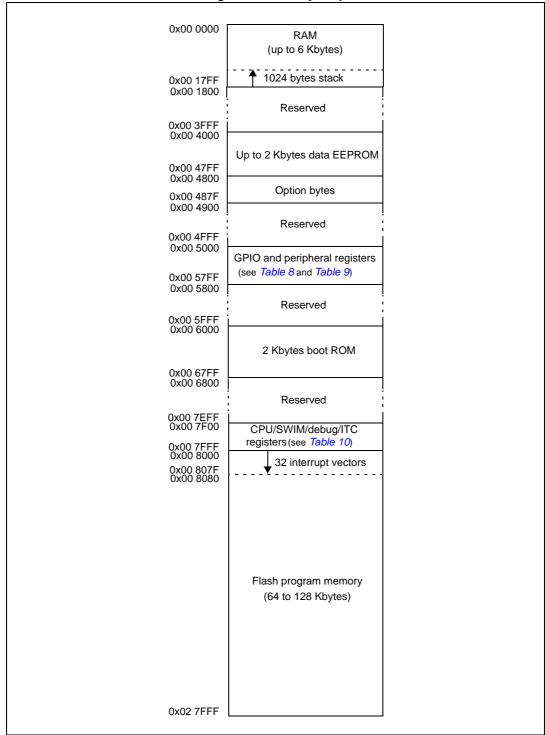

|   | 6.1   | Memory map                                                | 34 |  |  |  |  |

# List of figures

| Figure 1.                | STM8S20xxx block diagram                                                        | 12  |

|--------------------------|---------------------------------------------------------------------------------|-----|

| Figure 2.                | Flash memory organization                                                       |     |

| Figure 3.                | LQFP 80-pin pinout                                                              |     |

| Figure 4.                | LQFP 64-pin pinout                                                              |     |

| Figure 5.                | LQFP 48-pin pinout                                                              |     |

| Figure 6.                | LQFP 44-pin pinout                                                              |     |

| Figure 7.                | LQFP 32-pin pinout                                                              |     |

| Figure 8.                | Memory map                                                                      |     |

| Figure 9.                | Supply current measurement conditions                                           |     |

| Figure 10.               | Pin loading conditions                                                          |     |

| Figure 11.               | Pin input voltage                                                               |     |

| Figure 12.               | f <sub>CPUmax</sub> versus V <sub>DD</sub>                                      |     |

| Figure 13.               | External capacitor C <sub>FXT</sub>                                             | 57  |

| Figure 14.               | Typ. $I_{DD(RUN)}$ vs $V_{DD}$ , HSI RC osc, $f_{CPU} = 16$ MHz                 |     |

| Figure 15.               | Typ. $I_{DD(WFI)}$ vs $V_{DD}$ , HSI RC osc, $f_{CPU} = 16$ MHz                 |     |

| Figure 16.               | HSE external clock source                                                       |     |

| Figure 17.               | HSE oscillator circuit diagram                                                  |     |

| Figure 18.               | Typical HSI frequency variation vs V <sub>DD</sub> at 4 temperatures            |     |

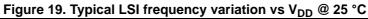

| Figure 19.               | Typical LSI frequency variation vs V <sub>DD</sub> @ 25 °C                      |     |

| Figure 20.               | Typical V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 4 temperatures |     |

| Figure 21.               | Typical pull-up resistance vs V <sub>DD</sub> @ 4 temperatures                  |     |

| Figure 22.               | Typical pull-up current vs V <sub>DD</sub> @ 4 temperatures                     |     |

| Figure 23.               | Typ. $V_{OL}$ @ $V_{DD} = 5$ V (standard ports)                                 |     |

| Figure 24.               | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (standard ports)                               |     |

| Figure 25.               | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (true open drain ports)                          |     |

| Figure 26.               | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (true open drain ports)                        |     |

| Figure 27.               | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (high sink ports)                                |     |

| Figure 28.               | Typ. $V_{OL}$ @ $V_{DD} = 3.3$ V (high sink ports)                              |     |

| Figure 29.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5 V$ (standard ports)                          |     |

| Figure 30.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (standard ports)}$                |     |

| Figure 31.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5 V$ (standard ports)                          |     |

| Figure 31.               | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (high sink ports)                   |     |

| Figure 33.               | Typical NRST $V_{II}$ and $V_{IH}$ vs $V_{DD}$ @ 4 temperatures                 |     |

| Figure 34.               | Typical NRST pull-up resistance vs V <sub>DD</sub> @ 4 temperatures             |     |

| Figure 35.               | Typical NRST pull-up current vs V <sub>DD</sub> @ 4 temperatures                |     |

| Figure 36.               | Recommended reset pin protection                                                |     |

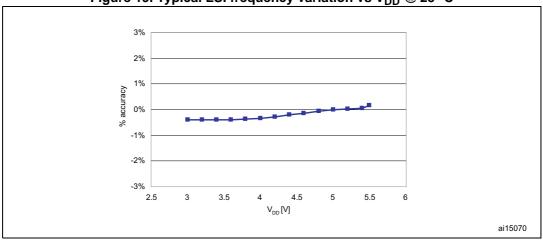

| Figure 30. Figure 37.    | SPI timing diagram - slave mode and CPHA = 0                                    |     |

| -                        | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                     | 01  |

| Figure 38.<br>Figure 39. | SPI timing diagram - master mode and GPHA = 1\(\frac{1}{2}\)                    | ا ٥ |

| •                        | Typical application with I <sup>2</sup> C bus and timing diagram                | 0   |

| Figure 40.               | ADC accuracy characteristics                                                    |     |

| Figure 41.               | •                                                                               |     |

| Figure 42.               | Typical application with ADC                                                    |     |

| Figure 43.               | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline               |     |

| Figure 44.               | LQFP80 recommended footprint                                                    | 93  |

| Figure 45.               | LQFP80 marking example (package top view)                                       |     |

| Figure 46.               | LQFP64 - 64-pin 14 mm x 14 mm low-profile quad flat package outline             |     |

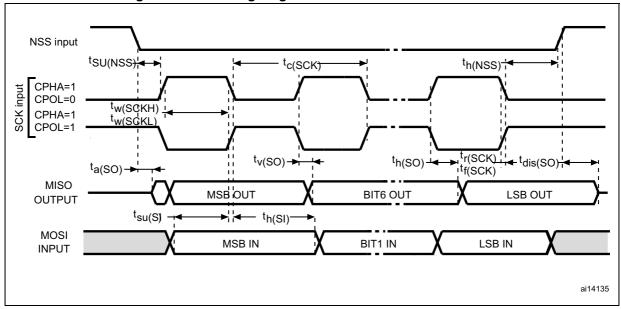

| Figure 47.               | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline               |     |

| Figure 48.               | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint         | 97  |

### 1 Introduction

This datasheet contains the description of the STM8S20xxx features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S microcontroller family reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

## 2 Description

The STM8S20xxx performance line 8-bit microcontrollers offer from 32 to 128 Kbytes Flash program memory. They are referred to as high-density devices in the STM8S microcontroller family reference manual.

All STM8S20xxx devices provide the following benefits: reduced system cost, performance robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, watchdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8S family thanks to their advanced core which is made in a state-of-the art technology for applications with 2.95 V to 5.5 V operating supply.

577

#### 4.5 Clock controller

The clock controller distributes the system clock (f<sub>MASTER)</sub> coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

#### **Features**

- Clock prescaler: To get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- Master clock sources: Four different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE)

- Up to 24 MHz high-speed user-external clock (HSE user-ext)

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- **Startup clock**: After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

- Configurable main clock output (CCO): This outputs an external clock for use by the application.

Table 3. Peripheral clock gating bit assignments in CLK PCKENR1/2 registers

| Bit     | Peripheral clock |

|---------|------------------|---------|------------------|---------|------------------|---------|------------------|

| PCKEN17 | TIM1             | PCKEN13 | UART3            | PCKEN27 | beCAN            | PCKEN23 | ADC              |

| PCKEN16 | TIM3             | PCKEN12 | UART1            | PCKEN26 | Reserved         | PCKEN22 | AWU              |

| PCKEN15 | TIM2             | PCKEN11 | SPI              | PCKEN25 | Reserved         | PCKEN21 | Reserved         |

| PCKEN14 | TIM4             | PCKEN10 | I <sup>2</sup> C | PCKEN24 | Reserved         | PCKEN20 | Reserved         |

#### 4.12 TIM4 - 8-bit basic timer

• 8-bit autoreload, adjustable prescaler ratio to any power of 2 from 1 to 128

• Clock source: CPU clock

• Interrupt source: 1 x overflow/update

Table 4. TIM timer features

| Timer | Counter<br>size<br>(bits) | Prescaler                      | Counting<br>mode | CAPCOM channels | Complem. outputs | Ext.<br>trigger | Timer<br>synchr-<br>onization/<br>chaining |

|-------|---------------------------|--------------------------------|------------------|-----------------|------------------|-----------------|--------------------------------------------|

| TIM1  | 16                        | Any integer from 1 to 65536    | Up/down          | 4               | 3                | Yes             |                                            |

| TIM2  | 16                        | Any power of 2 from 1 to 32768 | Up               | 3               | 0                | No              | No                                         |

| TIM3  | 16                        | Any power of 2 from 1 to 32768 | Up               | 2               | 0                | No              | INU                                        |

| TIM4  | 8                         | Any power of 2 from 1 to 128   | Up               | 0               | 0                | No              |                                            |

## 4.13 Analog-to-digital converter (ADC2)

STM8S20xxx performance line products contain a 10-bit successive approximation A/D converter (ADC2) with up to 16 multiplexed input channels and the following main features:

- Input voltage range: 0 to V<sub>DDA</sub>

- Dedicated voltage reference (VREF) pins available on 80 and 64-pin devices

- Conversion time: 14 clock cycles

- Single and continuous modes

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

#### 4.14 Communication interfaces

The following communication interfaces are implemented:

- UART1: Full feature UART, SPI emulation, LIN2.1 master capability, Smartcard mode, IrDA mode, single wire mode.

- UART3: Full feature UART, LIN2.1 master/slave capability

- SPI: Full and half-duplex, 10 Mbit/s

- I<sup>2</sup>C: Up to 400 Kbit/s

- beCAN (rev. 2.0A,B) 3 Tx mailboxes up to 1 Mbit/s

## 6 Memory and register map

## 6.1 Memory map

Figure 8. Memory map

Table 13. Option byte description

| Option buts no  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| ОРТ0            | ROP[7:0] Memory readout protection (ROP)  0xAA: Enable readout protection (write access via SWIM protocol)  Note: Refer to the family reference manual (RM0016) section on Flash/EEPROM memory readout protection for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OPT1            | UBC[7:0] User boot code area  0x00: no UBC, no write-protection 0x01: Pages 0 to 1 defined as UBC, memory write-protected 0x02: Pages 0 to 3 defined as UBC, memory write-protected 0x03: Pages 0 to 4 defined as UBC, memory write-protected  0xFE: Pages 0 to 255 defined as UBC, memory write-protected 0xFF: Reserved Note: Refer to the family reference manual (RM0016) section on Flash/EEPROM write protection for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| OPT2            | AFR7 Alternate function remapping option 7  0: Port D4 alternate function = TIM2_CH1  1: Port D4 alternate function = BEEP  AFR6 Alternate function remapping option 6  0: Port B5 alternate function = AIN5, port B4 alternate function = AIN4  1: Port B5 alternate function = I²C_SDA, port B4 alternate function = I²C_SCL  AFR5 Alternate function remapping option 5  0: Port B3 alternate function = AIN3, port B2 alternate function = AIN2, port B1 alternate function = AIN1, port B0 alternate function = AIN0  1: Port B3 alternate function = TIM1_ETR, port B2 alternate function = TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate function = TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate function = TIM1_CH1N  AFR4 Alternate function remapping option 4  0: Port D7 alternate function = TIM1_CH4  AFR3 Alternate function remapping option 3  0: Port D0 alternate function = TIM3_CH2  1: Port D0 alternate function = TIM3_CH2  1: Port D0 alternate function = TIM3_CH2  1: Port D0 alternate function = CLK_CCO  Note: AFR2 option has priority over AFR3 if both are activated  AFR1 Alternate function remapping option 1  0: Port A3 alternate function = TIM2_CH3, port D2 alternate function TIM3_CH1  1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH3  AFR0 Alternate function remapping option 0  0: Port D3 alternate function = TIM2_CH2  1: Port D3 alternate function = ADC_ETR |  |  |  |  |

Table 13. Option byte description (continued)

| Option byte no. | Description                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | LSI_EN: Low speed internal clock enable  0: LSI clock is not available as CPU clock source  1: LSI clock is available as CPU clock source                                                                                                |

| 0.77            | IWDG_HW: Independent watchdog  0: IWDG Independent watchdog activated by software  1: IWDG Independent watchdog activated by hardware                                                                                                    |

| OPT3            | <ul><li>WWDG_HW: Window watchdog activation</li><li>0: WWDG window watchdog activated by software</li><li>1: WWDG window watchdog activated by hardware</li></ul>                                                                        |

|                 | WWDG_HALT: Window watchdog reset on halt  0: No reset generated on halt if WWDG active  1: Reset generated on halt if WWDG active                                                                                                        |

|                 | EXTCLK: External clock selection  0: External crystal connected to OSCIN/OSCOUT  1: External clock signal on OSCIN                                                                                                                       |

| ОРТ4            | CKAWUSEL: Auto wakeup unit/clock  0: LSI clock source selected for AWU  1: HSE clock with prescaler selected as clock source for AWU                                                                                                     |

|                 | PRSC[1:0] AWU clock prescaler 00: 24 MHz to 128 kHz prescaler 01: 16 MHz to 128 kHz prescaler 10: 8 MHz to 128 kHz prescaler 11: 4 MHz to 128 kHz prescaler                                                                              |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time This configures the stabilization time. 0x00: 2048 HSE cycles 0xB4: 128 HSE cycles 0xD2: 8 HSE cycles 0xE1: 0.5 HSE cycles                                                        |

| OPT6            | Reserved                                                                                                                                                                                                                                 |

| ОРТ7            | WAITSTATE Wait state configuration  This option configures the number of wait states inserted when reading from the Flash/data EEPROM memory.  1 wait state is required if f <sub>CPU</sub> > 16 MHz.  0: No wait state  1: 1 wait state |

### Total current consumption in wait mode

Table 22. Total current consumption in wait mode at  $V_{DD}$  = 5 V

| Symbol               | Parameter            | Condit                                                      | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------------------|----------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.4                |      |    |

|                      |                      | T <sub>A</sub> ≤ 105 °C                                     | HSE user ext. clock (24 MHz)          | 1.8                | 4.7  |    |

| I <sub>DD(WFI)</sub> | Supply               | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 2.0                |      |    |

|                      |                      |                                                             | HSE user ext. clock (16 MHz)          | 1.4                | 4.4  | -  |

|                      | current in wait mode |                                                             | HSI RC osc. (16 MHz)                  | 1.2                | 1.6  | mA |

|                      | f<br>k               | $f_{CPU} = f_{MASTER}/128 = 125 \text{ kHz}$                | HSI RC osc. (16 MHz)                  | 1.0                |      |    |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55               |      |    |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.5                |      |    |

<sup>1.</sup> Data based on characterization results, not tested in production.

Table 23. Total current consumption in wait mode at  $V_{DD} = 3.3 \text{ V}$

| Symbol               | Parameter  | Condit                                                      | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------------------|------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.0                |      |    |

|                      |            | $T_A \leq 105  ^{\circ}C$                                   | HSE user ext. clock (24 MHz)          | 1.8                | 4.7  |    |

|                      |            |                                                             | HSE crystal osc. (16 MHz)             | 1.6                |      |    |

| Cum                  | Supply     | $f_{CPU} = f_{MASTER} = 16 \text{ MHz}$                     | HSE user ext. clock (16 MHz)          | 1.4                | 4.4  |    |

| I <sub>DD(WFI)</sub> | current in |                                                             | HSI RC osc. (16 MHz)                  | 1.2                | 1.6  | mA |

|                      | wait mode  | $f_{CPU} = f_{MASTER}/128 = 125 \text{ kHz}$                | HSI RC osc. (16 MHz)                  | 1.0                |      |    |

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55               |      |    |

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | LSI RC osc. (128 kHz)                 | 0.5                |      |    |

<sup>1.</sup> Data based on characterization results, not tested in production.

<sup>2.</sup> Default clock configuration measured with all peripherals off.

<sup>2.</sup> Default clock configuration measured with all peripherals off.

## Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\mbox{\scriptsize DD}}$  and  $T_{\mbox{\scriptsize A}}.$

Table 34. LSI oscillator characteristics

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        |            | 110 | 128 | 146              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       |            |     |     | 7 <sup>(1)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator power consumption |            |     | 5   |                  | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production.

## 10.3.6 I/O port pin characteristics

#### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

Table 37. I/O static characteristics

| Symbol                          | Parameter                                      | Conditions                                      | Min                   | Тур | Max                     | Unit |

|---------------------------------|------------------------------------------------|-------------------------------------------------|-----------------------|-----|-------------------------|------|

| V <sub>IL</sub>                 | Input low level voltage                        |                                                 | -0.3                  |     | 0.3 x V <sub>DD</sub>   | V    |

| V <sub>IH</sub>                 | Input high level voltage                       | V <sub>DD</sub> = 5 V                           | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                      |                                                 |                       | 700 |                         | mV   |

| R <sub>pu</sub>                 | Pull-up resistor                               | $V_{DD} = 5 \text{ V}, V_{IN} = V_{SS}$         | 30                    | 55  | 80                      | kΩ   |

|                                 | Rise and fall time (10% - 90%)                 | Fast I/Os<br>Load = 50 pF                       |                       |     | 20 <sup>(2)</sup>       |      |

|                                 |                                                | Standard and high sink I/Os<br>Load = 50 pF     |                       |     | 125 <sup>(2)</sup>      | 20   |

| t <sub>R</sub> , t <sub>F</sub> |                                                | Fast I/Os<br>Load = 20 pF                       |                       |     | 35 <sup>(3)</sup>       | ns   |

|                                 |                                                | Standard and high sink I/Os<br>Load = 20 pF     |                       |     | 125 <sup>(3)</sup>      |      |

| I <sub>lkg</sub>                | Input leakage current, analog and digital      | $V_{SS} \le V_{IN} \le V_{DD}$                  |                       |     | ±1                      | μΑ   |

| I <sub>Ikg ana</sub>            | Analog input leakage current                   | V <sub>SS</sub> V <sub>IN</sub> V <sub>DD</sub> |                       |     | ±250 <sup>(2)</sup>     | nA   |

| I <sub>lkg(inj)</sub>           | Leakage current in adjacent I/O <sup>(2)</sup> | Injection current ±4 mA                         |                       |     | ±1 <sup>(2)</sup>       | μА   |

<sup>1.</sup> Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

<sup>2.</sup> Data based on characterization results, not tested in production.

<sup>3.</sup> Guaranteed by design.

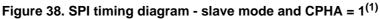

### 10.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

**Table 42. SPI characteristics**

| Symbol                                               | Parameter                    | Conditions                      | Min                      | Max                      | Unit   |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|--------|

| f <sub>SCK</sub>                                     | SDI alaak fraguanay          | Master mode                     | 0                        | 10                       | MHz    |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency          | Slave mode                      | 0                        | 6                        | IVITIZ |

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time | Capacitive load: C = 30 pF      |                          | 25                       |        |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  |                          |        |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                | Slave mode                      | 70                       |                          |        |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |        |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time        | Master mode                     | 5                        |                          |        |

| t <sub>su(SI)</sub> <sup>(1)</sup>                   | Data input setup time        | Slave mode                      | 5                        |                          |        |

| t <sub>h(MI)</sub> (1)                               | Data input hold time         | Master mode                     | 7                        |                          | ns     |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     | Data input hold time         | Slave mode                      | 10                       |                          |        |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time      | Slave mode                      |                          | 3 x t <sub>MASTER</sub>  |        |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time     | Slave mode                      | 25                       |                          |        |

| t <sub>v(SO)</sub> (1)                               | Data output valid time       | Slave mode (after enable edge)  |                          | 75                       |        |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time       | Master mode (after enable edge) |                          | 30                       |        |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data autaut hald time        | Slave mode (after enable edge)  | 31                       |                          |        |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master mode (after enable edge) | 12                       |                          |        |

<sup>1.</sup> Values based on design simulation and/or characterization results, and not tested in production.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

Figure 37. SPI timing diagram - slave mode and CPHA = 0

<sup>1.</sup> Measurement points are done at CMOS levels: 0.3  $\rm V_{DD}$  and 0.7  $\rm V_{DD.}$

Table 52. LQFP64 - 64-pin, 14 x 14 mm low-profile quad flat package mechanical data (continued)

| Symbol | mm    |       |       | inches <sup>(1)</sup> |       |        |

|--------|-------|-------|-------|-----------------------|-------|--------|

|        | Min   | Тур   | Max   | Min                   | Тур   | Max    |

| k      | 0.0 ° | 3.5 ° | 7.0 ° | 0.0 °                 | 3.5 ° | 7.0 °  |

| ccc    |       |       | 0.100 |                       |       | 0.0039 |

<sup>1.</sup> Values in inches are converted from mm and rounded to four decimal places.

Figure 47. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data

| Symbol | mm    |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------|-------|-----------------------|--------|--------|

|        | Min   | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -     | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |

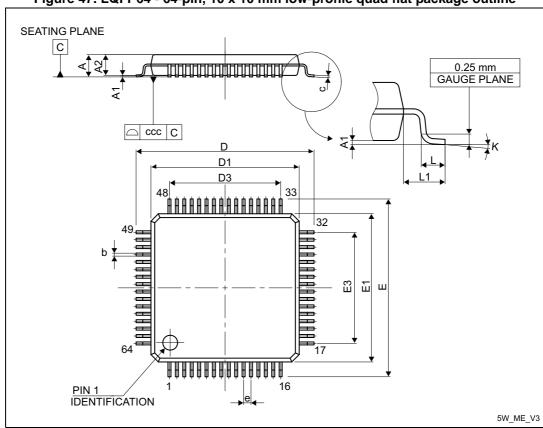

## 11.1.3 LQFP48 package information

Figure 50. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

Table 54. LQFP48 - 48-pin, 7x 7 mm low-profile quad flat package mechanical

| Symbol | mm    |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------|-------|-------|-----------------------|--------|--------|

|        | Min   | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -     | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800 | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800 | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -     | 5.500 | -     | -                     | 0.2165 | -      |

| Е      | 8.800 | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

#### 11.2.2 Selecting the product temperature range

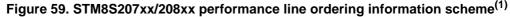

When ordering the microcontroller, the temperature range is specified in the order code (see *Figure 59: STM8S207xx/208xx performance line ordering information scheme(1) on page 112*).

The following example shows how to calculate the temperature range needed for a given application.

Assuming the following application conditions:

- Maximum ambient temperature T<sub>Amax</sub>= 82 °C (measured according to JESD51-2)

- $I_{DDmax} = 15 \text{ mA}, V_{DD} = 5.5 \text{ V}$

- Maximum eight standard I/Os used at the same time in output at low level with  $I_{OL} = 10$  mA,  $V_{OL} = 2 \text{ V}$

- Maximum four high sink I/Os used at the same time in output at low level with I<sub>OL</sub> = 20 mA, V<sub>OL</sub>= 1.5 V

- Maximum two true open drain I/Os used at the same time in output at low level with  $I_{OL} = 20$  mA,  $V_{OL} = 2$  V

$P_{INTmax} = 15 \text{ mA } x 5.5 \text{ V} = 82.5 \text{ mW}$

$P_{IOmax} = (10 \text{ mA x 2 V x 8}) + (20 \text{ mA x 2 V x 2}) + (20 \text{ mA x 1.5 V x 4}) = 360 \text{ mW}$

This gives: P<sub>INTmax</sub> = 82.5 mW and P<sub>IOmax</sub> 360 mW:

$P_{Dmax} = 82.5 \text{ mW} + 360 \text{ mW}$

Thus:  $P_{Dmax} = 443 \text{ mW}$

Using the values obtained in *Table 57: Thermal characteristics on page 108*  $T_{Jmax}$  is calculated as follows for LQFP64 10 x 10 mm = 46 °C/W:

$$T_{\text{-lmax}} = 82 \, ^{\circ}\text{C} + (46 \, ^{\circ}\text{C/W} \, \text{x} \, 443 \, \text{mW}) = 82 \, ^{\circ}\text{C} + 20 \, ^{\circ}\text{C} = 102 \, ^{\circ}\text{C}$$

This is within the range of the suffix 6 version parts (-40 <  $T_J$  < 105 °C).

In this case, parts must be ordered at least with the temperature range suffix 6.

## 12 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

## 12.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows you to order exactly what you need to meet the development requirements and to adapt the emulation system to support existing and future ST microcontrollers.

#### STice key features

- Occurrence and time profiling and code coverage (new features)

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Program and data trace recording up to 128 KB records

- Read/write on the fly of memory during emulation

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows you to specify the components you need to meet the development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

## 13 Ordering information

For a list of available options (e.g. memory size, package) and order-able part numbers or for further information on any aspect of this device, please go to www.st.com or contact the ST Sales Office nearest to you.

5//

<sup>2.</sup> Refer to Table 2: STM8S20xxx performance line features for detailed description.

Table 58. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 18-Feb-2015 | 13       | Updated:  - Figure 43: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline  - Table 51: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data  - Figure 51: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data  - Figure 51: LQFP64 - 80-pin, 10 x 10 mm low-profile quad flat package outline  - Table 53: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data  - Figure 50: LQFP64 - 64-pin, 7 x 7 mm low-profile quad flat package outline  - Table 54: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline  - Table 56: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical  - Figure 56: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline  - Table 56: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data  Added:  - Figure 44: LQFP80 recommended footprint  - Figure 45: LQFP80 marking example (package top view)  - Figure 49: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint  - Figure 51: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint  - Figure 52: LQFP48 marking example (package top view)  - Figure 53: LQFP48 marking example (package top view)  - Figure 55: LQFP44 marking example (package top view)  - Figure 55: LQFP44 marking example (package top view)  - Figure 55: LQFP44 marking example (package top view)  - Figure 55: LQFP44 marking example (package top view)  - Figure 55: LQFP44 marking example (package top view)  - Figure 57: LQFP45 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint |  |  |