Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detano                     |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 38                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 10x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207c8t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 6.2    | Registe  | map                                               |

|----|--------|----------|---------------------------------------------------|

| 7  | Interr | upt vec  | tor mapping                                       |

| 8  | Optio  | n bytes  |                                                   |

| 9  | Uniqu  | ie ID    |                                                   |

| 10 | Electr | ical cha | aracteristics                                     |

|    | 10.1   | Parame   | ter conditions                                    |

|    |        | 10.1.1   | Minimum and maximum values                        |

|    |        | 10.1.2   | Typical values                                    |

|    |        | 10.1.3   | Typical curves                                    |

|    |        | 10.1.4   | Typical current consumption                       |

|    |        | 10.1.5   | Pin loading conditions                            |

|    |        | 10.1.6   | Loading capacitor                                 |

|    |        | 10.1.7   | Pin input voltage                                 |

|    | 10.2   | Absolute | e maximum ratings 54                              |

|    | 10.3   | Operatir | ng conditions                                     |

|    |        | 10.3.1   | VCAP external capacitor                           |

|    |        | 10.3.2   | Supply current characteristics                    |

|    |        | 10.3.3   | External clock sources and timing characteristics |

|    |        | 10.3.4   | Internal clock sources and timing characteristics |

|    |        | 10.3.5   | Memory characteristics                            |

|    |        | 10.3.6   | I/O port pin characteristics                      |

|    |        | 10.3.7   | Reset pin characteristics                         |

|    |        | 10.3.8   | SPI serial peripheral interface80                 |

|    |        | 10.3.9   | I <sup>2</sup> C interface characteristics        |

|    |        | 10.3.10  | 10-bit ADC characteristics                        |

|    |        | 10.3.11  | EMC characteristics                               |

| 11 | Packa  | age cha  | racteristics                                      |

|    | 11.1   | Package  | e information                                     |

|    |        | 11.1.1   | LQFP80 package information92                      |

|    |        | 11.1.2   | LQFP64 package information95                      |

|    |        | 11.1.3   | LQFP48 package information                        |

|    |        | 11.1.4   | LQFP44 package information                        |

|    |        |          |                                                   |

DocID14733 Rev 13

# 1 Introduction

This datasheet contains the description of the STM8S20xxx features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S microcontroller family reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

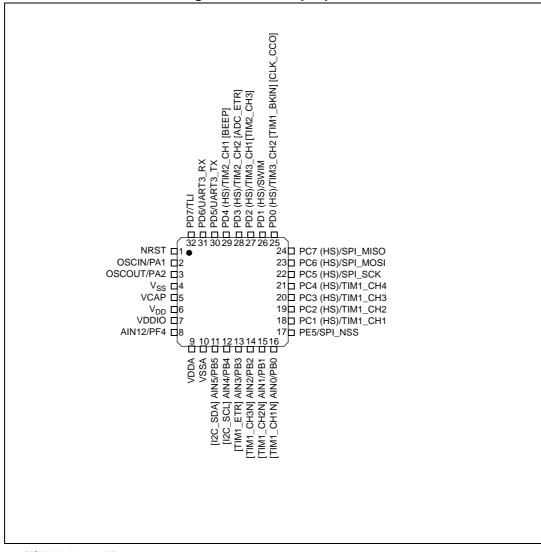

1. (HS) high sink capability.

2. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

| Туре             | I= Input, O                | = Input, O = Output, S = Power supply                                                                                                                                                                 |  |  |  |  |  |

|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Level            | Input                      | nput CM = CMOS                                                                                                                                                                                        |  |  |  |  |  |

|                  | Output HS = High sink      |                                                                                                                                                                                                       |  |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s | D1 = Slow (up to 2 MHz)<br>D2 = Fast (up to 10 MHz)<br>D3 = Fast/slow programmability with slow as default state after reset<br>D4 = Fast/slow programmability with fast as default state after reset |  |  |  |  |  |

| Port and control | Input                      | float = floating, wpu = weak pull-up                                                                                                                                                                  |  |  |  |  |  |

| configuration    | Output                     | Dutput T = True open drain, OD = Open drain, PP = Push pull                                                                                                                                           |  |  |  |  |  |

| Reset state      | Unless othe                | state after internal reset release)<br>erwise specified, the pin state is the same during the reset phase and<br>ernal reset release.                                                                 |  |  |  |  |  |

| Table 5. Legend/abbreviations | for pinout table |

|-------------------------------|------------------|

|-------------------------------|------------------|

|        | Pin    | num    | ber    |        |                     |      |          | Inpu     | t              |           | Out   | put |   |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------|------|----------|----------|----------------|-----------|-------|-----|---|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name            | Type | floating | ndw      | Ext. interrupt | High sink | Speed | QO  | Ы | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | 1      | 1      | 1      | NRST                | I/O  |          | <u>X</u> |                |           |       |     |   | Reset                          |                                  |                                                      |

| 2      | 2      | 2      | 2      | 2      | PA1/OSCIN           | I/O  | <u>x</u> | х        |                |           | 01    | х   | х | Port A1                        | Resonator/<br>crystal in         |                                                      |

| 3      | 3      | 3      | 3      | 3      | PA2/OSCOUT          | I/O  | X        | х        | х              |           | 01    | х   | х | Port A2                        | Resonator/<br>crystal out        |                                                      |

| 4      | 4      | 4      | 4      | -      | V <sub>SSIO_1</sub> | S    |          |          |                |           |       |     |   | I/O groun                      | d                                |                                                      |

| 5      | 5      | 5      | 5      | 4      | V <sub>SS</sub>     | S    |          |          |                |           |       |     |   | Digital gro                    | ound                             |                                                      |

| 6      | 6      | 6      | 6      | 5      | VCAP                | S    |          |          |                |           |       |     |   | 1.8 V reg                      | ulator capacitor                 |                                                      |

| 7      | 7      | 7      | 7      | 6      | V <sub>DD</sub>     | S    |          |          |                |           |       |     |   | Digital po                     | wer supply                       |                                                      |

| 8      | 8      | 8      | 8      | 7      | V <sub>DDIO_1</sub> | S    |          |          |                |           |       |     |   | I/O powe                       | r supply                         |                                                      |

| 9      | 9      | 9      | -      | -      | PA3/TIM2_CH3        | I/O  | <u>x</u> | х        | Х              |           | 01    | х   | х | Port A3                        | Timer 2 -<br>channel3            | TIM3_CH1<br>[AFR1]                                   |

| 10     | 10     | 10     | 9      | -      | PA4/UART1_RX        | I/O  | X        | х        | Х              | HS        | O3    | х   | Х | Port A4                        | UART1<br>receive                 |                                                      |

| 11     | 11     | 11     | 10     | -      | PA5/UART1_TX        | I/O  | <u>x</u> | х        | Х              | HS        | О3    | Х   | Х | Port A5                        | UART1<br>transmit                |                                                      |

### Table 6. Pin description

|        | Pin    | num    | nber   |        |                                 |      |          | Inpu     | t              |           | Out   | put              |    | -                              |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------------------|------|----------|----------|----------------|-----------|-------|------------------|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name                        | Type | floating | ndw      | Ext. interrupt | High sink | Speed | OD               | ΡР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 69     | 55     | 39     | 35     | -      | PE1/I <sup>2</sup> C_SCL        | I/O  | <u>X</u> |          | Х              |           | 01    | T <sup>(3)</sup> |    | Port E1                        | I <sup>2</sup> C clock           |                                                      |

| 70     | 56     | 40     | 36     | -      | PE0/CLK_CCO                     | I/O  | X        | Х        | Х              | HS        | O3    | х                | Х  | Port E0                        | Configurable<br>clock output     |                                                      |

| 71     | -      | -      | -      | -      | PI6                             | I/O  | <u>X</u> | Х        |                |           | 01    | Х                | Х  | Port I6                        |                                  |                                                      |

| 72     | -      | -      | -      | -      | PI7                             | I/O  | <u>X</u> | Х        |                |           | 01    | Х                | Х  | Port I7                        |                                  |                                                      |

| 73     | 57     | 41     | 37     | 25     | PD0/TIM3_CH2                    | I/O  | <u>x</u> | х        | х              | HS        | O3    | х                | х  | Port D0                        | Timer 3 -<br>channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 74     | 58     | 42     | 38     | 26     | PD1/SWIM <sup>(4)</sup>         | I/O  | х        | <u>x</u> | Х              | HS        | 04    | х                | х  | Port D1                        | SWIM data<br>interface           |                                                      |

| 75     | 59     | 43     | 39     | 27     | PD2/TIM3_CH1                    | I/O  | <u>x</u> | х        | Х              | HS        | O3    | х                | х  | Port D2                        | Timer 3 -<br>channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 76     | 60     | 44     | 40     | 28     | PD3/TIM2_CH2                    | I/O  | <u>x</u> | х        | Х              | HS        | O3    | х                | х  | Port D3                        | Timer 2 -<br>channel 2           | ADC_ETR<br>[AFR0]                                    |

| 77     | 61     | 45     | 41     | 29     | PD4/TIM2_CH1/B<br>EEP           | I/O  | X        | х        | Х              | HS        | O3    | х                | х  | Port D4                        | Timer 2 -<br>channel 1           | BEEP output<br>[AFR7]                                |

| 78     | 62     | 46     | 42     | 30     | PD5/ UART3_TX                   | I/O  | X        | х        | Х              |           | 01    | х                | х  | Port D5                        | UART3 data<br>transmit           |                                                      |

| 79     | 63     | 47     | 43     | 31     | PD6/<br>UART3_RX <sup>(1)</sup> | I/O  | X        | Х        | Х              |           | 01    | х                | х  | Port D6                        | UART3 data<br>receive            |                                                      |

| 80     | 64     | 48     | 44     | 32     | PD7/TLI                         | I/O  | X        | Х        | Х              |           | 01    | х                | х  | Port D7                        | Top level<br>interrupt           | TIM1_CH4<br>[AFR4] <sup>(5)</sup>                    |

| Table | 6.  | Pin | descri | ption ( | (continued) |  |

|-------|-----|-----|--------|---------|-------------|--|

| IUNIO | ••• |     | 400011 |         | (oonanaoa)  |  |

1. The default state of UART1\_RX and UART3\_RX pins is controlled by the ROM bootloader. These pins are pulled up as part of the bootloader activation process and returned to the floating state before a return from the bootloader.

2. The beCAN interface is available on STM8S208xx devices only

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to V<sub>DD</sub> are not implemented).

4. The PD1 pin is in input pull-up during the reset phase and after the internal reset release.

5. Available in 44-pin package only. On other packages, the AFR4 bit is reserved and must be kept at 0.

# 5.2 Alternate function remapping

As shown in the rightmost column of the pin description table, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function

| Address                   | Block   | Register label | Register name            | Reset<br>status     |

|---------------------------|---------|----------------|--------------------------|---------------------|

| 0x00 5428                 |         | CAN_P0         | CAN paged register 0     | 0xXX <sup>(3)</sup> |

| 0x00 5429                 |         | CAN_P1         | CAN paged register 1     | 0xXX <sup>(3)</sup> |

| 0x00 542A                 |         | CAN_P2         | CAN paged register 2     | 0xXX <sup>(3)</sup> |

| 0x00 542B                 | _       | CAN_P3         | CAN paged register 3     | 0xXX <sup>(3)</sup> |

| 0x00 542C                 | _       | CAN_P4         | CAN paged register 4     | 0xXX <sup>(3)</sup> |

| 0x00 542D                 | _       | CAN_P5         | CAN paged register 5     | 0xXX <sup>(3)</sup> |

| 0x00 542E                 | _       | CAN_P6         | CAN paged register 6     | 0xXX <sup>(3)</sup> |

| 0x00 542F                 |         | CAN_P7         | CAN paged register 7     | 0xXX <sup>(3)</sup> |

| 0x00 5430                 | - beCAN | CAN_P8         | CAN paged register 8     | 0xXX <sup>(3)</sup> |

| 0x00 5431                 | _       | CAN_P9         | CAN paged register 9     | 0xXX <sup>(3)</sup> |

| 0x00 5432                 | _       | CAN_PA         | CAN paged register A     | 0xXX <sup>(3)</sup> |

| 0x00 5433                 | -       | CAN_PB         | CAN paged register B     | 0xXX <sup>(3)</sup> |

| 0x00 5434                 | _       | CAN_PC         | CAN paged register C     | 0xXX <sup>(3)</sup> |

| 0x00 5435                 | _       | CAN_PD         | CAN paged register D     | 0xXX <sup>(3)</sup> |

| 0x00 5436                 | 1       | CAN_PE         | CAN paged register E     | 0xXX <sup>(3)</sup> |

| 0x00 5437                 |         | CAN_PF         | CAN paged register F     | 0xXX <sup>(3)</sup> |

| 0x00 5438 to<br>0x00 57FF |         | Re             | eserved area (968 bytes) |                     |

| Table 0  | Gonoral | hardwaro | rogistor | man | (continued) | • |

|----------|---------|----------|----------|-----|-------------|---|

| Table 9. | General | naruware | register | map | (continued) | , |

1. Depends on the previous reset source.

2. Write only register.

3. If the bootloader is enabled, it is initialized to 0x00.

| Option byte no. | Description                                                                                                                                                                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source                                                                                                                                                  |

| 0070            | <ul><li>IWDG_HW: Independent watchdog</li><li>0: IWDG Independent watchdog activated by software</li><li>1: IWDG Independent watchdog activated by hardware</li></ul>                                                                                                                          |

| OPT3            | <ul><li>WWDG_HW: Window watchdog activation</li><li>0: WWDG window watchdog activated by software</li><li>1: WWDG window watchdog activated by hardware</li></ul>                                                                                                                              |

|                 | WWDG_HALT: Window watchdog reset on halt<br>0: No reset generated on halt if WWDG active<br>1: Reset generated on halt if WWDG active                                                                                                                                                          |

|                 | <b>EXTCLK:</b> <i>External clock selection</i><br>0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                                                                                                                           |

| OPT4            | CKAWUSEL: Auto wakeup unit/clock<br>0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                                                                                                                                       |

|                 | PRSC[1:0] AWU clock prescaler<br>00: 24 MHz to 128 kHz prescaler<br>01: 16 MHz to 128 kHz prescaler<br>10: 8 MHz to 128 kHz prescaler<br>11: 4 MHz to 128 kHz prescaler                                                                                                                        |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>This configures the stabilization time.<br>0x00: 2048 HSE cycles<br>0xB4: 128 HSE cycles<br>0xD2: 8 HSE cycles<br>0xE1: 0.5 HSE cycles                                                                                               |

| OPT6            | Reserved                                                                                                                                                                                                                                                                                       |

| OPT7            | <ul> <li>WAITSTATE Wait state configuration</li> <li>This option configures the number of wait states inserted when reading from the Flash/data EEPROM memory.</li> <li>1 wait state is required if f<sub>CPU</sub> &gt; 16 MHz.</li> <li>0: No wait state</li> <li>1: 1 wait state</li> </ul> |

|  | Table 13. O | ption byte | description | (continued) |

|--|-------------|------------|-------------|-------------|

|--|-------------|------------|-------------|-------------|

| Symbol                                  | Ratings                                                                                                      | Max. <sup>(1)</sup> | Unit |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------|------|

| I <sub>VDD</sub>                        | Total current into V <sub>DD</sub> power lines (source) <sup>(2)</sup>                                       | 60                  |      |

| I <sub>VSS</sub>                        | Total current out of $V_{SS}$ ground lines (sink) <sup>(2)</sup>                                             | 60                  |      |

| 1                                       | Output current sunk by any I/O and control pin                                                               | 20                  |      |

| I <sub>IO</sub>                         | Output current source by any I/Os and control pin                                                            | 20                  |      |

|                                         | Total output current sourced (sum of all I/O and control pins) for devices with two $V_{DDIO}\rm pins^{(3)}$ | 200                 |      |

| ΣL                                      | Total output current sourced (sum of all I/O and control pins) for devices with one $V_{DDIO}\rm{pin}^{(3)}$ | 100                 | mA   |

| Σl <sub>lO</sub>                        | Total output current sunk (sum of all I/O and control pins) for devices with two $\rm V_{SSIO}\ pins^{(3)}$  | 160                 | IIIA |

|                                         | Total output current sunk (sum of all I/O and control pins) for devices with one $V_{SSIO}\text{pin}^{(3)}$  | 80                  |      |

|                                         | Injected current on NRST pin                                                                                 | ±4                  |      |

| I <sub>INJ(PIN)</sub> <sup>(4)(5)</sup> | Injected current on OSCIN pin                                                                                | ±4                  |      |

|                                         | Injected current on any other pin <sup>(6)</sup>                                                             | ±4                  |      |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$         | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                                      | ±20                 |      |

#### Table 16. Current characteristics

1. Data based on characterization results, not tested in production.

- 2. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external supply.

- 3. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package between the  $V_{DDIO}/V_{SSIO}$  pins.

- 4. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

- 5. Negative injection disturbs the analog performance of the device. See note in Section 10.3.10: 10-bit ADC characteristics on page 85.

- 6. When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| TJ               | Maximum junction temperature | 150        | 0    |

#### Table 17. Thermal characteristics

## Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        |            | 110 | 128 | 146              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       |            |     |     | 7 <sup>(1)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator power consumption |            |     | 5   |                  | μA   |

1. Guaranteed by design, not tested in production.

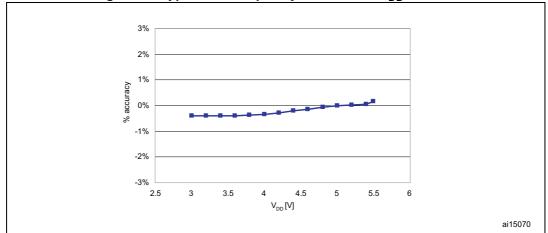

## Figure 19. Typical LSI frequency variation vs $V_{DD}$ @ 25 °C

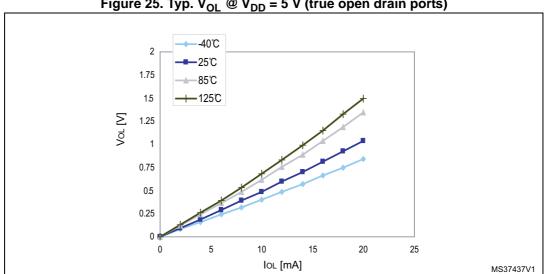

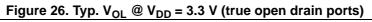

Figure 25. Typ.  $V_{OL} @ V_{DD} = 5 V$  (true open drain ports)

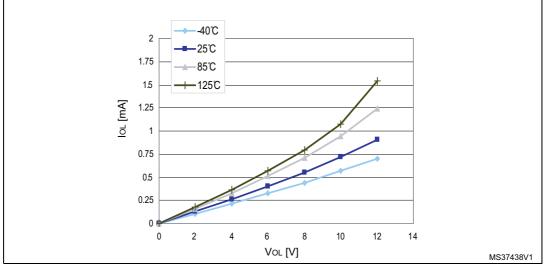

# 10.3.9 I<sup>2</sup>C interface characteristics

| O week at                                  | Denemation                              | Standard mode I <sup>2</sup> C |                    | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    |      |

|--------------------------------------------|-----------------------------------------|--------------------------------|--------------------|-------------------------------------------|--------------------|------|

| Symbol                                     | Parameter                               | Min <sup>(2)</sup>             | Max <sup>(2)</sup> | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> | Unit |

| t <sub>w(SCLL)</sub>                       | v(SCLL) SCL clock low time              |                                |                    | 1.3                                       |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                            |                    | 0.6                                       |                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                            |                    | 100                                       |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>               |                    | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                                | 1000               |                                           | 300 ns             |      |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                                | 300                |                                           | 300                |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                            |                    | 0.6                                       |                    |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                            |                    | 0.6                                       |                    | μs   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                            |                    | 0.6                                       |                    | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) |                                |                    | 1.3                                       |                    | μs   |

| Cb                                         | Capacitive load for each bus line       |                                | 400                |                                           | 400                | pF   |

Table 43. I<sup>2</sup>C characteristics

1.  $f_{MASTER},$  must be at least 8 MHz to achieve max fast I^2C speed (400kHz)  $\,$

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

Figure 40. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

### **10.3.10 10-bit ADC characteristics**

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol            | Parameter                                                          | Conditions                                                         | Min                 | Min Typ |                    | Unit               |  |

|-------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|---------|--------------------|--------------------|--|

| f                 | ADC alook fraguanay                                                | V <sub>DDA</sub> = 3 to 5.5 V                                      | 1                   |         | 4                  |                    |  |

| f <sub>ADC</sub>  | ADC clock frequency                                                | V <sub>DDA</sub> = 4.5 to 5.5 V                                    | 1                   |         | 6                  | MHz                |  |

| V <sub>DDA</sub>  | Analog supply                                                      |                                                                    | 3                   |         | 5.5                | V                  |  |

| V <sub>REF+</sub> | Positive reference voltage                                         |                                                                    | 2.75 <sup>(1)</sup> |         | V <sub>DDA</sub>   | V                  |  |

| V <sub>REF-</sub> | Negative reference voltage                                         |                                                                    | V <sub>SSA</sub>    |         | 0.5 <sup>(1)</sup> | V                  |  |

|                   |                                                                    |                                                                    | $V_{SSA}$           |         | V <sub>DDA</sub>   | V                  |  |

| V <sub>AIN</sub>  | Conversion voltage range <sup>(2)</sup>                            | Devices with external<br>V <sub>REF+</sub> /V <sub>REF-</sub> pins | V <sub>REF-</sub>   |         | V <sub>REF+</sub>  | V                  |  |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                 |                                                                    |                     | 3       |                    | pF                 |  |

| ts <sup>(2)</sup> | Sampling time                                                      | f <sub>ADC</sub> = 4 MHz                                           |                     | 0.75    |                    |                    |  |

| LS V              |                                                                    | f <sub>ADC</sub> = 6 MHz                                           |                     | 0.5     |                    | μs                 |  |

| t <sub>STAB</sub> | Wakeup time from standby                                           |                                                                    |                     | 7       |                    | μs                 |  |

|                   |                                                                    | $f_{ADC} = 4 MHz$                                                  | 3.5                 |         |                    | μs                 |  |

| t <sub>CONV</sub> | Total conversion time (including sampling time, 10-bit resolution) | f <sub>ADC</sub> = 6 MHz                                           |                     | 2.33    |                    | μs                 |  |

|                   |                                                                    |                                                                    |                     | 14      |                    | 1/f <sub>ADC</sub> |  |

| Table 44. | ADC | characteristics |

|-----------|-----|-----------------|

|-----------|-----|-----------------|

1. Data guaranteed by design, not tested in production.

2. During the sample time the input capacitance  $C_{AIN}$  (3 pF max) can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>S</sub> depend on programming.

| Symbol         | Parameter                                   | Conditions                | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|---------------------------|-----|--------------------|------|

|                |                                             | $f_{ADC} = 2 MHz$         | 1   | 2.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz  | 1.4 | 3                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 1.6 | 3.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.6 | 2                  |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz  | 1.1 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 1.2 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.2 | 2                  |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 4 MHz  | 0.6 | 2.5                | LSB  |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.8 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz  | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.8 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.6 | 1.5                |      |

| E <sub>L</sub> | Integral linearity error (2)                | $f_{ADC} = 4 \text{ MHz}$ | 0.6 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.6 | 1.5                |      |

| Table 45. ADC accuracy | y with R <sub>AIN</sub> < 10 | ) $\mathbf{k}\Omega$ , $\mathbf{V}_{\mathbf{DDA}} = 5 \mathbf{V}$ |

|------------------------|------------------------------|-------------------------------------------------------------------|

|------------------------|------------------------------|-------------------------------------------------------------------|

1. Data based on characterization results for LQFP80 device with  $V_{REF+}/V_{REF-}$ , not tested in production.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 10.3.6 does not affect the ADC accuracy.

| Symbol                           | Parameter Conditions                         |                           | Тур | Max <sup>(1)</sup> | Unit |

|----------------------------------|----------------------------------------------|---------------------------|-----|--------------------|------|

| E <sub>T</sub>                   | Total unadjusted error <sup>(2)</sup>        | $f_{ADC} = 2 MHz$         | 1.1 | 2                  |      |

| I⊢ŢI                             |                                              | f <sub>ADC</sub> = 4 MHz  | 1.6 | 2.5                |      |

| IEal                             | E <sub>O</sub>   Offset error <sup>(2)</sup> | $f_{ADC} = 2 MHz$         | 0.7 | 1.5                |      |

| E <sub>O</sub>   Offset e        |                                              | f <sub>ADC</sub> = 4 MHz  | 1.3 | 2                  |      |

| IE . I                           | E <sub>G</sub>   Gain error <sup>(2)</sup>   | f <sub>ADC</sub> = 2 MHz  | 0.2 | 1.5                | LSB  |

| I⊏GI                             |                                              | $f_{ADC} = 4 \text{ MHz}$ | 0.5 | 2                  | LSD  |

|                                  | Differential linearity error <sup>(2)</sup>  | f <sub>ADC</sub> = 2 MHz  | 0.7 | 1                  |      |

| E <sub>D</sub>   Differential li |                                              | f <sub>ADC</sub> = 4 MHz  | 0.7 | 1                  |      |

| E <sub>L</sub>                   | Integral linearity error <sup>(2)</sup>      | $f_{ADC} = 2 MHz$         | 0.6 | 1.5                |      |

| וברו                             |                                              | f <sub>ADC</sub> = 4 MHz  | 0.6 | 1.5                |      |

| Table 46. ADC accuracy | with $R_{AIN}$ < 10 k $\Omega$ | $R_{AIN}, V_{DDA} = 3.3 V$ |

|------------------------|--------------------------------|----------------------------|

| Table 52. LQFP64 - 64-pin, 14 x 14 mm low-profile quad flat package mechanical |  |

|--------------------------------------------------------------------------------|--|

| data (continued)                                                               |  |

| Symbol |       | mm    |                |       | inches <sup>(1)</sup> |        |  |

|--------|-------|-------|----------------|-------|-----------------------|--------|--|

| Symbol | Min   | Тур   | /p Max Min Typ |       | Max                   |        |  |

| k      | 0.0 ° | 3.5 ° | 7.0 °          | 0.0 ° | 3.5 °                 | 7.0 °  |  |

| CCC    |       |       | 0.100          |       |                       | 0.0039 |  |

1. Values in inches are converted from mm and rounded to four decimal places.

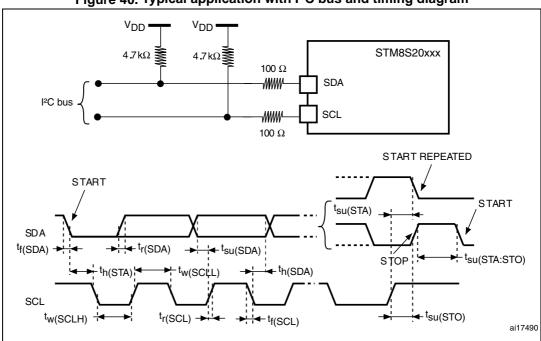

#### Figure 47. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data

| Gata   |       |       |       |                       |        |        |

|--------|-------|-------|-------|-----------------------|--------|--------|

| Symbol | mm    |       |       | inches <sup>(1)</sup> |        |        |

|        | Min   | Тур   | Max   | Min                   | Тур    | Мах    |

| А      | -     | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |

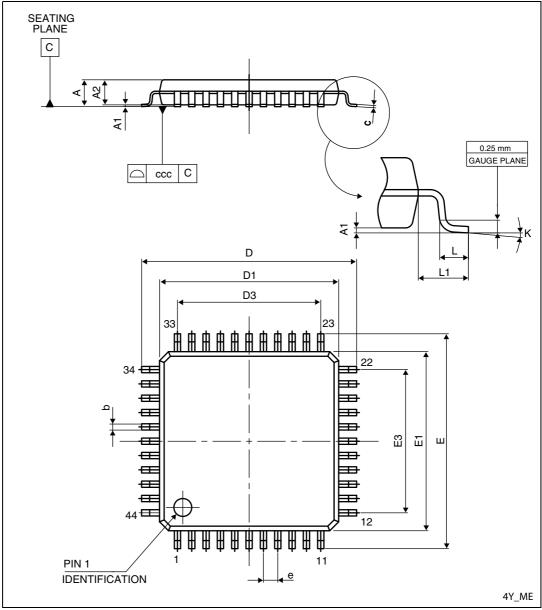

## 11.1.4 LQFP44 package information

Figure 53. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package outline

## **11.2** Thermal characteristics

The maximum chip junction temperature  $(T_{Jmax})$  must never exceed the values given in *Table 18: General operating conditions on page 56.*

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- $P_{I/Omax}$  represents the maximum power dissipation on output pins, where:  $P_{I/Omax} = \Sigma (V_{OL}*I_{OL}) + \Sigma ((V_{DD}-V_{OH})*I_{OH})$ , and taking account of the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                   | Value | Unit |

|---------------|-------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 80 - 14 x 14 mm | 38    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 64 - 14 x 14 mm | 45    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 64 - 10 x 10 mm | 46    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 48 - 7 x 7 mm   | 57    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 44 - 10 x 10 mm | 54    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 32 - 7 x 7 mm   | 60    | °C/W |

| Table 57. Thermal characteristics <sup>(1)</sup> | Table 57. | Thermal | characteristics <sup>(1)</sup> |

|--------------------------------------------------|-----------|---------|--------------------------------|

|--------------------------------------------------|-----------|---------|--------------------------------|

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

#### 11.2.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

## 12.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8. A free version that outputs up to 32 Kbytes of code is available.

#### 12.2.1 STM8 toolset

**STM8** toolset with STVD integrated development environment and STVP programming software is available for free download at <u>www.st.com/mcu</u>. This package includes:

ST Visual Develop - Full-featured integrated development environment from ST, featuring

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

**ST Visual Programmer (STVP)** – Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8 microcontroller Flash program memory, data EEPROM and option bytes. STVP also offers project mode for saving programming configurations and automating programming sequences.

### 12.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of the application directly from an easy-to-use graphical interface.

Available toolchains include:

- Cosmic C compiler for STM8 One free version that outputs up to 32 Kbytes of code is available. For more information, see www.cosmic-software.com.

- Raisonance C compiler for STM8 One free version that outputs up to 32 Kbytes of code. For more information, see www.raisonance.com.

- **STM8 assembler linker** Free assembly toolchain included in the STVD toolset, which allows you to assemble and link the application source code.

## 12.3 Programming tools

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

| Date        | Revision    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Jul-2009 | 8<br>cont'd | Section 10: Electrical characteristics: Added data for TBD values;<br>updated Table 15: Voltage characteristics and Table 18: General<br>operating conditions; updated VCAP specifications in Table 18 and<br>in Section 10.3.1: VCAP external capacitor, updated Figure 18;<br>replaced Figure 19; updated Table 35: RAM and hardware registers;<br>updated Figure 22 and Figure 35; added Figure 40: Typical<br>application with I2C bus and timing diagram.<br>Removed Table 56: Junction temperature range.<br>Added link between ordering information Figure 59 and STM8S20xx<br>features Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13-Apr-2010 | 9           | Document status changed from "preliminary data" to "datasheet".<br><i>Table 2: STM8S20xxx performance line features</i> : high sink I/O for<br>STM8S207C8 is 16 (not 13).<br><i>Table 3: Peripheral clock gating bit assignments in</i><br><i>CLK_PCKENR1/2 registers</i> : updated bit positions for TIM2 and<br>TIM3.<br><i>Figure 5: LQFP 48-pin pinout</i> : added CAN_TX and CAN_RX to pins<br>35 and 36; noted that these pins are available only in STM8S208xx<br>devices.<br><i>Figure 7: LQFP 32-pin pinout</i> : replaced uart2 with uart3.<br><i>Table 6: Pin description</i> : added footnotes concerning beCAN<br>availability and UART1_RX and UART3_RX pins.<br><i>Table 13: Option byte description</i> : added description of STM8L<br>bootloader option bytes to the option byte description table.<br>Added <i>Section 9: Unique ID</i> (and listed this attribute in <i>Features</i> ).<br><i>Section 10.3: Operating conditions</i> : replaced "C <sub>EXT</sub> " with "VCAP"<br>and added data for ESR and ESL; removed "low power dissipation"<br>condition for T <sub>A</sub> .<br><i>Table 26: Total current consumption in halt mode at VDD = 5 V</i> :<br>replaced max value of I <sub>DD(H)</sub> at 85 °C from 30 µA to 35 µA for the<br>condition "Flash in power-down mode, HSI clock after wakeup".<br><i>Table 33: HSI oscillator characteristics</i> : updated the ACC <sub>HSI</sub> factory<br>calibrated values.<br><i>Functional EMS (electromagnetic susceptibility)</i> and <i>Table 47</i> :<br>replaced "IEC 1000" with "IEC 61000".<br><i>Electromagnetic interference (EMI)</i> and <i>Table 48</i> : replaced "SAE<br>J1752/3" with "IEC 61967-2".<br><i>Table 57: Thermal characteristics</i> : changed the thermal resistance<br>junction-ambient value of LQFP32 (7x7 mm) from 59 °C/W to 60<br>°C/W. |

Table 58. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14733 Rev 13