Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 24MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                |

| Number of I/O              | 38                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 6K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                         |

| Data Converters            | A/D 10x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207cbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.5 Clock controller

The clock controller distributes the system clock ( $f_{MASTER}$ ) coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

#### Features

- **Clock prescaler:** To get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- *Master clock sources*: Four different clock sources can be used to drive the master clock:

- 1-24 MHz high-speed external crystal (HSE)

- Up to 24 MHz high-speed user-external clock (HSE user-ext)

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- **Startup clock:** After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

- **Configurable main clock output (CCO):** This outputs an external clock for use by the application.

| Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock | Bit     | Peripheral<br>clock |

|---------|---------------------|---------|---------------------|---------|---------------------|---------|---------------------|

| PCKEN17 | TIM1                | PCKEN13 | UART3               | PCKEN27 | beCAN               | PCKEN23 | ADC                 |

| PCKEN16 | TIM3                | PCKEN12 | UART1               | PCKEN26 | Reserved            | PCKEN22 | AWU                 |

| PCKEN15 | TIM2                | PCKEN11 | SPI                 | PCKEN25 | Reserved            | PCKEN21 | Reserved            |

| PCKEN14 | TIM4                | PCKEN10 | l <sup>2</sup> C    | PCKEN24 | Reserved            | PCKEN20 | Reserved            |

Table 3. Peripheral clock gating bit assignments in CLK\_PCKENR1/2 registers

## 4.6 **Power management**

For efficient power management, the application can be put in one of four different lowpower modes. You can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- *Wait mode*: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- **Halt mode**: In this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

## 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- 1. Timeout: At 16 MHz CPU clock the time-out period can be adjusted between 75  $\mu$ s up to 64 ms.

- 2. Refresh out of window: The downcounter is refreshed before its value is lower than the one stored in the window register.

## 4.12 TIM4 - 8-bit basic timer

- 8-bit autoreload, adjustable prescaler ratio to any power of 2 from 1 to 128

- Clock source: CPU clock

- Interrupt source: 1 x overflow/update

| Timer | Counter<br>size<br>(bits) | Prescaler                      | Counting<br>mode | CAPCOM<br>channels | Complem.<br>outputs | Ext.<br>trigger | Timer<br>synchr-<br>onization/<br>chaining |  |

|-------|---------------------------|--------------------------------|------------------|--------------------|---------------------|-----------------|--------------------------------------------|--|

| TIM1  | 16                        | Any integer from 1 to 65536    | Up/down          | 4                  | 3                   | Yes             |                                            |  |

| TIM2  | 16                        | Any power of 2 from 1 to 32768 | Up               | 3                  | 0                   | No              | No                                         |  |

| TIM3  | 16                        | Any power of 2 from 1 to 32768 | Up               | 2                  | 0                   | No              | NU                                         |  |

| TIM4  | 8                         | Any power of 2 from 1 to 128   | Up               | 0                  | 0                   | No              |                                            |  |

#### Table 4. TIM timer features

## 4.13 Analog-to-digital converter (ADC2)

STM8S20xxx performance line products contain a 10-bit successive approximation A/D converter (ADC2) with up to 16 multiplexed input channels and the following main features:

- Input voltage range: 0 to V<sub>DDA</sub>

- Dedicated voltage reference (VREF) pins available on 80 and 64-pin devices

- Conversion time: 14 clock cycles

- Single and continuous modes

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

## 4.14 Communication interfaces

The following communication interfaces are implemented:

- UART1: Full feature UART, SPI emulation, LIN2.1 master capability, Smartcard mode, IrDA mode, single wire mode.

- UART3: Full feature UART, LIN2.1 master/slave capability

- SPI: Full and half-duplex, 10 Mbit/s

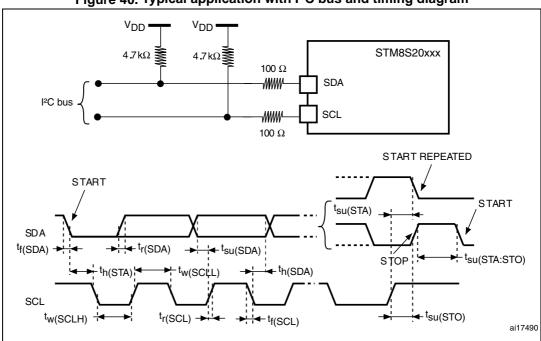

- I<sup>2</sup>C: Up to 400 Kbit/s

- beCAN (rev. 2.0A,B) 3 Tx mailboxes up to 1 Mbit/s

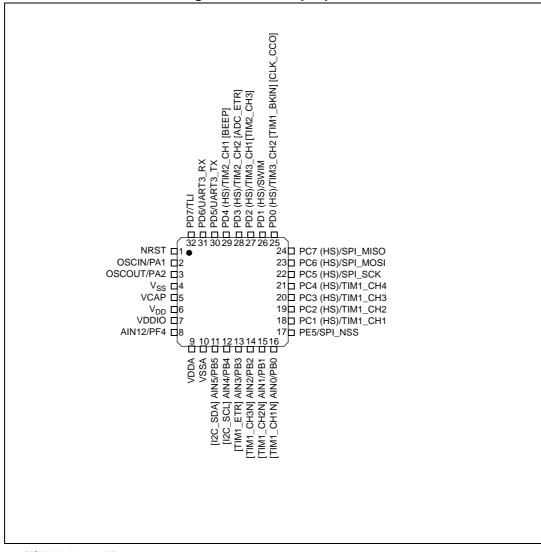

1. (HS) high sink capability.

2. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

|        | Pin    | num    | nber   |        |                           |      |          | Inpu |                |           | Out   |                  |    |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------------|------|----------|------|----------------|-----------|-------|------------------|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name                  | Type | floating | mdm  | Ext. interrupt | High sink | Speed | OD               | РР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 46     | 37     | 29     | -      | 21     | PC4/TIM1_CH4              | I/O  | X        | х    | Х              | HS        | O3    | х                | х  | Port C4                        | Timer 1 -<br>channel 4           |                                                      |

| 47     | 38     | 30     | 27     | 22     | PC5/SPI_SCK               | I/O  | <u>X</u> | Х    | Х              | HS        | O3    | Х                | Х  | Port C5                        | SPI clock                        |                                                      |

| 48     | 39     | 31     | 28     | -      | V <sub>SSIO_2</sub>       | S    |          |      |                |           |       |                  |    | I/O groun                      | d                                |                                                      |

| 49     | 40     | 32     | 29     | -      | V <sub>DDIO_2</sub>       | S    |          |      |                |           |       |                  |    | I/O powe                       | r supply                         |                                                      |

| 50     | 41     | 33     | 30     | 23     | PC6/SPI_MOSI              | I/O  | X        | x    | х              | HS        | О3    | х                | х  | Port C6                        | SPI master<br>out/<br>slave in   |                                                      |

| 51     | 42     | 34     | 31     | 24     | PC7/SPI_MISO              | I/O  | <u>x</u> | х    | Х              | HS        | O3    | х                | Х  | Port C7                        | SPI master in/<br>slave out      |                                                      |

| 52     | 43     | 35     | 32     | -      | PG0/CAN_TX <sup>(2)</sup> | I/O  | <u>x</u> | х    |                |           | 01    | х                | Х  | Port G0                        | beCAN<br>transmit                |                                                      |

| 53     | 44     | 36     | 33     | -      | PG1/CAN_RX <sup>(2)</sup> | I/O  | <u>x</u> | х    |                |           | 01    | х                | Х  | Port G1                        | beCAN<br>receive                 |                                                      |

| 54     | 45     | -      | -      | -      | PG2                       | I/O  | X        | Х    |                |           | 01    | Х                | Х  | Port G2                        |                                  |                                                      |

| 55     | 46     | -      | -      | -      | PG3                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port G3                        |                                  |                                                      |

| 56     | 47     | -      | -      | -      | PG4                       | I/O  | X        | Х    |                |           | O1    | Х                | Х  | Port G4                        |                                  |                                                      |

| 57     | 48     | -      | -      | -      | PI0                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port I0                        |                                  |                                                      |

| 58     | -      | -      | -      | -      | PI1                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port I1                        |                                  |                                                      |

| 59     | -      | -      | -      | -      | Pl2                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port I2                        |                                  |                                                      |

| 60     | -      | -      | -      | -      | PI3                       | I/O  | X        | Х    |                |           | 01    | Х                | Х  | Port I3                        |                                  |                                                      |

| 61     | -      | -      | -      | -      | PI4                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port I4                        |                                  |                                                      |

| 62     | -      | -      | -      | -      | PI5                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port I5                        |                                  |                                                      |

| 63     | 49     | -      | -      | -      | PG5                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port G5                        |                                  |                                                      |

| 64     | 50     | -      | -      | -      | PG6                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Х  | Port G6                        |                                  |                                                      |

| 65     | 51     | -      | -      | -      | PG7                       | I/O  | <u>X</u> | Х    |                |           | 01    | Х                | Х  | Port G7                        |                                  |                                                      |

| 66     | 52     | -      | -      | -      | PE4                       | I/O  | <u>X</u> | Х    | Х              |           | 01    | Х                | Х  | Port E4                        |                                  |                                                      |

| 67     | 53     | 37     | -      | -      | PE3/TIM1_BKIN             | I/O  | X        | х    | Х              |           | 01    | х                | Х  | Port E3                        | Timer 1 -<br>break input         |                                                      |

| 68     | 54     | 38     | 34     | -      | PE2/I <sup>2</sup> C_SDA  | I/O  | <u>X</u> |      | Х              |           | 01    | T <sup>(3)</sup> |    | Port E2                        | I <sup>2</sup> C data            |                                                      |

Table 6. Pin description (continued)

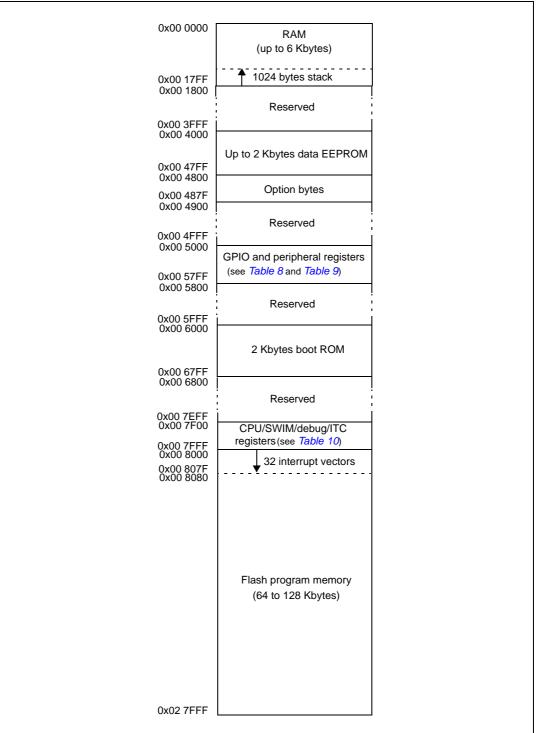

# 6 Memory and register map

## 6.1 Memory map

Figure 8. Memory map

| Address                   | Block   | Register label            | Register name        | Reset<br>status     |  |  |

|---------------------------|---------|---------------------------|----------------------|---------------------|--|--|

| 0x00 5428                 |         | CAN_P0                    | CAN paged register 0 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5429                 |         | CAN_P1                    | CAN paged register 1 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542A                 |         | CAN_P2                    | CAN paged register 2 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542B                 | _       | CAN_P3                    | CAN paged register 3 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542C                 | _       | CAN_P4                    | CAN paged register 4 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542D                 | _       | CAN_P5                    | CAN paged register 5 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542E                 | _       | CAN_P6                    | CAN paged register 6 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542F                 |         | CAN_P7                    | CAN paged register 7 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5430                 | - beCAN | CAN_P8                    | CAN paged register 8 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5431                 | _       | CAN_P9                    | CAN paged register 9 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5432                 | _       | CAN_PA                    | CAN paged register A | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5433                 | -       | CAN_PB                    | CAN paged register B | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5434                 | _       | CAN_PC                    | CAN paged register C | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5435                 | _       | CAN_PD                    | CAN paged register D | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5436                 | 1       | CAN_PE                    | CAN paged register E | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5437                 |         | CAN_PF                    | CAN paged register F | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5438 to<br>0x00 57FF |         | Reserved area (968 bytes) |                      |                     |  |  |

| Table 0  | Gonoral | hardwaro | rogistor | man | (continued) |   |

|----------|---------|----------|----------|-----|-------------|---|

| Table 9. | General | naruware | register | map | (continued) | , |

1. Depends on the previous reset source.

2. Write only register.

3. If the bootloader is enabled, it is initialized to 0x00.

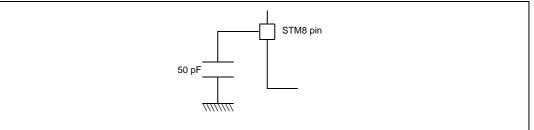

## 10.1.5 Pin loading conditions

## **10.1.6** Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 10.

#### Figure 10. Pin loading conditions

## 10.1.7 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

#### Figure 11. Pin input voltage

# **10.2** Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                           | Min                   | Max                                     | Unit |

|------------------------------------|-------------------------------------------------------------------|-----------------------|-----------------------------------------|------|

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                  | 6.5                                     |      |

| V                                  | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3 | 6.5                                     | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3                   |      |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           |                       | 50                                      | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins                  |                       | 50                                      | IIIV |

| V <sub>ESD</sub>                   | V <sub>ESD</sub> Electrostatic discharge voltage                  |                       | te maximum<br>´electrical<br>on page 89 |      |

| Table 15. | Voltage | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

## 10.3.6 I/O port pin characteristics

### **General characteristics**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$  unless otherwise specified. All unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor.

| Symbol                          | Parameter                                         | Conditions                                  | Min                   | Тур | Max                     | Unit |

|---------------------------------|---------------------------------------------------|---------------------------------------------|-----------------------|-----|-------------------------|------|

| V <sub>IL</sub>                 | Input low level<br>voltage                        |                                             | -0.3                  |     | 0.3 x V <sub>DD</sub>   | V    |

| V <sub>IH</sub>                 | Input high level<br>voltage                       | $V_{DD} = 5 V$                              | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | v    |

| V <sub>hys</sub>                | Hysteresis <sup>(1)</sup>                         |                                             |                       | 700 |                         | mV   |

| R <sub>pu</sub>                 | Pull-up resistor                                  | $V_{DD}$ = 5 V, $V_{IN}$ = $V_{SS}$         | 30                    | 55  | 80                      | kΩ   |

|                                 |                                                   | Fast I/Os<br>Load = 50 pF                   |                       |     | 20 <sup>(2)</sup>       |      |

|                                 | Rise and fall time<br>(10% - 90%)                 | Standard and high sink I/Os<br>Load = 50 pF |                       |     | 125 <sup>(2)</sup>      | 20   |

| t <sub>R</sub> , t <sub>F</sub> |                                                   | Fast I/Os<br>Load = 20 pF                   |                       |     | 35 <sup>(3)</sup>       | ns   |

|                                 |                                                   | Standard and high sink I/Os<br>Load = 20 pF |                       |     | 125 <sup>(3)</sup>      |      |

| l <sub>lkg</sub>                | Input leakage<br>current,<br>analog and digital   | $V_{SS} \leq V_{IN} \leq V_{DD}$            |                       |     | ±1                      | μA   |

| l <sub>ikg ana</sub>            | Analog input<br>leakage current                   | $V_{SS} \leq V_{IN} \leq V_{DD}$            |                       |     | ±250 <sup>(2)</sup>     | nA   |

| l <sub>lkg(inj)</sub>           | Leakage current in<br>adjacent I/O <sup>(2)</sup> | Injection current ±4 mA                     |                       |     | ±1 <sup>(2)</sup>       | μA   |

1. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested in production.

2. Data based on characterization results, not tested in production.

3. Guaranteed by design.

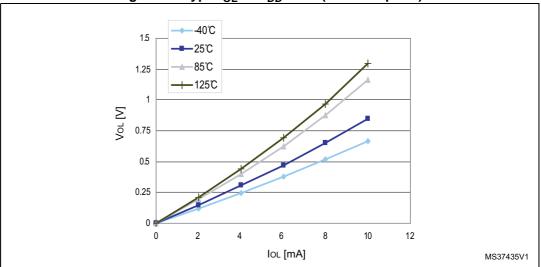

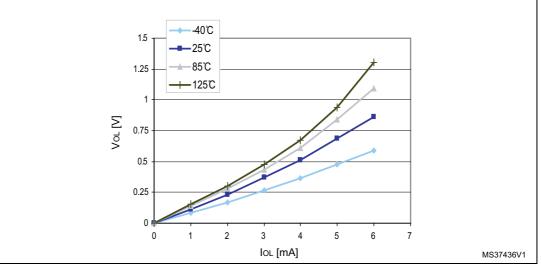

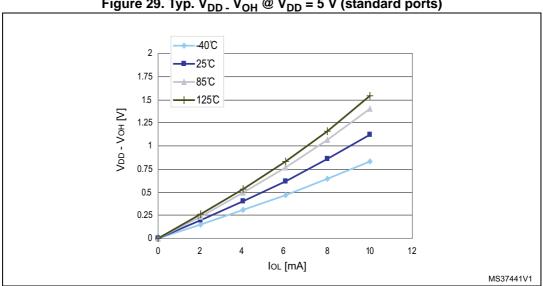

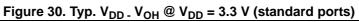

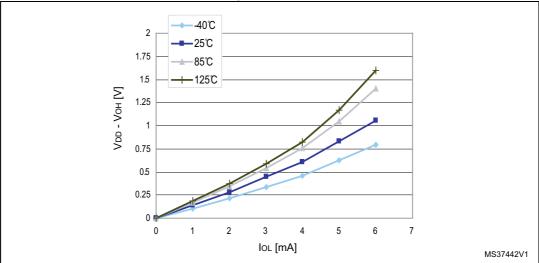

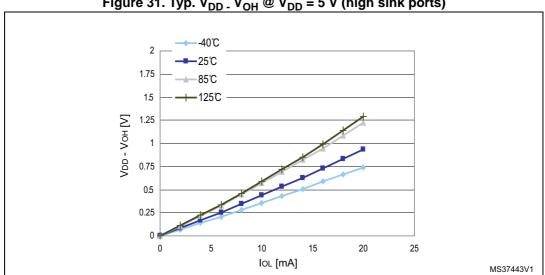

#### **Typical output level curves**

*Figure 24* to *Figure 31* show typical output level curves measured with output on a single pin.

## Figure 24. Typ. $V_{OL} @ V_{DD} = 3.3 V$ (standard ports)

Figure 29. Typ.  $V_{DD}$  V<sub>OH</sub> @  $V_{DD}$  = 5 V (standard ports)

Figure 31. Typ.  $V_{DD}$  -  $V_{OH}$  @  $V_{DD}$  = 5 V (high sink ports)

## 10.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions             | Min                         | <b>Typ</b> <sup>1)</sup> | Max                   | Unit |

|-------------------------|----------------------------------------------|------------------------|-----------------------------|--------------------------|-----------------------|------|

| V <sub>IL(NRST)</sub>   | NRST Input low level voltage <sup>(1)</sup>  |                        | -0.3 V                      |                          | 0.3 x V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub>   | NRST Input high level voltage <sup>(1)</sup> |                        | $0.7 	ext{ x V}_{	ext{DD}}$ |                          | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OL(NRST)</sub>   | NRST Output low level voltage (1)            | I <sub>OL</sub> = 2 mA |                             |                          | 0.5                   |      |

| R <sub>PU(NRST)</sub>   | NRST Pull-up resistor <sup>(2)</sup>         |                        | 30                          | 55                       | 80                    | kΩ   |

| t <sub>IFP(NRST)</sub>  | NRST Input filtered pulse <sup>(3)</sup>     |                        |                             |                          | 75                    | ns   |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse <sup>(3)</sup> |                        | 500                         |                          |                       | ns   |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(1)</sup>             |                        | 15                          |                          |                       | μs   |

| Table 41. | NRST | pin  | characteristics  |

|-----------|------|------|------------------|

|           |      | PIII | character istics |

1. Data based on characterization results, not tested in production.

2. The  $\rm R_{\rm PU}$  pull-up equivalent resistor is based on a resistive transistor

3. Data guaranteed by design, not tested in production.

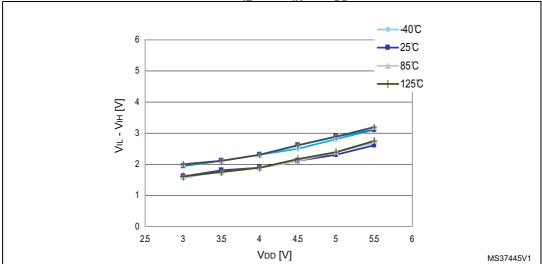

## Figure 33. Typical NRST $\rm V_{IL}$ and $\rm V_{IH}$ vs $\rm V_{DD}$ @ 4 temperatures

Figure 40. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

| Symbol         | Parameter                                   | Conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |  |

|----------------|---------------------------------------------|----------------------------------------------------------------|-----|--------------------|------|--|

|                |                                             | $f_{ADC} = 2 MHz$                                              | 1   | 2.5                |      |  |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz                                       | 1.4 | 3                  |      |  |

|                |                                             | f <sub>ADC</sub> = 6 MHz                                       | 1.6 | 3.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 2 MHz                                       | 0.6 | 2                  |      |  |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz                                       | 1.1 | 2.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 6 MHz                                       | 1.2 | 2.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 2 MHz                                       | 0.2 | 2                  |      |  |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 4 MHz                                       | 0.6 | 2.5                | LSB  |  |

|                |                                             | f <sub>ADC</sub> = 6 MHz                                       | 0.8 | 2.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 2 MHz                                       | 0.7 | 1.5                |      |  |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz                                       | 0.7 | 1.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 6 MHz                                       | 0.8 | 1.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 2 MHz                                       | 0.6 | 1.5                |      |  |

| E <sub>L</sub> | Integral linearity error (2)                | egral linearity error <sup>(2)</sup> $f_{ADC} = 4 \text{ MHz}$ | 0.6 | 1.5                |      |  |

|                |                                             | f <sub>ADC</sub> = 6 MHz                                       | 0.6 | 1.5                |      |  |

1. Data based on characterization results for LQFP80 device with  $V_{REF+}/V_{REF-}$ , not tested in production.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 10.3.6 does not affect the ADC accuracy.

| Symbol         | Parameter                                   | Conditions               | Тур | Max <sup>(1)</sup> | Unit |  |

|----------------|---------------------------------------------|--------------------------|-----|--------------------|------|--|

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | $f_{ADC} = 2 MHz$        | 1.1 | 2                  |      |  |

| I⊢ŢI           |                                             | f <sub>ADC</sub> = 4 MHz | 1.6 | 2.5                |      |  |

| IEal           | Offset error <sup>(2)</sup>                 | $f_{ADC} = 2 MHz$        | 0.7 | 1.5                |      |  |

| E <sub>O</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 1.3 | 2                  |      |  |

| IE . I         | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz | 0.2 | 1.5                | LSB  |  |

| E <sub>G</sub> | Gainenor                                    | f <sub>ADC</sub> = 4 MHz | 0.5 | 2                  | LSD  |  |

|                | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 2 MHz | 0.7 | 1                  |      |  |

| E <sub>D</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 0.7 | 1                  |      |  |

| IE. I          | Integral linearity error <sup>(2)</sup>     | $f_{ADC} = 2 MHz$        | 0.6 | 1.5                |      |  |

| E <sub>L</sub> |                                             | f <sub>ADC</sub> = 4 MHz | 0.6 | 1.5                |      |  |

| Table 46. ADC accuracy | with $R_{AIN}$ < 10 k $\Omega$ | $R_{AIN}, V_{DDA} = 3.3 V$ |

|------------------------|--------------------------------|----------------------------|

|        |       |        | a (continuou | /                     |        |        |  |  |

|--------|-------|--------|--------------|-----------------------|--------|--------|--|--|

| Symbol |       | mm     |              | inches <sup>(1)</sup> |        |        |  |  |

|        | Min   | Тур    | Max          | Min                   | Тур    | Max    |  |  |

| D      | -     | 12.000 | -            | -                     | 0.4724 | -      |  |  |

| D1     | -     | 10.000 | -            | -                     | 0.3937 | -      |  |  |

| D3     | -     | 7.500  | -            | -                     | 0.2953 | -      |  |  |

| E      | -     | 12.000 | -            | -                     | 0.4724 | -      |  |  |

| E1     | -     | 10.000 | -            | -                     | 0.3937 | -      |  |  |

| E3     | -     | 7.500  | -            | -                     | 0.2953 | -      |  |  |

| е      | -     | 0.500  | -            | -                     | 0.0197 | -      |  |  |

| θ      | 0°    | 3.5°   | 7°           | 0°                    | 3.5°   | 7°     |  |  |

| L      | 0.450 | 0.600  | 0.750        | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1     | -     | 1.000  | -            | -                     | 0.0394 | -      |  |  |

| CCC    | -     | -      | 0.080        | -                     | -      | 0.0031 |  |  |

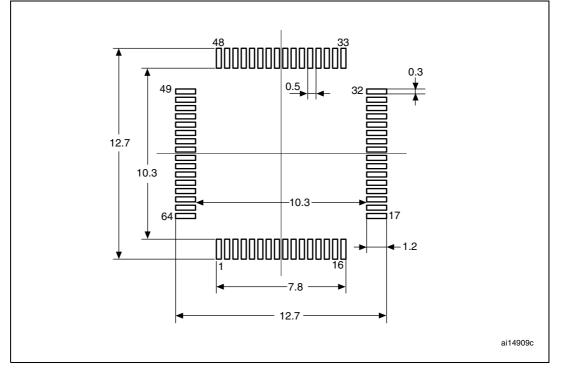

# Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanicaldata (continued)

1. Values in inches are converted from mm and rounded to four decimal places.

#### Figure 48. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

DocID14733 Rev 13

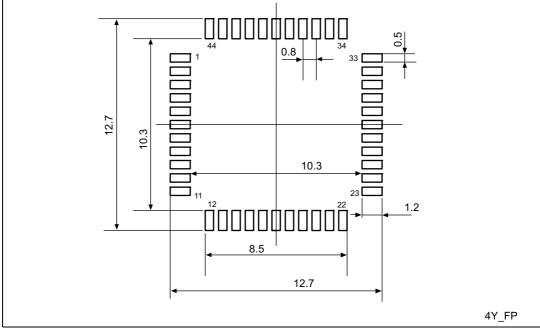

Figure 54. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

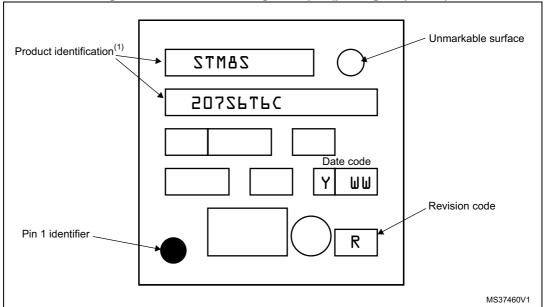

#### **Device marking**

The following figure shows the marking for the LQFP44 package.

Figure 55. LQFP44 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID14733 Rev 13

# 12 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

## 12.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows you to order exactly what you need to meet the development requirements and to adapt the emulation system to support existing and future ST microcontrollers.

#### STice key features

- Occurrence and time profiling and code coverage (new features)

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Program and data trace recording up to 128 KB records

- Read/write on the fly of memory during emulation

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows you to specify the components you need to meet the development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

# **13** Ordering information

| Example:                          | STM8 | S | 208 | М | В | т | 6 | В | TR |

|-----------------------------------|------|---|-----|---|---|---|---|---|----|

|                                   |      |   |     |   |   | I |   |   |    |

| Product class                     | ı    |   |     |   |   |   |   |   |    |

| STM8 microcontroller              |      |   |     |   |   |   |   |   |    |

| Family type -                     |      |   |     |   |   |   |   |   |    |

| S = Standard                      |      |   |     |   |   |   |   |   |    |

| Sub-family type <sup>(2)</sup>    |      |   |     |   |   |   |   |   |    |

| 208 = Full peripheral set         |      |   |     |   |   |   |   |   |    |

| 207 = Intermediate peripheral set |      |   |     |   |   |   |   |   |    |

| Pin count                         |      |   |     |   |   |   |   |   |    |

| K = 32 pins                       |      |   |     |   |   |   |   |   |    |

| S = 44 pins                       |      |   |     |   |   |   |   |   |    |

| C = 48 pins                       |      |   |     |   |   |   |   |   |    |

| R = 64 pins                       |      |   |     |   |   |   |   |   |    |

| M = 80 pins                       |      |   |     |   |   |   |   |   |    |

| Program memory size -             |      |   |     |   |   |   |   |   |    |

| 6 = 32 Kbyte                      |      |   |     |   |   |   |   |   |    |

| 8 = 64 Kbyte                      |      |   |     |   |   |   |   |   |    |

| B = 128 Kbyte                     |      |   |     |   |   |   |   |   |    |

| Package type                      |      |   |     |   |   |   |   |   |    |

| T = LQFP                          |      |   |     |   |   |   |   |   |    |

| Temperature range                 |      |   |     |   |   |   |   |   |    |

| 3 = -40 °C to 125 °C              |      |   |     |   |   |   |   |   |    |

| 6 = -40 °C to 85 °C               |      |   |     |   |   |   |   |   |    |

| Package pitch –                   |      |   |     |   |   |   |   | ] |    |

| No character = 0.5 mm             |      |   |     |   |   |   |   |   |    |

| B = 0.65 mm                       |      |   |     |   |   |   |   |   |    |

| C = 0.8 mm                        |      |   |     |   |   |   |   |   |    |

| Packing –                         |      |   |     |   |   |   |   |   |    |

| No character = Tray or tube       |      |   |     |   |   |   |   |   |    |

For a list of available options (e.g. memory size, package) and order-able part numbers or for further information on any aspect of this device, please go to <u>www.st.com</u> or contact the ST Sales Office nearest to you.

2. Refer to Table 2: STM8S20xxx performance line features for detailed description.