Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | STM8                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 24MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 25                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 6K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207k6t3ctr |

# List of figures

| Figure 1.                | STM8S20xxx block diagram                                                | 12           |

|--------------------------|-------------------------------------------------------------------------|--------------|

| Figure 2.                | Flash memory organization                                               |              |

| Figure 3.                | LQFP 80-pin pinout                                                      |              |

| Figure 4.                | LQFP 64-pin pinout                                                      |              |

| Figure 5.                | LQFP 48-pin pinout                                                      |              |

| Figure 6.                | LQFP 44-pin pinout                                                      |              |

| Figure 7.                | LQFP 32-pin pinout                                                      |              |

| Figure 8.                | Memory map                                                              |              |

| Figure 9.                | Supply current measurement conditions                                   |              |

| Figure 10.               | Pin loading conditions                                                  |              |

| Figure 11.               | Pin input voltage                                                       |              |

| Figure 12.               | f <sub>CPUmax</sub> versus V <sub>DD</sub>                              |              |

| Figure 13.               | External capacitor C <sub>FXT</sub>                                     | 57           |

| Figure 14.               | Typ. $I_{DD(RUN)}$ vs $V_{DD}$ , HSI RC osc, $f_{CPU} = 16$ MHz         |              |

| Figure 15.               | Typ. $I_{DD(WFI)}$ vs $V_{DD}$ , HSI RC osc, $f_{CPU} = 16$ MHz         |              |

| Figure 16.               | HSE external clock source                                               |              |

| Figure 17.               | HSE oscillator circuit diagram                                          |              |

| Figure 18.               | Typical HSI frequency variation vs V <sub>DD</sub> at 4 temperatures    |              |

| Figure 19.               | Typical LSI frequency variation vs V <sub>DD</sub> @ 25 °C              |              |

| Figure 20.               | Typical $V_{IL}$ and $V_{IH}$ vs $V_{DD}$ @ 4 temperatures              |              |

| Figure 21.               | Typical pull-up resistance vs V <sub>DD</sub> @ 4 temperatures          |              |

| Figure 22.               | Typical pull-up current vs V <sub>DD</sub> @ 4 temperatures             |              |

| Figure 23.               | Typ. $V_{OL}$ @ $V_{DD} = 5$ V (standard ports)                         |              |

| Figure 24.               | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (standard ports)                       |              |

| Figure 25.               | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (true open drain ports)                  |              |

| Figure 26.               | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (true open drain ports)                |              |

| Figure 27.               | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (high sink ports)                        |              |

| Figure 28.               | Typ. $V_{OL}$ @ $V_{DD}$ = 3.3 V (high sink ports)                      |              |

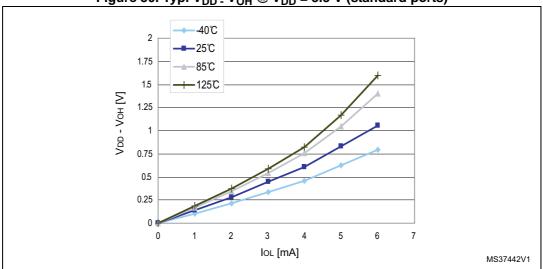

| Figure 29.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5 V$ (standard ports)                  |              |

| Figure 30.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (standard ports)}$        |              |

| Figure 31.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 5.3 \text{ (standard ports)}$          |              |

| Figure 31.               | Typ. $V_{DD} - V_{OH} @ V_{DD} = 3.3 \text{ V (high sink ports)}$       |              |

| Figure 33.               | Typical NRST $V_{II}$ and $V_{IH}$ vs $V_{DD}$ @ 4 temperatures         |              |

| Figure 34.               | Typical NRST pull-up resistance vs V <sub>DD</sub> @ 4 temperatures     |              |

| Figure 35.               | Typical NRST pull-up current vs V <sub>DD</sub> @ 4 temperatures        |              |

| Figure 36.               | Recommended reset pin protection                                        |              |

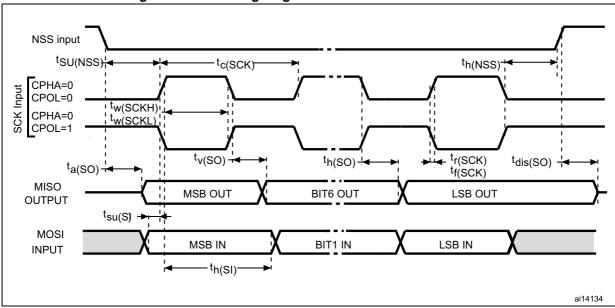

| Figure 30.               | SPI timing diagram - slave mode and CPHA = 0                            |              |

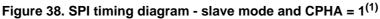

| -                        | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>             | 01           |

| Figure 38.<br>Figure 39. | SPI timing diagram - master mode and GPHA = 1\(\frac{1}{2}\)            | ۱۰.۰۰۱<br>ده |

| 0                        | Typical application with I <sup>2</sup> C bus and timing diagram        | 01           |

| Figure 40.               | ADC accuracy characteristics                                            |              |

| Figure 41.               |                                                                         |              |

| Figure 42.               | Typical application with ADC                                            |              |

| Figure 43.               | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline       |              |

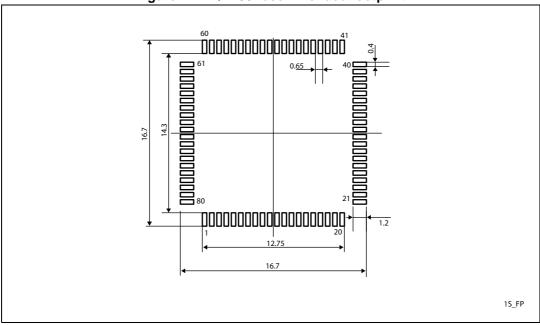

| Figure 44.               | LQFP80 recommended footprint                                            | 93           |

| Figure 45.               | LQFP80 marking example (package top view)                               |              |

| Figure 46.               | LQFP64 - 64-pin 14 mm x 14 mm low-profile quad flat package outline     |              |

| Figure 47.               | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline       |              |

| Figure 48.               | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint | 97           |

# 2 Description

The STM8S20xxx performance line 8-bit microcontrollers offer from 32 to 128 Kbytes Flash program memory. They are referred to as high-density devices in the STM8S microcontroller family reference manual.

All STM8S20xxx devices provide the following benefits: reduced system cost, performance robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, watchdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8S family thanks to their advanced core which is made in a state-of-the art technology for applications with 2.95 V to 5.5 V operating supply.

577

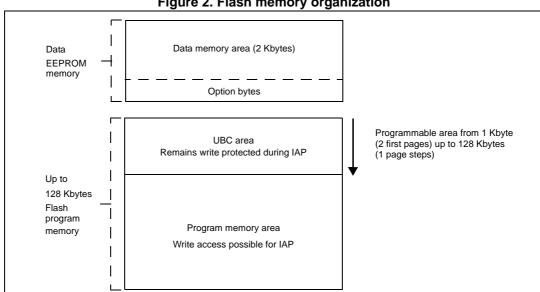

The size of the UBC is programmable through the UBC option byte (*Table 13*.), in increments of 1 page (512 bytes) by programming the UBC option byte in ICP mode.

This divides the program memory into two areas:

- Main program memory: Up to 128 Kbytes minus UBC

- User-specific boot code (UBC): Configurable up to 128 Kbytes

The UBC area remains write-protected during in-application programming. This means that the MASS keys do not unlock the UBC area. It protects the memory used to store the boot program, specific code libraries, reset and interrupt vectors, the reset routine and usually the IAP and communication routines.

Figure 2. Flash memory organization

## Read-out protection (ROP)

The read-out protection blocks reading and writing the Flash program memory and data EEPROM memory in ICP mode (and debug mode). Once the read-out protection is activated, any attempt to toggle its status triggers a global erase of the program and data memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure

The IWDG time base spans from 60 µs to 1 s.

# 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM3 input capture channel 1 for calibration

# 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

#### 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

# 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

5/

#### 4.14.1 UART1

#### **Main features**

- One Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- · Single wire half duplex mode

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

### **Synchronous communication**

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

#### LIN master mode

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

#### 4.14.2 UART3

#### **Main features**

- 1 Mbit/s full duplex SCI

- LIN master capable

- High precision baud rate generator

Table 6. Pin description (continued)

|        | Pin    | num    | ber    |        | 143            |      |          | Inpu |                |           | Out   | onti<br>put |    |                                |                                    |                                                      |

|--------|--------|--------|--------|--------|----------------|------|----------|------|----------------|-----------|-------|-------------|----|--------------------------------|------------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name       | Туре | floating | ndw  | Ext. interrupt | High sink | Speed | QO          | ЬР | Main function<br>(after reset) | Default<br>alternate<br>function   | Alternate<br>function<br>after remap<br>[option bit] |

| 31     | 27     | 19     | 18     | 13     | PB3/AIN3       | I/O  | <u>X</u> | X    | X              |           | 01    | X           | X  | Port B3                        | Analog<br>input 3                  | TIM1_ETR<br>[AFR5]                                   |

| 32     | 28     | 20     | 19     | 14     | PB2/AIN2       | I/O  | <u>x</u> | X    | X              |           | O1    | X           | X  | Port B2                        | Analog<br>input 2                  | TIM1_<br>CH3N<br>[AFR5]                              |

| 33     | 29     | 21     | 20     | 15     | PB1/AIN1       | I/O  | <u>x</u> | х    | Х              |           | O1    | X           | Х  | Port B1                        | Analog<br>input 1                  | TIM1_<br>CH2N<br>[AFR5]                              |

| 34     | 30     | 22     | 21     | 16     | PB0/AIN0       | I/O  | <u>x</u> | Х    | Х              |           | O1    | Х           | Х  | Port B0                        | Analog<br>input 0                  | TIM1_<br>CH1N<br>[AFR5]                              |

| 35     | -      | -      | -      | -      | PH4/TIM1_ETR   | I/O  | <u>X</u> | Х    |                |           | 01    | Х           | Х  | Port H4                        | Timer 1 -<br>trigger input         |                                                      |

| 36     | -      | •      | -      | -      | PH5/ TIM1_CH3N | I/O  | <u>X</u> | X    |                |           | O1    | Х           | Х  | Port H5                        | Timer 1 -<br>inverted<br>channel 3 |                                                      |

| 37     | -      | -      | 1      | •      | PH6/ TIM1_CH2N | I/O  | <u>X</u> | х    |                |           | O1    | Х           | Х  | Port H6                        | Timer 1 -<br>inverted<br>channel 2 |                                                      |

| 38     | -      | -      | -      | •      | PH7/ TIM1_CH1N | I/O  | <u>x</u> | х    |                |           | O1    | X           | Х  | Port H7                        | Timer 1 -<br>inverted<br>channel 2 |                                                      |

| 39     | 31     | 23     | 1      | •      | PE7/AIN8       | I/O  | <u>X</u> | Х    | Χ              |           | O1    | Χ           | Χ  | Port E7                        | Analog input 8                     |                                                      |

| 40     | 32     | 24     | 22     | •      | PE6/AIN9       | I/O  | <u>X</u> | Х    | Х              |           | 01    | Χ           | Χ  | Port E6                        | Analog input 9                     |                                                      |

| 41     | 33     | 25     | 23     | 17     | PE5/SPI_NSS    | I/O  | X        | X    | Х              |           | 01    | Χ           | X  | Port E5                        | SPI<br>master/slave<br>select      |                                                      |

| 42     | -      | -      | 1      | -      | PC0/ADC_ETR    | I/O  | <u>x</u> | Х    | Х              |           | 01    | Х           | Х  | Port C0                        | ADC trigger input                  |                                                      |

| 43     | 34     | 26     | 24     | 18     | PC1/TIM1_CH1   | I/O  | <u>X</u> | Х    | X              | HS        | О3    | X           | X  | Port C1                        | Timer 1 -<br>channel 1             |                                                      |

| 44     | 35     | 27     | 25     | 19     | PC2/TIM1_CH2   | I/O  | <u>X</u> | Х    | X              | HS        | О3    | X           | X  | Port C2                        | Timer 1-<br>channel 2              |                                                      |

| 45     | 36     | 28     | 26     | 20     | PC3/TIM1_CH3   | I/O  | <u>x</u> | Х    | Х              | HS        | О3    | Х           | Х  | Port C3                        | Timer 1 -<br>channel 3             |                                                      |

Table 6. Pin description (continued)

|        | Pin    | num    | ber    |        |                           |      |          | Inpu | t              |           | Out   |                  |    |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------------|------|----------|------|----------------|-----------|-------|------------------|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name                  | Туре | floating | mdm  | Ext. interrupt | High sink | Speed | OD               | ЬР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 46     | 37     | 29     | 1      | 21     | PC4/TIM1_CH4              | I/O  | <u>X</u> | Χ    | Χ              | HS        | О3    | Х                | Х  | Port C4                        | Timer 1 -<br>channel 4           |                                                      |

| 47     | 38     | 30     | 27     | 22     | PC5/SPI_SCK               | I/O  | <u>X</u> | Х    | Χ              | HS        | О3    | Х                | Χ  | Port C5                        | SPI clock                        |                                                      |

| 48     | 39     | 31     | 28     | -      | V <sub>SSIO_2</sub>       | S    |          |      |                |           |       |                  |    | I/O groun                      | d                                |                                                      |

| 49     | 40     | 32     | 29     | -      | $V_{DDIO_2}$              | S    |          |      |                |           |       |                  |    | I/O powe                       | supply                           |                                                      |

| 50     | 41     | 33     | 30     | 23     | PC6/SPI_MOSI              | I/O  | <u>X</u> | х    | х              | HS        | О3    | X                | Х  | Port C6                        | SPI master<br>out/<br>slave in   |                                                      |

| 51     | 42     | 34     | 31     | 24     | PC7/SPI_MISO              | I/O  | <u>X</u> | Х    | Х              | HS        | О3    | Х                | Х  | Port C7                        | SPI master in/<br>slave out      |                                                      |

| 52     | 43     | 35     | 32     | 1      | PG0/CAN_TX <sup>(2)</sup> | I/O  | <u>X</u> | Х    |                |           | 01    | Х                | X  | Port G0                        | beCAN<br>transmit                |                                                      |

| 53     | 44     | 36     | 33     | -      | PG1/CAN_RX <sup>(2)</sup> | I/O  | <u>X</u> | Х    |                |           | 01    | Х                | Х  | Port G1                        | beCAN<br>receive                 |                                                      |

| 54     | 45     | -      | -      | -      | PG2                       | I/O  | <u>X</u> | Χ    |                |           | O1    | Χ                | Χ  | Port G2                        |                                  |                                                      |

| 55     | 46     | -      | -      | -      | PG3                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Χ  | Port G3                        |                                  |                                                      |

| 56     | 47     | ı      | ı      | •      | PG4                       | I/O  | <u>X</u> | Х    |                |           | 01    | Х                | Χ  | Port G4                        |                                  |                                                      |

| 57     | 48     | 1      | 1      | 1      | PI0                       | I/O  | <u>X</u> | Х    |                |           | 01    | Х                | Χ  | Port I0                        |                                  |                                                      |

| 58     | -      | -      | -      | -      | PI1                       | I/O  | <u>X</u> | Χ    |                |           | O1    | Х                | Χ  | Port I1                        |                                  |                                                      |

| 59     | -      | -      | 1      | -      | PI2                       | I/O  | <u>X</u> | Χ    |                |           | 01    | Χ                | Χ  | Port I2                        |                                  |                                                      |

| 60     | -      | -      | 1      | -      | PI3                       | I/O  | <u>X</u> | Χ    |                |           | 01    | Χ                | Χ  | Port I3                        |                                  |                                                      |

| 61     | -      | -      | -      | -      | PI4                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Χ  | Port I4                        |                                  |                                                      |

| 62     | -      | -      | 1      | 1      | PI5                       | I/O  | <u>X</u> | Χ    |                |           | 01    | Χ                | Χ  | Port I5                        |                                  |                                                      |

| 63     | 49     | -      | -      | -      | PG5                       | I/O  | <u>X</u> | X    |                |           | 01    | Χ                | Χ  | Port G5                        |                                  |                                                      |

| 64     | 50     | -      | -      | -      | PG6                       | I/O  | <u>X</u> | Χ    |                |           | 01    | Χ                | Х  | Port G6                        |                                  |                                                      |

| 65     | 51     | -      | -      | -      | PG7                       | I/O  | <u>X</u> | Χ    |                |           | 01    | Χ                | Χ  | Port G7                        |                                  |                                                      |

| 66     | 52     | -      | 1      | -      | PE4                       | I/O  | <u>X</u> | Х    | Х              |           | 01    | Χ                | Χ  | Port E4                        |                                  |                                                      |

| 67     | 53     | 37     | 1      | 1      | PE3/TIM1_BKIN             | I/O  | <u>X</u> | Х    | Х              |           | 01    | Х                | Х  | Port E3                        | Timer 1 -<br>break input         |                                                      |

| 68     | 54     | 38     | 34     | -      | PE2/I <sup>2</sup> C_SDA  | I/O  | <u>X</u> |      | Χ              |           | 01    | T <sup>(3)</sup> |    | Port E2                        | I <sup>2</sup> C data            |                                                      |

Table 9. General hardware register map

| Address                   |       | able 9. General na       |                                                  | Reset               |  |  |

|---------------------------|-------|--------------------------|--------------------------------------------------|---------------------|--|--|

| Address                   | Block | Register label           | Register name                                    | status              |  |  |

| 0x00 5050 to<br>0x00 5059 |       | ı                        | Reserved area (10 bytes)                         |                     |  |  |

| 0x00 505A                 |       | FLASH_CR1                | Flash control register 1                         | 0x00                |  |  |

| 0x00 505B                 |       | FLASH_CR2                | Flash control register 2                         | 0x00                |  |  |

| 0x00 505C                 |       | FLASH_NCR2               | Flash complementary control register 2           | 0xFF                |  |  |

| 0x00 505D                 | Flash | FLASH _FPR               | Flash protection register                        | 0x00                |  |  |

| 0x00 505E                 |       | FLASH _NFPR              | Flash complementary protection register          | 0xFF                |  |  |

| 0x00 505F                 |       | FLASH_IAPSR              | Flash in-application programming status register | 0x00                |  |  |

| 0x00 5060 to<br>0x00 5061 |       |                          | Reserved area (2 bytes)                          |                     |  |  |

| 0x00 5062                 | Flash | FLASH _PUKR              | _PUKR Flash Program memory unprotection register |                     |  |  |

| 0x00 5063                 |       |                          | Reserved area (1 byte)                           |                     |  |  |

| 0x00 5064                 | Flash | FLASH _DUKR              | 0x00                                             |                     |  |  |

| 0x00 5065 to<br>0x00 509F |       | Reserved area (59 bytes) |                                                  |                     |  |  |

| 0x00 50A0                 | ITC   | EXTI_CR1                 | External interrupt control register 1            | 0x00                |  |  |

| 0x00 50A1                 |       | EXTI_CR2                 | External interrupt control register 2            | 0x00                |  |  |

| 0x00 50A2 to<br>0x00 50B2 |       | !                        | Reserved area (17 bytes)                         |                     |  |  |

| 0x00 50B3                 | RST   | RST_SR                   | Reset status register                            | 0xXX <sup>(1)</sup> |  |  |

| 0x00 50B4 to<br>0x00 50BF |       |                          | Reserved area (12 bytes)                         |                     |  |  |

| 0x00 50C0                 | CLK   | CLK_ICKR                 | Internal clock control register                  | 0x01                |  |  |

| 0x00 50C1                 | CLK   | CLK_ECKR                 | External clock control register                  | 0x00                |  |  |

| 0x00 50C2                 |       |                          | Reserved area (1 byte)                           |                     |  |  |

| 0x00 50C3                 |       | CLK_CMSR                 | Clock master status register                     | 0xE1                |  |  |

| 0x00 50C4                 |       | CLK_SWR                  | Clock master switch register                     | 0xE1                |  |  |

| 0x00 50C5                 |       | CLK_SWCR                 | Clock switch control register                    | 0xXX                |  |  |

| 0x00 50C6                 |       | CLK_CKDIVR               | Clock divider register                           | 0x18                |  |  |

| 0x00 50C7                 | CLK   | CLK_PCKENR1              | Peripheral clock gating register 1               | 0xFF                |  |  |

| 0x00 50C8                 |       | CLK_CSSR                 | Clock security system register                   | 0x00                |  |  |

| 0x00 50C9                 |       | CLK_CCOR                 | Configurable clock control register              | 0x00                |  |  |

| 0x00 50CA                 |       | CLK_PCKENR2              | Peripheral clock gating register 2               | 0xFF                |  |  |

| 0x00 50CB                 |       | CLK_CANCCR               | CAN clock control register                       | 0x00                |  |  |

**Table 16. Current characteristics**

| Symbol                             | Ratings                                                                                                                   | Max. <sup>(1)</sup> | Unit |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------|------|

| I <sub>VDD</sub>                   | Total current into V <sub>DD</sub> power lines (source) <sup>(2)</sup>                                                    | 60                  |      |

| I <sub>VSS</sub>                   | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(2)</sup>                                                   | 60                  |      |

| 1.                                 | Output current sunk by any I/O and control pin                                                                            | 20                  |      |

| I <sub>IO</sub>                    | Output current source by any I/Os and control pin                                                                         | 20                  |      |

|                                    | Total output current sourced (sum of all I/O and control pins) for devices with two V <sub>DDIO</sub> pins <sup>(3)</sup> | 200                 |      |

| 21                                 | Total output current sourced (sum of all I/O and control pins) for devices with one $V_{DDIO}$ pin <sup>(3)</sup>         | 100                 | mA   |

| Σl <sub>IO</sub>                   | Total output current sunk (sum of all I/O and control pins) for devices with two $\rm V_{SSIO}$ pins $^{(3)}$             | 160                 | IIIA |

|                                    | Total output current sunk (sum of all I/O and control pins) for devices with one V <sub>SSIO</sub> pin <sup>(3)</sup>     | 80                  |      |

|                                    | Injected current on NRST pin                                                                                              | ±4                  |      |

| I <sub>INJ(PIN)</sub> (4)(5)       | Injected current on OSCIN pin                                                                                             | ±4                  |      |

|                                    | Injected current on any other pin <sup>(6)</sup>                                                                          | ±4                  |      |

| $\Sigma I_{\text{INJ(PIN)}}^{(4)}$ | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                                                   | ±20                 |      |

- 1. Data based on characterization results, not tested in production.

- 2. All power ( $V_{DD}$ ,  $V_{DDIO}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSIO}$ ,  $V_{SSA}$ ) pins must always be connected to the external supply.

- I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package between the V<sub>DDIO</sub>/V<sub>SSIO</sub> pins.

- $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected

- 5. Negative injection disturbs the analog performance of the device. See note in Section 10.3.10: 10-bit ADC characteristics on page 85.

- When several inputs are submitted to a current injection, the maximum  $\Sigma I_{\text{INJ(PIN)}}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with  $\Sigma I_{\text{INJ(PIN)}}$  maximum current injection on four I/O port pins of the device.

**Table 17. Thermal characteristics**

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| T <sub>J</sub>   | Maximum junction temperature | 150        | C    |

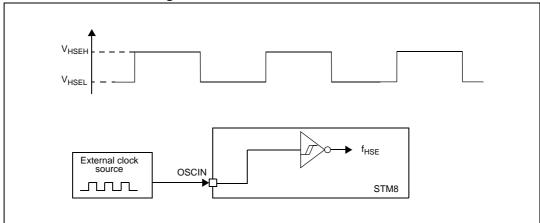

## 10.3.3 External clock sources and timing characteristics

#### **HSE** user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

Table 31. HSE user external clock characteristics

| Symbol                           | Parameter                            | Conditions                                          | Min                   | Тур | Max                     | Unit |

|----------------------------------|--------------------------------------|-----------------------------------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source frequency |                                                     | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage   |                                                     | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage    |                                                     | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage current          | V <sub>SS</sub> < V <sub>IN</sub> < V <sub>DD</sub> | -1                    |     | 1                       | μΑ   |

<sup>1.</sup> Data based on characterization results, not tested in production.

Figure 16. HSE external clock source

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

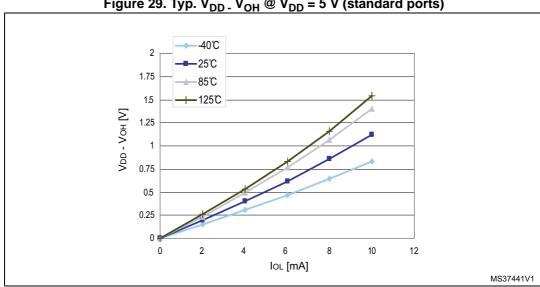

Figure 29. Typ.  $V_{DD}$  -  $V_{OH}$  @  $V_{DD}$  = 5 V (standard ports)

76/117 DocID14733 Rev 13

# 10.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\mbox{\scriptsize DD}}$  and  $T_{\mbox{\scriptsize A}}$  unless otherwise specified.

Table 41. NRST pin characteristics

| Symbol                  | Parameter                         | Conditions             | Min                   | Typ <sup>1)</sup> | Max                   | Unit |

|-------------------------|-----------------------------------|------------------------|-----------------------|-------------------|-----------------------|------|

| V <sub>IL(NRST)</sub>   | NRST Input low level voltage (1)  |                        | -0.3 V                |                   | 0.3 x V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub>   | NRST Input high level voltage (1) |                        | 0.7 x V <sub>DD</sub> |                   | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OL(NRST)</sub>   | NRST Output low level voltage (1) | I <sub>OL</sub> = 2 mA |                       |                   | 0.5                   |      |

| R <sub>PU(NRST)</sub>   | NRST Pull-up resistor (2)         |                        | 30                    | 55                | 80                    | kΩ   |

| t <sub>IFP(NRST)</sub>  | NRST Input filtered pulse (3)     |                        |                       |                   | 75                    | ns   |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse (3) |                        | 500                   |                   |                       | ns   |

| t <sub>OP(NRST)</sub>   | NRST output pulse (1)             |                        | 15                    |                   |                       | μs   |

- 1. Data based on characterization results, not tested in production.

- 2. The  $R_{\text{PU}}$  pull-up equivalent resistor is based on a resistive transistor

- 3. Data guaranteed by design, not tested in production.

Figure 33. Typical NRST  $\rm V_{IL}$  and  $\rm V_{IH}$  vs  $\rm V_{DD}$  @ 4 temperatures **-**40℃ 6 **—**25℃ <del>----</del>85℃ 5 <del>----</del>125℃ VIL - VIH [V] 2 0 2.5 6 3 3.5 4.5 5.5 VDD [V] MS37445V1

# 10.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

**Table 42. SPI characteristics**

| Symbol                                               | Parameter                    | Conditions                      | Min                      | Max                      | Unit   |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|--------|

| f <sub>SCK</sub>                                     | SDI alaak fraguanay          | Master mode                     | 0                        | 10                       | MHz    |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency          | Slave mode                      | 0                        | 6                        | IVITIZ |

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time | Capacitive load: C = 30 pF      |                          | 25                       |        |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  |                          |        |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                | Slave mode                      | 70                       |                          |        |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |        |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time        | Master mode                     | 5                        |                          |        |

| t <sub>su(SI)</sub> <sup>(1)</sup>                   | Data input setup time        | Slave mode                      | 5                        |                          |        |

| t <sub>h(MI)</sub> (1)                               | Data input hold time         | Master mode                     | 7                        |                          | ns     |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     | Data input hold time         | Slave mode                      | 10                       |                          |        |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time      | Slave mode                      |                          | 3 x t <sub>MASTER</sub>  |        |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time     | Slave mode                      | 25                       |                          |        |

| t <sub>v(SO)</sub> (1)                               | Data output valid time       | Slave mode (after enable edge)  |                          | 75                       |        |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time       | Master mode (after enable edge) |                          | 30                       |        |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data autaut hald time        | Slave mode (after enable edge)  | 31                       |                          |        |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master mode (after enable edge) | 12                       |                          |        |

<sup>1.</sup> Values based on design simulation and/or characterization results, and not tested in production.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

Figure 37. SPI timing diagram - slave mode and CPHA = 0

<sup>1.</sup> Measurement points are done at CMOS levels: 0.3  $\rm V_{DD}$  and 0.7  $\rm V_{DD.}$

SAE EMI

level

### **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

Conditions Max f<sub>HSE</sub>/f<sub>CPU</sub>(1) **Symbol** Unit **Parameter** Monitored **General conditions** 8 MHz/ 8 MHz/ 8 MHz/ frequency band 8 MHz 16 MHz 24 MHz 0.1MHz to 30 MHz 20 24  $V_{DD} = 5 V$ Peak level  $T_A = 25 \, ^{\circ}C$ 30 MHz to 130 MHz 18 21 16 dΒμV  $\mathsf{S}_{\mathsf{EMI}}$ LQFP80 package 130 MHz to 1 GHz -1 1 4 conforming to SAE IEC

Table 48. EMI data

61967-2

### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

SAE EMI level

2

2.5

2.5

## Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

Table 49. ESD absolute maximum ratings

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | T <sub>A</sub> = 25°C, conforming to JESD22-A114 | Α     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | ٧    |

<sup>1.</sup> Data based on characterization results, not tested in production.

<sup>1.</sup> Data based on characterization results, not tested in production.

# Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance:

- A supply overvoltage (applied to each power supply pin)

- A current injection (applied to each input, output and configurable I/O pin) is performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

Table 50. Electrical sensitivities

| Symbol | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------|-----------------------|-------------------------|----------------------|

|        |                       | T <sub>A</sub> = 25 °C  | Α                    |

| LU     | Static latch-up class | T <sub>A</sub> = 85 °C  | А                    |

|        |                       | T <sub>A</sub> = 125 °C | А                    |

Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

90/117 DocID14733 Rev 13

Table 51. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data<sup>(1)</sup> (continued)

| Symbol | millimeters |        |        | inches |        |        |

|--------|-------------|--------|--------|--------|--------|--------|

|        | Min         | Тур    | Max    | Min    | Тур    | Max    |

| D      | 15.800      | 16.000 | 16.200 | 0.6220 | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433 | 0.5512 | 0.5591 |

| D3     | -           | 12.350 | -      | -      | 0.4862 | -      |

| E      | 15.800      | 16.000 | 16.200 | 0.6220 | 0.6299 | 0.6378 |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433 | 0.5512 | 0.5591 |

| E3     | -           | 12.350 | -      | -      | 0.4862 | -      |

| е      | -           | 0.650  | -      | -      | 0.0256 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177 | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -      | 0.0394 | -      |

| k      | 0°          | 3.5°   | 7°     | 0°     | 3.5°   | 7°     |

| ccc    | -           | -      | 0.100  | -      | -      | 0.0039 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 44. LQFP80 recommended footprint

### 11.2 Thermal characteristics

The maximum chip junction temperature (T<sub>Jmax</sub>) must never exceed the values given in *Table 18: General operating conditions on page 56.*

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$$

#### Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance in ° C/W

- $P_{Dmax}$  is the sum of  $P_{INTmax}$  and  $P_{I/Omax}$  ( $P_{Dmax} = P_{INTmax} + P_{I/Omax}$ )

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- $P_{I/Omax}$  represents the maximum power dissipation on output pins, where:  $P_{I/Omax} = \sum (V_{OL}^*I_{OL}) + \sum ((V_{DD}^-V_{OH})^*I_{OH})$ , and taking account of the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                | Value | Unit |  |  |  |

|---------------|----------------------------------------------------------|-------|------|--|--|--|

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP 80 - 14 x 14 mm | 38    | °C/W |  |  |  |

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP 64 - 14 x 14 mm | 45    | °C/W |  |  |  |

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP 64 - 10 x 10 mm | 46    | °C/W |  |  |  |

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP 48 - 7 x 7 mm   | 57    | °C/W |  |  |  |

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP 44 - 10 x 10 mm | 54    | °C/W |  |  |  |

| $\Theta_{JA}$ | Thermal resistance junction-ambient LQFP 32 - 7 x 7 mm   | 60    | °C/W |  |  |  |

Table 57. Thermal characteristics<sup>(1)</sup>

#### 11.2.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

577

108/117 DocID14733 Rev 13

Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

# 14 Revision history

Table 58. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23-May-2008 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 05-Jun-2008 | 2        | Added part numbers on page 1 and in <i>Table 2 on page 11</i> . Updated <i>Section 4: Product overview</i> . Updated <i>Section 10: Electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 22-Jun-2008 | 3        | Added part numbers on page 1 and in Table 2 on page 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 12-Aug-2008 | 4        | Added 32 pin device pinout and ordering information. Updated UBC option description in <i>Table 13 on page 48</i> . USART renamed UART1, LINUART renamed UART3. Max. ADC frequency increased to 6 MHz.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 20-Oct-2008 | 5        | Removed STM8S207K4 part number. Removed LQFP64 14 x 14 mm package. Added medium and high density Flash memory categories. Added Section 6: Memory and register map on page 34. Replaced beCAN3 by beCAN in Section 4.14.5: beCAN. Updated Section 10: Electrical characteristics on page 52. Updated LQFP44 (Figure 53 and Table 55), and LQFP32 outline and mechanical data (Figure 56, and Table 56).                                                                                                                                                                                                |  |

| 08-Dec-2008 | 6        | Changed V <sub>DD</sub> minimum value from 3.0 to 2.95 V. Updated number of High Sink I/Os in pinout. Removed FLASH _NFPR and FLASH _FPR registers in <i>Table 9: General hardware register map</i> .                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 30-Jan-2009 | 7        | Removed preliminary status. Removed VQFN32 package. Added STM8S207C6, STM8S207S6. Updated external interrupts in <i>Table 2 on page 11</i> . Updated <i>Section 10: Electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 10-Jul-2009 | 8        | Document status changed from "preliminary data" to "datasheet".  Added LQFP64 14 x 14 mm package.  Added STM8S207M8, STM8S207SB, STM8S208R8, STM8S208R6, STM8S208C8, and STM8S208C6, STM8S208SB, STM8S208S8, and STM8S208S6.  Replaced "CAN" with "beCAN".  Added Table 3 to Section 4.5: Clock controller.  Updated Section 4.8: Auto wakeup counter.  Added beCAN peripheral (impacting Table 1 and Figure 6).  Added footnote about CAN_RX/TX to pinout figures 5, 4, and 6.  Table 6: Removed 'X' from wpu column of I <sup>2</sup> C pins (no wpu available).  Added Table 11: Interrupt mapping. |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved