Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207k6t6c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 49. | LQFP64 marking example (package top view)9                                   | 8  |

|------------|------------------------------------------------------------------------------|----|

| Figure 50. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline              | 9  |

| Figure 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint        | 0  |

| Figure 52. | LQFP48 marking example (package top view)10                                  | )1 |

| Figure 53. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package outline            | )2 |

| Figure 54. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint      | )4 |

| Figure 55. | LQFP44 marking example (package top view)10                                  | )4 |

| Figure 56. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline              | )5 |

| Figure 57. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint        | )6 |

| Figure 58. | LQFP32 marking example (package top view)10                                  | )7 |

| Figure 59. | STM8S207xx/208xx performance line ordering information scheme <sup>(1)</sup> | 2  |

| Device     | Pin count | Max. number of GPIOs<br>(I/O) | Ext. interrupt pins | Timer CAPCOM channels | Timer complementary outputs | A/D converter channels | High sink I/Os | High density Flash program memory<br>(bytes) | Data EEPROM<br>(bytes | RAM (bytes) | beCAN interface |

|------------|-----------|-------------------------------|---------------------|-----------------------|-----------------------------|------------------------|----------------|----------------------------------------------|-----------------------|-------------|-----------------|

| STM8S207MB | 80        | 68                            | 37                  | 9                     | 3                           | 16                     | 18             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S207M8 | 80        | 68                            | 37                  | 9                     | 3                           | 16                     | 18             | 64 K                                         | 2048                  | 6 K         |                 |

| STM8S207RB | 64        | 52                            | 36                  | 9                     | 3                           | 16                     | 16             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S207R8 | 64        | 52                            | 36                  | 9                     | 3                           | 16                     | 16             | 64 K                                         | 1536                  | 6 K         |                 |

| STM8S207R6 | 64        | 52                            | 36                  | 9                     | 3                           | 16                     | 16             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S207CB | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S207C8 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 64 K                                         | 1536                  | 6 K         | No              |

| STM8S207C6 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S207SB | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 128 K                                        | 1536                  | 6 K         |                 |

| STM8S207S8 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 64 K                                         | 1536                  | 6 K         |                 |

| STM8S207S6 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S207K8 | 32        | 25                            | 23                  | 8                     | 3                           | 7                      | 12             | 64 K                                         | 1024                  | 6 K         |                 |

| STM8S207K6 | 32        | 25                            | 23                  | 8                     | 3                           | 7                      | 12             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S208MB | 80        | 68                            | 37                  | 9                     | 3                           | 16                     | 18             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S208RB | 64        | 52                            | 37                  | 9                     | 3                           | 16                     | 16             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S208R8 | 64        | 52                            | 37                  | 9                     | 3                           | 16                     | 16             | 64 K                                         | 2048                  | 6 K         |                 |

| STM8S208R6 | 64        | 52                            | 37                  | 9                     | 3                           | 16                     | 16             | 32 K                                         | 2048                  | 6 K         |                 |

| STM8S208CB | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 128 K                                        | 2048                  | 6 K         | Vea             |

| STM8S208C8 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 64 K                                         | 2048                  | 6 K         | Yes             |

| STM8S208C6 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 32 K                                         | 2048                  | 6 K         |                 |

| STM8S208SB | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 128 K                                        | 1536                  | 6 K         |                 |

| STM8S208S8 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 64 K                                         | 1536                  | 6 K         |                 |

| STM8S208S6 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 32 K                                         | 1536                  | 6 K         |                 |

Table 2. STM8S20xxx performance line features

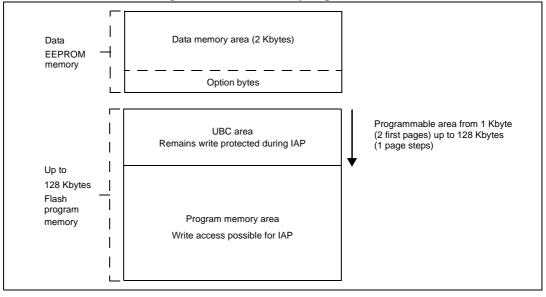

The size of the UBC is programmable through the UBC option byte (*Table 13.*), in increments of 1 page (512 bytes) by programming the UBC option byte in ICP mode.

This divides the program memory into two areas:

- Main program memory: Up to 128 Kbytes minus UBC

- User-specific boot code (UBC): Configurable up to 128 Kbytes

The UBC area remains write-protected during in-application programming. This means that the MASS keys do not unlock the UBC area. It protects the memory used to store the boot program, specific code libraries, reset and interrupt vectors, the reset routine and usually the IAP and communication routines.

#### Figure 2. Flash memory organization

#### Read-out protection (ROP)

The read-out protection blocks reading and writing the Flash program memory and data EEPROM memory in ICP mode (and debug mode). Once the read-out protection is activated, any attempt to toggle its status triggers a global erase of the program and data memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

### 4.6 **Power management**

For efficient power management, the application can be put in one of four different lowpower modes. You can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- *Wait mode*: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- **Halt mode**: In this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

# 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- 1. Timeout: At 16 MHz CPU clock the time-out period can be adjusted between 75  $\mu$ s up to 64 ms.

- 2. Refresh out of window: The downcounter is refreshed before its value is lower than the one stored in the window register.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure

The IWDG time base spans from 60  $\mu$ s to 1 s.

### 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM3 input capture channel 1 for calibration

### 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

# 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

# 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

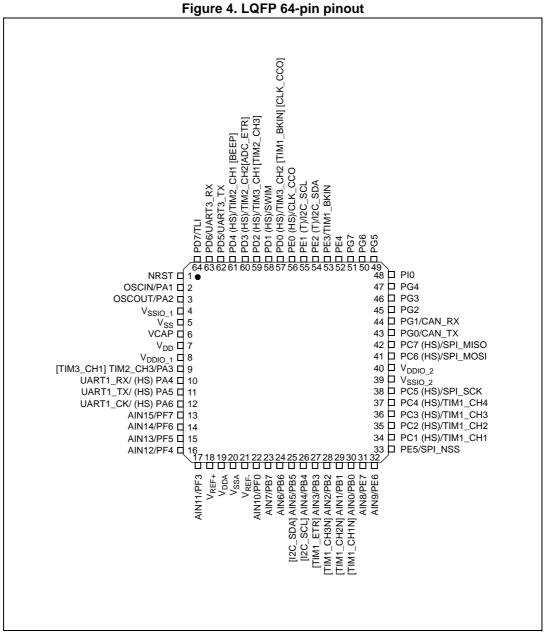

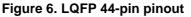

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

4. CAN\_RX and CAN\_TX is available on STM8S208xx devices only.

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to V<sub>DD</sub> not implemented).

[] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

4. CAN\_RX and CAN\_TX is available on STM8S208xx devices only.

|        | Pin    | num    | nber   |        |                |      |          | Inpu | t              |           | Out   |    |    | ,                              |                                    |                                                      |

|--------|--------|--------|--------|--------|----------------|------|----------|------|----------------|-----------|-------|----|----|--------------------------------|------------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name       | Type | floating | ndw  | Ext. interrupt | High sink | Speed | OD | ЪР | Main function<br>(after reset) | Default<br>alternate<br>function   | Alternate<br>function<br>after remap<br>[option bit] |

| 31     | 27     | 19     | 18     | 13     | PB3/AIN3       | I/O  | X        | х    | Х              |           | 01    | х  | х  | Port B3                        | Analog<br>input 3                  | TIM1_ETR<br>[AFR5]                                   |

| 32     | 28     | 20     | 19     | 14     | PB2/AIN2       | I/O  | X        | х    | х              |           | 01    | х  | х  | Port B2                        | Analog<br>input 2                  | TIM1_<br>CH3N<br>[AFR5]                              |

| 33     | 29     | 21     | 20     | 15     | PB1/AIN1       | I/O  | X        | x    | х              |           | 01    | Х  | x  | Port B1                        | Analog<br>input 1                  | TIM1_<br>CH2N<br>[AFR5]                              |

| 34     | 30     | 22     | 21     | 16     | PB0/AIN0       | I/O  | X        | х    | х              |           | 01    | Х  | х  | Port B0                        | Analog<br>input 0                  | TIM1_<br>CH1N<br>[AFR5]                              |

| 35     | -      | -      | -      | -      | PH4/TIM1_ETR   | I/O  | X        | х    |                |           | 01    | х  | х  | Port H4                        | Timer 1 -<br>trigger input         |                                                      |

| 36     | -      | -      | -      | -      | PH5/ TIM1_CH3N | I/O  | X        | х    |                |           | 01    | Х  | х  | Port H5                        | Timer 1 -<br>inverted<br>channel 3 |                                                      |

| 37     | -      | -      | -      | -      | PH6/ TIM1_CH2N | I/O  | X        | x    |                |           | 01    | х  | х  | Port H6                        | Timer 1 -<br>inverted<br>channel 2 |                                                      |

| 38     | -      | -      | -      | -      | PH7/ TIM1_CH1N | I/O  | X        | x    |                |           | 01    | х  | х  | Port H7                        | Timer 1 -<br>inverted<br>channel 2 |                                                      |

| 39     | 31     | 23     | -      | -      | PE7/AIN8       | I/O  | <u>X</u> | Х    | Х              |           | O1    | Х  | Х  | Port E7                        | Analog input 8                     |                                                      |

| 40     | 32     | 24     | 22     | -      | PE6/AIN9       | I/O  | <u>X</u> | Х    | Х              |           | 01    | Х  | Х  | Port E6                        | Analog input 9                     |                                                      |

| 41     | 33     | 25     | 23     | 17     | PE5/SPI_NSS    | I/O  | <u>x</u> | х    | х              |           | 01    | х  | х  | Port E5                        | SPI<br>master/slave<br>select      |                                                      |

| 42     | -      | -      | -      | -      | PC0/ADC_ETR    | I/O  | X        | х    | Х              |           | 01    | х  | х  | Port C0                        | ADC trigger<br>input               |                                                      |

| 43     | 34     | 26     | 24     | 18     | PC1/TIM1_CH1   | I/O  | X        | х    | Х              | HS        | O3    | х  | х  | Port C1                        | Timer 1 -<br>channel 1             |                                                      |

| 44     | 35     | 27     | 25     | 19     | PC2/TIM1_CH2   | I/O  | X        | х    | Х              | HS        | O3    | х  | х  | Port C2                        | Timer 1-<br>channel 2              |                                                      |

| 45     | 36     | 28     | 26     | 20     | PC3/TIM1_CH3   | I/O  | <u>x</u> | х    | Х              | HS        | О3    | х  | х  | Port C3                        | Timer 1 -<br>channel 3             |                                                      |

Table 6. Pin description (continued)

|        | Pin    | num    | nber   |        |                                 |      |          | Inpu     | t              |           | Out   | put              |    | -                              |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------------------|------|----------|----------|----------------|-----------|-------|------------------|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name                        | Type | floating | ndw      | Ext. interrupt | High sink | Speed | OD               | ΡР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 69     | 55     | 39     | 35     | -      | PE1/I <sup>2</sup> C_SCL        | I/O  | <u>X</u> |          | Х              |           | 01    | T <sup>(3)</sup> |    | Port E1                        | I <sup>2</sup> C clock           |                                                      |

| 70     | 56     | 40     | 36     | -      | PE0/CLK_CCO                     | I/O  | X        | Х        | Х              | HS        | O3    | х                | Х  | Port E0                        | Configurable<br>clock output     |                                                      |

| 71     | -      | -      | -      | -      | PI6                             | I/O  | <u>X</u> | Х        |                |           | 01    | Х                | Х  | Port I6                        |                                  |                                                      |

| 72     | -      | -      | -      | -      | PI7                             | I/O  | <u>X</u> | Х        |                |           | 01    | Х                | Х  | Port I7                        |                                  |                                                      |

| 73     | 57     | 41     | 37     | 25     | PD0/TIM3_CH2                    | I/O  | <u>x</u> | х        | х              | HS        | O3    | х                | х  | Port D0                        | Timer 3 -<br>channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 74     | 58     | 42     | 38     | 26     | PD1/SWIM <sup>(4)</sup>         | I/O  | х        | <u>x</u> | Х              | HS        | 04    | х                | х  | Port D1                        | SWIM data<br>interface           |                                                      |

| 75     | 59     | 43     | 39     | 27     | PD2/TIM3_CH1                    | I/O  | <u>x</u> | х        | Х              | HS        | O3    | х                | х  | Port D2                        | Timer 3 -<br>channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 76     | 60     | 44     | 40     | 28     | PD3/TIM2_CH2                    | I/O  | <u>x</u> | х        | Х              | HS        | O3    | х                | х  | Port D3                        | Timer 2 -<br>channel 2           | ADC_ETR<br>[AFR0]                                    |

| 77     | 61     | 45     | 41     | 29     | PD4/TIM2_CH1/B<br>EEP           | I/O  | X        | х        | Х              | HS        | O3    | х                | х  | Port D4                        | Timer 2 -<br>channel 1           | BEEP output<br>[AFR7]                                |

| 78     | 62     | 46     | 42     | 30     | PD5/ UART3_TX                   | I/O  | X        | х        | Х              |           | 01    | х                | х  | Port D5                        | UART3 data<br>transmit           |                                                      |

| 79     | 63     | 47     | 43     | 31     | PD6/<br>UART3_RX <sup>(1)</sup> | I/O  | X        | Х        | Х              |           | 01    | х                | х  | Port D6                        | UART3 data<br>receive            |                                                      |

| 80     | 64     | 48     | 44     | 32     | PD7/TLI                         | I/O  | X        | Х        | Х              |           | 01    | х                | х  | Port D7                        | Top level<br>interrupt           | TIM1_CH4<br>[AFR4] <sup>(5)</sup>                    |

| Table | 6.  | Pin | descri | ption ( | (continued) |  |

|-------|-----|-----|--------|---------|-------------|--|

| IUNIO | ••• |     | 400011 |         | (oonanaoa)  |  |

1. The default state of UART1\_RX and UART3\_RX pins is controlled by the ROM bootloader. These pins are pulled up as part of the bootloader activation process and returned to the floating state before a return from the bootloader.

2. The beCAN interface is available on STM8S208xx devices only

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to V<sub>DD</sub> are not implemented).

4. The PD1 pin is in input pull-up during the reset phase and after the internal reset release.

5. Available in 44-pin package only. On other packages, the AFR4 bit is reserved and must be kept at 0.

# 5.2 Alternate function remapping

As shown in the rightmost column of the pin description table, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function

remap) option bits. Refer to Section 8: Option bytes on page 47. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of the family reference manual, RM0016).

# 8 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated block of the memory. Except for the ROP (read-out protection) byte, each option byte has to be stored twice, in a regular form (OPTx) and a complemented one (NOPTx) for redundancy.

Option bytes can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in *Table 12: Option bytes* below. Option bytes can also be modified 'on the fly' by the application in IAP mode, except the ROP option that can only be modified in ICP mode (via SWIM).

Refer to the STM8S Flash programming manual (PM0051) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

| A .l.l. | Option                           | Option   |       |                                       |       | Opt     | ion bits    |               |              |                | Factory         |

|---------|----------------------------------|----------|-------|---------------------------------------|-------|---------|-------------|---------------|--------------|----------------|-----------------|

| Addr.   | name                             | byte no. | 7     | 6                                     | 5     | 4       | 3           | 2             | 1            | 0              | default setting |

| 4800h   | Read-out<br>protection<br>(ROP)  | OPT0     |       |                                       |       | R       | OP[7:0]     |               | ·            |                | 00h             |

| 4801h   | User boot                        | OPT1     |       |                                       |       | U       | BC[7:0]     |               |              |                | 00h             |

| 4802h   | code (UBC)                       | NOPT1    |       |                                       |       | NU      | JBC[7:0]    |               |              |                | FFh             |

| 4803h   | Alternate                        | OPT2     | AFR7  | AFR6                                  | AFR5  | AFR4    | AFR3        | AFR2          | AFR1         | AFR0           | 00h             |

| 4804h   | function<br>remapping<br>(AFR)   | NOPT2    | NAFR7 | NAFR6                                 | NAFR5 | NAFR4   | NAFR3       | NAFR2         | NAFR1        | NAFR0          | FFh             |

| 4805h   | Watchdog                         | OPT3     |       | Reserved LSI IWDG WWDG<br>_EN _HW _HW |       |         |             |               |              | WWDG<br>_HALT  | 00h             |

| 4806h   | option                           | NOPT3    |       | Reserved                              |       |         |             | NIWDG<br>_HW  | NWWDG<br>_HW | NWWDG<br>_HALT | FFh             |

| 4807h   | Olesk antian                     | OPT4     |       | Rese                                  | erved |         | EXT<br>CLK  | CKAWU<br>SEL  | PRS<br>C1    | PRS<br>C0      | 00h             |

| 4808h   | <ul> <li>Clock option</li> </ul> | NOPT4    |       | Rese                                  | erved |         | NEXT<br>CLK | NCKAWU<br>SEL | NPR<br>SC1   | NPR<br>SC0     | FFh             |

| 4809h   | HSE clock                        | OPT5     |       |                                       |       | HSE     | CNT[7:0]    |               |              | L              | 00h             |

| 480Ah   | startup                          | NOPT5    |       |                                       |       | NHS     | ECNT[7:0]   |               |              |                | FFh             |

| 480Bh   |                                  | OPT6     |       |                                       |       | R       | eserved     |               |              |                | 00h             |

| 480Ch   | Reserved                         | NOPT6    |       |                                       |       | R       | eserved     |               |              |                | FFh             |

| 480Dh   | Flash wait                       | OPT7     |       |                                       |       | Reserve | d           |               |              | Wait state     | 00h             |

| 480Eh   | states                           | NOPT7    |       |                                       |       | Reserve | d           |               |              | Nwait state    | FFh             |

| 487Eh   | Deatland                         | OPTBL    |       |                                       |       | E       | BL[7:0]     |               |              |                | 00h             |

| 487Fh   | Bootloader                       | NOPTBL   |       |                                       |       | N       | BL[7:0]     |               |              |                | FFh             |

#### Table 12. Option bytes

# 9 Unique ID

The devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content              |               |   |   | Uniq | ue ID bits | 6 |   |   |  |

|---------|----------------------|---------------|---|---|------|------------|---|---|---|--|

| Address | description          | 7             | 6 | 5 | 4    | 3          | 2 | 1 | 0 |  |

| 0x48CD  | X co-ordinate on the |               |   |   | U    | _ID[7:0]   |   |   |   |  |

| 0x48CE  | wafer                |               |   |   | U_   | _ID[15:8]  |   |   |   |  |

| 0x48CF  | Y co-ordinate on the | e U_ID[23:16] |   |   |      |            |   |   |   |  |

| 0x48D0  | wafer                | U_ID[31:24]   |   |   |      |            |   |   |   |  |

| 0x48D1  | Wafer number         | U_ID[39:32]   |   |   |      |            |   |   |   |  |

| 0x48D2  |                      | U_ID[47:40]   |   |   |      |            |   |   |   |  |

| 0x48D3  |                      |               |   |   | U_   | ID[55:48]  |   |   |   |  |

| 0x48D4  |                      |               |   |   | U_   | ID[63:56]  |   |   |   |  |

| 0x48D5  | Lot number           |               |   |   | U_   | ID[71:64]  |   |   |   |  |

| 0x48D6  |                      |               |   |   | U_   | ID[79:72]  |   |   |   |  |

| 0x48D7  |                      |               |   |   | U_   | ID[87:80]  |   |   |   |  |

| 0x48D8  |                      |               |   |   | U_   | ID[95:88]  |   |   |   |  |

#### Table 14. Unique ID registers (96 bits)

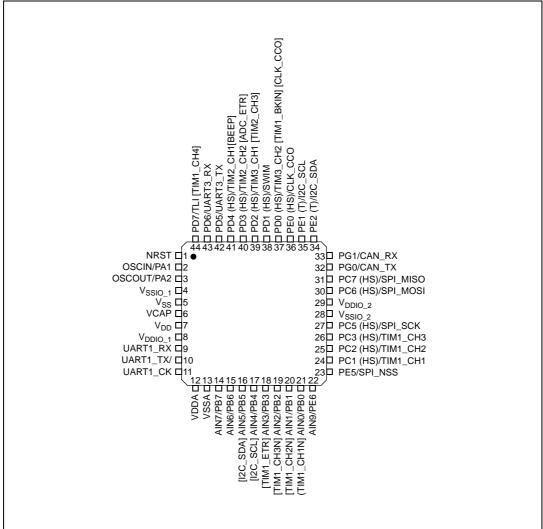

### **10.3.3** External clock sources and timing characteristics

#### HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Table 31. HSE us | ser external clock | characteristics |

|------------------|--------------------|-----------------|

|------------------|--------------------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency |                            | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      |                            | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       |                            | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    |     | 1                       | μA   |

1. Data based on characterization results, not tested in production.

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

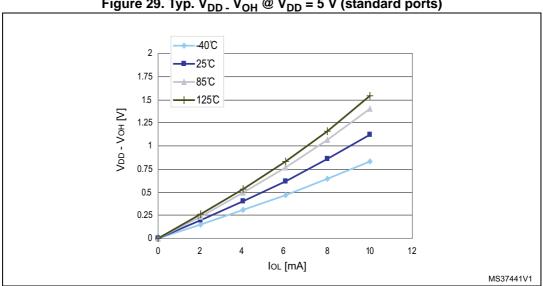

Figure 29. Typ.  $V_{DD}$  V<sub>OH</sub> @  $V_{DD}$  = 5 V (standard ports)

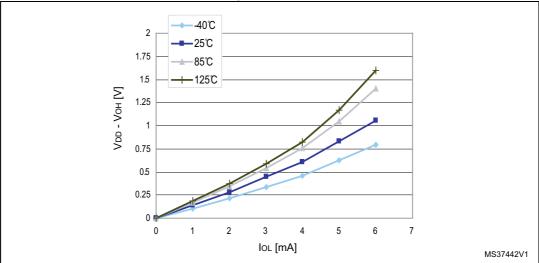

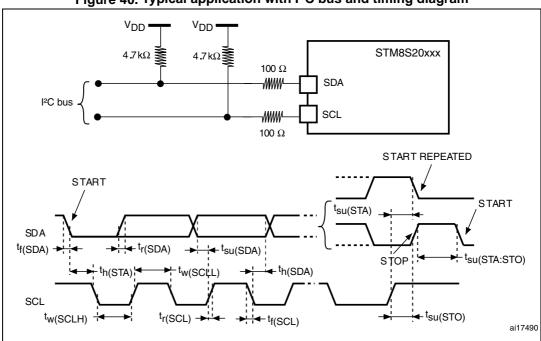

# 10.3.9 I<sup>2</sup>C interface characteristics

| Querra la cal                              | Denemation                              | Standard           | mode I <sup>2</sup> C | Fast mo            | de l <sup>2</sup> C <sup>(1)</sup> | 11   |

|--------------------------------------------|-----------------------------------------|--------------------|-----------------------|--------------------|------------------------------------|------|

| Symbol                                     | Parameter                               | Min <sup>(2)</sup> | Max <sup>(2)</sup>    | Min <sup>(2)</sup> | Max <sup>(2)</sup>                 | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                |                       | 1.3                |                                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                |                       | 0.6                |                                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                |                       | 100                |                                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>   |                       | 0 <sup>(4)</sup>   | 900 <sup>(3)</sup>                 |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                    | 1000                  |                    | 300                                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                    | 300                   |                    | 300                                |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                |                       | 0.6                |                                    |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                |                       | 0.6                |                                    | μs   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                |                       | 0.6                |                                    | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                |                       | 1.3                |                                    | μs   |

| Cb                                         | Capacitive load for each bus line       |                    | 400                   |                    | 400                                | pF   |

Table 43. I<sup>2</sup>C characteristics

1.  $f_{MASTER},$  must be at least 8 MHz to achieve max fast I^2C speed (400kHz)  $\,$

2. Data based on standard  $I^2C$  protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

Figure 40. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

#### **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

|                  |                  | Conditions                                      |                   |                 |                  |                  |      |  |  |

|------------------|------------------|-------------------------------------------------|-------------------|-----------------|------------------|------------------|------|--|--|

| Symbol           | Parameter        |                                                 | Monitored         | Max             | Unit             |                  |      |  |  |

|                  |                  | General conditions                              | frequency band    | 8 MHz/<br>8 MHz | 8 MHz/<br>16 MHz | 8 MHz/<br>24 MHz |      |  |  |

|                  |                  | V <sub>DD</sub> = 5 V<br>T <sub>A</sub> = 25 °C | 0.1MHz to 30 MHz  | 15              | 20               | 24               |      |  |  |

|                  | Peak level       |                                                 | 30 MHz to 130 MHz | 18              | 21               | 16               | dBµV |  |  |

| S <sub>EMI</sub> |                  | LQFP80 package<br>conforming to SAE IEC         | 130 MHz to 1 GHz  | -1              | 1                | 4                |      |  |  |

|                  | SAE EMI<br>level | 61967-2                                         | SAE EMI level     | 2               | 2.5              | 2.5              |      |  |  |

1. Data based on characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114  | А     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | V    |

Table 49. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

# 11.1 Package information

# 11.1.1 LQFP80 package information

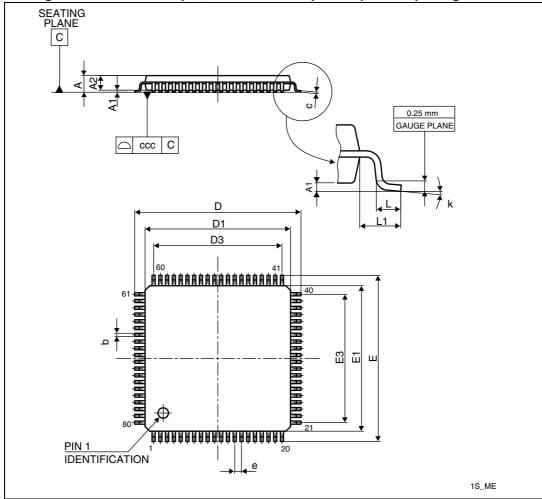

#### Figure 43. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 51. LQFP80 - 80-pin, 14 x 1 | 4 mm low-profile quad flat package mechanical |

|-----------------------------------|-----------------------------------------------|

| •                                 | data <sup>(1)</sup>                           |

| Symbol |       | millimeters |       |        | inches |        |

|--------|-------|-------------|-------|--------|--------|--------|

|        | Min   | Тур         | Max   | Min    | Тур    | Max    |

| A      | -     | -           | 1.600 | -      | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551 | 0.0571 |

| b      | 0.220 | 0.320       | 0.380 | 0.0087 | 0.0126 | 0.0150 |

| с      | 0.090 | -           | 0.200 | 0.0035 | -      | 0.0079 |

| Symbol | mm    |        | inches <sup>(1)</sup> |        |        |        |

|--------|-------|--------|-----------------------|--------|--------|--------|

|        | Min   | Тур    | Max                   | Min    | Тур    | Max    |

| D      | -     | 12.000 | -                     | -      | 0.4724 | -      |

| D1     | -     | 10.000 | -                     | -      | 0.3937 | -      |

| D3     | -     | 7.500  | -                     | -      | 0.2953 | -      |

| E      | -     | 12.000 | -                     | -      | 0.4724 | -      |

| E1     | -     | 10.000 | -                     | -      | 0.3937 | -      |

| E3     | -     | 7.500  | -                     | -      | 0.2953 | -      |

| е      | -     | 0.500  | -                     | -      | 0.0197 | -      |

| θ      | 0°    | 3.5°   | 7°                    | 0°     | 3.5°   | 7°     |

| L      | 0.450 | 0.600  | 0.750                 | 0.0177 | 0.0236 | 0.0295 |

| L1     | -     | 1.000  | -                     | -      | 0.0394 | -      |

| CCC    | -     | -      | 0.080                 | -      | -      | 0.0031 |

# Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanicaldata (continued)

1. Values in inches are converted from mm and rounded to four decimal places.

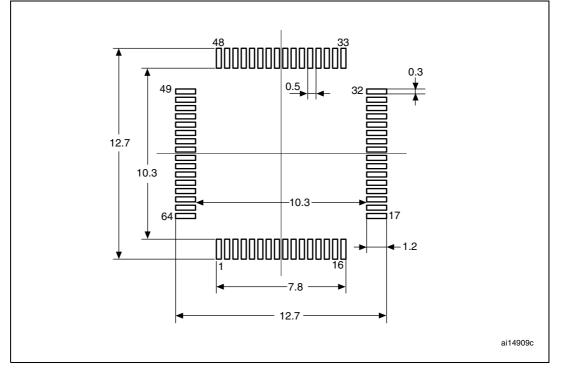

#### Figure 48. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

DocID14733 Rev 13

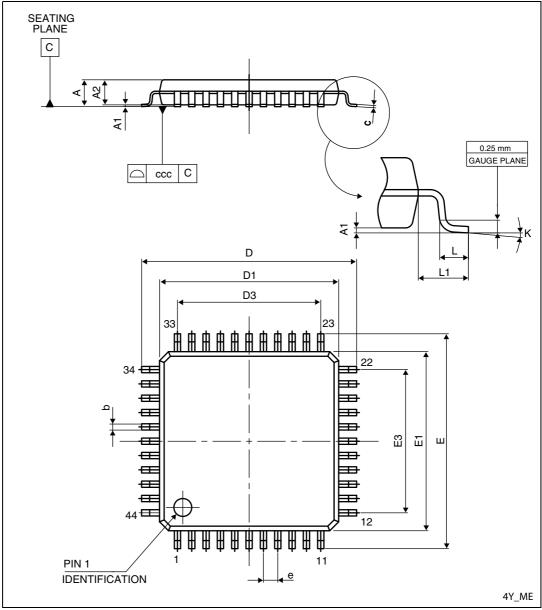

# 11.1.4 LQFP44 package information

Figure 53. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package outline