Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207k8t6c |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 49.<br>Table 50. | ESD absolute maximum ratings                                              |

|------------------------|---------------------------------------------------------------------------|

| Table 51.              | LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data |

| Table 52.              | LQFP64 - 64-pin, 14 x 14 mm low-profile quad flat package mechanical data |

| Table 53.              | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data |

| Table 54.<br>Table 55. | LQFP48 - 48-pin, 7x 7 mm low-profile quad flat package mechanical         |

| Table 56.              | data                                                                      |

| Table 50.              | data                                                                      |

| Table 57.<br>Table 58. | Thermal characteristics.    108      Document revision history    113     |

| Figure 49. | LQFP64 marking example (package top view)9                                   | 8  |

|------------|------------------------------------------------------------------------------|----|

| Figure 50. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline              | )9 |

| Figure 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint        | 0  |

| Figure 52. | LQFP48 marking example (package top view)10                                  | )1 |

| Figure 53. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package outline            | )2 |

| Figure 54. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint      | )4 |

| Figure 55. | LQFP44 marking example (package top view)10                                  | )4 |

| Figure 56. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline              | )5 |

| Figure 57. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint        | )6 |

| Figure 58. | LQFP32 marking example (package top view)10                                  | )7 |

| Figure 59. | STM8S207xx/208xx performance line ordering information scheme <sup>(1)</sup> | 2  |

## 1 Introduction

This datasheet contains the description of the STM8S20xxx features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S microcontroller family reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

## 4.12 TIM4 - 8-bit basic timer

- 8-bit autoreload, adjustable prescaler ratio to any power of 2 from 1 to 128

- Clock source: CPU clock

- Interrupt source: 1 x overflow/update

| Timer | Counter<br>size<br>(bits)        | Prescaler                      | Counting<br>mode | CAPCOM<br>channels | Complem.<br>outputs | Ext.<br>trigger | Timer<br>synchr-<br>onization/<br>chaining |

|-------|----------------------------------|--------------------------------|------------------|--------------------|---------------------|-----------------|--------------------------------------------|

| TIM1  | 16                               | Any integer from 1 to 65536    | Up/down          | 4                  | 3                   | Yes             |                                            |

| TIM2  | 16                               | Any power of 2 from 1 to 32768 | Up               | 3                  | 0                   | No              | No                                         |

| TIM3  | 16 Any power of 2 from 1 to 3276 |                                | Up               | 2                  | 0                   | No              | NU                                         |

| TIM4  | 8                                | Any power of 2 from 1 to 128   | Up               | 0                  | 0                   | No              |                                            |

### Table 4. TIM timer features

## 4.13 Analog-to-digital converter (ADC2)

STM8S20xxx performance line products contain a 10-bit successive approximation A/D converter (ADC2) with up to 16 multiplexed input channels and the following main features:

- Input voltage range: 0 to V<sub>DDA</sub>

- Dedicated voltage reference (VREF) pins available on 80 and 64-pin devices

- Conversion time: 14 clock cycles

- Single and continuous modes

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

## 4.14 Communication interfaces

The following communication interfaces are implemented:

- UART1: Full feature UART, SPI emulation, LIN2.1 master capability, Smartcard mode, IrDA mode, single wire mode.

- UART3: Full feature UART, LIN2.1 master/slave capability

- SPI: Full and half-duplex, 10 Mbit/s

- I<sup>2</sup>C: Up to 400 Kbit/s

- beCAN (rev. 2.0A,B) 3 Tx mailboxes up to 1 Mbit/s

| Туре             | I= Input, O                                                                                                                                                                            | = Output, S = Power supply                                                                                                                                |  |  |  |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Level            | Input                                                                                                                                                                                  | CM = CMOS                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|                  | Output                                                                                                                                                                                 | HS = High sink                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s                                                                                                                                                             | up to 2 MHz)<br>up to 10 MHz)<br>low programmability with slow as default state after reset<br>low programmability with fast as default state after reset |  |  |  |  |  |  |  |  |  |

| Port and control | Input                                                                                                                                                                                  | float = floating, wpu = weak pull-up                                                                                                                      |  |  |  |  |  |  |  |  |  |

| configuration    | Output                                                                                                                                                                                 | T = True open drain, OD = Open drain, PP = Push pull                                                                                                      |  |  |  |  |  |  |  |  |  |

| Reset state      | Bold $\underline{X}$ (pin state after internal reset release)<br>Unless otherwise specified, the pin state is the same during the reset phase and<br>after the internal reset release. |                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Table 5. Legend/abbreviations | for pinout table |

|-------------------------------|------------------|

|-------------------------------|------------------|

|        | Pin    | num    | ber    |        |                     |      |          | Inpu     | t              |           | Out   | put |   |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------|------|----------|----------|----------------|-----------|-------|-----|---|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name            | Type | floating | ndw      | Ext. interrupt | High sink | Speed | QO  | Ы | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | 1      | 1      | 1      | NRST                | I/O  |          | <u>X</u> |                |           |       |     |   | Reset                          |                                  |                                                      |

| 2      | 2      | 2      | 2      | 2      | PA1/OSCIN           | I/O  | <u>x</u> | х        |                |           | 01    | х   | х | Port A1                        | Resonator/<br>crystal in         |                                                      |

| 3      | 3      | 3      | 3      | 3      | PA2/OSCOUT          | I/O  | X        | х        | х              |           | 01    | х   | х | Port A2                        | Resonator/<br>crystal out        |                                                      |

| 4      | 4      | 4      | 4      | -      | V <sub>SSIO_1</sub> | S    |          |          |                |           |       |     |   | I/O groun                      | d                                |                                                      |

| 5      | 5      | 5      | 5      | 4      | V <sub>SS</sub>     | S    |          |          |                |           |       |     |   | Digital gro                    | ound                             |                                                      |

| 6      | 6      | 6      | 6      | 5      | VCAP                | S    |          |          |                |           |       |     |   | 1.8 V reg                      | ulator capacitor                 |                                                      |

| 7      | 7      | 7      | 7      | 6      | V <sub>DD</sub>     | S    |          |          |                |           |       |     |   | Digital po                     | wer supply                       |                                                      |

| 8      | 8      | 8      | 8      | 7      | V <sub>DDIO_1</sub> | S    |          |          |                |           |       |     |   | I/O powe                       | r supply                         |                                                      |

| 9      | 9      | 9      | -      | -      | PA3/TIM2_CH3        | I/O  | <u>x</u> | х        | Х              |           | 01    | х   | х | Port A3                        | Timer 2 -<br>channel3            | TIM3_CH1<br>[AFR1]                                   |

| 10     | 10     | 10     | 9      | -      | PA4/UART1_RX        | I/O  | X        | х        | Х              | HS        | O3    | х   | Х | Port A4                        | UART1<br>receive                 |                                                      |

| 11     | 11     | 11     | 10     | -      | PA5/UART1_TX        | I/O  | <u>x</u> | х        | Х              | HS        | О3    | Х   | Х | Port A5                        | UART1<br>transmit                |                                                      |

## Table 6. Pin description

|        | Pin    | num    | ber    |        |                   |      |          | Inpu | t              |           | Out   |    |    | ,                              |                                  |                                                      |

|--------|--------|--------|--------|--------|-------------------|------|----------|------|----------------|-----------|-------|----|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name          | Type | floating | ndw  | Ext. interrupt | High sink | Speed | OD | ЬР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 12     | 12     | 12     | 11     | -      | PA6/UART1_CK      | I/O  | X        | Х    | х              | HS        | О3    | х  | х  | Port A6                        | UART1<br>synchronous<br>clock    |                                                      |

| 13     | -      | -      | -      | -      | PH0               | I/O  | <u>X</u> | Х    |                | HS        | O3    | Х  | Х  | Port H0                        |                                  |                                                      |

| 14     | -      | -      | -      | -      | PH1               | I/O  | <u>X</u> | Х    |                | HS        | O3    | Х  | Х  | Port H1                        |                                  |                                                      |

| 15     | -      | -      | -      | -      | PH2               | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port H2                        |                                  |                                                      |

| 16     | -      | -      | -      | -      | PH3               | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port H3                        | A 1                              |                                                      |

| 17     | 13     | -      | -      | -      | PF7/AIN15         | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port F7                        | Analog<br>input 15               |                                                      |

| 18     | 14     | -      | -      | -      | PF6/AIN14         | I/O  | <u>X</u> | х    |                |           | 01    | Х  | Х  | Port F6                        | Analog<br>input 14               |                                                      |

| 19     | 15     | -      | -      | -      | PF5/AIN13         | I/O  | X        | х    |                |           | 01    | х  | х  | Port F5                        | Analog<br>input 13               |                                                      |

| 20     | 16     | -      | -      | 8      | PF4/AIN12         | I/O  | X        | х    |                |           | 01    | х  | х  | Port F4                        | Analog<br>input 12               |                                                      |

| 21     | 17     | -      | -      | -      | PF3/AIN11         | I/O  | X        | Х    |                |           | 01    | х  | х  | Port F3                        | Analog<br>input 11               |                                                      |

| 22     | 18     | -      | -      | -      | V <sub>REF+</sub> | s    |          |      |                |           |       |    |    | ADC pos<br>voltage             | tive reference                   |                                                      |

| 23     | 19     | 13     | 12     |        | V <sub>DDA</sub>  | S    |          |      |                |           |       |    |    | Analog p                       | ower supply                      |                                                      |

| 24     | 20     | 14     | 13     | 10     | V <sub>SSA</sub>  | S    |          |      |                |           |       |    |    | Analog gi                      | round                            |                                                      |

| 25     | 21     | -      | -      | -      | V <sub>REF-</sub> | S    |          |      |                |           |       |    |    | ADC neg<br>voltage             | ative reference                  |                                                      |

| 26     | 22     | -      | -      | -      | PF0/AIN10         | I/O  | <u>x</u> | х    |                |           | 01    | х  | х  | Port F0 Analog<br>input 10     |                                  |                                                      |

| 27     | 23     | 15     | 14     | -      | PB7/AIN7          | I/O  | X        | х    | Х              |           | 01    | х  | Х  | Port B7                        | Analog<br>input 7                |                                                      |

| 28     | 24     | 16     | 15     | -      | PB6/AIN6          | I/O  | X        | х    | Х              |           | 01    | х  | х  | Port B6                        | Analog<br>input 6                |                                                      |

| 29     | 25     | 17     | 16     | 11     | PB5/AIN5          | I/O  | <u>x</u> | х    | Х              |           | 01    | х  | х  | Port B5                        | Analog<br>input 5                | l <sup>2</sup> C_SDA<br>[AFR6]                       |

| 30     | 26     | 18     | 17     | 12     | PB4/AIN4          | I/O  | X        | х    | х              |           | 01    | х  | х  | Port B4                        | Analog<br>input 4                | I <sup>2</sup> C_SCL<br>[AFR6]                       |

Table 6. Pin description (continued)

|           |        |                                            | vare register map (continued)     | Reset  |

|-----------|--------|--------------------------------------------|-----------------------------------|--------|

| Address   | Block  | Register label                             | Register name                     | status |

| 0x00 500F |        | PD_ODR                                     | Port D data output latch register | 0x00   |

| 0x00 5010 |        | PD_IDR                                     | Port D input pin value register   | 0x00   |

| 0x00 5011 | Port D | PD_DDR                                     | Port D data direction register    | 0x00   |

| 0x00 5012 |        | PD_CR1                                     | Port D control register 1         | 0x02   |

| 0x00 5013 |        | PD_CR2                                     | Port D control register 2         | 0x00   |

| 0x00 5014 |        | PE_ODR                                     | Port E data output latch register | 0x00   |

| 0x00 5015 |        | PE_IDR                                     | Port E input pin value register   | 0x00   |

| 0x00 5016 | Port E | PE_DDR                                     | Port E data direction register    | 0x00   |

| 0x00 5017 |        | PE_CR1                                     | Port E control register 1         | 0x00   |

| 0x00 5018 |        | PE_CR2                                     | Port E control register 2         | 0x00   |

| 0x00 5019 |        | PF_ODR                                     | Port F data output latch register | 0x00   |

| 0x00 501A | Port F | PF_IDR                                     | Port F input pin value register   | 0x00   |

| 0x00 501B |        | rt F PF_DDR Port F data direction register |                                   | 0x00   |

| 0x00 501C |        | PF_CR1                                     | Port F control register 1         | 0x00   |

| 0x00 501D |        | PF_CR2                                     | Port F control register 2         | 0x00   |

| 0x00 501E |        | PG_ODR                                     | Port G data output latch register | 0x00   |

| 0x00 501F |        | PG_IDR                                     | Port G input pin value register   | 0x00   |

| 0x00 5020 | Port G | PG_DDR                                     | Port G data direction register    | 0x00   |

| 0x00 5021 |        | PG_CR1                                     | Port G control register 1         | 0x00   |

| 0x00 5022 |        | PG_CR2                                     | Port G control register 2         | 0x00   |

| 0x00 5023 |        | PH_ODR                                     | Port H data output latch register | 0x00   |

| 0x00 5024 |        | PH_IDR                                     | Port H input pin value register   | 0x00   |

| 0x00 5025 | Port H | PH_DDR                                     | Port H data direction register    | 0x00   |

| 0x00 5026 |        | PH_CR1                                     | Port H control register 1         | 0x00   |

| 0x00 5027 |        | PH_CR2                                     | Port H control register 2         | 0x00   |

| 0x00 5028 |        | PI_ODR                                     | Port I data output latch register | 0x00   |

| 0x00 5029 |        | PI_IDR                                     | Port I input pin value register   | 0x00   |

| 0x00 502A | Port I | PI_DDR                                     | Port I data direction register    | 0x00   |

| 0x00 502B |        | PI_CR1                                     | Port I control register 1         | 0x00   |

| 0x00 502C |        | PI_CR2                                     | Port I control register 2         | 0x00   |

Table 8. I/O port hardware register map (continued)

# 8 Option bytes

Option bytes contain configurations for device hardware features as well as the memory protection of the device. They are stored in a dedicated block of the memory. Except for the ROP (read-out protection) byte, each option byte has to be stored twice, in a regular form (OPTx) and a complemented one (NOPTx) for redundancy.

Option bytes can be modified in ICP mode (via SWIM) by accessing the EEPROM address shown in *Table 12: Option bytes* below. Option bytes can also be modified 'on the fly' by the application in IAP mode, except the ROP option that can only be modified in ICP mode (via SWIM).

Refer to the STM8S Flash programming manual (PM0051) and STM8 SWIM communication protocol and debug module user manual (UM0470) for information on SWIM programming procedures.

| A .l.l. | Option                           | Option   |          |                     |       | Opt     | ion bits    |               |              |                | Factory         |

|---------|----------------------------------|----------|----------|---------------------|-------|---------|-------------|---------------|--------------|----------------|-----------------|

| Addr.   | name                             | byte no. | 7        | 6                   | 5     | 4       | 3           | 2             | 1            | 0              | default setting |

| 4800h   | Read-out<br>protection<br>(ROP)  | OPT0     |          |                     |       | R       | OP[7:0]     |               | ·            |                | 00h             |

| 4801h   | User boot                        | OPT1     |          |                     |       | U       | BC[7:0]     |               |              |                | 00h             |

| 4802h   | code (UBC)                       | NOPT1    |          |                     |       | NU      | JBC[7:0]    |               |              |                | FFh             |

| 4803h   | Alternate                        | OPT2     | AFR7     | AFR6                | AFR5  | AFR4    | AFR3        | AFR2          | AFR1         | AFR0           | 00h             |

| 4804h   | function<br>remapping<br>(AFR)   | NOPT2    | NAFR7    | NAFR6               | NAFR5 | NAFR4   | NAFR3       | NAFR2         | NAFR1        | NAFR0          | FFh             |

| 4805h   | Watchdog                         | OPT3     |          | Rese                | erved |         | LSI<br>_EN  | IWDG<br>_HW   | WWDG<br>_HW  | WWDG<br>_HALT  | 00h             |

| 4806h   | option                           | NOPT3    | Reserved |                     |       |         | NLSI<br>_EN | NIWDG<br>_HW  | NWWDG<br>_HW | NWWDG<br>_HALT | FFh             |

| 4807h   | Oleale antian                    | OPT4     |          | Rese                | erved |         | EXT<br>CLK  | CKAWU<br>SEL  | PRS<br>C1    | PRS<br>C0      | 00h             |

| 4808h   | <ul> <li>Clock option</li> </ul> | NOPT4    |          | Rese                | erved |         | NEXT<br>CLK | NCKAWU<br>SEL | NPR<br>SC1   | NPR<br>SC0     | FFh             |

| 4809h   | HSE clock                        | OPT5     |          |                     |       | HSE     | CNT[7:0]    |               |              | L              | 00h             |

| 480Ah   | startup                          | NOPT5    |          |                     |       | NHS     | ECNT[7:0]   |               |              |                | FFh             |

| 480Bh   |                                  | OPT6     |          |                     |       | R       | eserved     |               |              |                | 00h             |

| 480Ch   | Reserved                         | NOPT6    |          |                     |       | R       | eserved     |               |              |                | FFh             |

| 480Dh   | Flash wait                       | OPT7     |          | Reserved Wait state |       |         |             |               |              |                |                 |

| 480Eh   | states                           | NOPT7    |          |                     |       | Reserve | d           |               |              | Nwait state    | FFh             |

| 487Eh   | Deatland                         | OPTBL    |          |                     |       | E       | BL[7:0]     |               |              |                | 00h             |

| 487Fh   | Bootloader                       | NOPTBL   |          |                     |       | N       | BL[7:0]     |               |              |                | FFh             |

#### Table 12. Option bytes

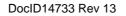

Figure 12. f<sub>CPUmax</sub> versus V<sub>DD</sub>

Table 19. Operating conditions at power-up/power-down

| Symbol                | Parameter                      | Conditions             | Min              | Тур  | Max                | Unit  |

|-----------------------|--------------------------------|------------------------|------------------|------|--------------------|-------|

| +                     | V <sub>DD</sub> rise time rate |                        | 2 <sup>(1)</sup> |      | $\infty$           | μs/V  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate |                        | 2 <sup>(1)</sup> |      | x                  | μ5/ ν |

| t <sub>TEMP</sub>     | Reset release<br>delay         | V <sub>DD</sub> rising |                  |      | 1.7 <sup>(1)</sup> | ms    |

| V <sub>IT+</sub>      | Power-on reset<br>threshold    |                        | 2.65             | 2.8  | 2.95               | V     |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold   |                        | 2.58             | 2.73 | 2.88               | V     |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis  |                        |                  | 70   |                    | mV    |

1. Guaranteed by design, not tested in production.

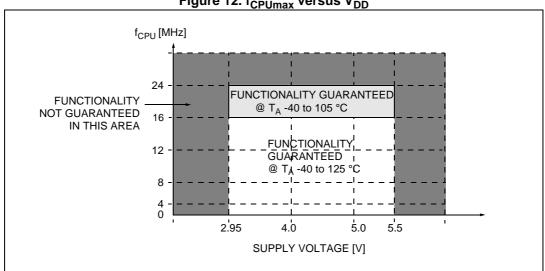

#### 10.3.1 VCAP external capacitor

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 18*. Care should be taken to limit the series inductance to less than 15 nH.

Figure 13. External capacitor CEXT

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

## **Current consumption curves**

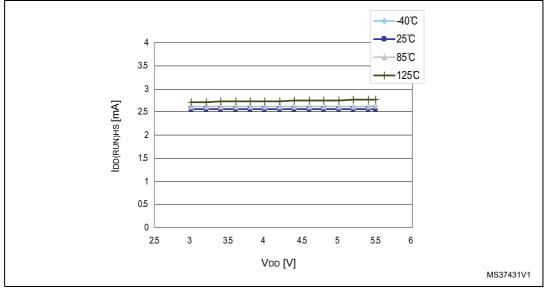

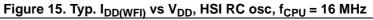

*Figure 14* and *Figure 15* show typical current consumption measured with code executing in RAM.

Figure 14. Typ. I<sub>DD(RUN)</sub> vs V<sub>DD</sub>, HSI RC osc, f<sub>CPU</sub> = 16 MHz

## Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        |            | 110 | 128 | 146              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       |            |     |     | 7 <sup>(1)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator power consumption |            |     | 5   |                  | μA   |

1. Guaranteed by design, not tested in production.

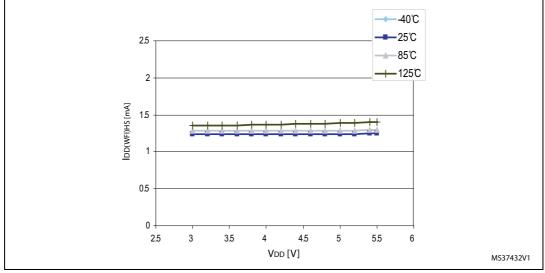

## Figure 19. Typical LSI frequency variation vs $V_{DD}$ @ 25 °C

## 10.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                               | Parameter                    | Conditions                      | Min                      | Max                      | Unit   |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|--------|

| f <sub>SCK</sub>                                     | CDL clock fraguency          | Master mode                     | 0                        | 10                       | MHz    |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency          | Slave mode                      | 0                        | 6                        | IVITIZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>           | SPI clock rise and fall time | Capacitive load: C = 30 pF      |                          | 25                       |        |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  |                          |        |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                | Slave mode                      | 70                       |                          |        |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |        |

| t <sub>su(MI)</sub> (1)                              | Data input actua tima        | Master mode                     | 5                        |                          |        |

| t <sub>su(SI)</sub> (1)                              | Data input setup time        | Slave mode                      | 5                        |                          |        |

| t <sub>h(MI)</sub> (1)                               | Data input hold time         | Master mode                     | 7                        |                          | ns     |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     |                              | Slave mode                      | 10                       |                          |        |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time      | Slave mode                      |                          | 3 x t <sub>MASTER</sub>  |        |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>               | Data output disable time     | Slave mode                      | 25                       |                          |        |

| t <sub>v(SO)</sub> <sup>(1)</sup>                    | Data output valid time       | Slave mode (after enable edge)  |                          | 75                       |        |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time       | Master mode (after enable edge) |                          | 30                       |        |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data autaut hald time        | Slave mode (after enable edge)  | 31                       |                          |        |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master mode (after enable edge) | 12                       |                          |        |

1. Values based on design simulation and/or characterization results, and not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

| Symbol         | Parameter                                   | Conditions                | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|---------------------------|-----|--------------------|------|

|                |                                             | $f_{ADC} = 2 \text{ MHz}$ | 1   | 2.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz  | 1.4 | 3                  |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 1.6 | 3.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.6 | 2                  |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz  | 1.1 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 1.2 | 2.5                |      |

|                | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz  | 0.2 | 2                  |      |

| E <sub>G</sub> |                                             | f <sub>ADC</sub> = 4 MHz  | 0.6 | 2.5                | LSB  |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.8 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz  | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.8 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.6 | 1.5                |      |

| E <sub>L</sub> | Integral linearity error (2)                | $f_{ADC} = 4 \text{ MHz}$ | 0.6 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.6 | 1.5                |      |

| Table 45. ADC accuracy | y with R <sub>AIN</sub> < 10 | ) $\mathbf{k}\Omega$ , $\mathbf{V}_{\mathbf{DDA}} = 5 \mathbf{V}$ |

|------------------------|------------------------------|-------------------------------------------------------------------|

|------------------------|------------------------------|-------------------------------------------------------------------|

1. Data based on characterization results for LQFP80 device with  $V_{REF+}/V_{REF-}$ , not tested in production.

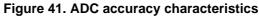

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 10.3.6 does not affect the ADC accuracy.

| Symbol         | Parameter                                                    | Conditions                | Тур | Max <sup>(1)</sup> | Unit |

|----------------|--------------------------------------------------------------|---------------------------|-----|--------------------|------|

|                | Total unadjusted error <sup>(2)</sup>                        | $f_{ADC} = 2 MHz$         | 1.1 | 2                  |      |

| E <sub>T</sub> |                                                              | f <sub>ADC</sub> = 4 MHz  | 1.6 | 2.5                |      |

| IEal           | E <sub>O</sub>   Offset error <sup>(2)</sup>                 | $f_{ADC} = 2 MHz$         | 0.7 | 1.5                |      |

| IFOI           |                                                              | f <sub>ADC</sub> = 4 MHz  | 1.3 | 2                  |      |

|                | Gain error <sup>(2)</sup>                                    | f <sub>ADC</sub> = 2 MHz  | 0.2 | 1.5                | LSB  |

| E <sub>G</sub> | Gainenoi                                                     | $f_{ADC} = 4 \text{ MHz}$ | 0.5 | 2                  | LSD  |

|                | E <sub>D</sub>   Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 2 MHz  | 0.7 | 1                  |      |

| E <sub>D</sub> |                                                              | f <sub>ADC</sub> = 4 MHz  | 0.7 | 1                  |      |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>                      | $f_{ADC} = 2 MHz$         | 0.6 | 1.5                |      |

| וברו           |                                                              | f <sub>ADC</sub> = 4 MHz  | 0.6 | 1.5                |      |

| Table 46. ADC accuracy | with $R_{AIN}$ < 10 k $\Omega$ | $R_{AIN}, V_{DDA} = 3.3 V$ |

|------------------------|--------------------------------|----------------------------|

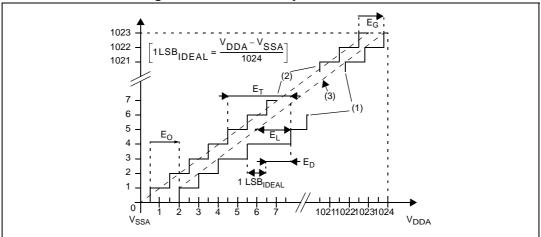

1. Example of an actual transfer curve.

- 2. The ideal transfer curve

- 3.

End point correlation line  $E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_0$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.  $E_D$  = Differential linearity error: maximum deviation between actual steps and the ideal one.  $E_L$  = Integral linearity error: maximum deviation between any actual transition and the end point correlation between any actual transition and the end point correlation line.

## 10.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                                    | Level/class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD} = 5 V$ , $T_A = 25 °C$ ,<br>$f_{MASTER} = 16 MHz$ ,<br>conforming to IEC 61000-4-2                    | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 5 \text{ V}, T_A = 25 \text{ °C},$<br>$f_{MASTER} = 16 \text{ MHz},$<br>conforming to IEC 61000-4-4 | 4A          |

| Table | 47.          | EMS | data |

|-------|--------------|-----|------|

| Table | <b>T</b> / . |     | uuu  |

## **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

| Symbol           |                  | Conditions                                      |                             |                                                       |                  |                  |      |

|------------------|------------------|-------------------------------------------------|-----------------------------|-------------------------------------------------------|------------------|------------------|------|

|                  | Parameter        | General conditions                              | Monitored<br>frequency band | Max f <sub>HSE</sub> /f <sub>CPU</sub> <sup>(1)</sup> |                  |                  | Unit |

|                  |                  |                                                 |                             | 8 MHz/<br>8 MHz                                       | 8 MHz/<br>16 MHz | 8 MHz/<br>24 MHz |      |

|                  |                  | V <sub>DD</sub> = 5 V<br>T <sub>A</sub> = 25 °C | 0.1MHz to 30 MHz            | 15                                                    | 20               | 24               | dBµV |

|                  | Peak level       |                                                 | 30 MHz to 130 MHz           | 18                                                    | 21               | 16               |      |

| S <sub>EMI</sub> |                  | LQFP80 package                                  |                             | -1                                                    | 1                | 4                |      |

|                  | SAE EMI<br>level | conforming to SAE IEC<br>61967-2                | SAE EMI level               | 2                                                     | 2.5              | 2.5              |      |

1. Data based on characterization results, not tested in production.

## Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114  | А     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | V    |

Table 49. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

# 11 Package characteristics

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at *www.st.com*. ECOPACK® is an ST trademark.

### **Device marking**

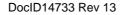

The following figure shows the marking for the LQFP48 package.

Figure 52. LQFP48 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Date        | Revision    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Jul-2009 | 8<br>cont'd | Section 10: Electrical characteristics: Added data for TBD values;<br>updated Table 15: Voltage characteristics and Table 18: General<br>operating conditions; updated VCAP specifications in Table 18 and<br>in Section 10.3.1: VCAP external capacitor, updated Figure 18;<br>replaced Figure 19; updated Table 35: RAM and hardware registers;<br>updated Figure 22 and Figure 35; added Figure 40: Typical<br>application with I2C bus and timing diagram.<br>Removed Table 56: Junction temperature range.<br>Added link between ordering information Figure 59 and STM8S20xx<br>features Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13-Apr-2010 | 9           | Document status changed from "preliminary data" to "datasheet".<br><i>Table 2: STM8S20xxx performance line features</i> : high sink I/O for<br>STM8S207C8 is 16 (not 13).<br><i>Table 3: Peripheral clock gating bit assignments in</i><br><i>CLK_PCKENR1/2 registers</i> : updated bit positions for TIM2 and<br>TIM3.<br><i>Figure 5: LQFP 48-pin pinout</i> : added CAN_TX and CAN_RX to pins<br>35 and 36; noted that these pins are available only in STM8S208xx<br>devices.<br><i>Figure 7: LQFP 32-pin pinout</i> : replaced uart2 with uart3.<br><i>Table 6: Pin description</i> : added footnotes concerning beCAN<br>availability and UART1_RX and UART3_RX pins.<br><i>Table 13: Option byte description</i> : added description of STM8L<br>bootloader option bytes to the option byte description table.<br>Added <i>Section 9: Unique ID</i> (and listed this attribute in <i>Features</i> ).<br><i>Section 10.3: Operating conditions</i> : replaced "C <sub>EXT</sub> " with "VCAP"<br>and added data for ESR and ESL; removed "low power dissipation"<br>condition for T <sub>A</sub> .<br><i>Table 26: Total current consumption in halt mode at VDD = 5 V</i> :<br>replaced max value of I <sub>DD(H)</sub> at 85 °C from 30 µA to 35 µA for the<br>condition "Flash in power-down mode, HSI clock after wakeup".<br><i>Table 33: HSI oscillator characteristics</i> : updated the ACC <sub>HSI</sub> factory<br>calibrated values.<br><i>Functional EMS (electromagnetic susceptibility)</i> and <i>Table 47</i> :<br>replaced "IEC 1000" with "IEC 61000".<br><i>Electromagnetic interference (EMI)</i> and <i>Table 48</i> : replaced "SAE<br>J1752/3" with "IEC 61967-2".<br><i>Table 57: Thermal characteristics</i> : changed the thermal resistance<br>junction-ambient value of LQFP32 (7x7 mm) from 59 °C/W to 60<br>°C/W. |

Table 58. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-Sep-2010 | 10       | Added part number STM8S208M8 to <i>Table 1: Device summary</i> .<br>Updated "reset state" of <i>Table 5: Legend/abbreviations for pinout</i><br><i>table</i> .<br>Added footnote <i>4</i> to <i>Table 6: Pin description</i> .<br><i>Table 9: General hardware register map</i> : standardized all reset state<br>values; updated the reset state values of RST_SR, CLK_SWCR,<br>CLK_HSITRIMR, CLK_SWIMCCR, IWDG_KR, and ADC_DRx<br>registers; added the reset values of the CAN paged registers.<br><i>Figure 36: Recommended reset pin protection</i> : replaced 0.01 μF with<br>0.1 μF.<br><i>Figure 40: Typical application with I2C bus and timing diagram</i> :<br>t <sub>w</sub> (SCKH), t <sub>w</sub> (SCKL), t <sub>r</sub> (SCK), and t <sub>f</sub> (SCK) replaced by t <sub>w</sub> (SCLH), t <sub>w</sub> (SCLL),<br>t <sub>r</sub> (SCL), and t <sub>f</sub> (SCL) respectively. |

| 22-Mar-2011 | 11       | Table 1: Device summary: added STM8S207K8.         Table 2: STM8S20xxx performance line features: added         STM8S207K8 device and changed the RAM value of all other         devices to 6 Kbytes.         Figure 5, Figure 4, Figure 5, and Figure 7: removed TIM1_CH4 from         pins 80, 64, 48, and 32 respectively.         Table 6: Pin description: updated note 3 and added note 5.         Table 9: General hardware register map: removed I2C_PECR         register.         Section 10.3.7: Reset pin characteristics: added text regarding the         rest network.                                                                                                                                                                                                                                                                                                           |

| 10-Feb-2012 | 12       | <i>Figure 1: STM8S20xxx block diagram</i> : updated POR/PDR and BOR;<br>updated LINUART input; added legend.<br><i>Table 18: General operating conditions</i> : updated V <sub>CAP</sub> .<br><i>Table 26: Total current consumption in halt mode at VDD = 5 V</i> :<br>updated title, modified existing max column, and added new max<br>column (at 125 °C) with data.<br><i>Table 37: I/O static characteristics</i> : added new condition and new<br>max values for rise and fall time; added footnote <i>3</i> ; updated Typ and<br>max pull-up resistor values.<br><i>Section 10.3.7: Reset pin characteristics</i> : updated cross reference in<br>text below <i>Figure 35</i><br><i>Table 41: NRST pin characteristics</i> : updated Typ and max values of<br>the NRST pull-up resistor.                                                                                                 |