Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | STM8                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 24MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 68                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 6K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-LQFP                                                                 |

| Supplier Device Package    | 80-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207m8t3btr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet contains the description of the STM8S20xxx features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S microcontroller family reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

### 4.14.1 UART1

#### **Main features**

- One Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- Single wire half duplex mode

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

#### LIN master mode

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

#### 4.14.2 UART3

#### Main features

- 1 Mbit/s full duplex SCI

- LIN master capable

- High precision baud rate generator

|        | Pin    | num    | ber    |        |                   |      |          | Inpu | t              |           | Out   |    |    | ,                              |                                  |                                                      |

|--------|--------|--------|--------|--------|-------------------|------|----------|------|----------------|-----------|-------|----|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name          | Type | floating | ndw  | Ext. interrupt | High sink | Speed | OD | ЬР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 12     | 12     | 12     | 11     | -      | PA6/UART1_CK      | I/O  | X        | Х    | х              | HS        | О3    | х  | х  | Port A6                        | UART1<br>synchronous<br>clock    |                                                      |

| 13     | -      | -      | -      | -      | PH0               | I/O  | <u>X</u> | Х    |                | HS        | O3    | Х  | Х  | Port H0                        |                                  |                                                      |

| 14     | -      | -      | -      | -      | PH1               | I/O  | <u>X</u> | Х    |                | HS        | O3    | Х  | Х  | Port H1                        |                                  |                                                      |

| 15     | -      | -      | -      | -      | PH2               | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port H2                        |                                  |                                                      |

| 16     | -      | -      | -      | -      | PH3               | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port H3                        | A 1                              |                                                      |

| 17     | 13     | -      | -      | -      | PF7/AIN15         | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port F7                        | Analog<br>input 15               |                                                      |

| 18     | 14     | -      | -      | -      | PF6/AIN14         | I/O  | <u>X</u> | х    |                |           | 01    | Х  | х  | Port F6                        | Analog<br>input 14               |                                                      |

| 19     | 15     | -      | -      | -      | PF5/AIN13         | I/O  | X        | х    |                |           | 01    | х  | х  | Port F5                        | Analog<br>input 13               |                                                      |

| 20     | 16     | -      | -      | 8      | PF4/AIN12         | I/O  | X        | х    |                |           | 01    | х  | х  | Port F4                        | Analog<br>input 12               |                                                      |

| 21     | 17     | -      | -      | -      | PF3/AIN11         | I/O  | X        | Х    |                |           | 01    | х  | х  | Port F3                        | Analog<br>input 11               |                                                      |

| 22     | 18     | -      | -      | -      | V <sub>REF+</sub> | s    |          |      |                |           |       |    |    | ADC positive reference voltage |                                  |                                                      |

| 23     | 19     | 13     | 12     |        | V <sub>DDA</sub>  | S    |          |      |                |           |       |    |    | Analog p                       | ower supply                      |                                                      |

| 24     | 20     | 14     | 13     | 10     | V <sub>SSA</sub>  | S    |          |      |                |           |       |    |    | Analog gi                      | round                            |                                                      |

| 25     | 21     | -      | -      | -      | V <sub>REF-</sub> | S    |          |      |                |           |       |    |    | ADC negative reference voltage |                                  |                                                      |

| 26     | 22     | -      | -      | -      | PF0/AIN10         | I/O  | <u>x</u> | х    |                |           | 01    | х  | х  | Port F0                        | Analog<br>input 10               |                                                      |

| 27     | 23     | 15     | 14     | -      | PB7/AIN7          | I/O  | X        | х    | Х              |           | 01    | х  | Х  | Port B7                        | Analog<br>input 7                |                                                      |

| 28     | 24     | 16     | 15     | -      | PB6/AIN6          | I/O  | X        | х    | Х              |           | 01    | х  | х  | Port B6                        | Analog<br>input 6                |                                                      |

| 29     | 25     | 17     | 16     | 11     | PB5/AIN5          | I/O  | <u>x</u> | х    | Х              |           | 01    | х  | х  | Port B5                        | Analog<br>input 5                | l <sup>2</sup> C_SDA<br>[AFR6]                       |

| 30     | 26     | 18     | 17     | 12     | PB4/AIN4          | I/O  | X        | х    | х              |           | 01    | х  | х  | Port B4                        | Analog<br>input 4                | I <sup>2</sup> C_SCL<br>[AFR6]                       |

Table 6. Pin description (continued)

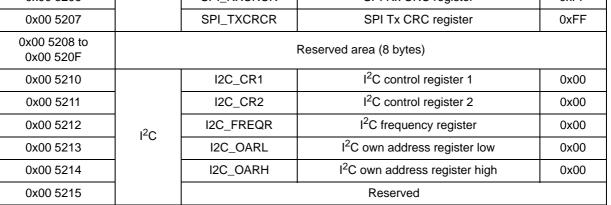

| Table 9. General hardware register map (continued) |          |                          |                                            |                     |  |  |  |  |  |

|----------------------------------------------------|----------|--------------------------|--------------------------------------------|---------------------|--|--|--|--|--|

| Address                                            | Block    | Register label           | Register name                              | Reset<br>status     |  |  |  |  |  |

| 0x00 50CC                                          |          | CLK_HSITRIMR             | HSI clock calibration trimming register    | 0x00                |  |  |  |  |  |

| 0x00 50CD                                          | CLK      | CLK_SWIMCCR              | SWIM clock control register                | 0bXXXX<br>XXX0      |  |  |  |  |  |

| 0x00 50CE to<br>0x00 50D0                          |          | Reserved area (3 bytes)  |                                            |                     |  |  |  |  |  |

| 0x00 50D1                                          | WWDG     | WWDG_CR                  | WWDG control register                      | 0x7F                |  |  |  |  |  |

| 0x00 50D2                                          | - www.DG | WWDG_WR                  | WWDR window register                       | 0x7F                |  |  |  |  |  |

| 0x00 50D3 to<br>0x00 50DF                          |          | Reserved area (13 bytes) |                                            |                     |  |  |  |  |  |

| 0x00 50E0                                          |          | IWDG_KR                  | IWDG key register                          | 0xXX <sup>(2)</sup> |  |  |  |  |  |

| 0x00 50E1                                          | IWDG     | IWDG_PR                  | IWDG prescaler register                    | 0x00                |  |  |  |  |  |

| 0x00 50E2                                          |          | IWDG_RLR                 | IWDG reload register                       | 0xFF                |  |  |  |  |  |

| 0x00 50E3 to<br>0x00 50EF                          |          | Reserved area (13 bytes) |                                            |                     |  |  |  |  |  |

| 0x00 50F0                                          |          | AWU_CSR1                 | AWU control/status register 1              | 0x00                |  |  |  |  |  |

| 0x00 50F1                                          | AWU      | AWU_APR                  | AWU asynchronous prescaler buffer register | 0x3F                |  |  |  |  |  |

| 0x00 50F2                                          |          | AWU_TBR                  | AWU timebase selection register            | 0x00                |  |  |  |  |  |

| 0x00 50F3                                          | BEEP     | BEEP_CSR                 | BEEP control/status register               | 0x1F                |  |  |  |  |  |

| 0x00 50F4 to<br>0x00 50FF                          |          |                          | Reserved area (12 bytes)                   |                     |  |  |  |  |  |

| 0x00 5200                                          |          | SPI_CR1                  | SPI control register 1                     | 0x00                |  |  |  |  |  |

| 0x00 5201                                          |          | SPI_CR2                  | SPI control register 2                     | 0x00                |  |  |  |  |  |

| 0x00 5202                                          |          | SPI_ICR                  | SPI interrupt control register             | 0x00                |  |  |  |  |  |

| 0x00 5203                                          | SPI      | SPI_SR                   | SPI status register                        | 0x02                |  |  |  |  |  |

| 0x00 5204                                          | 551      | SPI_DR                   | SPI data register                          | 0x00                |  |  |  |  |  |

| 0x00 5205                                          |          | SPI_CRCPR                | SPI CRC polynomial register                | 0x07                |  |  |  |  |  |

| 0x00 5206                                          |          | SPI_RXCRCR               | SPI Rx CRC register                        | 0xFF                |  |  |  |  |  |

| 0x00 5207                                          |          | SPI_TXCRCR               | SPI Tx CRC register                        | 0xFF                |  |  |  |  |  |

| 0x00 5208 to<br>0x00 520F                          |          |                          | Reserved area (8 bytes)                    |                     |  |  |  |  |  |

| 0x00 5210                                          |          | I2C_CR1                  | I <sup>2</sup> C control register 1        | 0x00                |  |  |  |  |  |

| 0x00 5211                                          |          | 12C CR2                  | I <sup>2</sup> C control register 2        | 0x00                |  |  |  |  |  |

| Address                   | Block   | Register label            | Register name        | Reset<br>status     |  |  |  |

|---------------------------|---------|---------------------------|----------------------|---------------------|--|--|--|

| 0x00 5428                 |         | CAN_P0                    | CAN paged register 0 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5429                 |         | CAN_P1                    | CAN paged register 1 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 542A                 |         | CAN_P2                    | CAN paged register 2 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 542B                 | _       | CAN_P3                    | CAN paged register 3 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 542C                 | _       | CAN_P4                    | CAN paged register 4 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 542D                 | _       | CAN_P5                    | CAN paged register 5 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 542E                 | _       | CAN_P6                    | CAN paged register 6 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 542F                 |         | CAN_P7                    | CAN paged register 7 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5430                 | - beCAN | CAN_P8                    | CAN paged register 8 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5431                 | _       | CAN_P9                    | CAN paged register 9 | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5432                 | _       | CAN_PA                    | CAN paged register A | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5433                 | -       | CAN_PB                    | CAN paged register B | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5434                 | _       | CAN_PC                    | CAN paged register C | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5435                 | _       | CAN_PD                    | CAN paged register D | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5436                 | 1       | CAN_PE                    | CAN paged register E | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5437                 |         | CAN_PF                    | CAN paged register F | 0xXX <sup>(3)</sup> |  |  |  |

| 0x00 5438 to<br>0x00 57FF |         | Reserved area (968 bytes) |                      |                     |  |  |  |

| Table 0  | Gonoral | hardwaro | rogistor | man | (continued) |   |

|----------|---------|----------|----------|-----|-------------|---|

| Table 9. | General | naruware | register | map | (continued) | , |

1. Depends on the previous reset source.

2. Write only register.

3. If the bootloader is enabled, it is initialized to 0x00.

7 Interrupt vector mapping

| Table 11. Interrupt mapping |                  |                                                  |                          |                                 |                           |  |  |  |

|-----------------------------|------------------|--------------------------------------------------|--------------------------|---------------------------------|---------------------------|--|--|--|

| IRQ<br>no.                  | Source<br>block  | Description                                      | Wakeup from<br>Halt mode | Wakeup from<br>Active-halt mode | Vector address            |  |  |  |

|                             | RESET            | Reset                                            | Yes                      | Yes                             | 0x00 8000                 |  |  |  |

|                             | TRAP             | Software interrupt                               | -                        | -                               | 0x00 8004                 |  |  |  |

| 0                           | TLI              | External top level interrupt                     | -                        | -                               | 0x00 8008                 |  |  |  |

| 1                           | AWU              | Auto wake up from halt                           | -                        | Yes                             | 0x00 800C                 |  |  |  |

| 2                           | CLK              | Clock controller                                 | -                        | -                               | 0x00 8010                 |  |  |  |

| 3                           | EXTI0            | Port A external interrupts                       | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>              | 0x00 8014                 |  |  |  |

| 4                           | EXTI1            | Port B external interrupts                       | Yes                      | Yes                             | 0x00 8018                 |  |  |  |

| 5                           | EXTI2            | Port C external interrupts                       | Yes                      | Yes                             | 0x00 801C                 |  |  |  |

| 6                           | EXTI3            | Port D external interrupts                       | Yes                      | Yes                             | 0x00 8020                 |  |  |  |

| 7                           | EXTI4            | Port E external interrupts                       | Yes                      | Yes                             | 0x00 8024                 |  |  |  |

| 8                           | beCAN            | beCAN RX interrupt                               | Yes                      | Yes                             | 0x00 8028                 |  |  |  |

| 9                           | beCAN            | beCAN TX/ER/SC interrupt                         | -                        | -                               | 0x00 802C                 |  |  |  |

| 10                          | SPI              | End of transfer                                  | Yes                      | Yes                             | 0x00 8030                 |  |  |  |

| 11                          | TIM1             | TIM1 update/overflow/underflow/<br>trigger/break | -                        | -                               | 0x00 8034                 |  |  |  |

| 12                          | TIM1             | TIM1 capture/compare                             | -                        | -                               | 0x00 8038                 |  |  |  |

| 13                          | TIM2             | TIM2 update /overflow                            | -                        | -                               | 0x00 803C                 |  |  |  |

| 14                          | TIM2             | TIM2 capture/compare                             | -                        | -                               | 0x00 8040                 |  |  |  |

| 15                          | TIM3             | Update/overflow                                  | -                        | -                               | 0x00 8044                 |  |  |  |

| 16                          | TIM3             | Capture/compare                                  | -                        | -                               | 0x00 8048                 |  |  |  |

| 17                          | UART1            | Tx complete                                      | -                        | -                               | 0x00 804C                 |  |  |  |

| 18                          | UART1            | Receive register DATA FULL                       | -                        | -                               | 0x00 8050                 |  |  |  |

| 19                          | l <sup>2</sup> C | I <sup>2</sup> C interrupt                       | Yes                      | Yes                             | 0x00 8054                 |  |  |  |

| 20                          | UART3            | Tx complete                                      | -                        | -                               | 0x00 8058                 |  |  |  |

| 21                          | UART3            | Receive register DATA FULL                       | -                        | -                               | 0x00 805C                 |  |  |  |

| 22                          | ADC2             | ADC2 end of conversion                           | -                        | -                               | 0x00 8060                 |  |  |  |

| 23                          | TIM4             | TIM4 update/overflow                             | -                        | -                               | 0x00 8064                 |  |  |  |

| 24                          | Flash            | EOP/WR_PG_DIS                                    | -                        | -                               | 0x00 8068                 |  |  |  |

|                             |                  | Reserved                                         |                          |                                 | 0x00 806C to<br>0x00 807C |  |  |  |

#### Table 11. Interrupt mapping

1. Except PA1

|                 | Table 13. Option byte description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OPT0            | <b>ROP[7:0]</b> <i>Memory readout protection (ROP)</i><br>0xAA: Enable readout protection (write access via SWIM protocol)<br>Note: Refer to the family reference manual (RM0016) section on<br>Flash/EEPROM memory readout protection for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OPT1            | UBC[7:0] User boot code area<br>0x00: no UBC, no write-protection<br>0x01: Pages 0 to 1 defined as UBC, memory write-protected<br>0x02: Pages 0 to 3 defined as UBC, memory write-protected<br>0x03: Pages 0 to 4 defined as UBC, memory write-protected<br><br>0xFE: Pages 0 to 255 defined as UBC, memory write-protected<br>0xFF: Reserved<br>Note: Refer to the family reference manual (RM0016) section on<br>Flash/EEPROM write protection for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OPT2            | <ul> <li>AFR7<i>Alternate function remapping option 7</i></li> <li>0: Port D4 alternate function = TIM2_CH1</li> <li>1: Port D4 alternate function = BEEP</li> <li>AFR6 <i>Alternate function remapping option 6</i></li> <li>0: Port B5 alternate function = AIN5, port B4 alternate function = AIN4</li> <li>1: Port B5 alternate function = l<sup>2</sup>C_SDA, port B4 alternate function = l<sup>2</sup>C_SCL</li> <li>AFR5 <i>Alternate function remapping option 5</i></li> <li>0: Port B3 alternate function = AIN3, port B2 alternate function = AIN2, port B1 alternate function = AIN1, port B0 alternate function = AIN0</li> <li>1: Port B3 alternate function = TIM1_ETR, port B2 alternate function = TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate function = TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate function = TIM1_CH1N</li> <li>AFR4 <i>Alternate function remapping option 4</i></li> <li>0: Port D7 alternate function = TIM1_CH4</li> <li>AFR3 <i>Alternate function remapping option 3</i></li> <li>0: Port D0 alternate function = TIM3_CH2</li> <li>1: Port D0 alternate function = TIM3_CH2</li> <li>1: Port D0 alternate function = CLK_CCO</li> <li>Note: AFR2 option has priority over AFR3 if both are activated</li> <li>AFR1 <i>Alternate function remapping option 1</i></li> <li>0: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH3</li> <li>AFR0 <i>Alternate function remapping option 1</i></li> <li>0: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH3</li> <li>AFR0 <i>Alternate function remapping option 0</i></li> <li>0: Port D3 alternate function = TIM3_CH2</li> <li>1: Port D3 alternate function = TIM3_CH2</li> <li>1: Port D3 alternate function = TIM3_CH2</li></ul> |

#### Table 13. Option byte description

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTBL           | <ul> <li>BL[7:0] Bootloader option byte</li> <li>For STM8S products, this option is checked by the boot ROM code after reset. Depending on the content of addresses 0x487E, 0x487F, and 0x8000 (reset vector), the CPU jumps to the bootloader or to the reset vector. Refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> <li>For STM8L products, the bootloader option bytes are on addresses 0xXXXX and 0xXXXX+1 (2 bytes). These option bytes control whether the bootloader is active or not. For more details, refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> </ul> |

Table 13. Option byte description (continued)

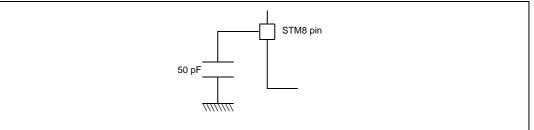

# 10.1.5 Pin loading conditions

### **10.1.6** Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 10.

#### Figure 10. Pin loading conditions

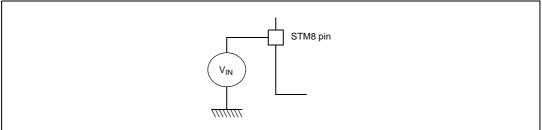

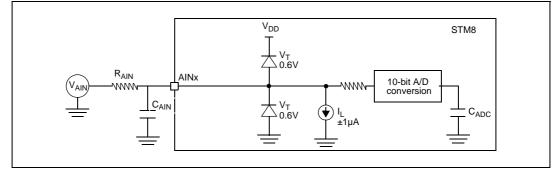

## 10.1.7 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

#### Figure 11. Pin input voltage

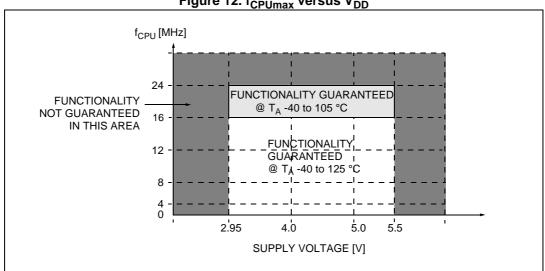

Figure 12. f<sub>CPUmax</sub> versus V<sub>DD</sub>

Table 19. Operating conditions at power-up/power-down

| Symbol                | Parameter                      | Conditions             | Min              | Тур  | Max                | Unit  |

|-----------------------|--------------------------------|------------------------|------------------|------|--------------------|-------|

| +                     | V <sub>DD</sub> rise time rate |                        | 2 <sup>(1)</sup> |      | $\infty$           | μs/V  |

| t <sub>VDD</sub>      | V <sub>DD</sub> fall time rate |                        | 2 <sup>(1)</sup> |      | x                  | μ5/ ν |

| t <sub>TEMP</sub>     | Reset release<br>delay         | V <sub>DD</sub> rising |                  |      | 1.7 <sup>(1)</sup> | ms    |

| V <sub>IT+</sub>      | Power-on reset<br>threshold    |                        | 2.65             | 2.8  | 2.95               | V     |

| V <sub>IT-</sub>      | Brown-out reset<br>threshold   |                        | 2.58             | 2.73 | 2.88               | V     |

| V <sub>HYS(BOR)</sub> | Brown-out reset<br>hysteresis  |                        |                  | 70   |                    | mV    |

1. Guaranteed by design, not tested in production.

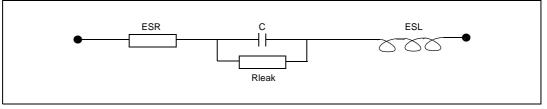

#### 10.3.1 VCAP external capacitor

Stabilization for the main regulator is achieved connecting an external capacitor  $C_{EXT}$  to the  $V_{CAP}$  pin.  $C_{EXT}$  is specified in *Table 18*. Care should be taken to limit the series inductance to less than 15 nH.

Figure 13. External capacitor CEXT

1. Legend: ESR is the equivalent series resistance and ESL is the equivalent inductance.

### 10.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                    | Conditions                      | Min                      | Max                      | Unit |

|----------------------------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|------|

| f <sub>SCK</sub>                                                           |                              | Master mode                     |                          | 10                       | MHz  |

| 1/t <sub>c(SCK)</sub>                                                      | SPI clock frequency          | Slave mode                      | 0                        | 6                        |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>                                 | SPI clock rise and fall time | Capacitive load: C = 30 pF      |                          | 25                       |      |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                                        | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  |                          |      |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                                         | NSS hold time                | Slave mode                      | 70                       |                          |      |

| t <sub>w(SCKH)</sub> <sup>(1)</sup><br>t <sub>w(SCKL)</sub> <sup>(1)</sup> | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |      |

| t <sub>su(MI)</sub> (1)                                                    | Data input setup time        | Master mode                     | 5                        |                          |      |

| t <sub>su(SI)</sub> (1)                                                    |                              | Slave mode                      | 5                        |                          |      |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)                           | Data input hold time         | Master mode                     | 7                        |                          | ns   |

| $t_{h(SI)}^{(1)}$                                                          |                              | Slave mode                      | 10                       |                          |      |

| t <sub>a(SO)</sub> <sup>(1)(2)</sup>                                       | Data output access time      | Slave mode                      |                          | 3 x t <sub>MASTER</sub>  |      |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>                                     | Data output disable time     | Slave mode                      | 25                       |                          |      |

| t <sub>v(SO)</sub> <sup>(1)</sup>                                          | Data output valid time       | Slave mode (after enable edge)  |                          | 75                       |      |

| t <sub>v(MO)</sub> <sup>(1)</sup>                                          | Data output valid time       | Master mode (after enable edge) |                          | 30                       |      |

| t <sub>h(SO)</sub> <sup>(1)</sup>                                          | Data output hold time        | Slave mode (after enable edge)  | 31                       |                          |      |

| t <sub>h(MO)</sub> <sup>(1)</sup>                                          | Data output hold time        | Master mode (after enable edge) | 12                       |                          |      |

1. Values based on design simulation and/or characterization results, and not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

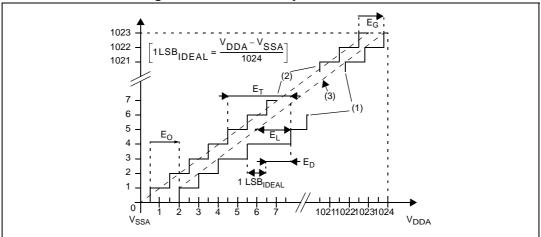

1. Example of an actual transfer curve.

- 2. The ideal transfer curve

- 3.

End point correlation line  $E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_0$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.  $E_D$  = Differential linearity error: maximum deviation between actual steps and the ideal one.  $E_L$  = Integral linearity error: maximum deviation between any actual transition and the end point correlation between any actual transition and the end point correlation line.

# 11 Package characteristics

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at *www.st.com*. ECOPACK® is an ST trademark.

| Table 52. LQFP64 - 64-pin, 14 x 14 mm low-profile quad flat package mechanical |  |  |  |  |  |

|--------------------------------------------------------------------------------|--|--|--|--|--|

| data (continued)                                                               |  |  |  |  |  |

| Symbol |       | mm    |       | inches <sup>(1)</sup> |       |        |

|--------|-------|-------|-------|-----------------------|-------|--------|

|        | Min   | Тур   | Max   | Min                   | Тур   | Max    |

| k      | 0.0 ° | 3.5 ° | 7.0 ° | 0.0 °                 | 3.5 ° | 7.0 °  |

| CCC    |       |       | 0.100 |                       |       | 0.0039 |

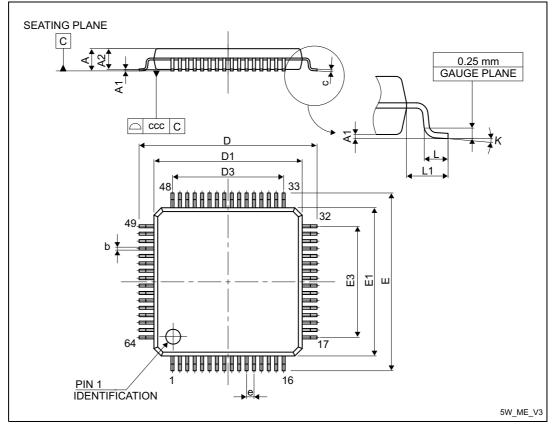

#### Figure 47. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data

| data   |       |       |       |                       |        |        |

|--------|-------|-------|-------|-----------------------|--------|--------|

| Symbol | mm    |       |       | inches <sup>(1)</sup> |        |        |

|        | Min   | Тур   | Max   | Min                   | Тур    | Мах    |

| А      | -     | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |

| (continued) |       |       |       |                       |        |        |

|-------------|-------|-------|-------|-----------------------|--------|--------|

| Symbol      | mm    |       |       | inches <sup>(1)</sup> |        |        |

|             | Min   | Тур   | Max   | Min                   | Тур    | Max    |

| E1          | 6.800 | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3          | -     | 5.500 | -     | -                     | 0.2165 | -      |

| е           | -     | 0.500 | -     | -                     | 0.0197 | -      |

| L           | 0.450 | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1          | -     | 1.000 | -     | -                     | 0.0394 | -      |

| k           | 0°    | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC         | -     | -     | 0.080 | -                     | -      | 0.0031 |

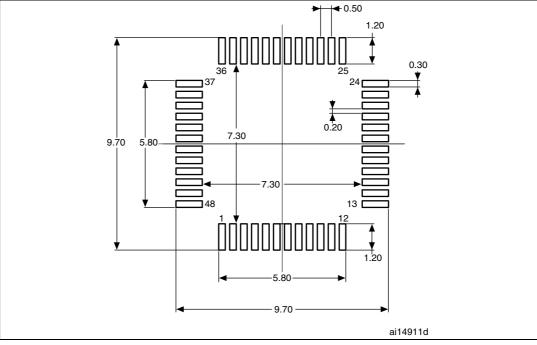

Table 54. LQFP48 - 48-pin, 7x 7 mm low-profile quad flat package mechanical(continued)

1. Dimensions are expressed in millimeters.

| data   |        |        |        |                       |        |        |

|--------|--------|--------|--------|-----------------------|--------|--------|

| Symbol |        | mm     |        | inches <sup>(1)</sup> |        |        |

|        | Min    | Тур    | Max    | Min                   | Тур    | Max    |

| А      | -      | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050  | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350  | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.300  | 0.370  | 0.450  | 0.0118                | 0.0146 | 0.0177 |

| С      | 0.090  | -      | 0.200  | 0.0035                |        | 0.0079 |

| D      | 11.800 | 12.000 | 12.200 | 0.4646                | 0.4724 | 0.4803 |

| D1     | 9.800  | 10.000 | 10.200 | 0.3858                | 0.3937 | 0.4016 |

| D3     | -      | 8.000  | -      | -                     | 0.3150 | -      |

| E      | 11.800 | 12.000 | 12.200 | 0.4646                | 0.4724 | 0.4803 |

| E1     | 9.800  | 10.000 | 10.200 | 0.3858                | 0.3937 | 0.4016 |

| E3     | -      | 8.000  | -      | -                     | 0.3150 | -      |

| е      | -      | 0.800  | -      | -                     | 0.0315 | -      |

| L      | 0.450  | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -      | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0.0°   | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| CCC    | -      | -      | 0.100  | -                     | -      | 0.0039 |

| Table 55. LQFP44 - 44-pin. 10         | x 10 mm low-profile quad flat package mechanical |

|---------------------------------------|--------------------------------------------------|

| · · · · · · · · · · · · · · · · · · · | data                                             |

|                                       |                                                  |

| data   |       |       |       |                       |        |        |

|--------|-------|-------|-------|-----------------------|--------|--------|

| Symbol | mm    |       |       | inches <sup>(1)</sup> |        |        |

|        | Min   | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | -     | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.300 | 0.370 | 0.450 | 0.0118                | 0.0146 | 0.0177 |

| С      | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |

| D      | 8.800 | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| D1     | 6.800 | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| D3     | -     | 5.600 | -     | -                     | 0.2205 | -      |

| E      | 8.800 | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |

| E1     | 6.800 | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |

| E3     | -     | 5.600 | -     | -                     | 0.2205 | -      |

| е      | -     | 0.800 | -     | -                     | 0.0315 | -      |

| L      | 0.450 | 0.600 | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -     | 1.000 | -     | -                     | 0.0394 | -      |

| k      | 0°    | 3.5°  | 7°    | 0°                    | 3.5°   | 7°     |

| CCC    | -     | -     | 0.100 | -                     | -      | 0.0039 |

Table 56. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data

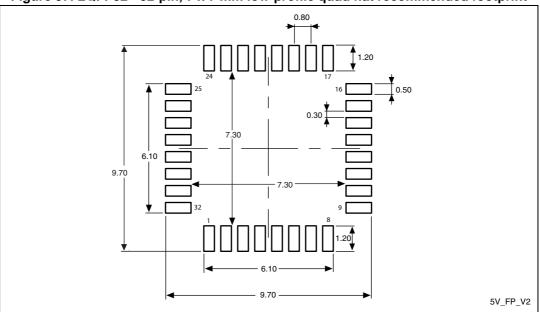

#### Figure 57. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

DocID14733 Rev 13

#### **11.2.2** Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the order code (see *Figure 59: STM8S207xx/208xx performance line ordering information scheme(1) on page 112*).

The following example shows how to calculate the temperature range needed for a given application.

Assuming the following application conditions:

- Maximum ambient temperature T<sub>Amax</sub>= 82 °C (measured according to JESD51-2)

- $I_{DDmax} = 15 \text{ mA}, V_{DD} = 5.5 \text{ V}$

- Maximum eight standard I/Os used at the same time in output at low level with  $I_{OL}$  = 10 mA,  $V_{OL}$  = 2 V

- Maximum four high sink I/Os used at the same time in output at low level with  $\rm I_{OL}$  = 20 mA,  $\rm V_{OL}$  = 1.5 V

- Maximum two true open drain I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$  = 2 V

P<sub>INTmax =</sub> 15 mA x 5.5 V = 82.5 mW

$P_{IOmax} = (10 \text{ mA x } 2 \text{ V x } 8) + (20 \text{ mA x } 2 \text{ V x } 2) + (20 \text{ mA x } 1.5 \text{ V x } 4) = 360 \text{ mW}$ This gives:  $P_{INTmax} = 82.5 \text{ mW}$  and  $P_{IOmax} 360 \text{ mW}$ :

$P_{Dmax} = 82.5 \text{ mW} + 360 \text{ mW}$

Thus: P<sub>Dmax</sub> = 443 mW

Using the values obtained in *Table 57: Thermal characteristics on page 108*  $T_{Jmax}$  is calculated as follows for LQFP64 10 x 10 mm = 46 °C/W:

T<sub>Jmax</sub> = 82 °C + (46 °C/W x 443 mW) = 82 °C + 20 °C = 102 °C

This is within the range of the suffix 6 version parts (-40 <  $T_J$  < 105 °C).

In this case, parts must be ordered at least with the temperature range suffix 6.

# 12 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

# 12.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows you to order exactly what you need to meet the development requirements and to adapt the emulation system to support existing and future ST microcontrollers.

#### STice key features

- Occurrence and time profiling and code coverage (new features)

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Program and data trace recording up to 128 KB records

- Read/write on the fly of memory during emulation

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows you to specify the components you need to meet the development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14733 Rev 13