Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207r8t3tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure

The IWDG time base spans from 60  $\mu$ s to 1 s.

## 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM3 input capture channel 1 for calibration

## 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

## 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

## 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

## 4.14.1 UART1

#### **Main features**

- One Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- Single wire half duplex mode

## Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

## Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

## LIN master mode

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

## 4.14.2 UART3

## Main features

- 1 Mbit/s full duplex SCI

- LIN master capable

- High precision baud rate generator

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### LIN master capability

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

#### LIN slave mode

- Autonomous header handling one single interrupt per valid message header

- Automatic baud rate synchronization maximum tolerated initial clock deviation ±15%

- Sync delimiter checking

- 11-bit LIN sync break detection break detection always active

- Parity check on the LIN identifier field

- LIN error management

- Hot plugging support

## 4.14.3 SPI

- Maximum speed: 10 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

## 4.14.4 I<sup>2</sup>C

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

## 4.14.5 beCAN

The beCAN controller (basic enhanced CAN), interfaces the CAN network and supports the CAN protocol version 2.0A and B. It has been designed to manage a high number of incoming messages efficiently with a minimum CPU load.

For safety-critical applications the beCAN controller provides all hardware functions to support the CAN time triggered communication option (TTCAN).

The maximum transmission speed is 1 Mbit.

## Transmission

- Three transmit mailboxes

- Configurable transmit priority by identifier or order request

- Time stamp on SOF transmission

## Reception

- 8-, 11- and 29-bit ID

- One receive FIFO (3 messages deep)

- Software-efficient mailbox mapping at a unique address space

- FMI (filter match index) stored with message

- Configurable FIFO overrun

- Time stamp on SOF reception

- Six filter banks, 2 x 32 bytes (scalable to 4 x 16-bit) each, enabling various masking configurations, such as 12 filters for 29-bit ID or 48 filters for 11-bit ID

- Filtering modes:

- Mask mode permitting ID range filtering

- ID list mode

- Time triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Configurable timer resolution

- Time stamp sent in last two data bytes

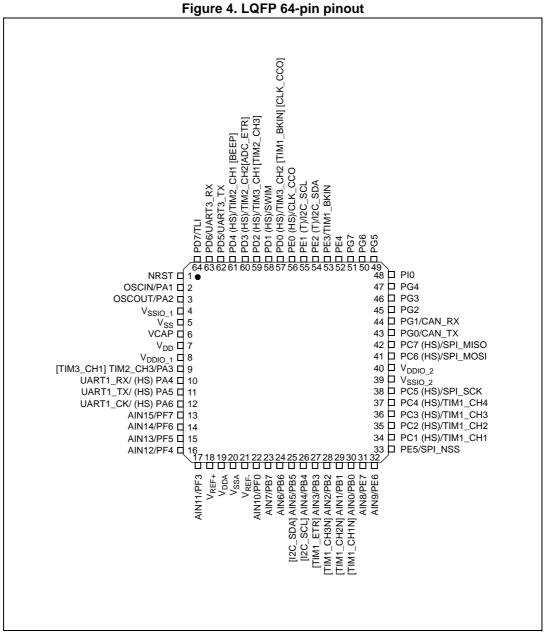

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

4. CAN\_RX and CAN\_TX is available on STM8S208xx devices only.

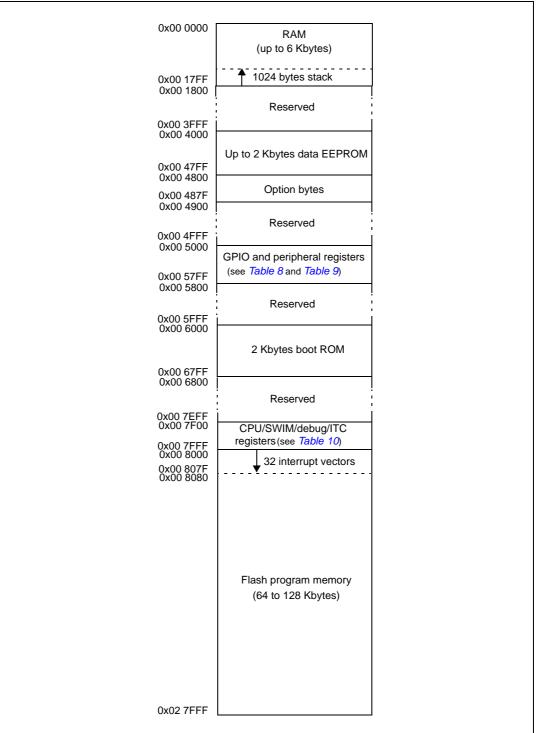

# 6 Memory and register map

## 6.1 Memory map

Figure 8. Memory map

|           |        |                | vare register map (continued)     | Reset  |

|-----------|--------|----------------|-----------------------------------|--------|

| Address   | Block  | Register label | Register name                     | status |

| 0x00 500F |        | PD_ODR         | Port D data output latch register | 0x00   |

| 0x00 5010 |        | PD_IDR         | Port D input pin value register   | 0x00   |

| 0x00 5011 | Port D | PD_DDR         | Port D data direction register    | 0x00   |

| 0x00 5012 |        | PD_CR1         | Port D control register 1         | 0x02   |

| 0x00 5013 |        | PD_CR2         | Port D control register 2         | 0x00   |

| 0x00 5014 |        | PE_ODR         | Port E data output latch register | 0x00   |

| 0x00 5015 |        | PE_IDR         | Port E input pin value register   | 0x00   |

| 0x00 5016 | Port E | PE_DDR         | Port E data direction register    | 0x00   |

| 0x00 5017 |        | PE_CR1         | Port E control register 1         | 0x00   |

| 0x00 5018 |        | PE_CR2         | Port E control register 2         | 0x00   |

| 0x00 5019 |        | PF_ODR         | Port F data output latch register | 0x00   |

| 0x00 501A |        | PF_IDR         | Port F input pin value register   | 0x00   |

| 0x00 501B | Port F | PF_DDR         | Port F data direction register    | 0x00   |

| 0x00 501C |        | PF_CR1         | Port F control register 1         | 0x00   |

| 0x00 501D |        | PF_CR2         | Port F control register 2         | 0x00   |

| 0x00 501E |        | PG_ODR         | Port G data output latch register | 0x00   |

| 0x00 501F |        | PG_IDR         | Port G input pin value register   | 0x00   |

| 0x00 5020 | Port G | PG_DDR         | Port G data direction register    | 0x00   |

| 0x00 5021 |        | PG_CR1         | Port G control register 1         | 0x00   |

| 0x00 5022 |        | PG_CR2         | Port G control register 2         | 0x00   |

| 0x00 5023 |        | PH_ODR         | Port H data output latch register | 0x00   |

| 0x00 5024 |        | PH_IDR         | Port H input pin value register   | 0x00   |

| 0x00 5025 | Port H | PH_DDR         | Port H data direction register    | 0x00   |

| 0x00 5026 |        | PH_CR1         | Port H control register 1         | 0x00   |

| 0x00 5027 |        | PH_CR2         | Port H control register 2         | 0x00   |

| 0x00 5028 |        | PI_ODR         | Port I data output latch register | 0x00   |

| 0x00 5029 |        | PI_IDR         | Port I input pin value register   | 0x00   |

| 0x00 502A | Port I | PI_DDR         | Port I data direction register    | 0x00   |

| 0x00 502B |        | PI_CR1         | Port I control register 1         | 0x00   |

| 0x00 502C |        | PI_CR2         | Port I control register 2         | 0x00   |

Table 8. I/O port hardware register map (continued)

| Address                   | Block | Register label | Register name                                    | Reset<br>status    |  |

|---------------------------|-------|----------------|--------------------------------------------------|--------------------|--|

| 0x00 5050 to<br>0x00 5059 |       |                | Reserved area (10 bytes)                         |                    |  |

| 0x00 505A                 |       | FLASH_CR1      | Flash control register 1                         | 0x00               |  |

| 0x00 505B                 |       | FLASH_CR2      | Flash control register 2                         | 0x00               |  |

| 0x00 505C                 |       | FLASH_NCR2     | Flash complementary control register 2           | 0xFF               |  |

| 0x00 505D                 | Flash | FLASH _FPR     |                                                  |                    |  |

| 0x00 505E                 |       | FLASH _NFPR    | Flash complementary protection register          | 0xFF               |  |

| 0x00 505F                 |       | FLASH _IAPSR   | Flash in-application programming status register | 0x00               |  |

| 0x00 5060 to<br>0x00 5061 |       |                | Reserved area (2 bytes)                          |                    |  |

| 0x00 5062                 | Flash | FLASH_PUKR     | Flash Program memory unprotection register       | 0x00               |  |

| 0x00 5063                 |       |                | Reserved area (1 byte)                           |                    |  |

| 0x00 5064                 | Flash | FLASH _DUKR    | Data EEPROM unprotection register                | 0x00               |  |

| 0x00 5065 to<br>0x00 509F |       |                | Reserved area (59 bytes)                         |                    |  |

| 0x00 50A0                 | ІТС   | EXTI_CR1       | EXTI_CR1 External interrupt control register 1   |                    |  |

| 0x00 50A1                 |       | EXTI_CR2       | External interrupt control register 2            | 0x00               |  |

| 0x00 50A2 to<br>0x00 50B2 |       |                | Reserved area (17 bytes)                         |                    |  |

| 0x00 50B3                 | RST   | RST_SR         | Reset status register                            | 0xXX <sup>(1</sup> |  |

| 0x00 50B4 to<br>0x00 50BF |       |                | Reserved area (12 bytes)                         |                    |  |

| 0x00 50C0                 | CLK   | CLK_ICKR       | Internal clock control register                  | 0x01               |  |

| 0x00 50C1                 | - CLK | CLK_ECKR       | External clock control register                  | 0x00               |  |

| 0x00 50C2                 |       |                | Reserved area (1 byte)                           |                    |  |

| 0x00 50C3                 |       | CLK_CMSR       | Clock master status register                     | 0xE1               |  |

| 0x00 50C4                 | ]     | CLK_SWR        | Clock master switch register                     | 0xE1               |  |

| 0x00 50C5                 |       | CLK_SWCR       | Clock switch control register                    | 0xXX               |  |

| 0x00 50C6                 |       | CLK_CKDIVR     | Clock divider register                           | 0x18               |  |

| 0x00 50C7                 | CLK   | CLK_PCKENR1    | Peripheral clock gating register 1               | 0xFF               |  |

| 0x00 50C8                 |       | CLK_CSSR       | Clock security system register                   | 0x00               |  |

| 0x00 50C9                 |       | CLK_CCOR       | Configurable clock control register              | 0x00               |  |

| 0x00 50CA                 |       | CLK_PCKENR2    | Peripheral clock gating register 2               | 0xFF               |  |

| 0x00 50CB                 |       | CLK_CANCCR     | CAN clock control register                       | 0x00               |  |

Table 9. General hardware register map

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTBL           | <ul> <li>BL[7:0] Bootloader option byte</li> <li>For STM8S products, this option is checked by the boot ROM code after reset. Depending on the content of addresses 0x487E, 0x487F, and 0x8000 (reset vector), the CPU jumps to the bootloader or to the reset vector. Refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> <li>For STM8L products, the bootloader option bytes are on addresses 0xXXXX and 0xXXXX+1 (2 bytes). These option bytes control whether the bootloader is active or not. For more details, refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> </ul> |

Table 13. Option byte description (continued)

# 9 Unique ID

The devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content              |             |             | Unique ID bits |    |           |   |   |   |

|---------|----------------------|-------------|-------------|----------------|----|-----------|---|---|---|

| Address | description          | 7           | 6           | 5              | 4  | 3         | 2 | 1 | 0 |

| 0x48CD  | X co-ordinate on the |             |             |                | U  | _ID[7:0]  |   |   |   |

| 0x48CE  | wafer                | U_ID[15:8]  |             |                |    |           |   |   |   |

| 0x48CF  | Y co-ordinate on the |             | U_ID[23:16] |                |    |           |   |   |   |

| 0x48D0  | wafer                |             | U_ID[31:24] |                |    |           |   |   |   |

| 0x48D1  | Wafer number         | U_ID[39:32] |             |                |    |           |   |   |   |

| 0x48D2  |                      |             |             |                | U_ | ID[47:40] |   |   |   |

| 0x48D3  |                      |             |             |                | U_ | ID[55:48] |   |   |   |

| 0x48D4  |                      |             |             |                | U_ | ID[63:56] |   |   |   |

| 0x48D5  | Lot number           |             |             |                | U_ | ID[71:64] |   |   |   |

| 0x48D6  |                      |             |             |                | U_ | ID[79:72] |   |   |   |

| 0x48D7  |                      |             | U_ID[87:80] |                |    |           |   |   |   |

| 0x48D8  |                      |             |             |                | U_ | ID[95:88] |   |   |   |

#### Table 14. Unique ID registers (96 bits)

## Total current consumption and timing in forced reset state

| Symbol                 | Parameter                                | Conditions              | Тур | Max <sup>(1)</sup> | Unit |

|------------------------|------------------------------------------|-------------------------|-----|--------------------|------|

|                        | Supply current in reset state            | $V_{DD} = 5 V$          | 1.6 |                    | mA   |

| I <sub>DD(R)</sub> Sup | Supply current in reset state            | V <sub>DD</sub> = 3.3 V | 0.8 |                    | ША   |

| t <sub>RESETBL</sub>   | Reset release to bootloader vector fetch |                         |     | 150                | μs   |

#### Table 29. Total current consumption and timing in forced reset state

1. Data guaranteed by design, not tested in production.

## **Current consumption of on-chip peripherals**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

HSI internal RC/ $f_{CPU} = f_{MASTER} = 16$  MHz.

#### Table 30. Peripheral current consumption

| Symbol                            | Parameter                                          | Тур. | Unit |

|-----------------------------------|----------------------------------------------------|------|------|

| I <sub>DD(TIM1)</sub>             | TIM1 supply current <sup>(1)</sup>                 | 220  |      |

| I <sub>DD(TIM2)</sub>             | TIM2 supply current <sup>(1)</sup>                 | 120  |      |

| I <sub>DD(TIM3)</sub>             | TIM3 timer supply current <sup>(1)</sup>           | 100  |      |

| I <sub>DD(TIM4)</sub>             | TIM4 timer supply current <sup>(1)</sup>           | 25   |      |

| I <sub>DD(UART1)</sub>            | UART1 supply current <sup>(2)</sup>                | 90   |      |

| I <sub>DD(UART3)</sub>            | UART3 supply current <sup>(2)</sup>                | 110  | μA   |

| I <sub>DD(SPI)</sub>              | SPI supply current <sup>(2)</sup>                  | 40   |      |

| I <sub>DD(I</sub> <sup>2</sup> C) | I <sup>2</sup> C supply current <sup>(2)</sup>     | 50   |      |

| I <sub>DD(CAN)</sub>              | beCAN supply current <sup>(2)</sup>                | 210  |      |

| I <sub>DD(ADC2)</sub>             | ADC2 supply current when converting <sup>(3)</sup> | 1000 |      |

1. Data based on a differential  $I_{DD}$  measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions. Not tested in production.

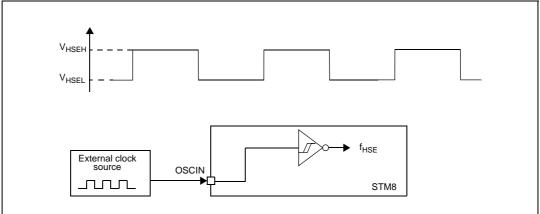

## **10.3.3** External clock sources and timing characteristics

## HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Table 31. HSE us | ser external clock | characteristics |

|------------------|--------------------|-----------------|

|------------------|--------------------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency |                            | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      |                            | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       |                            | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    |     | 1                       | μA   |

1. Data based on characterization results, not tested in production.

## HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

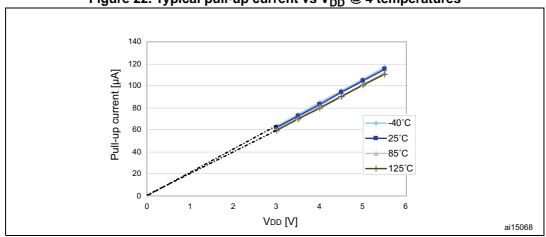

Figure 22. Typical pull-up current vs  $V_{\text{DD}} @$  4 temperatures

1. The pull-up is a pure resistor (slope goes through 0).

| Symbol          | Parameter                             | Conditions                                      | Min                | Max              | Unit |

|-----------------|---------------------------------------|-------------------------------------------------|--------------------|------------------|------|

| M               | Output low level with 8 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$  |                    | 2                | V    |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | I <sub>IO</sub> = 4 mA, V <sub>DD</sub> = 3.3 V |                    | 1 <sup>(1)</sup> | V    |

| V               | Output high level with 8 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$  | 2.8                |                  | V    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | $I_{IO} = 4 \text{ mA}, V_{DD} = 3.3 \text{ V}$ | 2.1 <sup>(1)</sup> |                  | v    |

## Table 38. Output driving current (standard ports)

1. Data based on characterization results, not tested in production

| Table 39. | Output driving | a current ( | (true oper | n drain ports) |  |

|-----------|----------------|-------------|------------|----------------|--|

|           |                | ,           |            |                |  |

| Symbol          | Parameter                         | Conditions                                       | Max                | Unit |

|-----------------|-----------------------------------|--------------------------------------------------|--------------------|------|

|                 |                                   | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   | 1                  |      |

| V <sub>OL</sub> | Output low level with 2 pins sunk | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 3.3 V | 1.5 <sup>(1)</sup> | V    |

|                 |                                   | I <sub>IO</sub> = 20 mA, V <sub>DD</sub> = 5 V   | 2 <sup>(1)</sup>   |      |

1. Data based on characterization results, not tested in production

| Symbol          | Parameter Conditions                  |                                                | Min                | Max                | Unit |

|-----------------|---------------------------------------|------------------------------------------------|--------------------|--------------------|------|

|                 | Output low level with 8 pins sunk     | $I_{IO}$ = 10 mA, $V_{DD}$ = 5 V               |                    | 0.8                |      |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | $I_{IO}$ = 10 mA, $V_{DD}$ = 3.3 V             |                    | 1 <sup>(1)</sup>   |      |

|                 | Output low level with 4 pins sunk     | $I_{IO} = 20 \text{ mA}, V_{DD} = 5 \text{ V}$ |                    | 1.5 <sup>(1)</sup> | V    |

|                 | Output high level with 8 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$ | 4.0                |                    | v    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | $I_{IO}$ = 10 mA, $V_{DD}$ = 3.3 V             | 2.1 <sup>(1)</sup> |                    |      |

|                 | Output high level with 4 pins sourced | $I_{IO} = 20 \text{ mA}, V_{DD} = 5 \text{ V}$ | 3.3 <sup>(1)</sup> |                    |      |

1. Data based on characterization results, not tested in production

## **10.3.10 10-bit ADC characteristics**

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                                      | Parameter                                                          | Conditions                                                         | Min                 | Тур  | Max                | Unit               |  |

|---------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|------|--------------------|--------------------|--|

| f                                           |                                                                    | V <sub>DDA</sub> = 3 to 5.5 V                                      | 1                   |      | 4                  | MHz                |  |

| f <sub>ADC</sub>                            | ADC clock frequency                                                | V <sub>DDA</sub> = 4.5 to 5.5 V                                    | 1                   |      | 6                  |                    |  |

| V <sub>DDA</sub>                            | Analog supply                                                      |                                                                    | 3                   |      | 5.5                | V                  |  |

| V <sub>REF+</sub>                           | Positive reference voltage                                         |                                                                    | 2.75 <sup>(1)</sup> |      | V <sub>DDA</sub>   | V                  |  |

| V <sub>REF-</sub>                           | Negative reference voltage                                         |                                                                    | V <sub>SSA</sub>    |      | 0.5 <sup>(1)</sup> | V                  |  |

|                                             |                                                                    |                                                                    | $V_{SSA}$           |      | V <sub>DDA</sub>   | V                  |  |

| V <sub>AIN</sub>                            | Conversion voltage range <sup>(2)</sup>                            | Devices with external<br>V <sub>REF+</sub> /V <sub>REF-</sub> pins | V <sub>REF-</sub>   |      | V <sub>REF+</sub>  | V                  |  |

| C <sub>ADC</sub>                            | Internal sample and hold capacitor                                 |                                                                    |                     | 3    |                    | pF                 |  |

| ts <sup>(2)</sup>                           | Sampling time                                                      | f <sub>ADC</sub> = 4 MHz                                           | 0.75                |      |                    |                    |  |

| t <sub>S</sub> <sup>(2)</sup> Sampling time |                                                                    | f <sub>ADC</sub> = 6 MHz                                           | 0.5                 |      | μs                 |                    |  |

| t <sub>STAB</sub>                           | Wakeup time from standby                                           |                                                                    |                     | 7    |                    | μs                 |  |

| t <sub>CONV</sub>                           | Total conversion time (including sampling time, 10-bit resolution) | $f_{ADC} = 4 MHz$                                                  | 3.5                 |      | μs                 |                    |  |

|                                             |                                                                    | f <sub>ADC</sub> = 6 MHz                                           |                     | 2.33 |                    | μs                 |  |

|                                             |                                                                    |                                                                    |                     | 14   |                    | 1/f <sub>ADC</sub> |  |

| Table 44. | ADC | characteristics |

|-----------|-----|-----------------|

|-----------|-----|-----------------|

1. Data guaranteed by design, not tested in production.

2. During the sample time the input capacitance  $C_{AIN}$  (3 pF max) can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>S</sub> depend on programming.

#### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance:

- A supply overvoltage (applied to each power supply pin)

- A current injection (applied to each input, output and configurable I/O pin) is performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol                   | Parameter             | Conditions              | Class <sup>(1)</sup> |

|--------------------------|-----------------------|-------------------------|----------------------|

|                          |                       | T <sub>A</sub> = 25 °C  | А                    |

| LU Static latch-up class | Static latch-up class | $T_A = 85 \ ^{\circ}C$  | А                    |

|                          |                       | T <sub>A</sub> = 125 °C | А                    |

| Table 50. I | Electrical | sensitivities |

|-------------|------------|---------------|

|-------------|------------|---------------|

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

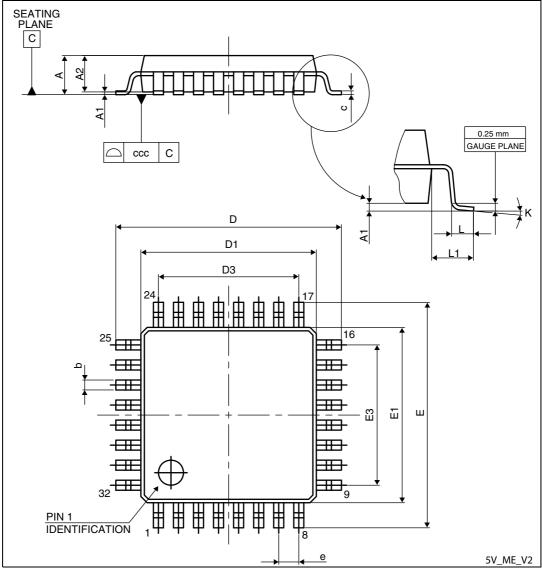

| Cumhal | millimeters |        |        | inches |        |        |  |

|--------|-------------|--------|--------|--------|--------|--------|--|

| Symbol | Min         | Тур    | Max    | Min    | Тур    | Max    |  |

| D      | 15.800      | 16.000 | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| D3     | -           | 12.350 | -      | -      | 0.4862 | -      |  |

| E      | 15.800      | 16.000 | 16.200 | 0.6220 | 0.6299 | 0.6378 |  |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433 | 0.5512 | 0.5591 |  |

| E3     | -           | 12.350 | -      | -      | 0.4862 | -      |  |

| е      | -           | 0.650  | -      | -      | 0.0256 | -      |  |

| L      | 0.450       | 0.600  | 0.750  | 0.0177 | 0.0236 | 0.0295 |  |

| L1     | -           | 1.000  | -      | -      | 0.0394 | -      |  |

| k      | 0°          | 3.5°   | 7°     | 0°     | 3.5°   | 7°     |  |

| CCC    | -           | -      | 0.100  | -      | -      | 0.0039 |  |

# Table 51. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanicaldata<sup>(1)</sup> (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

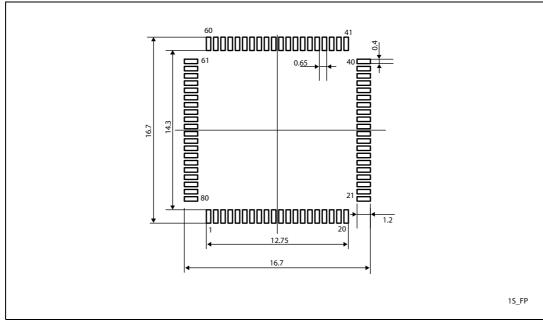

#### Figure 44. LQFP80 recommended footprint

## 11.1.5 LQFP32 package information

Figure 56. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

DocID14733 Rev 13

## **11.2** Thermal characteristics

The maximum chip junction temperature  $(T_{Jmax})$  must never exceed the values given in *Table 18: General operating conditions on page 56.*

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- $P_{I/Omax}$  represents the maximum power dissipation on output pins, where:  $P_{I/Omax} = \Sigma (V_{OL}*I_{OL}) + \Sigma ((V_{DD}-V_{OH})*I_{OH})$ , and taking account of the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                        | Value | Unit |

|---------------|----------------------------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 80 - 14 x 14 mm                      | 38    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 64 - 14 x 14 mm                      | 45    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 64 - 10 x 10 mm                      | 46    | °C/W |

| $\Theta_{JA}$ | Θ <sub>JA</sub> Thermal resistance junction-ambient           LQFP 48 - 7 x 7 mm |       | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 44 - 10 x 10 mm                      | 54    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 32 - 7 x 7 mm                        | 60    | °C/W |

| Table 57. Thermal characteristics <sup>(1)</sup> | Table 57. | Thermal | characteristics <sup>(1)</sup> |

|--------------------------------------------------|-----------|---------|--------------------------------|

|--------------------------------------------------|-----------|---------|--------------------------------|

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

## 11.2.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

# 12 STM8 development tools

Development tools for the STM8 microcontrollers include the full-featured STice emulation system supported by a complete software tool package including C compiler, assembler and integrated development environment with high-level language debugger. In addition, the STM8 is to be supported by a complete range of tools including starter kits, evaluation boards and a low-cost in-circuit debugger/programmer.

## 12.1 Emulation and in-circuit debugging tools

The STice emulation system offers a complete range of emulation and in-circuit debugging features on a platform that is designed for versatility and cost-effectiveness. In addition, STM8 application development is supported by a low-cost in-circuit debugger/programmer.

The STice is the fourth generation of full featured emulators from STMicroelectronics. It offers new advanced debugging capabilities including profiling and coverage to help detect and eliminate bottlenecks in application execution and dead code when fine tuning an application.

In addition, STice offers in-circuit debugging and programming of STM8 microcontrollers via the STM8 single wire interface module (SWIM), which allows non-intrusive debugging of an application while it runs on the target microcontroller.

For improved cost effectiveness, STice is based on a modular design that allows you to order exactly what you need to meet the development requirements and to adapt the emulation system to support existing and future ST microcontrollers.

#### STice key features

- Occurrence and time profiling and code coverage (new features)

- Advanced breakpoints with up to 4 levels of conditions

- Data breakpoints

- Program and data trace recording up to 128 KB records

- Read/write on the fly of memory during emulation

- In-circuit debugging/programming via SWIM protocol

- 8-bit probe analyzer

- 1 input and 2 output triggers

- Power supply follower managing application voltages between 1.62 to 5.5 V

- Modularity that allows you to specify the components you need to meet the development requirements and adapt to future requirements

- Supported by free software tools that include integrated development environment (IDE), programming software interface and assembler for STM8.

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 18-Feb-2015 | 13       | <ul> <li>Updated:</li> <li>Figure 43: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline</li> <li>Table 51: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data</li> <li>Figure 51: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data</li> <li>Figure 51: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline</li> <li>Table 53: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline</li> <li>Table 53: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Table 54: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Table 56: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Table 56: LQFP48 - 32-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Figure 56: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data</li> <li>Added:</li> <li>Figure 44: LQFP80 recommended footprint</li> <li>Figure 45: LQFP48 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 48: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 51: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint</li> <li>Figure 51: LQFP48 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 52: LQFP48 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 52: LQFP48 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 53: LQFP44 marking example (package top view)</li> <li>Figure 54: LQFP44 - 34-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 55: LQFP48 marking example (package top view)</li> <li>Figure 55: LQFP44 marking example (package top view)</li> <li>Figure 55:</li></ul> |  |

Table 58. Document revision history (continued)