Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | STM8                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 24MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 52                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 1.5K x 8                                                               |

| RAM Size                   | 6K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207r8t6tr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

### LIN master capability

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

### LIN slave mode

- Autonomous header handling one single interrupt per valid message header

- Automatic baud rate synchronization maximum tolerated initial clock deviation ±15%

- Sync delimiter checking

- 11-bit LIN sync break detection break detection always active

- Parity check on the LIN identifier field

- LIN error management

- Hot plugging support

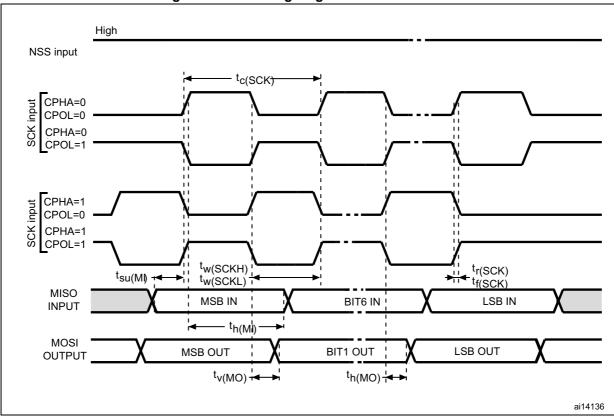

# 4.14.3 SPI

- Maximum speed: 10 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

|        | Pin    | num    | ber    |        |                   |      |          | Inpu | t              |           | Out   |    |    | ,                              |                                  |                                                      |

|--------|--------|--------|--------|--------|-------------------|------|----------|------|----------------|-----------|-------|----|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name          | Type | floating | ndw  | Ext. interrupt | High sink | Speed | OD | ЬР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 12     | 12     | 12     | 11     | -      | PA6/UART1_CK      | I/O  | X        | Х    | х              | HS        | О3    | х  | х  | Port A6                        | UART1<br>synchronous<br>clock    |                                                      |

| 13     | -      | -      | -      | -      | PH0               | I/O  | <u>X</u> | Х    |                | HS        | O3    | Х  | Х  | Port H0                        |                                  |                                                      |

| 14     | -      | -      | -      | -      | PH1               | I/O  | <u>X</u> | Х    |                | HS        | O3    | Х  | Х  | Port H1                        |                                  |                                                      |

| 15     | -      | -      | -      | -      | PH2               | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port H2                        |                                  |                                                      |

| 16     | -      | -      | -      | -      | PH3               | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port H3                        | A 1                              |                                                      |

| 17     | 13     | -      | -      | -      | PF7/AIN15         | I/O  | <u>X</u> | Х    |                |           | 01    | Х  | Х  | Port F7                        | Analog<br>input 15               |                                                      |

| 18     | 14     | -      | -      | -      | PF6/AIN14         | I/O  | <u>X</u> | х    |                |           | 01    | Х  | Х  | Port F6                        | Analog<br>input 14               |                                                      |

| 19     | 15     | -      | -      | -      | PF5/AIN13         | I/O  | X        | х    |                |           | 01    | х  | х  | Port F5                        | Analog<br>input 13               |                                                      |

| 20     | 16     | -      | -      | 8      | PF4/AIN12         | I/O  | X        | х    |                |           | 01    | х  | х  | Port F4                        | Analog<br>input 12               |                                                      |

| 21     | 17     | -      | -      | -      | PF3/AIN11         | I/O  | X        | Х    |                |           | 01    | х  | х  | Port F3                        | Analog<br>input 11               |                                                      |

| 22     | 18     | -      | -      | -      | V <sub>REF+</sub> | s    |          |      |                |           |       |    |    | ADC pos<br>voltage             | tive reference                   |                                                      |

| 23     | 19     | 13     | 12     |        | V <sub>DDA</sub>  | S    |          |      |                |           |       |    |    | Analog p                       | ower supply                      |                                                      |

| 24     | 20     | 14     | 13     | 10     | V <sub>SSA</sub>  | S    |          |      |                |           |       |    |    | Analog gi                      | round                            |                                                      |

| 25     | 21     | -      | -      | -      | V <sub>REF-</sub> | S    |          |      |                |           |       |    |    | ADC neg<br>voltage             | ative reference                  |                                                      |

| 26     | 22     | -      | -      | -      | PF0/AIN10         | I/O  | <u>x</u> | х    |                |           | 01    | х  | х  | Port F0                        | Analog<br>input 10               |                                                      |

| 27     | 23     | 15     | 14     | -      | PB7/AIN7          | I/O  | X        | х    | Х              |           | 01    | х  | Х  | Port B7                        | Analog<br>input 7                |                                                      |

| 28     | 24     | 16     | 15     | -      | PB6/AIN6          | I/O  | X        | х    | Х              |           | 01    | х  | х  | Port B6                        | Analog<br>input 6                |                                                      |

| 29     | 25     | 17     | 16     | 11     | PB5/AIN5          | I/O  | X        | х    | Х              |           | 01    | х  | х  | Port B5                        | Analog<br>input 5                | l <sup>2</sup> C_SDA<br>[AFR6]                       |

| 30     | 26     | 18     | 17     | 12     | PB4/AIN4          | I/O  | X        | х    | х              |           | 01    | х  | х  | Port B4                        | Analog<br>input 4                | I <sup>2</sup> C_SCL<br>[AFR6]                       |

Table 6. Pin description (continued)

| Address                   | Block | Register label | Register name                                    | Reset<br>status    |  |  |

|---------------------------|-------|----------------|--------------------------------------------------|--------------------|--|--|

| 0x00 5050 to<br>0x00 5059 |       |                | Reserved area (10 bytes)                         |                    |  |  |

| 0x00 505A                 |       | FLASH_CR1      | Flash control register 1                         | 0x00               |  |  |

| 0x00 505B                 |       | FLASH_CR2      | Flash control register 2                         | 0x00               |  |  |

| 0x00 505C                 |       | FLASH_NCR2     | Flash complementary control register 2           | 0xFF               |  |  |

| 0x00 505D                 | Flash | FLASH _FPR     | Flash protection register                        | 0x00               |  |  |

| 0x00 505E                 |       | FLASH _NFPR    | Flash complementary protection register          | 0xFF               |  |  |

| 0x00 505F                 |       | FLASH _IAPSR   | Flash in-application programming status register | 0x00               |  |  |

| 0x00 5060 to<br>0x00 5061 |       |                | Reserved area (2 bytes)                          |                    |  |  |

| 0x00 5062                 | Flash | FLASH_PUKR     | Flash Program memory unprotection register       | 0x00               |  |  |

| 0x00 5063                 |       |                | Reserved area (1 byte)                           |                    |  |  |

| 0x00 5064                 | Flash | FLASH _DUKR    | FLASH _DUKR Data EEPROM unprotection register    |                    |  |  |

| 0x00 5065 to<br>0x00 509F |       |                | Reserved area (59 bytes)                         |                    |  |  |

| 0x00 50A0                 | ІТС   | EXTI_CR1       | External interrupt control register 1            | 0x00               |  |  |

| 0x00 50A1                 |       | EXTI_CR2       | External interrupt control register 2            | 0x00               |  |  |

| 0x00 50A2 to<br>0x00 50B2 |       |                | Reserved area (17 bytes)                         |                    |  |  |

| 0x00 50B3                 | RST   | RST_SR         | Reset status register                            | 0xXX <sup>(1</sup> |  |  |

| 0x00 50B4 to<br>0x00 50BF |       |                | Reserved area (12 bytes)                         |                    |  |  |

| 0x00 50C0                 | CLK   | CLK_ICKR       | Internal clock control register                  | 0x01               |  |  |

| 0x00 50C1                 | - CLK | CLK_ECKR       | External clock control register                  | 0x00               |  |  |

| 0x00 50C2                 |       |                | Reserved area (1 byte)                           |                    |  |  |

| 0x00 50C3                 |       | CLK_CMSR       | Clock master status register                     | 0xE1               |  |  |

| 0x00 50C4                 | ]     | CLK_SWR        | Clock master switch register                     | 0xE1               |  |  |

| 0x00 50C5                 |       | CLK_SWCR       | Clock switch control register                    | 0xXX               |  |  |

| 0x00 50C6                 |       | CLK_CKDIVR     | Clock divider register                           | 0x18               |  |  |

| 0x00 50C7                 | CLK   | CLK_PCKENR1    | Peripheral clock gating register 1               | 0xFF               |  |  |

| 0x00 50C8                 |       | CLK_CSSR       | Clock security system register                   | 0x00               |  |  |

| 0x00 50C9                 |       | CLK_CCOR       | Configurable clock control register              | 0x00               |  |  |

| 0x00 50CA                 |       | CLK_PCKENR2    | Peripheral clock gating register 2               | 0xFF               |  |  |

| 0x00 50CB                 |       | CLK_CANCCR     | CAN clock control register                       | 0x00               |  |  |

Table 9. General hardware register map

|                           | Table 9  | . General hardwar | e register map (continued)                 |                     |

|---------------------------|----------|-------------------|--------------------------------------------|---------------------|

| Address                   | Block    | Register label    | Register name                              | Reset<br>status     |

| 0x00 50CC                 |          | CLK_HSITRIMR      | HSI clock calibration trimming register    | 0x00                |

| 0x00 50CD                 | CLK      | CLK_SWIMCCR       | SWIM clock control register                | 0bXXXX<br>XXX0      |

| 0x00 50CE to<br>0x00 50D0 |          |                   | Reserved area (3 bytes)                    |                     |

| 0x00 50D1                 | WWDG     | WWDG_CR           | WWDG control register                      | 0x7F                |

| 0x00 50D2                 | - www.DG | WWDG_WR           | WWDR window register                       | 0x7F                |

| 0x00 50D3 to<br>0x00 50DF |          |                   | Reserved area (13 bytes)                   |                     |

| 0x00 50E0                 |          | IWDG_KR           | IWDG key register                          | 0xXX <sup>(2)</sup> |

| 0x00 50E1                 | IWDG     | IWDG_PR           | IWDG prescaler register                    | 0x00                |

| 0x00 50E2                 |          | IWDG_RLR          | IWDG reload register                       | 0xFF                |

| 0x00 50E3 to<br>0x00 50EF |          |                   | Reserved area (13 bytes)                   |                     |

| 0x00 50F0                 |          | AWU_CSR1          | AWU control/status register 1              | 0x00                |

| 0x00 50F1                 | AWU      | AWU_APR           | AWU asynchronous prescaler buffer register | 0x3F                |

| 0x00 50F2                 |          | AWU_TBR           | AWU timebase selection register            | 0x00                |

| 0x00 50F3                 | BEEP     | BEEP_CSR          | BEEP control/status register               | 0x1F                |

| 0x00 50F4 to<br>0x00 50FF |          |                   | Reserved area (12 bytes)                   |                     |

| 0x00 5200                 |          | SPI_CR1           | SPI control register 1                     | 0x00                |

| 0x00 5201                 |          | SPI_CR2           | SPI control register 2                     | 0x00                |

| 0x00 5202                 |          | SPI_ICR           | SPI interrupt control register             | 0x00                |

| 0x00 5203                 | SPI      | SPI_SR            | SPI status register                        | 0x02                |

| 0x00 5204                 | 551      | SPI_DR            | SPI data register                          | 0x00                |

| 0x00 5205                 |          | SPI_CRCPR         | SPI CRC polynomial register                | 0x07                |

| 0x00 5206                 |          | SPI_RXCRCR        | SPI Rx CRC register                        | 0xFF                |

| 0x00 5207                 |          | SPI_TXCRCR        | SPI Tx CRC register                        | 0xFF                |

| 0x00 5208 to<br>0x00 520F |          |                   | Reserved area (8 bytes)                    |                     |

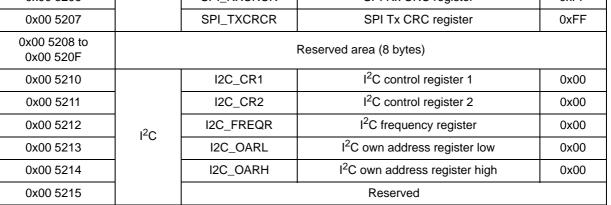

| 0x00 5210                 |          | I2C_CR1           | I <sup>2</sup> C control register 1        | 0x00                |

| 0x00 5211                 |          | 12C CR2           | I <sup>2</sup> C control register 2        | 0x00                |

| Address                   | Block   | Register label            | Register name        | Reset<br>status     |  |  |

|---------------------------|---------|---------------------------|----------------------|---------------------|--|--|

| 0x00 5428                 |         | CAN_P0                    | CAN paged register 0 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5429                 |         | CAN_P1                    | CAN paged register 1 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542A                 |         | CAN_P2                    | CAN paged register 2 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542B                 | _       | CAN_P3                    | CAN paged register 3 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542C                 | _       | CAN_P4                    | CAN paged register 4 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542D                 | _       | CAN_P5                    | CAN paged register 5 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542E                 | _       | CAN_P6                    | CAN paged register 6 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 542F                 |         | CAN_P7                    | CAN paged register 7 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5430                 | - beCAN | CAN_P8                    | CAN paged register 8 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5431                 | _       | CAN_P9                    | CAN paged register 9 | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5432                 | _       | CAN_PA                    | CAN paged register A | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5433                 | -       | CAN_PB                    | CAN paged register B | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5434                 | _       | CAN_PC                    | CAN paged register C | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5435                 | _       | CAN_PD                    | CAN paged register D | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5436                 | 1       | CAN_PE                    | CAN paged register E | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5437                 |         | CAN_PF                    | CAN paged register F | 0xXX <sup>(3)</sup> |  |  |

| 0x00 5438 to<br>0x00 57FF |         | Reserved area (968 bytes) |                      |                     |  |  |

| Table 0  | Gonoral | hardwaro | rogistor | man | (continued) |   |

|----------|---------|----------|----------|-----|-------------|---|

| Table 9. | General | naruware | register | map | (continued) | , |

1. Depends on the previous reset source.

2. Write only register.

3. If the bootloader is enabled, it is initialized to 0x00.

| Option byte no. | Description                                                                                                                                                                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | LSI_EN: Low speed internal clock enable<br>0: LSI clock is not available as CPU clock source<br>1: LSI clock is available as CPU clock source                                                                                                                                                  |

| 0070            | <ul><li>IWDG_HW: Independent watchdog</li><li>0: IWDG Independent watchdog activated by software</li><li>1: IWDG Independent watchdog activated by hardware</li></ul>                                                                                                                          |

| OPT3            | <ul><li>WWDG_HW: Window watchdog activation</li><li>0: WWDG window watchdog activated by software</li><li>1: WWDG window watchdog activated by hardware</li></ul>                                                                                                                              |

|                 | WWDG_HALT: Window watchdog reset on halt<br>0: No reset generated on halt if WWDG active<br>1: Reset generated on halt if WWDG active                                                                                                                                                          |

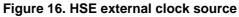

|                 | <b>EXTCLK:</b> <i>External clock selection</i><br>0: External crystal connected to OSCIN/OSCOUT<br>1: External clock signal on OSCIN                                                                                                                                                           |

| OPT4            | CKAWUSEL: Auto wakeup unit/clock<br>0: LSI clock source selected for AWU<br>1: HSE clock with prescaler selected as clock source for AWU                                                                                                                                                       |

|                 | PRSC[1:0] AWU clock prescaler<br>00: 24 MHz to 128 kHz prescaler<br>01: 16 MHz to 128 kHz prescaler<br>10: 8 MHz to 128 kHz prescaler<br>11: 4 MHz to 128 kHz prescaler                                                                                                                        |

| OPT5            | HSECNT[7:0]: HSE crystal oscillator stabilization time<br>This configures the stabilization time.<br>0x00: 2048 HSE cycles<br>0xB4: 128 HSE cycles<br>0xD2: 8 HSE cycles<br>0xE1: 0.5 HSE cycles                                                                                               |

| OPT6            | Reserved                                                                                                                                                                                                                                                                                       |

| OPT7            | <ul> <li>WAITSTATE Wait state configuration</li> <li>This option configures the number of wait states inserted when reading from the Flash/data EEPROM memory.</li> <li>1 wait state is required if f<sub>CPU</sub> &gt; 16 MHz.</li> <li>0: No wait state</li> <li>1: 1 wait state</li> </ul> |

|  | Table 13. O | ption byte | description | (continued) |

|--|-------------|------------|-------------|-------------|

|--|-------------|------------|-------------|-------------|

# Total current consumption and timing in forced reset state

| Symbol               | Parameter                                | Conditions              | Тур | Max <sup>(1)</sup> | Unit |

|----------------------|------------------------------------------|-------------------------|-----|--------------------|------|

| I <sub>DD(R)</sub>   | Supply current in reset state            | $V_{DD} = 5 V$          | 1.6 |                    | mA   |

|                      | Supply current in reset state            | V <sub>DD</sub> = 3.3 V | 0.8 |                    | ША   |

| t <sub>RESETBL</sub> | Reset release to bootloader vector fetch |                         |     | 150                | μs   |

#### Table 29. Total current consumption and timing in forced reset state

1. Data guaranteed by design, not tested in production.

# **Current consumption of on-chip peripherals**

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

HSI internal RC/ $f_{CPU} = f_{MASTER} = 16$  MHz.

#### Table 30. Peripheral current consumption

| Symbol                            | Parameter                                          | Тур. | Unit |

|-----------------------------------|----------------------------------------------------|------|------|

| I <sub>DD(TIM1)</sub>             | TIM1 supply current <sup>(1)</sup>                 | 220  |      |

| I <sub>DD(TIM2)</sub>             | TIM2 supply current <sup>(1)</sup>                 | 120  |      |

| I <sub>DD(TIM3)</sub>             | TIM3 timer supply current <sup>(1)</sup>           | 100  |      |

| I <sub>DD(TIM4)</sub>             | TIM4 timer supply current <sup>(1)</sup>           | 25   |      |

| I <sub>DD(UART1)</sub>            | UART1 supply current <sup>(2)</sup>                | 90   |      |

| I <sub>DD(UART3)</sub>            | UART3 supply current <sup>(2)</sup>                | 110  | μA   |

| I <sub>DD(SPI)</sub>              | SPI supply current <sup>(2)</sup>                  | 40   |      |

| I <sub>DD(I</sub> <sup>2</sup> C) | I <sup>2</sup> C supply current <sup>(2)</sup>     | 50   |      |

| I <sub>DD(CAN)</sub>              | beCAN supply current <sup>(2)</sup>                | 210  |      |

| I <sub>DD(ADC2)</sub>             | ADC2 supply current when converting <sup>(3)</sup> | 1000 |      |

1. Data based on a differential  $I_{DD}$  measurement between reset configuration and timer counter running at 16 MHz. No IC/OC programmed (no I/O pads toggling). Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between the on-chip peripheral when kept under reset and not clocked and the on-chip peripheral when clocked and not kept under reset. No I/O pads toggling. Not tested in production.

Data based on a differential I<sub>DD</sub> measurement between reset configuration and continuous A/D conversions. Not tested in production.

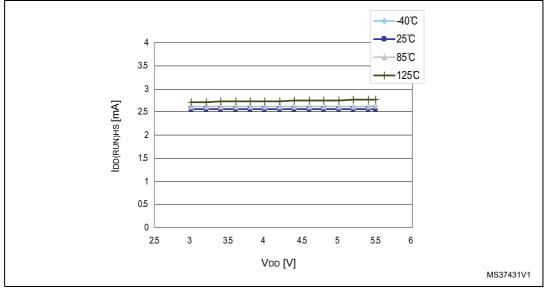

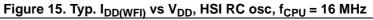

# **Current consumption curves**

*Figure 14* and *Figure 15* show typical current consumption measured with code executing in RAM.

Figure 14. Typ. I<sub>DD(RUN)</sub> vs V<sub>DD</sub>, HSI RC osc, f<sub>CPU</sub> = 16 MHz

# **10.3.3** External clock sources and timing characteristics

# HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Table 31. HSE us | ser external clock | characteristics |

|------------------|--------------------|-----------------|

|------------------|--------------------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency |                            | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      |                            | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       |                            | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    |     | 1                       | μA   |

1. Data based on characterization results, not tested in production.

# HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

# **10.3.4** Internal clock sources and timing characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}\text{.}\ f_{\text{HSE}}$

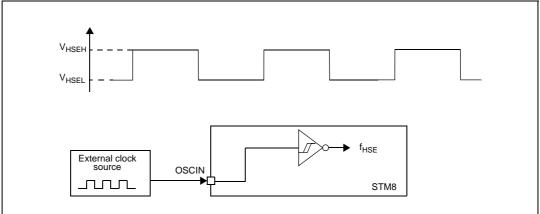

# High speed internal RC oscillator (HSI)

| Symbol               | Parameter                                          | Conditions                                                                                                                                  | Min                 | Тур | Max                | Unit |

|----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|--------------------|------|

| f <sub>HSI</sub>     | Frequency                                          |                                                                                                                                             |                     | 16  |                    | MHz  |

|                      | Accuracy of HSI oscillator                         | Trimmed by the CLK_HSITRIMR register for given $V_{DD}$ and $T_A$ conditions                                                                | -1.0 <sup>(1)</sup> |     | 1.0                |      |

|                      |                                                    | V <sub>DD</sub> = 5 V, T <sub>A</sub> = 25 °C                                                                                               | -1.5                |     | 1.5                |      |

| ACC <sub>HSI</sub>   | Accuracy of HSI assoillator                        |                                                                                                                                             | -2.2                |     | 2.2                | %    |

|                      | Accuracy of HSI oscillator<br>(factory calibrated) | $\begin{array}{l} 2.95 \text{ V} \leq \text{ V}_{DD} \leq \text{ 5.5 V,} \\ \text{-40 °C} \leq \text{ T}_A \leq \text{ 125 °C} \end{array}$ | -3.0 <sup>(2)</sup> |     | 3.0 <sup>(2)</sup> |      |

| t <sub>su(HSI)</sub> | HSI oscillator wakeup time including calibration   |                                                                                                                                             |                     |     | 1.0 <sup>(1)</sup> | μs   |

| I <sub>DD(HSI)</sub> | HSI oscillator power<br>consumption                |                                                                                                                                             |                     | 170 | 250 <sup>(2)</sup> | μA   |

# Table 33. HSI oscillator characteristics

1. Guaranteed by design, not tested in production.

2. Data based on characterization results, not tested in production

# Figure 18. Typical HSI frequency variation vs V<sub>DD</sub> at 4 temperatures

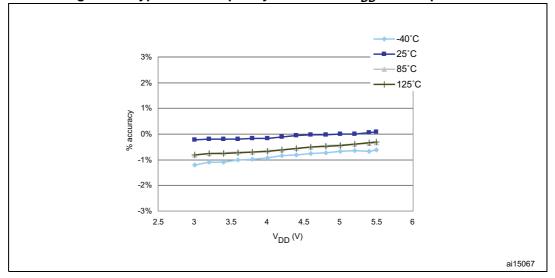

Figure 22. Typical pull-up current vs  $V_{\text{DD}} @$  4 temperatures

1. The pull-up is a pure resistor (slope goes through 0).

| Symbol          | Parameter                             | Conditions                                      | Min                | Max              | Unit |

|-----------------|---------------------------------------|-------------------------------------------------|--------------------|------------------|------|

| M               | Output low level with 8 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$  |                    | 2                | V    |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | I <sub>IO</sub> = 4 mA, V <sub>DD</sub> = 3.3 V |                    | 1 <sup>(1)</sup> | V    |

| V               | Output high level with 8 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$  | 2.8                |                  | V    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | $I_{IO} = 4 \text{ mA}, V_{DD} = 3.3 \text{ V}$ | 2.1 <sup>(1)</sup> |                  | v    |

# Table 38. Output driving current (standard ports)

1. Data based on characterization results, not tested in production

| Table 39. | Output driving | a current ( | (true oper | n drain ports) |  |

|-----------|----------------|-------------|------------|----------------|--|

|           |                | ,           |            |                |  |

| Symbol          | Parameter                         | Conditions                                       | Max                | Unit |

|-----------------|-----------------------------------|--------------------------------------------------|--------------------|------|

|                 |                                   | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   | 1                  |      |

| V <sub>OL</sub> | Output low level with 2 pins sunk | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 3.3 V | 1.5 <sup>(1)</sup> | V    |

|                 |                                   | I <sub>IO</sub> = 20 mA, V <sub>DD</sub> = 5 V   | 2 <sup>(1)</sup>   |      |

1. Data based on characterization results, not tested in production

| Symbol          | Parameter                             | Conditions                                       | Min                | Max                | Unit |

|-----------------|---------------------------------------|--------------------------------------------------|--------------------|--------------------|------|

|                 | Output low level with 8 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   |                    | 0.8                |      |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 3.3 \text{ V}$ |                    | 1 <sup>(1)</sup>   |      |

|                 | Output low level with 4 pins sunk     | $I_{IO} = 20 \text{ mA}, V_{DD} = 5 \text{ V}$   |                    | 1.5 <sup>(1)</sup> | V    |

|                 | Output high level with 8 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   | 4.0                |                    | v    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 3.3 \text{ V}$ | 2.1 <sup>(1)</sup> |                    |      |

|                 | Output high level with 4 pins sourced | $I_{IO} = 20 \text{ mA}, V_{DD} = 5 \text{ V}$   | 3.3 <sup>(1)</sup> |                    |      |

1. Data based on characterization results, not tested in production

# 10.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions             | Min                         | <b>Typ</b> <sup>1)</sup> | Max                   | Unit |

|-------------------------|----------------------------------------------|------------------------|-----------------------------|--------------------------|-----------------------|------|

| V <sub>IL(NRST)</sub>   | NRST Input low level voltage <sup>(1)</sup>  |                        | -0.3 V                      |                          | 0.3 x V <sub>DD</sub> |      |

| V <sub>IH(NRST)</sub>   | NRST Input high level voltage <sup>(1)</sup> |                        | $0.7 	ext{ x V}_{	ext{DD}}$ |                          | V <sub>DD</sub> + 0.3 | V    |

| V <sub>OL(NRST)</sub>   | NRST Output low level voltage (1)            | I <sub>OL</sub> = 2 mA |                             |                          | 0.5                   |      |

| R <sub>PU(NRST)</sub>   | NRST Pull-up resistor <sup>(2)</sup>         |                        | 30                          | 55                       | 80                    | kΩ   |

| t <sub>IFP(NRST)</sub>  | NRST Input filtered pulse <sup>(3)</sup>     |                        |                             |                          | 75                    | ns   |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse <sup>(3)</sup> |                        | 500                         |                          |                       | ns   |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(1)</sup>             |                        | 15                          |                          |                       | μs   |

| Table 41. | NRST | pin  | characteristics |

|-----------|------|------|-----------------|

|           |      | PIII | characteristics |

1. Data based on characterization results, not tested in production.

2. The  $\rm R_{\rm PU}$  pull-up equivalent resistor is based on a resistive transistor

3. Data guaranteed by design, not tested in production.

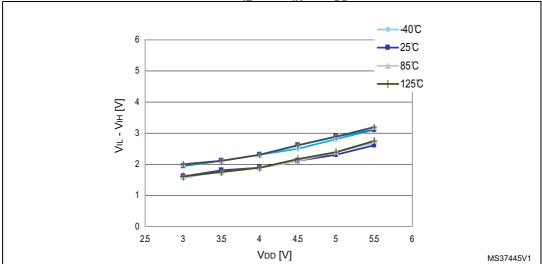

# Figure 33. Typical NRST $\rm V_{IL}$ and $\rm V_{IH}$ vs $\rm V_{DD}$ @ 4 temperatures

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

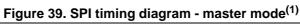

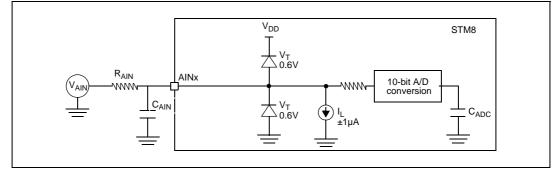

Figure 40. Typical application with I<sup>2</sup>C bus and timing diagram

1. Measurement points are made at CMOS levels: 0.3 x  $V_{\text{DD}}$  and 0.7 x  $V_{\text{DD}}$

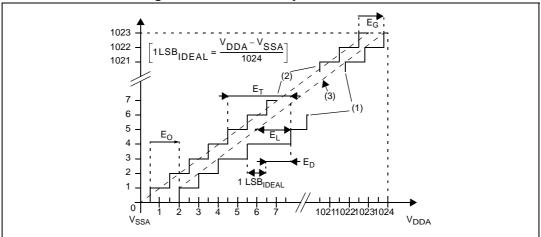

1. Example of an actual transfer curve.

- 2. The ideal transfer curve

- 3.

End point correlation line  $E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_0$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.  $E_D$  = Differential linearity error: maximum deviation between actual steps and the ideal one.  $E_L$  = Integral linearity error: maximum deviation between any actual transition and the end point correlation between any actual transition and the end point correlation line.

### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance:

- A supply overvoltage (applied to each power supply pin)

- A current injection (applied to each input, output and configurable I/O pin) is performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol | Parameter                | Conditions              | Class <sup>(1)</sup> |

|--------|--------------------------|-------------------------|----------------------|

|        |                          | T <sub>A</sub> = 25 °C  | А                    |

| LU     | LU Static latch-up class | $T_A = 85 \ ^{\circ}C$  | А                    |

|        |                          | T <sub>A</sub> = 125 °C | А                    |

| Table 50. I | Electrical | sensitivities |

|-------------|------------|---------------|

|-------------|------------|---------------|

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

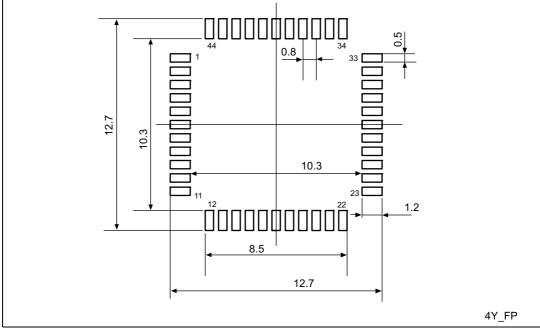

Figure 54. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

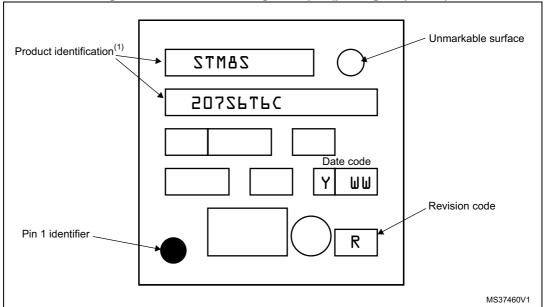

### **Device marking**

The following figure shows the marking for the LQFP44 package.

Figure 55. LQFP44 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID14733 Rev 13

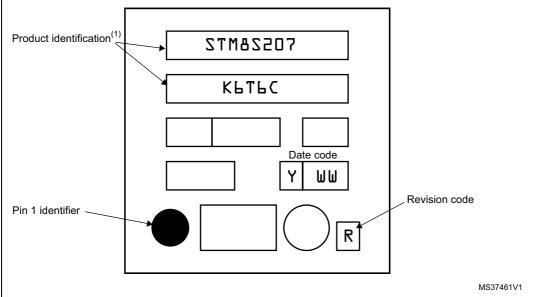

# **Device marking**

The following figure shows the marking for the LQFP32 package.

Figure 58. LQFP32 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity. 1.

# **11.2** Thermal characteristics

The maximum chip junction temperature  $(T_{Jmax})$  must never exceed the values given in *Table 18: General operating conditions on page 56.*

The maximum chip-junction temperature,  $T_{Jmax}$ , in degrees Celsius, may be calculated using the following equation:

$T_{Jmax} = T_{Amax} + (P_{Dmax} \times \Theta_{JA})$

Where:

- T<sub>Amax</sub> is the maximum ambient temperature in °C

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance in ° C/W

- P<sub>Dmax</sub> is the sum of P<sub>INTmax</sub> and P<sub>I/Omax</sub> (P<sub>Dmax</sub> = P<sub>INTmax</sub> + P<sub>I/Omax</sub>)

- P<sub>INTmax</sub> is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

- $P_{I/Omax}$  represents the maximum power dissipation on output pins, where:  $P_{I/Omax} = \Sigma (V_{OL}*I_{OL}) + \Sigma ((V_{DD}-V_{OH})*I_{OH})$ , and taking account of the actual  $V_{OL}/I_{OL}$  and  $V_{OH}/I_{OH}$  of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                   | Value | Unit |

|---------------|-------------------------------------------------------------|-------|------|

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 80 - 14 x 14 mm | 38    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 64 - 14 x 14 mm | 45    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 64 - 10 x 10 mm | 46    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 48 - 7 x 7 mm   | 57    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 44 - 10 x 10 mm | 54    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP 32 - 7 x 7 mm   | 60    | °C/W |

| Table 57. Thermal characteristics | hermal characteristics <sup>(1)</sup> |

|-----------------------------------|---------------------------------------|

|-----------------------------------|---------------------------------------|

1. Thermal resistances are based on JEDEC JESD51-2 with 4-layer PCB in a natural convection environment.

# 11.2.1 Reference document

JESD51-2 integrated circuits thermal test method environment conditions - natural convection (still air). Available from www.jedec.org.

# **13** Ordering information

| Example:                          | STM8 | S | 208 | М | В | т | 6 | В | TR |

|-----------------------------------|------|---|-----|---|---|---|---|---|----|

|                                   |      |   |     |   |   |   |   |   |    |

| Product class -                   |      |   |     |   |   |   |   |   |    |

| STM8 microcontroller              |      |   |     |   |   |   |   |   |    |

| Family type                       |      |   |     |   |   |   |   |   |    |

| S = Standard                      |      |   |     |   |   |   |   |   |    |

| Sub-family type <sup>(2)</sup>    |      |   |     |   |   |   |   |   |    |

| 208 = Full peripheral set         |      |   |     |   |   |   |   |   |    |

| 207 = Intermediate peripheral set |      |   |     |   |   |   |   |   |    |

| Pin count                         |      |   |     |   |   |   |   |   |    |

| K = 32 pins                       |      |   |     |   |   |   |   |   |    |

| S = 44 pins                       |      |   |     |   |   |   |   |   |    |

| C = 48 pins                       |      |   |     |   |   |   |   |   |    |

| R = 64 pins                       |      |   |     |   |   |   |   |   |    |

| M = 80 pins                       |      |   |     |   |   |   |   |   |    |

| Program memory size               |      |   |     |   |   |   |   |   |    |

| 6 = 32 Kbyte                      |      |   |     |   |   |   |   |   |    |

| 8 = 64 Kbyte                      |      |   |     |   |   |   |   |   |    |

| B = 128 Kbyte                     |      |   |     |   |   |   |   |   |    |

| Package type                      |      |   |     |   |   |   |   |   |    |

| T = LQFP                          |      |   |     |   |   |   |   |   |    |

| Temperature range                 |      |   |     |   |   |   |   |   |    |

| 3 = -40 °C to 125 °C              |      |   |     |   |   |   |   |   |    |

| 6 = -40 °C to 85 °C               |      |   |     |   |   |   |   |   |    |

| Package pitch                     |      |   |     |   |   |   |   | ] |    |

| No character = 0.5 mm             |      |   |     |   |   |   |   |   |    |

| B = 0.65 mm                       |      |   |     |   |   |   |   |   |    |

| C = 0.8 mm                        |      |   |     |   |   |   |   |   |    |

| Packing –                         |      |   |     |   |   |   |   |   |    |

| No character = Tray or tube       |      |   |     |   |   |   |   |   |    |

For a list of available options (e.g. memory size, package) and order-able part numbers or for further information on any aspect of this device, please go to <u>www.st.com</u> or contact the ST Sales Office nearest to you.

2. Refer to Table 2: STM8S20xxx performance line features for detailed description.