#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 9x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207s6t6c |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet contains the description of the STM8S20xxx features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S microcontroller family reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the STM8S Flash programming manual (PM0051).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

# 2 Description

The STM8S20xxx performance line 8-bit microcontrollers offer from 32 to 128 Kbytes Flash program memory. They are referred to as high-density devices in the STM8S microcontroller family reference manual.

All STM8S20xxx devices provide the following benefits: reduced system cost, performance robustness, short development cycles, and product longevity.

The system cost is reduced thanks to an integrated true data EEPROM for up to 300 k write/erase cycles and a high system integration level with internal clock oscillators, watchdog, and brown-out reset.

Device performance is ensured by 20 MIPS at 24 MHz CPU clock frequency and enhanced characteristics which include robust I/O, independent watchdogs (with a separate clock source), and a clock security system.

Short development cycles are guaranteed due to application scalability across a common family product architecture with compatible pinout, memory map and modular peripherals. Full documentation is offered with a wide choice of development tools.

Product longevity is ensured in the STM8S family thanks to their advanced core which is made in a state-of-the art technology for applications with 2.95 V to 5.5 V operating supply.

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### LIN master capability

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

#### LIN slave mode

- Autonomous header handling one single interrupt per valid message header

- Automatic baud rate synchronization maximum tolerated initial clock deviation ±15%

- Sync delimiter checking

- 11-bit LIN sync break detection break detection always active

- Parity check on the LIN identifier field

- LIN error management

- Hot plugging support

#### 4.14.3 SPI

- Maximum speed: 10 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

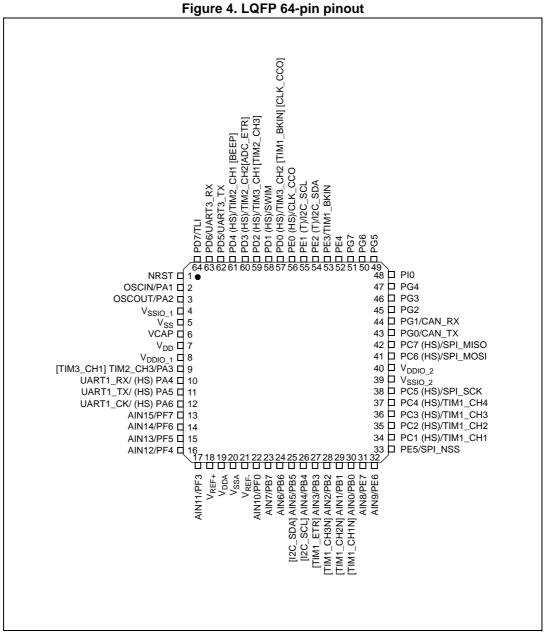

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

4. CAN\_RX and CAN\_TX is available on STM8S208xx devices only.

| Туре             | I= Input, O                                                                                                                                                                          | Input, O = Output, S = Power supply                                                                                                                       |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Level            | Input                                                                                                                                                                                | nput CM = CMOS                                                                                                                                            |  |  |  |  |  |

|                  | Output HS = High sink                                                                                                                                                                |                                                                                                                                                           |  |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s                                                                                                                                                           | up to 2 MHz)<br>up to 10 MHz)<br>low programmability with slow as default state after reset<br>low programmability with fast as default state after reset |  |  |  |  |  |

| Port and control | Input                                                                                                                                                                                | float = floating, wpu = weak pull-up                                                                                                                      |  |  |  |  |  |

| configuration    | Output                                                                                                                                                                               | T = True open drain, OD = Open drain, PP = Push pull                                                                                                      |  |  |  |  |  |

| Reset state      | Bold $\underline{X}$ (pin state after internal reset release)<br>Unless otherwise specified, the pin state is the same during the reset phase a<br>after the internal reset release. |                                                                                                                                                           |  |  |  |  |  |

| Table 5. Legend/abbreviations | for pinout table |

|-------------------------------|------------------|

|-------------------------------|------------------|

|        | Pin    | num    | ber    |        |                     |      |          | Inpu     | t              |           | Out   | put |   |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------|------|----------|----------|----------------|-----------|-------|-----|---|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name            | Type | floating | ndw      | Ext. interrupt | High sink | Speed | QO  | Ы | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | 1      | 1      | 1      | NRST                | I/O  |          | <u>X</u> |                |           |       |     |   | Reset                          |                                  |                                                      |

| 2      | 2      | 2      | 2      | 2      | PA1/OSCIN           | I/O  | <u>x</u> | х        |                |           | 01    | х   | х | Port A1                        | Resonator/<br>crystal in         |                                                      |

| 3      | 3      | 3      | 3      | 3      | PA2/OSCOUT          | I/O  | X        | х        | х              |           | 01    | х   | х | Port A2                        | Resonator/<br>crystal out        |                                                      |

| 4      | 4      | 4      | 4      | -      | V <sub>SSIO_1</sub> | S    |          |          |                |           |       |     |   | I/O groun                      | d                                |                                                      |

| 5      | 5      | 5      | 5      | 4      | V <sub>SS</sub>     | S    |          |          |                |           |       |     |   | Digital gro                    | ound                             |                                                      |

| 6      | 6      | 6      | 6      | 5      | VCAP                | S    |          |          |                |           |       |     |   | 1.8 V reg                      | ulator capacitor                 |                                                      |

| 7      | 7      | 7      | 7      | 6      | V <sub>DD</sub>     | S    |          |          |                |           |       |     |   | Digital po                     | wer supply                       |                                                      |

| 8      | 8      | 8      | 8      | 7      | V <sub>DDIO_1</sub> | S    |          |          |                |           |       |     |   | I/O powe                       | r supply                         |                                                      |

| 9      | 9      | 9      | -      | -      | PA3/TIM2_CH3        | I/O  | <u>x</u> | х        | Х              |           | 01    | х   | х |                                |                                  | TIM3_CH1<br>[AFR1]                                   |

| 10     | 10     | 10     | 9      | -      | PA4/UART1_RX        | I/O  | X        | х        | Х              | HS        | O3    | х   | Х | Port A4                        | UART1<br>receive                 |                                                      |

| 11     | 11     | 11     | 10     | -      | PA5/UART1_TX        | I/O  | <u>x</u> | х        | Х              | HS        | О3    | Х   | Х | Port A5                        | UART1<br>transmit                |                                                      |

### Table 6. Pin description

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTBL           | <ul> <li>BL[7:0] Bootloader option byte</li> <li>For STM8S products, this option is checked by the boot ROM code after reset. Depending on the content of addresses 0x487E, 0x487F, and 0x8000 (reset vector), the CPU jumps to the bootloader or to the reset vector. Refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> <li>For STM8L products, the bootloader option bytes are on addresses 0xXXXX and 0xXXXX+1 (2 bytes). These option bytes control whether the bootloader is active or not. For more details, refer to the UM0560 (STM8L/S bootloader manual) for more details.</li> </ul> |

Table 13. Option byte description (continued)

#### Total current consumption in wait mode

| Symbol               | Parameter                         | Condit                                                      | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------------------|-----------------------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

|                      |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.4                |      |    |

|                      |                                   | $T_A \leq 105 \ ^{\circ}C$                                  | HSE user ext. clock (24 MHz)          | 1.8                | 4.7  |    |

|                      | Supply<br>current in<br>wait mode | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 2.0                |      |    |

|                      |                                   |                                                             | HSE user ext. clock (16 MHz)          | lz) 1.4 4          | 4.4  |    |

| I <sub>DD(WFI)</sub> |                                   |                                                             | HSI RC osc. (16 MHz)                  | 1.2                | 1.6  | mA |

|                      | wait mode                         | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.0                |      |    |

|                      |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55               |      |    |

|                      |                                   | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.5                |      |    |

#### Table 22. Total current consumption in wait mode at $V_{DD}$ = 5 V

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

| Symbol               | Parameter            | Condi                                                       | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------------------|----------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.0                |      |    |

|                      |                      | $T_A \leq 105 \ ^{\circ}C$                                  | HSE user ext. clock (24 MHz)          | 1.8                | 4.7  |    |

|                      |                      |                                                             | HSE crystal osc. (16 MHz)             | 1.6                |      |    |

|                      | Supply               | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)          | 1.4                | 4.4  |    |

| I <sub>DD(WFI)</sub> | Supply<br>current in |                                                             | HSI RC osc. (16 MHz)                  | 1.2                | 1.6  | mA |

|                      | wait mode            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.0                |      |    |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55               |      |    |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | LSI RC osc. (128 kHz)                 | 0.5                |      |    |

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

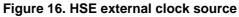

## **10.3.3** External clock sources and timing characteristics

#### HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Table 31. HSE us | ser external clock | characteristics |

|------------------|--------------------|-----------------|

|------------------|--------------------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency |                            | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      |                            | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       |                            | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    |     | 1                       | μA   |

1. Data based on characterization results, not tested in production.

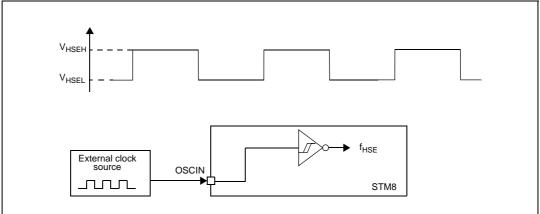

#### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                              | Parameter                                   | Conditions                              | Min | Тур | Мах                                            | Unit |

|-------------------------------------|---------------------------------------------|-----------------------------------------|-----|-----|------------------------------------------------|------|

| f <sub>HSE</sub>                    | External high speed oscillator<br>frequency |                                         | 1   |     | 24                                             | MHz  |

| R <sub>F</sub>                      | Feedback resistor                           |                                         |     | 220 |                                                | kΩ   |

| C <sup>(1)</sup>                    | Recommended load capacitance (2)            |                                         |     |     | 20                                             | pF   |

| I <sub>DD(HSE)</sub>                | HSE oscillator power consumption            | C = 20 pF,<br>f <sub>OSC</sub> = 24 MHz |     |     | 6 (startup)<br>2 (stabilized) <sup>(3)</sup>   | mA   |

|                                     |                                             | C = 10 pF,<br>f <sub>OSC</sub> = 24 MHz |     |     | 6 (startup)<br>1.5 (stabilized) <sup>(3)</sup> | IIIA |

| 9 <sub>m</sub>                      | Oscillator transconductance                 |                                         | 5   |     |                                                | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | $V_{\text{DD}}$ is stabilized           |     | 1   |                                                | ms   |

| Table 32. HSE oscillator characterist | ics |

|---------------------------------------|-----|

|---------------------------------------|-----|

1. C is approximately equivalent to 2 x crystal Cload.

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small R<sub>m</sub> value. Refer to crystal manufacturer for more details

3. Data based on characterization results, not tested in production.

t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 24 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### Figure 17. HSE oscillator circuit diagram

#### HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

$\begin{array}{l} {\sf R}_m: \mbox{ Notional resistance (see crystal specification)} \\ {\sf L}_m: \mbox{ Notional inductance (see crystal specification)} \\ {\sf C}_m: \mbox{ Notional capacitance (see crystal specification)} \\ {\sf Co: Shunt capacitance (see crystal specification)} \\ {\sf C}_{L1} = {\sf C}_{L2} = {\sf C}: \mbox{ Grounded external capacitance } \\ {\sf g}_m >> {\sf g}_{mcrit} \end{array}$

DocID14733 Rev 13

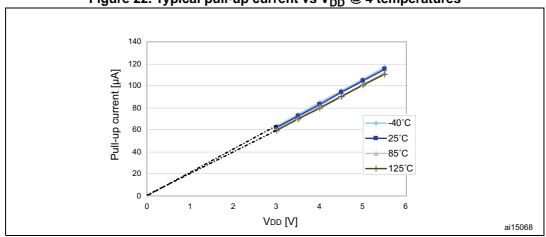

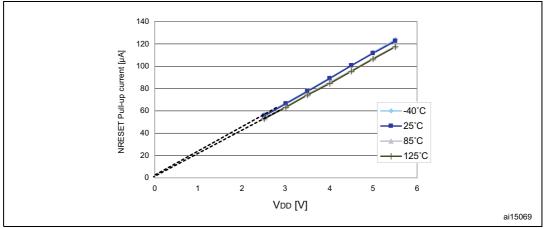

Figure 22. Typical pull-up current vs  $V_{\text{DD}} @$  4 temperatures

1. The pull-up is a pure resistor (slope goes through 0).

| Symbol          | Parameter                             | Conditions                                      |                    | Max              | Unit |

|-----------------|---------------------------------------|-------------------------------------------------|--------------------|------------------|------|

| M               | Output low level with 8 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$  |                    | 2                | V    |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | I <sub>IO</sub> = 4 mA, V <sub>DD</sub> = 3.3 V |                    | 1 <sup>(1)</sup> | V    |

| V               | Output high level with 8 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$  | 2.8                |                  | V    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | $I_{IO} = 4 \text{ mA}, V_{DD} = 3.3 \text{ V}$ | 2.1 <sup>(1)</sup> |                  | v    |

#### Table 38. Output driving current (standard ports)

1. Data based on characterization results, not tested in production

| Table 39. | Output driving | a current ( | (true oper | n drain ports) |  |

|-----------|----------------|-------------|------------|----------------|--|

|           |                | ,           |            |                |  |

| Symbol          | Parameter                         | Conditions                                       | Max                | Unit |

|-----------------|-----------------------------------|--------------------------------------------------|--------------------|------|

|                 |                                   | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   | 1                  |      |

| V <sub>OL</sub> | Output low level with 2 pins sunk | I <sub>IO</sub> = 10 mA, V <sub>DD</sub> = 3.3 V | 1.5 <sup>(1)</sup> | V    |

|                 |                                   | I <sub>IO</sub> = 20 mA, V <sub>DD</sub> = 5 V   | 2 <sup>(1)</sup>   |      |

1. Data based on characterization results, not tested in production

| Symbol          | Parameter                             | Conditions                                       | Min                | Max                | Unit |

|-----------------|---------------------------------------|--------------------------------------------------|--------------------|--------------------|------|

|                 | Output low level with 8 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   |                    | 0.8                |      |

| V <sub>OL</sub> | Output low level with 4 pins sunk     | $I_{IO} = 10 \text{ mA}, V_{DD} = 3.3 \text{ V}$ |                    | 1 <sup>(1)</sup>   |      |

|                 | Output low level with 4 pins sunk     | $I_{IO} = 20 \text{ mA}, V_{DD} = 5 \text{ V}$   |                    | 1.5 <sup>(1)</sup> | V    |

|                 | Output high level with 8 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 5 \text{ V}$   | 4.0                |                    | v    |

| V <sub>OH</sub> | Output high level with 4 pins sourced | $I_{IO} = 10 \text{ mA}, V_{DD} = 3.3 \text{ V}$ | 2.1 <sup>(1)</sup> |                    |      |

|                 | Output high level with 4 pins sourced | $I_{IO} = 20 \text{ mA}, V_{DD} = 5 \text{ V}$   | 3.3 <sup>(1)</sup> |                    |      |

1. Data based on characterization results, not tested in production

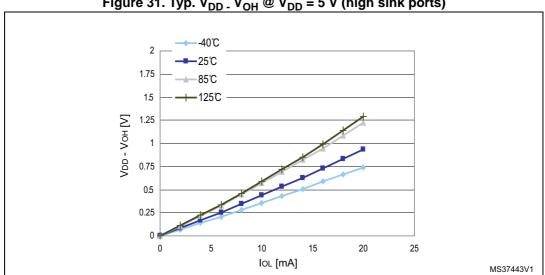

Figure 31. Typ.  $V_{DD}$  -  $V_{OH}$  @  $V_{DD}$  = 5 V (high sink ports)

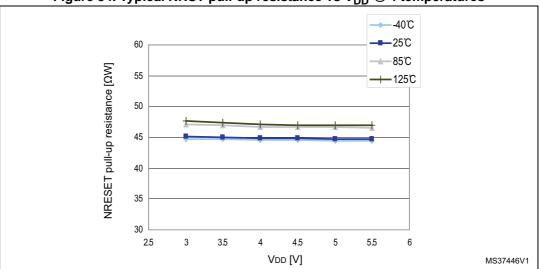

Figure 34. Typical NRST pull-up resistance vs V<sub>DD</sub> @ 4 temperatures

Figure 35. Typical NRST pull-up current vs V<sub>DD</sub> @ 4 temperatures

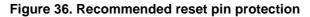

The reset network shown in *Figure 36* protects the device against parasitic resets. The user must ensure that the level on the NRST pin can go below the  $V_{IL}$  max. level specified in *Table 41*. Otherwise the reset is not taken into account internally. For power consumption sensitive applications, the capacity of the external reset capacitor can be reduced to limit charge/discharge current. If the NRSTsignal is used to reset the external circuitry, care must be taken of the charge/discharge time of the external capacitor to fulfill the external device's reset timing conditions. The minimum recommended capacity is 10 nF.

## **10.3.10 10-bit ADC characteristics**

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol            | Parameter                                                          | Conditions                                                         | Min                 | Тур  | Max                | Unit               |  |

|-------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|------|--------------------|--------------------|--|

| f                 |                                                                    | V <sub>DDA</sub> = 3 to 5.5 V                                      | 1                   |      | 4                  | MHz                |  |

| f <sub>ADC</sub>  | ADC clock frequency                                                | V <sub>DDA</sub> = 4.5 to 5.5 V                                    | 1                   |      | 6                  | IVIFIZ             |  |

| V <sub>DDA</sub>  | Analog supply                                                      |                                                                    | 3                   |      | 5.5                | V                  |  |

| V <sub>REF+</sub> | Positive reference voltage                                         |                                                                    | 2.75 <sup>(1)</sup> |      | V <sub>DDA</sub>   | V                  |  |

| V <sub>REF-</sub> | Negative reference voltage                                         |                                                                    | V <sub>SSA</sub>    |      | 0.5 <sup>(1)</sup> | V                  |  |

|                   |                                                                    |                                                                    | $V_{SSA}$           |      | V <sub>DDA</sub>   | V                  |  |

| V <sub>AIN</sub>  | Conversion voltage range <sup>(2)</sup>                            | Devices with external<br>V <sub>REF+</sub> /V <sub>REF-</sub> pins | V <sub>REF-</sub>   |      | V <sub>REF+</sub>  | V                  |  |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                 |                                                                    |                     | 3    |                    | pF                 |  |

| ts <sup>(2)</sup> | Sampling time                                                      | f <sub>ADC</sub> = 4 MHz                                           |                     | 0.75 |                    |                    |  |

| LS.               |                                                                    | f <sub>ADC</sub> = 6 MHz                                           |                     | 0.5  |                    | μs                 |  |

| t <sub>STAB</sub> | Wakeup time from standby                                           |                                                                    |                     | 7    |                    | μs                 |  |

|                   |                                                                    | $f_{ADC} = 4 MHz$                                                  |                     | 3.5  |                    | μs                 |  |

| t <sub>CONV</sub> | Total conversion time (including sampling time, 10-bit resolution) | f <sub>ADC</sub> = 6 MHz                                           |                     | 2.33 |                    | μs                 |  |

|                   |                                                                    |                                                                    |                     | 14   |                    | 1/f <sub>ADC</sub> |  |

| Table 44. | ADC | characteristics |

|-----------|-----|-----------------|

|-----------|-----|-----------------|

1. Data guaranteed by design, not tested in production.

2. During the sample time the input capacitance  $C_{AIN}$  (3 pF max) can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>S</sub> depend on programming.

| Symbol         | Parameter                                   | Conditions                | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|---------------------------|-----|--------------------|------|

|                |                                             | $f_{ADC} = 2 MHz$         | 1   | 2.5                |      |

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | f <sub>ADC</sub> = 4 MHz  | 1.4 | 3                  |      |

| -              |                                             | f <sub>ADC</sub> = 6 MHz  | 1.6 | 3.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.6 | 2                  |      |

| E <sub>O</sub> | Offset error <sup>(2)</sup>                 | f <sub>ADC</sub> = 4 MHz  | 1.1 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 1.2 | 2.5                |      |

| E <sub>G</sub> | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz  | 0.2 | 2                  |      |

|                |                                             | f <sub>ADC</sub> = 4 MHz  | 0.6 | 2.5                | LSB  |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.8 | 2.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.7 | 1.5                |      |

| E <sub>D</sub> | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 4 MHz  | 0.7 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.8 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 2 MHz  | 0.6 | 1.5                |      |

| E <sub>L</sub> | Integral linearity error (2)                | $f_{ADC} = 4 \text{ MHz}$ | 0.6 | 1.5                |      |

|                |                                             | f <sub>ADC</sub> = 6 MHz  | 0.6 | 1.5                |      |

| Table 45. ADC accuracy | y with R <sub>AIN</sub> < 10 | ) $\mathbf{k}\Omega$ , $\mathbf{V}_{\mathbf{DDA}} = 5 \mathbf{V}$ |

|------------------------|------------------------------|-------------------------------------------------------------------|

|------------------------|------------------------------|-------------------------------------------------------------------|

1. Data based on characterization results for LQFP80 device with  $V_{REF+}/V_{REF-}$ , not tested in production.

ADC accuracy vs. negative injection current: Injecting negative current on any of the analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 10.3.6 does not affect the ADC accuracy.

| Symbol         | Parameter                                   | Conditions                | Тур | Max <sup>(1)</sup> | Unit |

|----------------|---------------------------------------------|---------------------------|-----|--------------------|------|

| E <sub>T</sub> | Total unadjusted error <sup>(2)</sup>       | $f_{ADC} = 2 MHz$         | 1.1 | 2                  |      |

| I⊢ŢI           |                                             | f <sub>ADC</sub> = 4 MHz  | 1.6 | 2.5                |      |

| IEal           | Offset error <sup>(2)</sup>                 | $f_{ADC} = 2 MHz$         | 0.7 | 1.5                |      |

| E <sub>O</sub> |                                             | f <sub>ADC</sub> = 4 MHz  | 1.3 | 2                  |      |

| IE . I         | Gain error <sup>(2)</sup>                   | f <sub>ADC</sub> = 2 MHz  | 0.2 | 1.5                | LSB  |

| E <sub>G</sub> | Gainenoi                                    | $f_{ADC} = 4 \text{ MHz}$ | 0.5 | 2                  | LSD  |

|                | Differential linearity error <sup>(2)</sup> | f <sub>ADC</sub> = 2 MHz  | 0.7 | 1                  |      |

| E <sub>D</sub> |                                             | f <sub>ADC</sub> = 4 MHz  | 0.7 | 1                  |      |

| E <sub>L</sub> | Integral linearity error <sup>(2)</sup>     | $f_{ADC} = 2 MHz$         | 0.6 | 1.5                |      |

| וברו           |                                             | f <sub>ADC</sub> = 4 MHz  | 0.6 | 1.5                |      |

| Table 46. ADC accuracy | with $R_{AIN}$ < 10 k $\Omega$ | $R_{AIN}, V_{DDA} = 3.3 V$ |

|------------------------|--------------------------------|----------------------------|

#### **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

| Symbol Par |                  |                                         | Conditions        |                 |                                     |                   |      |

|------------|------------------|-----------------------------------------|-------------------|-----------------|-------------------------------------|-------------------|------|

|            | Parameter        |                                         | Monitored         | Max             | k f <sub>HSE</sub> /f <sub>CP</sub> | יט <sup>(1)</sup> | Unit |

|            |                  | General conditions                      | frequency band    | 8 MHz/<br>8 MHz | 8 MHz/<br>16 MHz                    | 8 MHz/<br>24 MHz  |      |

|            |                  | 0.1MHz to 30 MHz                        | 15                | 20              | 24                                  |                   |      |

|            | Peak level       | $V_{DD} = 5 V$<br>$T_A = 25 °C$         | 30 MHz to 130 MHz | 18              | 21                                  | 16                | dBµV |

|            |                  | LQFP80 package<br>conforming to SAE IEC | 130 MHz to 1 GHz  | -1              | 1                                   | 4                 |      |

|            | SAE EMI<br>level | 61967-2                                 | SAE EMI level     | 2               | 2.5                                 | 2.5               |      |

1. Data based on characterization results, not tested in production.

#### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114  | А     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | V    |

Table 49. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

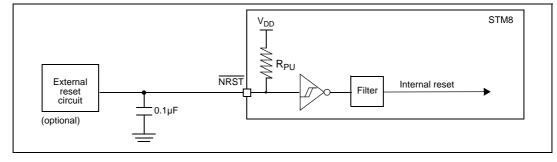

# 11.1.2 LQFP64 package information

#### Figure 46. LQFP64 - 64-pin 14 mm x 14 mm low-profile quad flat package outline

Table 52. LQFP64 - 64-pin, 14 x 14 mm low-profile quad flat package mechanicaldata

| Symbol | mm     |        |        | inches <sup>(1)</sup> |        |        |

|--------|--------|--------|--------|-----------------------|--------|--------|

|        | Min    | Тур    | Max    | Min                   | Тур    | Max    |

| А      |        |        | 1.600  |                       |        | 0.0630 |

| A1     | 0.050  |        | 0.150  | 0.0020                |        | 0.0059 |

| A2     | 1.350  | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.300  | 0.370  | 0.450  | 0.0118                | 0.0146 | 0.0177 |

| С      | 0.090  |        | 0.200  | 0.0035                |        | 0.0079 |

| D      | 15.800 | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800 | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| D3     |        | 12.000 |        |                       | 0.4724 |        |

| E      | 15.800 | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| E1     | 13.800 | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     |        | 12.000 |        |                       | 0.4724 |        |

| е      |        | 0.800  |        |                       | 0.0315 |        |

| L      | 0.450  | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     |        | 1.000  |        |                       | 0.0394 |        |

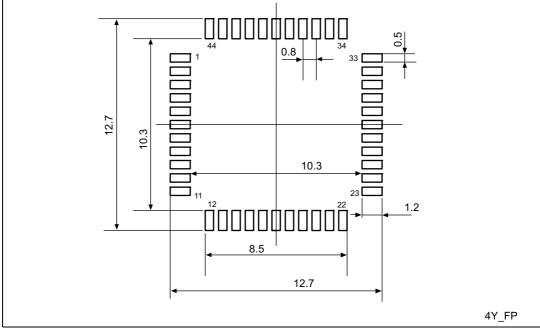

Figure 54. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

#### **Device marking**

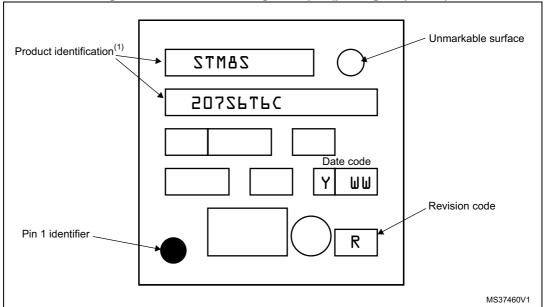

The following figure shows the marking for the LQFP44 package.

Figure 55. LQFP44 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID14733 Rev 13

# 14 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 23-May-2008 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 05-Jun-2008 | 2        | Added part numbers on page 1 and in <i>Table 2 on page 11</i> .<br>Updated <i>Section 4: Product overview</i> .<br>Updated <i>Section 10: Electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 22-Jun-2008 | 3        | Added part numbers on page 1 and in Table 2 on page 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 12-Aug-2008 | 4        | Added 32 pin device pinout and ordering information.<br>Updated UBC option description in <i>Table 13 on page 48</i> .<br>USART renamed UART1, LINUART renamed UART3.<br>Max. ADC frequency increased to 6 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 20-Oct-2008 | 5        | <ul> <li>Removed STM8S207K4 part number.</li> <li>Removed LQFP64 14 x 14 mm package.</li> <li>Added medium and high density Flash memory categories.</li> <li>Added Section 6: Memory and register map on page 34.</li> <li>Replaced beCAN3 by beCAN in Section 4.14.5: beCAN.</li> <li>Updated Section 10: Electrical characteristics on page 52.</li> <li>Updated LQFP44 (Figure 53 and Table 55), and LQFP32 outline and mechanical data (Figure 56, and Table 56).</li> </ul>                                                                                                                                                                                                                                                                                              |  |

| 08-Dec-2008 | 6        | Changed V <sub>DD</sub> minimum value from 3.0 to 2.95 V.<br>Updated number of High Sink I/Os in pinout.<br>Removed FLASH _NFPR and FLASH _FPR registers in <i>Table 9:</i><br><i>General hardware register map</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 30-Jan-2009 | 7        | Removed preliminary status.<br>Removed VQFN32 package.<br>Added STM8S207C6, STM8S207S6.<br>Updated external interrupts in <i>Table 2 on page 11</i> .<br>Updated <i>Section 10: Electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 10-Jul-2009 | 8        | <ul> <li>Document status changed from "preliminary data" to "datasheet".</li> <li>Added LQFP64 14 x 14 mm package.</li> <li>Added STM8S207M8, STM8S207SB, STM8S208R8, STM8S208R6</li> <li>STM8S208C8, and STM8S208C6, STM8S208SB, STM8S208S8, and STM8S208S6.</li> <li>Replaced "CAN" with "beCAN".</li> <li>Added <i>Table 3</i> to <i>Section 4.5: Clock controller</i>.</li> <li>Updated <i>Section 4.8: Auto wakeup counter</i>.</li> <li>Added beCAN peripheral (impacting <i>Table 1</i> and <i>Figure 6</i>).</li> <li>Added footnote about CAN_RX/TX to pinout figures <i>5</i>, <i>4</i>, and <i>6</i>.</li> <li><i>Table 6</i>: Removed 'X' from wpu column of I<sup>2</sup>C pins (no wpu available).</li> <li>Added <i>Table 11: Interrupt mapping</i>.</li> </ul> |  |

| Table 58. Document rev | ision history |

|------------------------|---------------|

|------------------------|---------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Feb-2015 | 13       | <ul> <li>Updated:</li> <li>Figure 43: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline</li> <li>Table 51: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data</li> <li>Figure 51: LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package mechanical data</li> <li>Figure 51: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline</li> <li>Table 53: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline</li> <li>Table 53: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Table 54: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Table 56: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Table 56: LQFP48 - 32-pin, 7 x 7 mm low-profile quad flat package outline</li> <li>Figure 56: LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data</li> <li>Added:</li> <li>Figure 44: LQFP80 recommended footprint</li> <li>Figure 45: LQFP48 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 48: LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 51: LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint</li> <li>Figure 51: LQFP48 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 52: LQFP48 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 52: LQFP48 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 52: LQFP48 marking example (package top view)</li> <li>Figure 53: LQFP44 marking example (package top view)</li> <li>Figure 54: LQFP44 - 34-pin, 10 x 10 mm low-profile quad flat recommended footprint</li> <li>Figure 55: LQFP48 marking example (package top view)</li> <li>Figure 55: LQFP44 marking example (package top view)</li> <li>Figure 55:</li></ul> |

Table 58. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14733 Rev 13