#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 9x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s207sbt6c |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure

The IWDG time base spans from 60  $\mu$ s to 1 s.

## 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM3 input capture channel 1 for calibration

## 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

# 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

## 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

## 4.14.4 I<sup>2</sup>C

- I<sup>2</sup>C master features:

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features:

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds:

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

### 4.14.5 beCAN

The beCAN controller (basic enhanced CAN), interfaces the CAN network and supports the CAN protocol version 2.0A and B. It has been designed to manage a high number of incoming messages efficiently with a minimum CPU load.

For safety-critical applications the beCAN controller provides all hardware functions to support the CAN time triggered communication option (TTCAN).

The maximum transmission speed is 1 Mbit.

### Transmission

- Three transmit mailboxes

- Configurable transmit priority by identifier or order request

- Time stamp on SOF transmission

### Reception

- 8-, 11- and 29-bit ID

- One receive FIFO (3 messages deep)

- Software-efficient mailbox mapping at a unique address space

- FMI (filter match index) stored with message

- Configurable FIFO overrun

- Time stamp on SOF reception

- Six filter banks, 2 x 32 bytes (scalable to 4 x 16-bit) each, enabling various masking configurations, such as 12 filters for 29-bit ID or 48 filters for 11-bit ID

- Filtering modes:

- Mask mode permitting ID range filtering

- ID list mode

- Time triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Configurable timer resolution

- Time stamp sent in last two data bytes

| Туре             | I= Input, O                | Input, O = Output, S = Power supply                                                                                                                                            |  |  |  |  |  |  |

|------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Level            | Input                      | CM = CMOS                                                                                                                                                                      |  |  |  |  |  |  |

|                  | Output                     | HS = High sink                                                                                                                                                                 |  |  |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s | up to 2 MHz)<br>up to 10 MHz)<br>low programmability with slow as default state after reset<br>low programmability with fast as default state after reset                      |  |  |  |  |  |  |

| Port and control | Input                      | float = floating, wpu = weak pull-up                                                                                                                                           |  |  |  |  |  |  |

| configuration    | Output                     | T = True open drain, OD = Open drain, PP = Push pull                                                                                                                           |  |  |  |  |  |  |

| Reset state      | Unless othe                | d $\underline{X}$ (pin state after internal reset release)<br>less otherwise specified, the pin state is the same during the reset phase and<br>er the internal reset release. |  |  |  |  |  |  |

| Table 5. Legend/abbreviations | for pinout table |

|-------------------------------|------------------|

|-------------------------------|------------------|

|        | Pin    | num    | ber    |        |                     |      |          | Inpu     | t              |           | Out   | put |   |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------|------|----------|----------|----------------|-----------|-------|-----|---|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name            | Type | floating | ndw      | Ext. interrupt | High sink | Speed | QO  | Ы | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | 1      | 1      | 1      | NRST                | I/O  |          | <u>X</u> |                |           |       |     |   | Reset                          |                                  |                                                      |

| 2      | 2      | 2      | 2      | 2      | PA1/OSCIN           | I/O  | <u>x</u> | х        |                |           | 01    | х   | х | Port A1                        | Resonator/<br>crystal in         |                                                      |

| 3      | 3      | 3      | 3      | 3      | PA2/OSCOUT          | I/O  | X        | х        | х              |           | 01    | х   | х | Port A2                        | Resonator/<br>crystal out        |                                                      |

| 4      | 4      | 4      | 4      | -      | V <sub>SSIO_1</sub> | S    |          |          |                |           |       |     |   | I/O groun                      | d                                |                                                      |

| 5      | 5      | 5      | 5      | 4      | V <sub>SS</sub>     | S    |          |          |                |           |       |     |   | Digital gro                    | ound                             |                                                      |

| 6      | 6      | 6      | 6      | 5      | VCAP                | S    |          |          |                |           |       |     |   | 1.8 V reg                      | ulator capacitor                 |                                                      |

| 7      | 7      | 7      | 7      | 6      | V <sub>DD</sub>     | S    |          |          |                |           |       |     |   | Digital po                     | wer supply                       |                                                      |

| 8      | 8      | 8      | 8      | 7      | V <sub>DDIO_1</sub> | S    |          |          |                |           |       |     |   | I/O powe                       | r supply                         |                                                      |

| 9      | 9      | 9      | -      | -      | PA3/TIM2_CH3        | I/O  | <u>x</u> | х        | Х              |           | 01    | х   | х | Port A3                        | Timer 2 -<br>channel3            | TIM3_CH1<br>[AFR1]                                   |

| 10     | 10     | 10     | 9      | -      | PA4/UART1_RX        | I/O  | X        | х        | Х              | HS        | O3    | х   | Х | Port A4                        | UART1<br>receive                 |                                                      |

| 11     | 11     | 11     | 10     | -      | PA5/UART1_TX        | I/O  | <u>x</u> | х        | Х              | HS        | О3    | Х   | Х | Port A5                        | UART1<br>transmit                |                                                      |

### Table 6. Pin description

|        | Pin    | num    | nber   |        |                                 |      |          | Inpu     | t              |           | Out   | put              |    | -                              |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------------------|------|----------|----------|----------------|-----------|-------|------------------|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name                        | Type | floating | ndw      | Ext. interrupt | High sink | Speed | OD               | ΡР | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 69     | 55     | 39     | 35     | -      | PE1/I <sup>2</sup> C_SCL        | I/O  | <u>X</u> |          | Х              |           | 01    | T <sup>(3)</sup> |    | Port E1                        | I <sup>2</sup> C clock           |                                                      |

| 70     | 56     | 40     | 36     | -      | PE0/CLK_CCO                     | I/O  | X        | Х        | Х              | HS        | O3    | х                | Х  | Port E0                        | Configurable<br>clock output     |                                                      |

| 71     | -      | -      | -      | -      | PI6                             | I/O  | <u>X</u> | Х        |                |           | 01    | Х                | Х  | Port I6                        |                                  |                                                      |

| 72     | -      | -      | -      | -      | PI7                             | I/O  | <u>X</u> | Х        |                |           | 01    | Х                | Х  | Port I7                        |                                  |                                                      |

| 73     | 57     | 41     | 37     | 25     | PD0/TIM3_CH2                    | I/O  | <u>x</u> | х        | х              | HS        | O3    | х                | х  | Port D0                        | Timer 3 -<br>channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 74     | 58     | 42     | 38     | 26     | PD1/SWIM <sup>(4)</sup>         | I/O  | х        | <u>x</u> | Х              | HS        | 04    | х                | х  | Port D1                        | SWIM data<br>interface           |                                                      |

| 75     | 59     | 43     | 39     | 27     | PD2/TIM3_CH1                    | I/O  | <u>x</u> | х        | Х              | HS        | O3    | х                | х  | Port D2                        | Timer 3 -<br>channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 76     | 60     | 44     | 40     | 28     | PD3/TIM2_CH2                    | I/O  | <u>x</u> | х        | Х              | HS        | O3    | х                | х  | Port D3                        | Timer 2 -<br>channel 2           | ADC_ETR<br>[AFR0]                                    |

| 77     | 61     | 45     | 41     | 29     | PD4/TIM2_CH1/B<br>EEP           | I/O  | X        | х        | Х              | HS        | O3    | х                | х  | Port D4                        | Timer 2 -<br>channel 1           | BEEP output<br>[AFR7]                                |

| 78     | 62     | 46     | 42     | 30     | PD5/ UART3_TX                   | I/O  | X        | х        | Х              |           | 01    | х                | х  | Port D5                        | UART3 data<br>transmit           |                                                      |

| 79     | 63     | 47     | 43     | 31     | PD6/<br>UART3_RX <sup>(1)</sup> | I/O  | X        | х        | Х              |           | 01    | х                | х  | Port D6                        | UART3 data<br>receive            |                                                      |

| 80     | 64     | 48     | 44     | 32     | PD7/TLI                         | I/O  | X        | Х        | Х              |           | 01    | х                | х  | Port D7                        | Top level<br>interrupt           | TIM1_CH4<br>[AFR4] <sup>(5)</sup>                    |

| Table | 6.  | Pin | descri | ption ( | (continued) |  |

|-------|-----|-----|--------|---------|-------------|--|

| IUNIO | ••• |     | 400011 |         | (oonanaoa)  |  |

1. The default state of UART1\_RX and UART3\_RX pins is controlled by the ROM bootloader. These pins are pulled up as part of the bootloader activation process and returned to the floating state before a return from the bootloader.

2. The beCAN interface is available on STM8S208xx devices only

3. In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to V<sub>DD</sub> are not implemented).

4. The PD1 pin is in input pull-up during the reset phase and after the internal reset release.

5. Available in 44-pin package only. On other packages, the AFR4 bit is reserved and must be kept at 0.

# 5.2 Alternate function remapping

As shown in the rightmost column of the pin description table, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function

|                           | Table 9  | . General hardwar | e register map (continued)                 |                     |

|---------------------------|----------|-------------------|--------------------------------------------|---------------------|

| Address                   | Block    | Register label    | Register name                              | Reset<br>status     |

| 0x00 50CC                 |          | CLK_HSITRIMR      | HSI clock calibration trimming register    | 0x00                |

| 0x00 50CD                 | CLK      | CLK_SWIMCCR       | SWIM clock control register                | 0bXXXX<br>XXX0      |

| 0x00 50CE to<br>0x00 50D0 |          |                   | Reserved area (3 bytes)                    |                     |

| 0x00 50D1                 | WWDG     | WWDG_CR           | WWDG control register                      | 0x7F                |

| 0x00 50D2                 | - www.DG | WWDG_WR           | WWDR window register                       | 0x7F                |

| 0x00 50D3 to<br>0x00 50DF |          |                   | Reserved area (13 bytes)                   |                     |

| 0x00 50E0                 |          | IWDG_KR           | IWDG key register                          | 0xXX <sup>(2)</sup> |

| 0x00 50E1                 | IWDG     | IWDG_PR           | IWDG prescaler register                    | 0x00                |

| 0x00 50E2                 |          | IWDG_RLR          | IWDG reload register                       | 0xFF                |

| 0x00 50E3 to<br>0x00 50EF |          |                   | Reserved area (13 bytes)                   |                     |

| 0x00 50F0                 |          | AWU_CSR1          | AWU control/status register 1              | 0x00                |

| 0x00 50F1                 | AWU      | AWU_APR           | AWU asynchronous prescaler buffer register | 0x3F                |

| 0x00 50F2                 |          | AWU_TBR           | AWU timebase selection register            | 0x00                |

| 0x00 50F3                 | BEEP     | BEEP_CSR          | BEEP control/status register               | 0x1F                |

| 0x00 50F4 to<br>0x00 50FF |          |                   | Reserved area (12 bytes)                   |                     |

| 0x00 5200                 |          | SPI_CR1           | SPI control register 1                     | 0x00                |

| 0x00 5201                 |          | SPI_CR2           | SPI control register 2                     | 0x00                |

| 0x00 5202                 |          | SPI_ICR           | SPI interrupt control register             | 0x00                |

| 0x00 5203                 | SPI      | SPI_SR            | SPI status register                        | 0x02                |

| 0x00 5204                 | 551      | SPI_DR            | SPI data register                          | 0x00                |

| 0x00 5205                 |          | SPI_CRCPR         | SPI CRC polynomial register                | 0x07                |

| 0x00 5206                 |          | SPI_RXCRCR        | SPI Rx CRC register                        | 0xFF                |

| 0x00 5207                 |          | SPI_TXCRCR        | SPI Tx CRC register                        | 0xFF                |

| 0x00 5208 to<br>0x00 520F |          |                   | Reserved area (8 bytes)                    |                     |

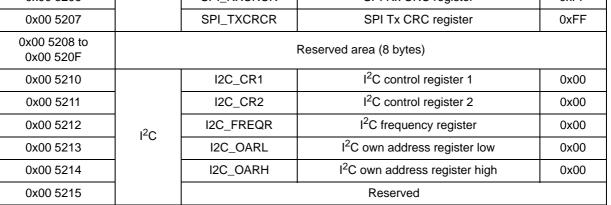

| 0x00 5210                 |          | I2C_CR1           | I <sup>2</sup> C control register 1        | 0x00                |

| 0x00 5211                 |          | 12C CR2           | I <sup>2</sup> C control register 2        | 0x00                |

| Table 9. General hardware register map (continued) |       |                |                                           |                 |  |  |  |  |  |  |  |

|----------------------------------------------------|-------|----------------|-------------------------------------------|-----------------|--|--|--|--|--|--|--|

| Address                                            | Block | Register label | Register name                             | Reset<br>status |  |  |  |  |  |  |  |

| 0x00 532B                                          |       | TIM3_ARRH      | TIM3 auto-reload register high            | 0xFF            |  |  |  |  |  |  |  |

| 0x00 532C                                          |       | TIM3_ARRL      | TIM3 auto-reload register low             | 0xFF            |  |  |  |  |  |  |  |

| 0x00 532D                                          | ТІМЗ  | TIM3_CCR1H     | TIM3 capture/compare register 1 high      | 0x00            |  |  |  |  |  |  |  |

| 0x00 532E                                          | TIMS  | TIM3_CCR1L     | TIM3 capture/compare register 1 low       | 0x00            |  |  |  |  |  |  |  |

| 0x00 532F                                          |       | TIM3_CCR2H     | TIM3 capture/compare register 2 high      | 0x00            |  |  |  |  |  |  |  |

| 0x00 5330                                          |       | TIM3_CCR2L     | TIM3 capture/compare register 2 low       | 0x00            |  |  |  |  |  |  |  |

| 0x00 5331 to<br>0x00 533F                          |       |                | Reserved area (15 bytes)                  |                 |  |  |  |  |  |  |  |

| 0x00 5340                                          |       | TIM4_CR1       | TIM4 control register 1                   | 0x00            |  |  |  |  |  |  |  |

| 0x00 5341                                          |       | TIM4_IER       | TIM4 interrupt enable register            | 0x00            |  |  |  |  |  |  |  |

| 0x00 5342                                          |       | TIM4_SR        | TIM4 status register                      | 0x00            |  |  |  |  |  |  |  |

| 0x00 5343                                          | TIM4  | TIM4_EGR       | TIM4 event generation register            | 0x00            |  |  |  |  |  |  |  |

| 0x00 5344                                          | _     | TIM4_CNTR      | TIM4 counter                              | 0x00            |  |  |  |  |  |  |  |

| 0x00 5345                                          | _     | TIM4_PSCR      | TIM4 prescaler register                   | 0x00            |  |  |  |  |  |  |  |

| 0x00 5346                                          |       | TIM4_ARR       | TIM4 auto-reload register                 | 0xFF            |  |  |  |  |  |  |  |

| 0x00 5347 to<br>0x00 53FF                          |       | F              | Reserved area (185 bytes)                 |                 |  |  |  |  |  |  |  |

| 0x00 5400                                          |       | ADC _CSR       | ADC control/status register               | 0x00            |  |  |  |  |  |  |  |

| 0x00 5401                                          |       | ADC_CR1        | ADC configuration register 1              | 0x00            |  |  |  |  |  |  |  |

| 0x00 5402                                          |       | ADC_CR2        | ADC configuration register 2              | 0x00            |  |  |  |  |  |  |  |

| 0x00 5403                                          | ADC2  | ADC_CR3        | ADC configuration register 3              | 0x00            |  |  |  |  |  |  |  |

| 0x00 5404                                          | ADC2  | ADC_DRH        | ADC data register high                    | 0xXX            |  |  |  |  |  |  |  |

| 0x00 5405                                          |       | ADC_DRL        | ADC data register low                     | 0xXX            |  |  |  |  |  |  |  |

| 0x00 5406                                          |       | ADC_TDRH       | ADC Schmitt trigger disable register high | 0x00            |  |  |  |  |  |  |  |

| 0x00 5407                                          |       | ADC_TDRL       | ADC Schmitt trigger disable register low  | 0x00            |  |  |  |  |  |  |  |

| 0x00 5408 to<br>0x00 541F                          |       |                | Reserved area (24 bytes)                  |                 |  |  |  |  |  |  |  |

| 0x00 5420                                          |       | CAN_MCR        | CAN master control register               | 0x02            |  |  |  |  |  |  |  |

| 0x00 5421                                          | 1     | CAN_MSR        | CAN master status register                | 0x02            |  |  |  |  |  |  |  |

| 0x00 5422                                          | 7     | CAN_TSR        | CAN transmit status register              | 0x00            |  |  |  |  |  |  |  |

| 0x00 5423                                          | baCAN | CAN_TPR        | CAN transmit priority register            | 0x0C            |  |  |  |  |  |  |  |

| 0x00 5424                                          | beCAN | CAN_RFR        | CAN receive FIFO register                 | 0x00            |  |  |  |  |  |  |  |

| 0x00 5425                                          |       | CAN_IER        | CAN interrupt enable register             | 0x00            |  |  |  |  |  |  |  |

| 0x00 5426                                          | 7     | CAN_DGR        | CAN diagnosis register                    | 0x0C            |  |  |  |  |  |  |  |

| 0x00 5427                                          | 7     | CAN_FPSR       | CAN page selection register               | 0x00            |  |  |  |  |  |  |  |

| Table O  | <b>0</b> |          |          |       | (           |  |

|----------|----------|----------|----------|-------|-------------|--|

| Table 9. | General  | nardware | register | map ( | (continued) |  |

| Address                   | Block | Register Label                        | Register Name                                   | Reset<br>Status |  |  |  |  |  |  |  |  |

|---------------------------|-------|---------------------------------------|-------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

| 0x00 7F98                 |       | DM_CSR1                               | DM debug module control/status register 1       | 0x10            |  |  |  |  |  |  |  |  |

| 0x00 7F99                 | DM    | DM_CSR2                               | _CSR2 DM debug module control/status register 2 |                 |  |  |  |  |  |  |  |  |

| 0x00 7F9A                 |       | DM_ENFCTR DM enable function register |                                                 | 0xFF            |  |  |  |  |  |  |  |  |

| 0x00 7F9B to<br>0x00 7F9F |       |                                       | Reserved area (5 bytes)                         |                 |  |  |  |  |  |  |  |  |

#### Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

2. Product dependent value, see Figure 8: Memory map.

# 9 Unique ID

The devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content description  | Unique ID bits |             |   |           |           |   |   |   |  |  |  |  |

|---------|----------------------|----------------|-------------|---|-----------|-----------|---|---|---|--|--|--|--|

| Address |                      | 7              | 6           | 5 | 4         | 3         | 2 | 1 | 0 |  |  |  |  |

| 0x48CD  | X co-ordinate on the | U_ID[7:0]      |             |   |           |           |   |   |   |  |  |  |  |

| 0x48CE  | wafer                | U_ID[15:8]     |             |   |           |           |   |   |   |  |  |  |  |

| 0x48CF  | Y co-ordinate on the |                |             |   | U_        | ID[23:16] |   |   |   |  |  |  |  |

| 0x48D0  | wafer                | U_ID[31:24]    |             |   |           |           |   |   |   |  |  |  |  |

| 0x48D1  | Wafer number         | U_ID[39:32]    |             |   |           |           |   |   |   |  |  |  |  |

| 0x48D2  |                      | U_ID[47:40]    |             |   |           |           |   |   |   |  |  |  |  |

| 0x48D3  |                      | U_ID[55:48]    |             |   |           |           |   |   |   |  |  |  |  |

| 0x48D4  |                      | U_ID[63:56]    |             |   |           |           |   |   |   |  |  |  |  |

| 0x48D5  | Lot number           |                |             |   | ID[71:64] |           |   |   |   |  |  |  |  |

| 0x48D6  |                      | U_ID[79:72]    |             |   |           |           |   |   |   |  |  |  |  |

| 0x48D7  |                      |                | U_ID[87:80] |   |           |           |   |   |   |  |  |  |  |

| 0x48D8  |                      | U_ID[95:88]    |             |   |           |           |   |   |   |  |  |  |  |

#### Table 14. Unique ID registers (96 bits)

# 10.3 Operating conditions

The device must be used in operating conditions that respect the parameters in *Table 18*. In addition, full account must be taken of all physical capacitor characteristics and tolerances.

| Symbol                          | Parameter                                              | Conditions                                                                                                                                          | Min                                                                | Max                | Unit |

|---------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------|------|

| f <sub>CPU</sub>                | Internal CPU clock frequency                           | $T_A \le 105 \ ^{\circ}C$                                                                                                                           | 0                                                                  | 24                 | MHz  |

| 'CPU                            | Internal OF O clock frequency                          |                                                                                                                                                     | 0                                                                  | 16                 | MHz  |

| $V_{DD/}V_{DD_{IO}}$            | Standard operating voltage                             |                                                                                                                                                     | 2.95                                                               | 5.5                | V    |

|                                 | C <sub>EXT</sub> : capacitance of external capacitor   |                                                                                                                                                     | 470                                                                | 3300               | nF   |

| V <sub>CAP</sub> <sup>(1)</sup> | ESR of external capacitor                              | at 1 MHz <sup>(2)</sup>                                                                                                                             | -                                                                  | 0.3                | Ω    |

|                                 | ESL of external capacitor                              |                                                                                                                                                     | 0 24 MHz   0 16 MHz   2.95 5.5 V   470 3300 nF   - 0.3 Ω   - 15 nH | nH                 |      |

| Р <sub>D</sub> <sup>(3)</sup>   | Power dissipation at $T_A = 85^{\circ}$ C for suffix 6 | 44, 48, 64, and 80-pin<br>devices, with output on 8<br>standard ports, 2 high sink<br>ports and 2 open drain ports<br>simultaneously <sup>(4)</sup> |                                                                    | 443                | mW   |

|                                 | or $T_A = 125^\circ$ C for suffix 3                    | 32-pin package, with output<br>on 8 standard ports and 2<br>high sink ports<br>simultaneously <sup>(4)</sup>                                        |                                                                    | 360                |      |

| T <sub>A</sub>                  | Ambient temperature for 6 suffix version               | Maximum power dissipation                                                                                                                           | -40                                                                | 85                 |      |

| 'A                              | Ambient temperature for 3 suffix version               | Maximum power dissipation                                                                                                                           | -40                                                                | 125                | °C   |

| ТJ                              | Junction temperature range                             | 6 suffix version                                                                                                                                    | -40                                                                | 105                |      |

| ١J                              | Survey of temperature range                            | 3 suffix version                                                                                                                                    | -40                                                                | 130 <sup>(5)</sup> |      |

|  | Table 18. | General | operating | conditions |

|--|-----------|---------|-----------|------------|

|--|-----------|---------|-----------|------------|

1. Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

2. This frequency of 1 MHz as a condition for  $V_{CAP}$  parameters is given by design of internal regulator.

To calculate P<sub>Dmax</sub>(T<sub>A</sub>), use the formula P<sub>Dmax</sub> = (T<sub>Jmax</sub> - T<sub>A</sub>)/Θ<sub>JA</sub> (see Section 11.2: Thermal characteristics on page 108) with the value for T<sub>Jmax</sub> given in Table 18 above and the value for Θ<sub>JA</sub> given in Table 57: Thermal characteristics.

4. Refer to Section 11.2: Thermal characteristics on page 108 for the calculation method.

5. T<sub>Jmax</sub> is given by the test limit. Above this value the product behavior is not guaranteed.

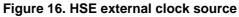

### **10.3.3** External clock sources and timing characteristics

### HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Table 31. HSE us | ser external clock | characteristics |

|------------------|--------------------|-----------------|

|------------------|--------------------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency |                            | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      |                            | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       |                            | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    |     | 1                       | μA   |

1. Data based on characterization results, not tested in production.

### HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

## **10.3.5** Memory characteristics

### **RAM** and hardware registers

| Table | 35. | RAM | and | hardware | registers |

|-------|-----|-----|-----|----------|-----------|

|       |     |     | ~   |          |           |

| Symbol          | Parameter                          | Conditions           | Min                                | Unit |

|-----------------|------------------------------------|----------------------|------------------------------------|------|

| V <sub>RM</sub> | Data retention mode <sup>(1)</sup> | Halt mode (or reset) | V <sub>IT-max</sub> <sup>(2)</sup> | V    |

1. Minimum supply voltage without losing data stored in RAM (in halt mode or under reset) or in hardware registers (only in halt mode). Guaranteed by design, not tested in production.

2. Refer to Table 19 on page 57 for the value of  $V_{IT-max}$ .

### Flash program memory/data EEPROM memory

General conditions:  $T_A = -40$  to 125 °C.

| Symbol             | Parameter                                                                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max | Unit   |

|--------------------|--------------------------------------------------------------------------------------------------|------------------------------|--------------------|-----|-----|--------|

| V <sub>DD</sub>    | Operating voltage<br>(all modes, execution/write/erase)                                          | $f_{CPU} \le 24 \text{ MHz}$ | 2.95               |     | 5.5 | V      |

| t <sub>prog</sub>  | Standard programming time (including<br>erase) for byte/word/block<br>(1 byte/4 bytes/128 bytes) |                              |                    | 6   | 6.6 | ms     |

|                    | Fast programming time for 1 block (128 bytes)                                                    |                              |                    | 3   | 3.3 | ms     |

| t <sub>erase</sub> | Erase time for 1 block (128 bytes)                                                               |                              |                    | 3   | 3.3 | ms     |

| N <sub>RW</sub>    | Erase/write cycles <sup>(2)</sup><br>(program memory)                                            | T <sub>A</sub> = 85 °C       | 10 k               |     |     | cycles |

|                    | Erase/write cycles (data memory) <sup>(2)</sup>                                                  | $T_A = 125 \ ^\circ C$       | 300 k              | 1M  |     |        |

|                    | Data retention (program memory)<br>after 10 k erase/write cycles at<br>$T_A = 85 \text{ °C}$     | T <sub>RET</sub> = 55° C     | 20                 |     |     |        |

| t <sub>RET</sub>   | Data retention (data memory) after 10 k erase/write cycles at $T_A = 85$ °C                      | T <sub>RET</sub> = 55° C     | 20                 |     |     | years  |

|                    | Data retention (data memory) after 300k erase/write cycles at $T_A = 125$ °C                     | T <sub>RET</sub> = 85° C     | 1                  |     |     |        |

| I <sub>DD</sub>    | Supply current (Flash programming or erasing for 1 to 128 bytes)                                 |                              |                    | 2   |     | mA     |

1. Data based on characterization results, not tested in production.

2. The physical granularity of the memory is 4 bytes, so cycling is performed on 4 bytes even when a write/erase operation addresses a single byte.

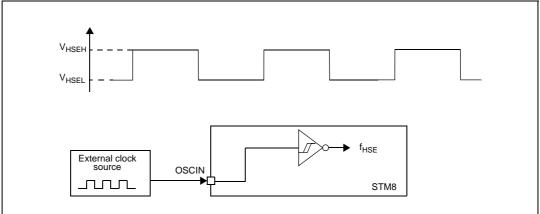

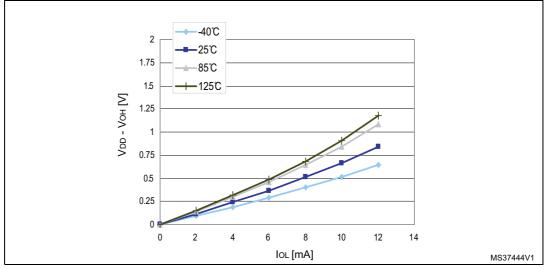

Figure 31. Typ.  $V_{DD}$  -  $V_{OH}$  @  $V_{DD}$  = 5 V (high sink ports)

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

# 10.3.9 I<sup>2</sup>C interface characteristics

| Symbol                                     | Descustor                               | Standard           | mode I <sup>2</sup> C | Fast mode I <sup>2</sup> C <sup>(1)</sup> |                    |      |

|--------------------------------------------|-----------------------------------------|--------------------|-----------------------|-------------------------------------------|--------------------|------|

|                                            | Parameter                               | Min <sup>(2)</sup> | Max <sup>(2)</sup>    | Min <sup>(2)</sup>                        | Max <sup>(2)</sup> | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7                |                       | 1.3                                       |                    |      |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0                |                       | 0.6                                       |                    | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250                |                       | 100                                       |                    |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup>   |                       | 0 <sup>(4)</sup>                          | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                    | 1000                  |                                           | 300                | ns   |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                    | 300                   |                                           | 300                |      |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0                |                       | 0.6                                       |                    |      |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7                |                       | 0.6                                       |                    | μs   |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0                |                       | 0.6                                       |                    | μs   |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7                |                       | 1.3                                       |                    | μs   |

| Cb                                         | Capacitive load for each bus line       |                    | 400                   |                                           | 400                | pF   |

Table 43. I<sup>2</sup>C characteristics

1.  $f_{MASTER},$  must be at least 8 MHz to achieve max fast I^2C speed (400kHz)  $\,$

2. Data based on standard I<sup>2</sup>C protocol requirement, not tested in production

3. The maximum hold time of the start condition has only to be met if the interface does not stretch the low time

4. The device must internally provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL

## **10.3.10 10-bit ADC characteristics**

Subject to general operating conditions for  $V_{\text{DDA}},\,f_{\text{MASTER}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol            | Parameter                                                             | Conditions                                                         | Min                 | Тур  | Max                | Unit               |

|-------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|------|--------------------|--------------------|

| f                 |                                                                       | V <sub>DDA</sub> = 3 to 5.5 V                                      | 1                   |      | 4                  | N411-              |

| f <sub>ADC</sub>  | ADC clock frequency                                                   | V <sub>DDA</sub> = 4.5 to 5.5 V                                    | 1                   |      | 6                  | MHz                |

| V <sub>DDA</sub>  | Analog supply                                                         |                                                                    | 3                   |      | 5.5                | V                  |

| V <sub>REF+</sub> | Positive reference voltage                                            |                                                                    | 2.75 <sup>(1)</sup> |      | V <sub>DDA</sub>   | V                  |

| V <sub>REF-</sub> | Negative reference voltage                                            |                                                                    | V <sub>SSA</sub>    |      | 0.5 <sup>(1)</sup> | V                  |

|                   |                                                                       |                                                                    | $V_{SSA}$           |      | V <sub>DDA</sub>   | V                  |

| V <sub>AIN</sub>  | Conversion voltage range <sup>(2)</sup>                               | Devices with external<br>V <sub>REF+</sub> /V <sub>REF-</sub> pins | V <sub>REF-</sub>   |      | V <sub>REF+</sub>  | V                  |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                    |                                                                    |                     | 3    |                    | pF                 |

| ts <sup>(2)</sup> | Sampling time                                                         | f <sub>ADC</sub> = 4 MHz                                           |                     | 0.75 |                    |                    |

| LS V              |                                                                       | f <sub>ADC</sub> = 6 MHz                                           |                     | 0.5  |                    | μs                 |

| t <sub>STAB</sub> | Wakeup time from standby                                              |                                                                    |                     | 7    |                    | μs                 |

|                   |                                                                       | $f_{ADC} = 4 MHz$                                                  |                     | 3.5  |                    | μs                 |

| t <sub>CONV</sub> | Total conversion time (including<br>sampling time, 10-bit resolution) | f <sub>ADC</sub> = 6 MHz                                           |                     | 2.33 |                    | μs                 |

|                   |                                                                       |                                                                    |                     | 14   |                    | 1/f <sub>ADC</sub> |

| Table 44. | ADC | characteristics |

|-----------|-----|-----------------|

|-----------|-----|-----------------|

1. Data guaranteed by design, not tested in production.

2. During the sample time the input capacitance  $C_{AIN}$  (3 pF max) can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within t<sub>S</sub>. After the end of the sample time t<sub>S</sub>, changes of the analog input voltage have no effect on the conversion result. Values for the sample clock t<sub>S</sub> depend on programming.

### 10.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- **ESD**: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                        | Conditions                                                                                                    | Level/class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD} = 5 V$ , $T_A = 25 °C$ ,<br>$f_{MASTER} = 16 MHz$ ,<br>conforming to IEC 61000-4-2                    | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 5 \text{ V}, T_A = 25 \text{ °C},$<br>$f_{MASTER} = 16 \text{ MHz},$<br>conforming to IEC 61000-4-4 | 4A          |

| Table | 47.          | EMS | data |

|-------|--------------|-----|------|

| Table | <b>T</b> / . |     | uuu  |

### **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

| Symbol           | Parameter        | Conditions                                                                 |                   |                                                       |                  |                  |      |  |

|------------------|------------------|----------------------------------------------------------------------------|-------------------|-------------------------------------------------------|------------------|------------------|------|--|

|                  |                  | General conditions                                                         | Monitored         | Max f <sub>HSE</sub> /f <sub>CPU</sub> <sup>(1)</sup> |                  |                  | Unit |  |

|                  |                  |                                                                            | frequency band    | 8 MHz/<br>8 MHz                                       | 8 MHz/<br>16 MHz | 8 MHz/<br>24 MHz |      |  |

| S <sub>EMI</sub> | Peak level       | $V_{DD} = 5 V$<br>$T_A = 25 °C$<br>LQFP80 package<br>conforming to SAE IEC | 0.1MHz to 30 MHz  | 15                                                    | 20               | 24               |      |  |

|                  |                  |                                                                            | 30 MHz to 130 MHz | 18                                                    | 21               | 16               | dBµV |  |

|                  |                  |                                                                            | 130 MHz to 1 GHz  | -1                                                    | 1                | 4                |      |  |

|                  | SAE EMI<br>level | 61967-2                                                                    | SAE EMI level     | 2                                                     | 2.5              | 2.5              |      |  |

1. Data based on characterization results, not tested in production.

### Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114  | А     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | V    |

Table 49. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

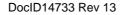

# 11 Package characteristics

To meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at *www.st.com*. ECOPACK® is an ST trademark.

# 11.1 Package information

## 11.1.1 LQFP80 package information

### Figure 43. LQFP80 - 80-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| Table 51. LQFP80 - 80-pin, 14 x 1 | 4 mm low-profile quad flat package mechanical |

|-----------------------------------|-----------------------------------------------|

| •                                 | data <sup>(1)</sup>                           |

| Symbol | millimeters |       |       | inches |        |        |  |

|--------|-------------|-------|-------|--------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Min    | Тур    | Max    |  |

| A      | -           | -     | 1.600 | -      | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020 | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531 | 0.0551 | 0.0571 |  |

| b      | 0.220       | 0.320 | 0.380 | 0.0087 | 0.0126 | 0.0150 |  |

| с      | 0.090       | -     | 0.200 | 0.0035 | -      | 0.0079 |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14733 Rev 13