Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Active                                                               |

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 24MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                |

| Number of I/O              | 38                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 6K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                         |

| Data Converters            | A/D 10x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-LQFP                                                              |

| Supplier Device Package    | 48-LQFP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s208c8t6 |

### 4.2 Single wire interface module (SWIM) and debug module (DM)

The single wire interface module and debug module permits non-intrusive, real-time incircuit debugging and fast memory programming.

#### **SWIM**

Single wire interface module for direct access to the debug module and memory programming. The interface can be activated in all device operation modes. The maximum data transmission speed is 145 bytes/ms.

#### **Debug module**

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, also CPU operation can be monitored in real-time by means of shadow registers.

- R/W to RAM and peripheral registers in real-time

- R/W access to all resources by stalling the CPU

- Breakpoints on all program-memory instructions (software breakpoints)

- Two advanced breakpoints, 23 predefined configurations

### 4.3 Interrupt controller

- Nested interrupts with three software priority levels

- 32 interrupt vectors with hardware priority

- Up to 37 external interrupts on six vectors including TLI

- Trap and reset interrupts

# 4.4 Flash program and data EEPROM memory

- Up to 128 Kbytes of high density Flash program single voltage Flash memory

- Up to 2K bytes true data EEPROM

- Read while write: Writing in data memory possible while executing code in program memory.

- User option byte area

#### Write protection (WP)

Write protection of Flash program memory and data EEPROM is provided to avoid unintentional overwriting of memory that could result from a user software malfunction.

There are two levels of write protection. The first level is known as MASS (memory access security system). MASS is always enabled and protects the main Flash program memory, data EEPROM and option bytes.

To perform in-application programming (IAP), this write protection can be removed by writing a MASS key sequence in a control register. This allows the application to write to data EEPROM, modify the contents of main program memory or the device option bytes.

A second level of write protection, can be enabled to further protect a specific area of memory known as UBC (user boot code). Refer to *Figure 2*.

#### Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure

The IWDG time base spans from 60 µs to 1 s.

### 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM3 input capture channel 1 for calibration

## 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

#### 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

# 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

5/

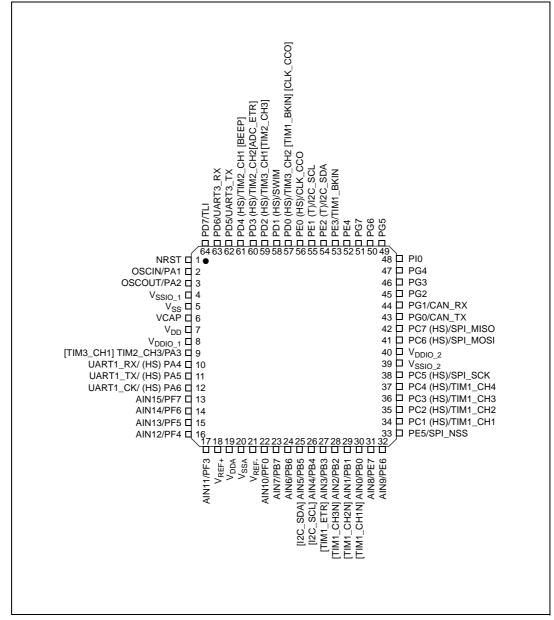

Figure 4. LQFP 64-pin pinout

- (HS) high sink capability.

- 2. (T) True open drain (P-buffer and protection diode to  $V_{\mbox{\scriptsize DD}}$  not implemented).

- 3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

- 4. CAN\_RX and CAN\_TX is available on STM8S208xx devices only.

57

Table 5. Legend/abbreviations for pinout table

| Туре             | I= Input, O                | = Output, S = Power supply                                                                                                                          |  |  |  |  |

|------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Level            | Input                      | CM = CMOS                                                                                                                                           |  |  |  |  |

|                  | Output                     | HS = High sink                                                                                                                                      |  |  |  |  |

| Output speed     | O2 = Fast (<br>O3 = Fast/s | (up to 2 MHz) up to 10 MHz) slow programmability with slow as default state after reset slow programmability with fast as default state after reset |  |  |  |  |

| Port and control | Input                      | float = floating, wpu = weak pull-up                                                                                                                |  |  |  |  |

| configuration    | Output                     | T = True open drain, OD = Open drain, PP = Push pull                                                                                                |  |  |  |  |

| Reset state      |                            |                                                                                                                                                     |  |  |  |  |

### Table 6. Pin description

|        | Pin    | num    | ber    |        |                     |      |          | Inpu     | t              |           | Out   | put |    |                                |                                  |                                                      |

|--------|--------|--------|--------|--------|---------------------|------|----------|----------|----------------|-----------|-------|-----|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name            | Туре | floating | ndw      | Ext. interrupt | High sink | Speed | ОО  | PP | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | 1      | 1      | 1      | NRST                | I/O  |          | <u>X</u> |                |           |       |     |    | Reset                          |                                  |                                                      |

| 2      | 2      | 2      | 2      | 2      | PA1/OSCIN           | I/O  | <u>X</u> | Х        |                |           | 01    | Х   | Х  | Port A1                        | Resonator/<br>crystal in         |                                                      |

| 3      | 3      | 3      | 3      | 3      | PA2/OSCOUT          | I/O  | <u>X</u> | Х        | X              |           | 01    | Х   | Х  | Port A2                        | Resonator/<br>crystal out        |                                                      |

| 4      | 4      | 4      | 4      | -      | V <sub>SSIO_1</sub> | S    |          |          |                |           |       |     |    | I/O groun                      | d                                |                                                      |

| 5      | 5      | 5      | 5      | 4      | V <sub>SS</sub>     | S    |          |          |                |           |       |     |    | Digital gro                    | ound                             |                                                      |

| 6      | 6      | 6      | 6      | 5      | VCAP                | S    |          |          |                |           |       |     |    | 1.8 V reg                      | ulator capacitor                 |                                                      |

| 7      | 7      | 7      | 7      | 6      | $V_{DD}$            | S    |          |          |                |           |       |     |    | Digital po                     | wer supply                       |                                                      |

| 8      | 8      | 8      | 8      | 7      | V <sub>DDIO_1</sub> | S    |          |          |                |           |       |     |    | I/O powe                       | r supply                         |                                                      |

| 9      | 9      | 9      | -      | -      | PA3/TIM2_CH3        | I/O  | <u>X</u> | X        | Х              |           | 01    | X   | Х  | Port A3                        | Timer 2 -<br>channel3            | TIM3_CH1<br>[AFR1]                                   |

| 10     | 10     | 10     | 9      | -      | PA4/UART1_RX        | I/O  | <u>X</u> | Х        | Х              | HS        | О3    | Х   | Х  | Port A4                        | UART1<br>receive                 |                                                      |

| 11     | 11     | 11     | 10     | -      | PA5/UART1_TX        | I/O  | <u>X</u> | Х        | X              | HS        | О3    | X   | Х  | Port A5                        | UART1<br>transmit                |                                                      |

Table 6. Pin description (continued)

|        | Pin    | num    | ber    |        | 143            |      |          | Inpu | scri<br>t      |           | Out   |   |   | ,                              |                                    |                                                      |

|--------|--------|--------|--------|--------|----------------|------|----------|------|----------------|-----------|-------|---|---|--------------------------------|------------------------------------|------------------------------------------------------|

| LQFP80 | LQFP64 | LQFP48 | LQFP44 | LQFP32 | Pin name       | Туре | floating | ndw  | Ext. interrupt | High sink | Speed | Ф | М | Main function<br>(after reset) | Default<br>alternate<br>function   | Alternate<br>function<br>after remap<br>[option bit] |

| 31     | 27     | 19     | 18     | 13     | PB3/AIN3       | I/O  | <u>X</u> | Х    | Х              |           | 01    | X | Х | Port B3                        | Analog<br>input 3                  | TIM1_ETR<br>[AFR5]                                   |

| 32     | 28     | 20     | 19     | 14     | PB2/AIN2       | I/O  | <u>X</u> | X    | Х              |           | 01    | Χ | Х | Port B2                        | Analog<br>input 2                  | TIM1_<br>CH3N<br>[AFR5]                              |

| 33     | 29     | 21     | 20     | 15     | PB1/AIN1       | I/O  | <u>X</u> | х    | Х              |           | O1    | Х | Х | Port B1                        | Analog<br>input 1                  | TIM1_<br>CH2N<br>[AFR5]                              |

| 34     | 30     | 22     | 21     | 16     | PB0/AIN0       | I/O  | <u>X</u> | Х    | Х              |           | O1    | Х | Х | Port B0                        | Analog<br>input 0                  | TIM1_<br>CH1N<br>[AFR5]                              |

| 35     | -      | -      | 1      | 1      | PH4/TIM1_ETR   | I/O  | <u>x</u> | Х    |                |           | 01    | Х | Х | Port H4                        | Timer 1 -<br>trigger input         |                                                      |

| 36     |        | 1      | 1      | 1      | PH5/ TIM1_CH3N | I/O  | <u>X</u> | X    |                |           | 01    | Х | Х | Port H5                        | Timer 1 -<br>inverted<br>channel 3 |                                                      |

| 37     | ,      | -      | 1      | •      | PH6/ TIM1_CH2N | I/O  | <u>X</u> | х    |                |           | O1    | Х | Х | Port H6                        | Timer 1 -<br>inverted<br>channel 2 |                                                      |

| 38     | -      | -      | 1      | -      | PH7/ TIM1_CH1N | I/O  | <u>X</u> | х    |                |           | O1    | Х | Х | Port H7                        | Timer 1 -<br>inverted<br>channel 2 |                                                      |

| 39     | 31     | 23     | -      | -      | PE7/AIN8       | I/O  | <u>X</u> | Х    | Χ              |           | O1    | Χ | Х | Port E7                        | Analog input 8                     |                                                      |

| 40     | 32     | 24     | 22     | •      | PE6/AIN9       | I/O  | <u>X</u> | Х    | Х              |           | 01    | Χ | Χ | Port E6                        | Analog input 9                     |                                                      |

| 41     | 33     | 25     | 23     | 17     | PE5/SPI_NSS    | I/O  | <u>x</u> | X    | Х              |           | O1    | X | Х | Port E5                        | SPI<br>master/slave<br>select      |                                                      |

| 42     | -      | -      | 1      | -      | PC0/ADC_ETR    | I/O  | <u>x</u> | Х    | Х              |           | 01    | Х | Х | Port C0                        | ADC trigger input                  |                                                      |

| 43     | 34     | 26     | 24     | 18     | PC1/TIM1_CH1   | I/O  | <u>x</u> | Х    | Х              | HS        | О3    | Х | Х | Port C1                        | Timer 1 -<br>channel 1             |                                                      |

| 44     | 35     | 27     | 25     | 19     | PC2/TIM1_CH2   | I/O  | <u>X</u> | Х    | Х              | HS        | О3    | X | Х | Port C2                        | Timer 1-<br>channel 2              |                                                      |

| 45     | 36     | 28     | 26     | 20     | PC3/TIM1_CH3   | I/O  | <u>X</u> | Х    | Х              | HS        | О3    | X | Х | Port C3                        | Timer 1 -<br>channel 3             |                                                      |

Pin number Input Output Main function (after reset) Alternate Ext. interrupt **Default** Type function LQFP48 floating High sink LQFP44 LQFP64 LQFP80 alternate Pin name Speed ndw ОО after remap Р function [option bit] 55 39 35 PE1/I<sup>2</sup>C\_SCL I/O Χ 01  $T^{(3)}$ Port E1 I<sup>2</sup>C clock 69 <u>X</u> Configurable 56 40 PE0/CLK\_CCO I/O HS О3 Χ 70 36 <u>X</u> Χ Χ Χ Port E0 clock output 71 I/O 01 PI6 Χ Χ Χ Port I6 <u>X</u> I/O PI7 <u>X</u> Х 01 Х Port I7 72 Х TIM1\_BKIN [AFR3]/ Timer 3 -25 PD0/TIM3\_CH2 I/O 73 57 HS О3 Χ Port D0 41 37 <u>X</u> Χ Χ Х channel 2 CLK\_CCO [AFR2] SWIM data 74 58 42 38 26 PD1/SWIM<sup>(4)</sup> I/O Χ HS 04 Χ Χ Port D1 <u>X</u> Χ interface Timer 3 -TIM2\_CH3 59 HS 43 27 PD2/TIM3 CH1 I/O Х О3 Χ Port D2 75 39 <u>X</u> Χ Х channel 1 [AFR1] ADC\_ETR Timer 2 -76 60 44 40 28 PD3/TIM2\_CH2 I/O <u>X</u> Χ Χ HS О3 Χ Χ Port D3 channel 2 [AFR0] **BEEP** output PD4/TIM2\_CH1/B Timer 2 -Port D4 I/O HS О3 61 45 41 29 <u>X</u> Χ Χ Χ 77 Х EEP channel 1 [AFR7] UART3 data 78 62 46 42 30 PD5/ UART3\_TX I/O Χ Χ 01 Χ Χ Port D5 <u>X</u> transmit PD6/ UART3 data I/O 01 Port D6 79 63 47 43 31 <u>X</u> Χ Χ Χ Χ UART3\_RX<sup>(1)</sup> receive Top level TIM1\_CH4 48 44 32 PD7/TLI I/O Х Х 01 Х Х Port D7 80 64 <u>X</u> [AFR4]<sup>(5)</sup> interrupt

Table 6. Pin description (continued)

# 5.2 Alternate function remapping

As shown in the rightmost column of the pin description table, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function

The default state of UART1\_RX and UART3\_RX pins is controlled by the ROM bootloader. These pins are pulled up as part

of the bootloader activation process and returned to the floating state before a return from the bootloader.

<sup>2.</sup> The beCAN interface is available on STM8S208xx devices only

In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to V<sub>DD</sub> are not implemented).

<sup>4.</sup> The PD1 pin is in input pull-up during the reset phase and after the internal reset release.

<sup>5.</sup> Available in 44-pin package only. On other packages, the AFR4 bit is reserved and must be kept at 0.

remap) option bits. Refer to Section 8: Option bytes on page 47. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of the family reference manual, RM0016).

Table 13. Option byte description (continued)

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPTBL           | BL[7:0] Bootloader option byte  For STM8S products, this option is checked by the boot ROM code after reset. Depending on the content of addresses 0x487E, 0x487F, and 0x8000 (reset vector), the CPU jumps to the bootloader or to the reset vector. Refer to the UM0560 (STM8L/S bootloader manual) for more details.  For STM8L products, the bootloader option bytes are on addresses 0xXXXX and 0xXXXX+1 (2 bytes). These option bytes control whether the bootloader is active or not. For more details, refer to the UM0560 (STM8L/S bootloader manual) for more details. |

### 10 Electrical characteristics

#### 10.1 Parameter conditions

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>.

#### 10.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_{Amax}$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm$  3  $\Sigma$ ).

### 10.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 5$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm$  2  $\Sigma$ ).

### 10.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 10.1.4 Typical current consumption

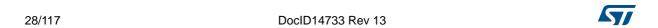

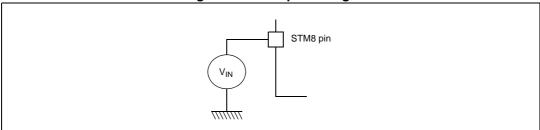

For typical current consumption measurements,  $V_{DD}$ ,  $V_{DDIO}$  and  $V_{DDA}$  are connected together in the configuration shown in *Figure 9*.

Figure 9. Supply current measurement conditions

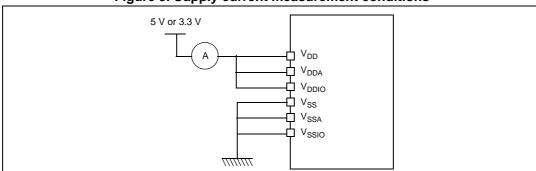

### 10.1.5 Pin loading conditions

### 10.1.6 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 10*.

Figure 10. Pin loading conditions

## 10.1.7 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 11*.

Figure 11. Pin input voltage

### 10.3 Operating conditions

The device must be used in operating conditions that respect the parameters in *Table 18*. In addition, full account must be taken of all physical capacitor characteristics and tolerances.

**Table 18. General operating conditions**

| Symbol                          | Parameter                                                | Conditions                                                                                                                                          | Min  | Max                | Unit |

|---------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| f <sub>CPU</sub>                | Internal CPU clock frequency                             | $T_A \le 105 ^{\circ}C$                                                                                                                             | 0    | 24                 | MHz  |

| CPU                             | internal of o clock frequency                            |                                                                                                                                                     | 0    | 16                 | MHz  |

| $V_{DD/}V_{DD\_IO}$             | Standard operating voltage                               |                                                                                                                                                     | 2.95 | 5.5                | V    |

| (1)                             | C <sub>EXT</sub> : capacitance of external capacitor     |                                                                                                                                                     | 470  | 3300               | nF   |

| V <sub>CAP</sub> <sup>(1)</sup> | ESR of external capacitor                                | at 1 MHz <sup>(2)</sup>                                                                                                                             | -    | 0.3                | Ω    |

|                                 | ESL of external capacitor                                | at i winz ,                                                                                                                                         | -    | 15                 | nH   |

| P <sub>D</sub> <sup>(3)</sup>   | Power dissipation at T <sub>A</sub> = 85° C for suffix 6 | 44, 48, 64, and 80-pin<br>devices, with output on 8<br>standard ports, 2 high sink<br>ports and 2 open drain ports<br>simultaneously <sup>(4)</sup> |      | 443                | mW   |

| _                               | or T <sub>A</sub> = 125° C for suffix 3                  | 32-pin package, with output<br>on 8 standard ports and 2<br>high sink ports<br>simultaneously <sup>(4)</sup>                                        |      | 360                |      |

| т                               | Ambient temperature for 6 suffix version                 | Maximum power dissipation                                                                                                                           | -40  | 85                 |      |

| T <sub>A</sub>                  | Ambient temperature for 3 suffix version                 | Maximum power dissipation                                                                                                                           | -40  | 125                | °C   |

| т                               | Junction temperature range                               | 6 suffix version                                                                                                                                    | -40  | 105                |      |

| ТЈ                              | Juniculon temperature range                              | 3 suffix version                                                                                                                                    | -40  | 130 <sup>(5)</sup> |      |

Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

DocID14733 Rev 13

<sup>2.</sup> This frequency of 1 MHz as a condition for  $V_{\mbox{\footnotesize{CAP}}}$  parameters is given by design of internal regulator.

To calculate P<sub>Dmax</sub>(T<sub>A</sub>), use the formula P<sub>Dmax</sub> = (T<sub>Jmax</sub> - T<sub>A</sub>)/Θ<sub>JA</sub> (see Section 11.2: Thermal characteristics on page 108) with the value for T<sub>Jmax</sub> given in Table 18 above and the value for Θ<sub>JA</sub> given in Table 57: Thermal characteristics.

<sup>4.</sup> Refer to Section 11.2: Thermal characteristics on page 108 for the calculation method.

<sup>5.</sup>  $T_{Jmax}$  is given by the test limit. Above this value the product behavior is not guaranteed.

### Total current consumption in wait mode

Table 22. Total current consumption in wait mode at  $V_{DD}$  = 5 V

| Symbol               | Parameter            | Condit                                                      | Тур                                   | Max <sup>(1)</sup> | Unit |    |

|----------------------|----------------------|-------------------------------------------------------------|---------------------------------------|--------------------|------|----|

|                      |                      | 1CPU - 1MASTER - 24 WI 12,                                  | HSE crystal osc. (24 MHz)             | 2.4                |      |    |

|                      |                      |                                                             | HSE user ext. clock (24 MHz)          | 1.8                | 4.7  |    |

|                      | Supply               | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 2.0                |      |    |

|                      |                      |                                                             | HSE user ext. clock (16 MHz)          | 1.4                | 4.4  |    |

| I <sub>DD(WFI)</sub> | current in wait mode |                                                             | HSI RC osc. (16 MHz)                  | 1.2                | 1.6  | mA |

|                      | wait mode            | $f_{CPU} = f_{MASTER}/128 = 125 \text{ kHz}$                | HSI RC osc. (16 MHz)                  | 1.0                |      |    |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55               |      |    |

|                      |                      | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.5                |      |    |

<sup>1.</sup> Data based on characterization results, not tested in production.

Table 23. Total current consumption in wait mode at  $V_{DD}$  = 3.3 V

| Symbol               | Parameter  | Condit                                                      | ions                                  | Тур  | Max <sup>(1)</sup> | Unit |

|----------------------|------------|-------------------------------------------------------------|---------------------------------------|------|--------------------|------|

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.0  |                    |      |

|                      |            | T <sub>A</sub> ≤ 105 °C                                     | HSE user ext. clock (24 MHz)          | 1.8  | 4.7                |      |

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE crystal osc. (16 MHz)             | 1.6  |                    |      |

|                      | Supply     |                                                             | HSE user ext. clock (16 MHz)          | 1.4  | 4.4                |      |

| I <sub>DD(WFI)</sub> | current in |                                                             | HSI RC osc. (16 MHz)                  | 1.2  | 1.6                | mA   |

|                      | wait mode  | $f_{CPU} = f_{MASTER}/128 = 125 \text{ kHz}$                | HSI RC osc. (16 MHz)                  | 1.0  |                    |      |

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55 |                    |      |

|                      |            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | LSI RC osc. (128 kHz)                 | 0.5  |                    |      |

<sup>1.</sup> Data based on characterization results, not tested in production.

<sup>2.</sup> Default clock configuration measured with all peripherals off.

<sup>2.</sup> Default clock configuration measured with all peripherals off.

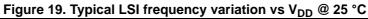

### Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{DD}$  and  $T_{A}$ .

Table 34. LSI oscillator characteristics

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        |            | 110 | 128 | 146              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       |            |     |     | 7 <sup>(1)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator power consumption |            |     | 5   |                  | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production.

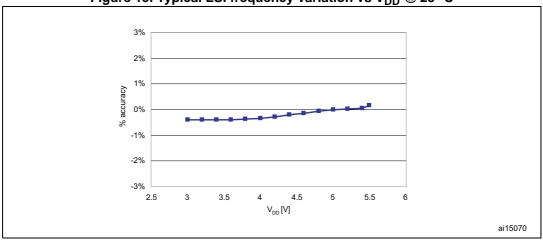

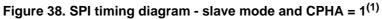

### 10.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

**Table 42. SPI characteristics**

| Symbol                                               | Parameter                    | Conditions                      | Min                      | Max                      | Unit   |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|--------|

| f <sub>SCK</sub>                                     | SDI alaak fraguanay          | Master mode                     | 0                        | 10                       | MHz    |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency          | Slave mode                      | 0                        | 6                        | IVITIZ |

| t <sub>r(SCK)</sub>                                  | SPI clock rise and fall time | Capacitive load: C = 30 pF      |                          | 25                       |        |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  |                          |        |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                | Slave mode                      | 70                       |                          |        |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |        |

| t <sub>su(MI)</sub> (1)<br>t <sub>su(SI)</sub> (1)   | Data input setup time        | Master mode                     | 5                        |                          |        |

| t <sub>su(SI)</sub> <sup>(1)</sup>                   | Data input setup time        | Slave mode                      | 5                        |                          |        |

| t <sub>h(MI)</sub> (1)                               | Data input hold time         | Master mode                     | 7                        |                          | ns     |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     | Data input hold time         | Slave mode                      | 10                       |                          |        |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time      | Slave mode                      |                          | 3 x t <sub>MASTER</sub>  |        |

| t <sub>dis(SO)</sub> (1)(3)                          | Data output disable time     | Slave mode                      | 25                       |                          |        |

| t <sub>v(SO)</sub> (1)                               | Data output valid time       | Slave mode (after enable edge)  |                          | 75                       |        |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time       | Master mode (after enable edge) |                          | 30                       |        |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data autaut hald time        | Slave mode (after enable edge)  | 31                       |                          |        |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master mode (after enable edge) | 12                       |                          |        |

<sup>1.</sup> Values based on design simulation and/or characterization results, and not tested in production.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

Figure 37. SPI timing diagram - slave mode and CPHA = 0

<sup>1.</sup> Measurement points are done at CMOS levels: 0.3  $\rm V_{DD}$  and 0.7  $\rm V_{DD.}$

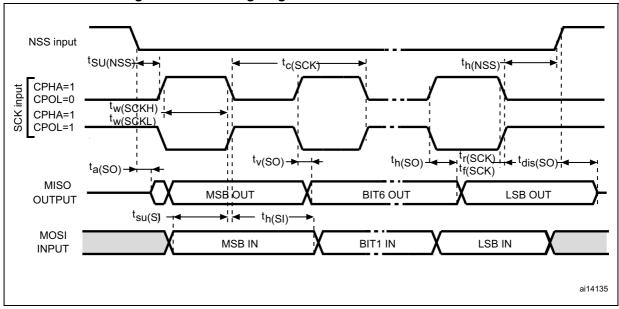

Figure 41. ADC accuracy characteristics

- 1. Example of an actual transfer curve.

- The ideal transfer curve

- End point correlation line

E<sub>T</sub> = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.

E<sub>O</sub> = Offset error: deviation between the first actual transition and the first ideal one.

E<sub>G</sub> = Gain error: deviation between the last ideal transition and the last actual one.

E<sub>D</sub> = Differential linearity error: maximum deviation between actual steps and the ideal one.

E<sub>L</sub> = Integral linearity error: maximum deviation between any actual transition and the end point correlation

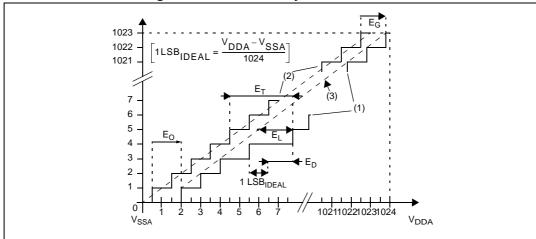

Figure 42. Typical application with ADC

#### 10.3.11 EMC characteristics

Susceptibility tests are performed on a sample basis during product characterization.

#### Functional EMS (electromagnetic susceptibility)

While executing a simple application (toggling 2 LEDs through I/O ports), the product is stressed by two electromagnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electrostatic discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be recovered by applying a low state on the NRST pin or the oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

Table 47. EMS data

| Symbol            | Parameter                                                                                                                        | Conditions                                                                        | Level/class |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                   | $V_{DD} = 5$ V, $T_A = 25$ °C, $f_{MASTER} = 16$ MHz, conforming to IEC 61000-4-2 | 2B          |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 5$ V, $T_A = 25$ °C, $f_{MASTER} = 16$ MHz, conforming to IEC 61000-4-4 | 4A          |

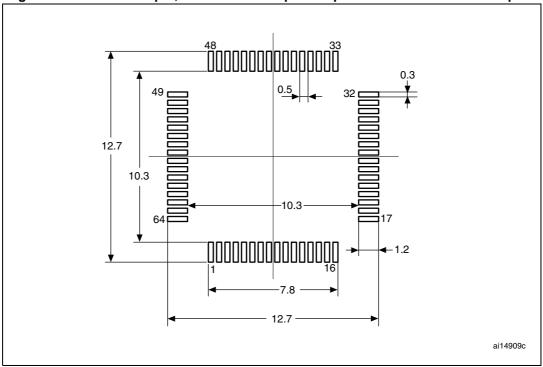

Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data (continued)

|        |       | mm     | (00111111000 |        | inches <sup>(1)</sup> |        |

|--------|-------|--------|--------------|--------|-----------------------|--------|

| Symbol | Min   | Тур    | Max          | Min    | Тур                   | Max    |

| D      | -     | 12.000 | -            | -      | 0.4724                | -      |

| D1     | -     | 10.000 | -            | -      | 0.3937                | -      |

| D3     | -     | 7.500  | -            | -      | 0.2953                | -      |

| Е      | -     | 12.000 | -            | -      | 0.4724                | -      |

| E1     | -     | 10.000 | -            | -      | 0.3937                | -      |

| E3     | -     | 7.500  | -            | -      | 0.2953                | -      |

| е      | -     | 0.500  | -            | -      | 0.0197                | -      |

| θ      | 0°    | 3.5°   | 7°           | 0°     | 3.5°                  | 7°     |

| L      | 0.450 | 0.600  | 0.750        | 0.0177 | 0.0236                | 0.0295 |

| L1     | -     | 1.000  | -            | -      | 0.0394                | -      |

| ccc    | -     | -      | 0.080        | -      | -                     | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to four decimal places.

Figure 48. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

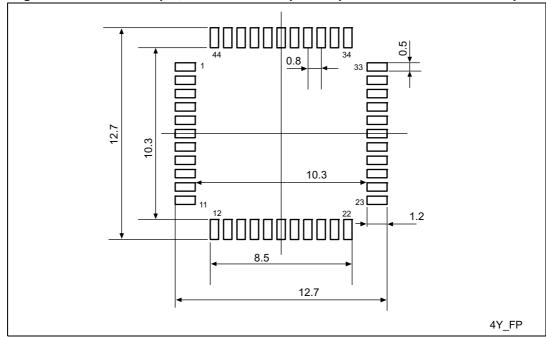

Figure 54. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

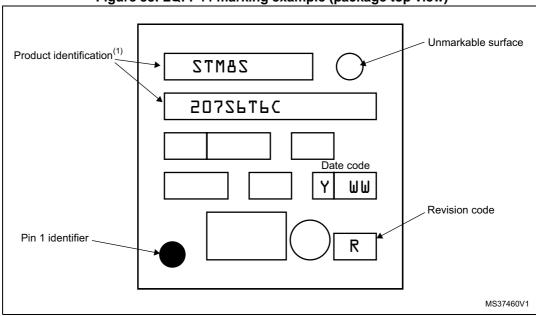

#### **Device marking**

104/117

The following figure shows the marking for the LQFP44 package.

Figure 55. LQFP44 marking example (package top view)

DocID14733 Rev 13

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 14 Revision history

Table 58. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-May-2008 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 05-Jun-2008 | 2        | Added part numbers on page 1 and in <i>Table 2 on page 11</i> . Updated <i>Section 4: Product overview</i> . Updated <i>Section 10: Electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22-Jun-2008 | 3        | Added part numbers on page 1 and in Table 2 on page 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12-Aug-2008 | 4        | Added 32 pin device pinout and ordering information.  Updated UBC option description in <i>Table 13 on page 48</i> .  USART renamed UART1, LINUART renamed UART3.  Max. ADC frequency increased to 6 MHz.                                                                                                                                                                                                                                                                                                                                                                                             |

| 20-Oct-2008 | 5        | Removed STM8S207K4 part number. Removed LQFP64 14 x 14 mm package. Added medium and high density Flash memory categories. Added Section 6: Memory and register map on page 34. Replaced beCAN3 by beCAN in Section 4.14.5: beCAN. Updated Section 10: Electrical characteristics on page 52. Updated LQFP44 (Figure 53 and Table 55), and LQFP32 outline and mechanical data (Figure 56, and Table 56).                                                                                                                                                                                               |

| 08-Dec-2008 | 6        | Changed V <sub>DD</sub> minimum value from 3.0 to 2.95 V. Updated number of High Sink I/Os in pinout. Removed FLASH _NFPR and FLASH _FPR registers in <i>Table 9: General hardware register map</i> .                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30-Jan-2009 | 7        | Removed preliminary status. Removed VQFN32 package. Added STM8S207C6, STM8S207S6. Updated external interrupts in <i>Table 2 on page 11</i> . Updated <i>Section 10: Electrical characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10-Jul-2009 | 8        | Document status changed from "preliminary data" to "datasheet". Added LQFP64 14 x 14 mm package.  Added STM8S207M8, STM8S207SB, STM8S208R8, STM8S208R6, STM8S208C8, and STM8S208C6, STM8S208SB, STM8S208S8, and STM8S208S6.  Replaced "CAN" with "beCAN".  Added Table 3 to Section 4.5: Clock controller.  Updated Section 4.8: Auto wakeup counter.  Added beCAN peripheral (impacting Table 1 and Figure 6).  Added footnote about CAN_RX/TX to pinout figures 5, 4, and 6.  Table 6: Removed 'X' from wpu column of I <sup>2</sup> C pins (no wpu available).  Added Table 11: Interrupt mapping. |