# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                               |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | STM8                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 24MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                   |

| Program Memory Size        | 128KB (128K x 8)                                                     |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 6K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                         |

| Data Converters            | A/D 16x10b                                                           |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 64-LQFP                                                              |

| Supplier Device Package    | 64-LQFP (10x10)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s208rbt3 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 6.2    | Registe  | map                                               |

|----|--------|----------|---------------------------------------------------|

| 7  | Interr | upt vec  | tor mapping                                       |

| 8  | Optio  | n bytes  |                                                   |

| 9  | Uniqu  | ie ID    |                                                   |

| 10 | Electr | ical cha | aracteristics                                     |

|    | 10.1   | Parame   | ter conditions                                    |

|    |        | 10.1.1   | Minimum and maximum values                        |

|    |        | 10.1.2   | Typical values                                    |

|    |        | 10.1.3   | Typical curves                                    |

|    |        | 10.1.4   | Typical current consumption                       |

|    |        | 10.1.5   | Pin loading conditions                            |

|    |        | 10.1.6   | Loading capacitor                                 |

|    |        | 10.1.7   | Pin input voltage                                 |

|    | 10.2   | Absolute | e maximum ratings 54                              |

|    | 10.3   | Operatir | ng conditions                                     |

|    |        | 10.3.1   | VCAP external capacitor                           |

|    |        | 10.3.2   | Supply current characteristics                    |

|    |        | 10.3.3   | External clock sources and timing characteristics |

|    |        | 10.3.4   | Internal clock sources and timing characteristics |

|    |        | 10.3.5   | Memory characteristics                            |

|    |        | 10.3.6   | I/O port pin characteristics                      |

|    |        | 10.3.7   | Reset pin characteristics                         |

|    |        | 10.3.8   | SPI serial peripheral interface80                 |

|    |        | 10.3.9   | I <sup>2</sup> C interface characteristics        |

|    |        | 10.3.10  | 10-bit ADC characteristics                        |

|    |        | 10.3.11  | EMC characteristics                               |

| 11 | Packa  | age cha  | racteristics                                      |

|    | 11.1   | Package  | e information                                     |

|    |        | 11.1.1   | LQFP80 package information92                      |

|    |        | 11.1.2   | LQFP64 package information95                      |

|    |        | 11.1.3   | LQFP48 package information                        |

|    |        | 11.1.4   | LQFP44 package information                        |

|    |        |          |                                                   |

DocID14733 Rev 13

| Figure 49. | LQFP64 marking example (package top view)9                                   | 8  |

|------------|------------------------------------------------------------------------------|----|

| Figure 50. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline              | )9 |

| Figure 51. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint        | 0  |

| Figure 52. | LQFP48 marking example (package top view)10                                  | )1 |

| Figure 53. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat package outline            | )2 |

| Figure 54. | LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint      | )4 |

| Figure 55. | LQFP44 marking example (package top view)10                                  | )4 |

| Figure 56. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline              | )5 |

| Figure 57. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint        | )6 |

| Figure 58. | LQFP32 marking example (package top view)10                                  | )7 |

| Figure 59. | STM8S207xx/208xx performance line ordering information scheme <sup>(1)</sup> | 2  |

#### **Block diagram** 3

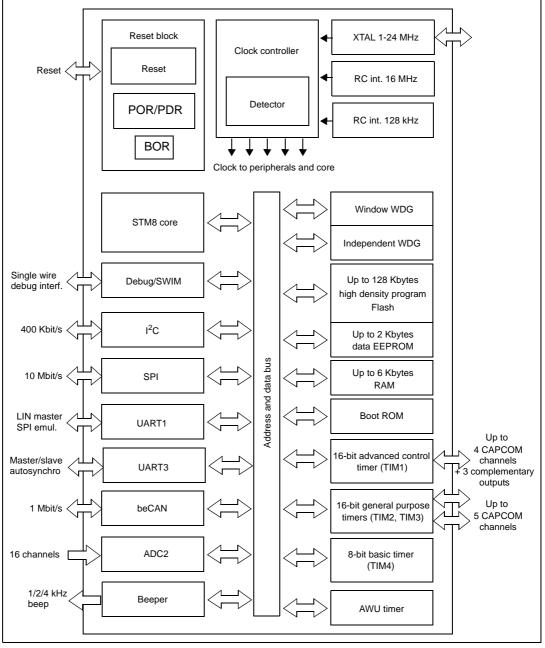

Figure 1. STM8S20xxx block diagram

1.

Legend: ADC: Analog-to-digital converter beCAN: Controller area network BOR: Brownout reset PC: Inter-integrated circuit multimaster interface Independent WDG: Independent watchdog POR/PDR: Power on reset / power down reset SPI: Serial peripheral interface SWIM: Single wire interface module UART: Universal asynchronous receiver transmitter Window WDG: Window watchdog

DocID14733 Rev 13

# 4 **Product overview**

The following section intends to give an overview of the basic features of the STM8S20xxx functional modules and peripherals.

For more detailed information please refer to the corresponding family reference manual (RM0016).

## 4.1 Central processing unit STM8

The 8-bit STM8 core is designed for code efficiency and performance.

It contains 6 internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

#### Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching for most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16-Mbyte linear memory space

- 16-bit stack pointer access to a 64 K-level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

#### Addressing

- 20 addressing modes

- Indexed indirect addressing mode for look-up tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

#### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

## 4.6 **Power management**

For efficient power management, the application can be put in one of four different lowpower modes. You can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- *Wait mode*: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- **Halt mode**: In this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

## 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

#### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- 1. Timeout: At 16 MHz CPU clock the time-out period can be adjusted between 75  $\mu$ s up to 64 ms.

- 2. Refresh out of window: The downcounter is refreshed before its value is lower than the one stored in the window register.

## 4.14.1 UART1

#### **Main features**

- One Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- Single wire half duplex mode

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

#### LIN master mode

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

## 4.14.2 UART3

#### Main features

- 1 Mbit/s full duplex SCI

- LIN master capable

- High precision baud rate generator

#### Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

#### LIN master capability

- Emission: Generates 13-bit sync break frame

- Reception: Detects 11-bit break frame

#### LIN slave mode

- Autonomous header handling one single interrupt per valid message header

- Automatic baud rate synchronization maximum tolerated initial clock deviation ±15%

- Sync delimiter checking

- 11-bit LIN sync break detection break detection always active

- Parity check on the LIN identifier field

- LIN error management

- Hot plugging support

#### 4.14.3 SPI

- Maximum speed: 10 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

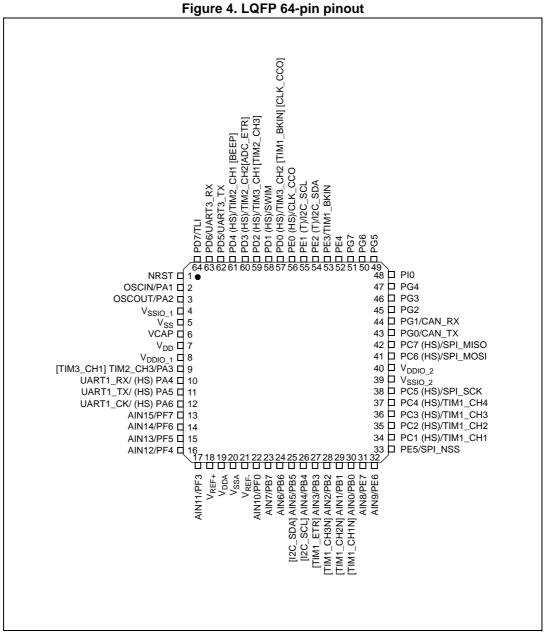

1. (HS) high sink capability.

2. (T) True open drain (P-buffer and protection diode to  $V_{\mbox{\scriptsize DD}}$  not implemented).

3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

4. CAN\_RX and CAN\_TX is available on STM8S208xx devices only.

| Address                   | Block | Register label           | Register name                                    | Reset<br>status    |  |

|---------------------------|-------|--------------------------|--------------------------------------------------|--------------------|--|

| 0x00 5050 to<br>0x00 5059 |       | Reserved area (10 bytes) |                                                  |                    |  |

| 0x00 505A                 |       | FLASH_CR1                | Flash control register 1                         | 0x00               |  |

| 0x00 505B                 |       | FLASH_CR2                | Flash control register 2                         | 0x00               |  |

| 0x00 505C                 |       | FLASH_NCR2               | Flash complementary control register 2           | 0xFF               |  |

| 0x00 505D                 | Flash | FLASH _FPR               | Flash protection register                        | 0x00               |  |

| 0x00 505E                 |       | FLASH _NFPR              | Flash complementary protection register          | 0xFF               |  |

| 0x00 505F                 |       | FLASH _IAPSR             | Flash in-application programming status register | 0x00               |  |

| 0x00 5060 to<br>0x00 5061 |       |                          | Reserved area (2 bytes)                          |                    |  |

| 0x00 5062                 | Flash | FLASH_PUKR               | Flash Program memory unprotection register       | 0x00               |  |

| 0x00 5063                 |       |                          | Reserved area (1 byte)                           |                    |  |

| 0x00 5064                 | Flash | FLASH _DUKR              | Data EEPROM unprotection register                | 0x00               |  |

| 0x00 5065 to<br>0x00 509F |       |                          | Reserved area (59 bytes)                         |                    |  |

| 0x00 50A0                 | ІТС   | EXTI_CR1                 | External interrupt control register 1            | 0x00               |  |

| 0x00 50A1                 |       | EXTI_CR2                 | External interrupt control register 2            | 0x00               |  |

| 0x00 50A2 to<br>0x00 50B2 |       |                          | Reserved area (17 bytes)                         |                    |  |

| 0x00 50B3                 | RST   | RST_SR                   | Reset status register                            | 0xXX <sup>(1</sup> |  |

| 0x00 50B4 to<br>0x00 50BF |       |                          | Reserved area (12 bytes)                         |                    |  |

| 0x00 50C0                 | CLK   | CLK_ICKR                 | Internal clock control register                  | 0x01               |  |

| 0x00 50C1                 | - CLK | CLK_ECKR                 | External clock control register                  | 0x00               |  |

| 0x00 50C2                 |       |                          | Reserved area (1 byte)                           |                    |  |

| 0x00 50C3                 |       | CLK_CMSR                 | Clock master status register                     | 0xE1               |  |

| 0x00 50C4                 | ]     | CLK_SWR                  | Clock master switch register                     | 0xE1               |  |

| 0x00 50C5                 |       | CLK_SWCR                 | Clock switch control register                    | 0xXX               |  |

| 0x00 50C6                 |       | CLK_CKDIVR               | Clock divider register                           | 0x18               |  |

| 0x00 50C7                 | CLK   | CLK_PCKENR1              | Peripheral clock gating register 1               | 0xFF               |  |

| 0x00 50C8                 |       | CLK_CSSR                 | Clock security system register                   | 0x00               |  |

| 0x00 50C9                 |       | CLK_CCOR                 | Configurable clock control register              | 0x00               |  |

| 0x00 50CA                 |       | CLK_PCKENR2              | Peripheral clock gating register 2               | 0xFF               |  |

| 0x00 50CB                 |       | CLK_CANCCR               | CAN clock control register                       | 0x00               |  |

Table 9. General hardware register map

|                 | Table 13. Option byte description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Option byte no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| OPT0            | <b>ROP[7:0]</b> <i>Memory readout protection (ROP)</i><br>0xAA: Enable readout protection (write access via SWIM protocol)<br>Note: Refer to the family reference manual (RM0016) section on<br>Flash/EEPROM memory readout protection for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| OPT1            | UBC[7:0] User boot code area<br>0x00: no UBC, no write-protection<br>0x01: Pages 0 to 1 defined as UBC, memory write-protected<br>0x02: Pages 0 to 3 defined as UBC, memory write-protected<br>0x03: Pages 0 to 4 defined as UBC, memory write-protected<br><br>0xFE: Pages 0 to 255 defined as UBC, memory write-protected<br>0xFF: Reserved<br>Note: Refer to the family reference manual (RM0016) section on<br>Flash/EEPROM write protection for more details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| OPT2            | <ul> <li>AFR7<i>Alternate function remapping option 7</i></li> <li>0: Port D4 alternate function = TIM2_CH1</li> <li>1: Port D4 alternate function = BEEP</li> <li>AFR6 <i>Alternate function remapping option 6</i></li> <li>0: Port B5 alternate function = AIN5, port B4 alternate function = AIN4</li> <li>1: Port B5 alternate function = l<sup>2</sup>C_SDA, port B4 alternate function = l<sup>2</sup>C_SCL</li> <li>AFR5 <i>Alternate function remapping option 5</i></li> <li>0: Port B3 alternate function = AIN3, port B2 alternate function = AIN2, port B1 alternate function = AIN1, port B0 alternate function = AIN0</li> <li>1: Port B3 alternate function = TIM1_ETR, port B2 alternate function = TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate function = TIM1_CH3N, port B1 alternate function = TIM1_CH2N, port B0 alternate function = TIM1_CH1N</li> <li>AFR4 <i>Alternate function remapping option 4</i></li> <li>0: Port D7 alternate function = TIM1_CH4</li> <li>AFR3 <i>Alternate function remapping option 3</i></li> <li>0: Port D0 alternate function = TIM3_CH2</li> <li>1: Port D0 alternate function = TIM3_CH2</li> <li>1: Port D0 alternate function = CLK_CCO</li> <li>Note: AFR2 option has priority over AFR3 if both are activated</li> <li>AFR1 <i>Alternate function remapping option 1</i></li> <li>0: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH3</li> <li>AFR0 <i>Alternate function remapping option 1</i></li> <li>0: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH1</li> <li>1: Port A3 alternate function = TIM3_CH1, port D2 alternate function TIM3_CH3</li> <li>AFR0 <i>Alternate function remapping option 0</i></li> <li>0: Port D3 alternate function = TIM3_CH2</li> <li>1: Port D3 alternate function = TIM3_CH2</li> <li>1: Port D3 alternate function = TIM3_CH2</li></ul> |  |  |  |  |

## Table 13. Option byte description

# **10.2** Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                             | Ratings                                                           | Min                                                                    | Max                   | Unit |

|------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------|------|

| V <sub>DDx</sub> - V <sub>SS</sub> | Supply voltage (including $V_{DDA and} V_{DDIO}$ ) <sup>(1)</sup> | -0.3                                                                   | 6.5                   |      |

| V                                  | Input voltage on true open drain pins (PE1, PE2) <sup>(2)</sup>   | V <sub>SS</sub> - 0.3                                                  | 6.5                   | V    |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>                     | V <sub>SS</sub> - 0.3                                                  | V <sub>DD</sub> + 0.3 |      |

| V <sub>DDx</sub> - V <sub>DD</sub> | Variations between different power pins                           |                                                                        |                       | mV   |

| V <sub>SSx</sub> - V <sub>SS</sub> | Variations between all the different ground pins                  |                                                                        | 50                    | IIIV |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                                   | see Absolute maximum<br>ratings (electrical<br>sensitivity) on page 89 |                       |      |

| Table 15. | Voltage | characteristics |

|-----------|---------|-----------------|

|-----------|---------|-----------------|

1. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

## 10.3 Operating conditions

The device must be used in operating conditions that respect the parameters in *Table 18*. In addition, full account must be taken of all physical capacitor characteristics and tolerances.

| Symbol                          | Parameter                                              | Conditions                                                                                                                                          | Min  | Max                | Unit |  |

|---------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|--|

| f <sub>CPU</sub>                | Internal CPU clock frequency                           | $T_A \le 105 \ ^{\circ}C$                                                                                                                           | 0    | 24                 | MHz  |  |

| 'CPU                            | Internal OF O clock frequency                          |                                                                                                                                                     | 0    | 16                 | MHz  |  |

| $V_{DD/}V_{DD_{IO}}$            | Standard operating voltage                             |                                                                                                                                                     | 2.95 | 5.5                | V    |  |

|                                 | C <sub>EXT</sub> : capacitance of external capacitor   |                                                                                                                                                     | 470  | 3300               | nF   |  |

| V <sub>CAP</sub> <sup>(1)</sup> | ESR of external capacitor                              | at 1 MHz <sup>(2)</sup>                                                                                                                             | -    | 0.3                | Ω    |  |

|                                 | ESL of external capacitor                              |                                                                                                                                                     | -    | 15                 | nH   |  |

| P <sub>D</sub> <sup>(3)</sup>   | Power dissipation at $T_A = 85^{\circ}$ C for suffix 6 | 44, 48, 64, and 80-pin<br>devices, with output on 8<br>standard ports, 2 high sink<br>ports and 2 open drain ports<br>simultaneously <sup>(4)</sup> |      | 443                | mW   |  |

|                                 | or $T_A = 125^{\circ} C$ for suffix 3                  | 32-pin package, with output<br>on 8 standard ports and 2<br>high sink ports<br>simultaneously <sup>(4)</sup>                                        |      | 360                |      |  |

| т.                              | Ambient temperature for 6 suffix version               | Maximum power dissipation                                                                                                                           | -40  | 85                 |      |  |

| Τ <sub>Α</sub>                  | Ambient temperature for 3 suffix version               | Maximum power dissipation                                                                                                                           | -40  | 125                | °C   |  |

| ТJ                              | Junction temperature range                             | 6 suffix version                                                                                                                                    | -40  | 105                |      |  |

| ١J                              | Survey of temperature range                            | 3 suffix version                                                                                                                                    | -40  | 130 <sup>(5)</sup> |      |  |

| Table 18. | General | operating | conditions |

|-----------|---------|-----------|------------|

|-----------|---------|-----------|------------|

1. Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

2. This frequency of 1 MHz as a condition for  $V_{CAP}$  parameters is given by design of internal regulator.

To calculate P<sub>Dmax</sub>(T<sub>A</sub>), use the formula P<sub>Dmax</sub> = (T<sub>Jmax</sub> - T<sub>A</sub>)/Θ<sub>JA</sub> (see Section 11.2: Thermal characteristics on page 108) with the value for T<sub>Jmax</sub> given in Table 18 above and the value for Θ<sub>JA</sub> given in Table 57: Thermal characteristics.

4. Refer to Section 11.2: Thermal characteristics on page 108 for the calculation method.

5. T<sub>Jmax</sub> is given by the test limit. Above this value the product behavior is not guaranteed.

### Total current consumption in wait mode

| Symbol               | Parameter               | Conditions                                                  |                                       |      | Max <sup>(1)</sup> | Unit |

|----------------------|-------------------------|-------------------------------------------------------------|---------------------------------------|------|--------------------|------|

|                      |                         | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.4  |                    |      |

|                      |                         | $T_A \leq 105 \ ^{\circ}C$                                  | HSE user ext. clock (24 MHz)          | 1.8  | 4.7                |      |

|                      |                         | int in                                                      | HSE crystal osc. (16 MHz)             | 2.0  |                    |      |

|                      | Supply                  |                                                             | HSE user ext. clock (16 MHz)          | 1.4  | 4.4                |      |

| I <sub>DD(WFI)</sub> | current in<br>wait mode |                                                             | HSI RC osc. (16 MHz)                  | 1.2  | 1.6                |      |

|                      | wait mode               | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.0  |                    |      |

|                      |                         | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55 |                    |      |

|                      |                         | f <sub>CPU</sub> = f <sub>MASTER</sub> = 128 kHz            | LSI RC osc. (128 kHz)                 | 0.5  |                    |      |

#### Table 22. Total current consumption in wait mode at $V_{DD}$ = 5 V

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

| Symbol                                | Parameter  | Conditions                                                  |                                       |      | Max <sup>(1)</sup> | Unit |

|---------------------------------------|------------|-------------------------------------------------------------|---------------------------------------|------|--------------------|------|

|                                       |            | f <sub>CPU</sub> = f <sub>MASTER</sub> = 24 MHz,            | HSE crystal osc. (24 MHz)             | 2.0  |                    |      |

|                                       |            | $T_A \leq 105 \ ^{\circ}C$                                  | HSE user ext. clock (24 MHz)          | 1.8  | 4.7                |      |

|                                       |            |                                                             | HSE crystal osc. (16 MHz)             | 1.6  |                    |      |

|                                       | Supply     | f <sub>CPU</sub> = f <sub>MASTER</sub> = 16 MHz             | HSE user ext. clock (16 MHz)          | 1.4  | 4.4                | mA   |

| I <sub>DD(WFI)</sub>                  | current in |                                                             | HSI RC osc. (16 MHz)                  | 1.2  | 1.6                |      |

| , , , , , , , , , , , , , , , , , , , | wait mode  | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 125 kHz       | HSI RC osc. (16 MHz)                  | 1.0  |                    |      |

|                                       |            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | HSI RC osc. (16 MHz/8) <sup>(2)</sup> | 0.55 |                    |      |

|                                       |            | f <sub>CPU</sub> = f <sub>MASTER</sub> /128 = 15.625<br>kHz | LSI RC osc. (128 kHz)                 | 0.5  |                    |      |

1. Data based on characterization results, not tested in production.

2. Default clock configuration measured with all peripherals off.

| Symbol                              | Parameter                                   | Conditions                              | Min | Тур | Мах                                            | Unit |  |

|-------------------------------------|---------------------------------------------|-----------------------------------------|-----|-----|------------------------------------------------|------|--|

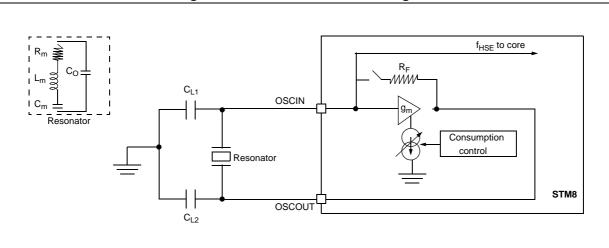

| f <sub>HSE</sub>                    | External high speed oscillator<br>frequency |                                         | 1   |     | 24                                             | MHz  |  |

| R <sub>F</sub>                      | Feedback resistor                           |                                         |     | 220 |                                                | kΩ   |  |

| C <sup>(1)</sup>                    | Recommended load capacitance (2)            |                                         |     |     | 20                                             | pF   |  |

| I <sub>DD(HSE)</sub>                | HSE oscillator power consumption            | C = 20 pF,<br>f <sub>OSC</sub> = 24 MHz |     |     | 6 (startup)<br>2 (stabilized) <sup>(3)</sup>   | mA   |  |

|                                     |                                             | C = 10 pF,<br>f <sub>OSC</sub> = 24 MHz |     |     | 6 (startup)<br>1.5 (stabilized) <sup>(3)</sup> | ША   |  |

| 9 <sub>m</sub>                      | Oscillator transconductance                 |                                         | 5   |     |                                                | mA/V |  |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                                | $V_{\text{DD}}$ is stabilized           |     | 1   |                                                | ms   |  |

1. C is approximately equivalent to 2 x crystal Cload.

2. The oscillator selection can be optimized in terms of supply current using a high quality resonator with small R<sub>m</sub> value. Refer to crystal manufacturer for more details

3. Data based on characterization results, not tested in production.

t<sub>SU(HSE)</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 24 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### Figure 17. HSE oscillator circuit diagram

#### HSE oscillator critical g<sub>m</sub> formula

$g_{mcrit} = (2 \times \Pi \times f_{HSE})^2 \times R_m (2Co + C)^2$

$\begin{array}{l} {\sf R}_m: \mbox{ Notional resistance (see crystal specification)} \\ {\sf L}_m: \mbox{ Notional inductance (see crystal specification)} \\ {\sf C}_m: \mbox{ Notional capacitance (see crystal specification)} \\ {\sf Co: Shunt capacitance (see crystal specification)} \\ {\sf C}_{L1} = {\sf C}_{L2} = {\sf C}: \mbox{ Grounded external capacitance } \\ {\sf g}_m >> {\sf g}_{mcrit} \end{array}$

DocID14733 Rev 13

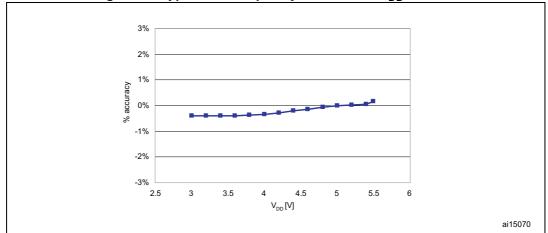

## Low speed internal RC oscillator (LSI)

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}.$

| Symbol               | Parameter                        | Conditions | Min | Тур | Max              | Unit |

|----------------------|----------------------------------|------------|-----|-----|------------------|------|

| f <sub>LSI</sub>     | Frequency                        |            | 110 | 128 | 146              | kHz  |

| t <sub>su(LSI)</sub> | LSI oscillator wakeup time       |            |     |     | 7 <sup>(1)</sup> | μs   |

| I <sub>DD(LSI)</sub> | LSI oscillator power consumption |            |     | 5   |                  | μA   |

1. Guaranteed by design, not tested in production.

## Figure 19. Typical LSI frequency variation vs $V_{DD}$ @ 25 °C

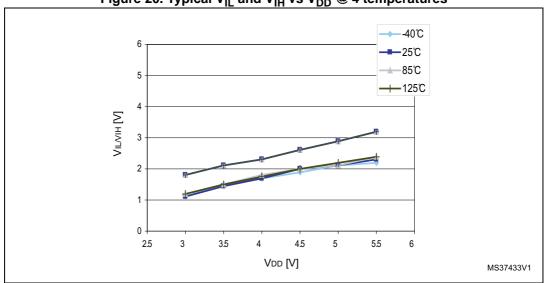

Figure 20. Typical  $V_{IL}$  and  $V_{IH}$  vs  $V_{DD} @$  4 temperatures

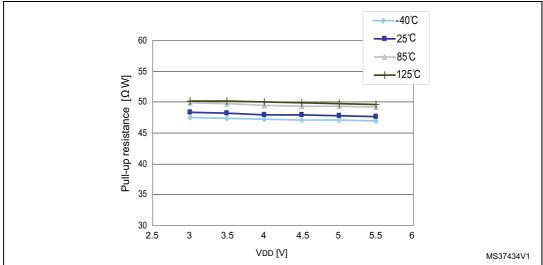

Figure 21. Typical pull-up resistance vs V<sub>DD</sub> @ 4 temperatures

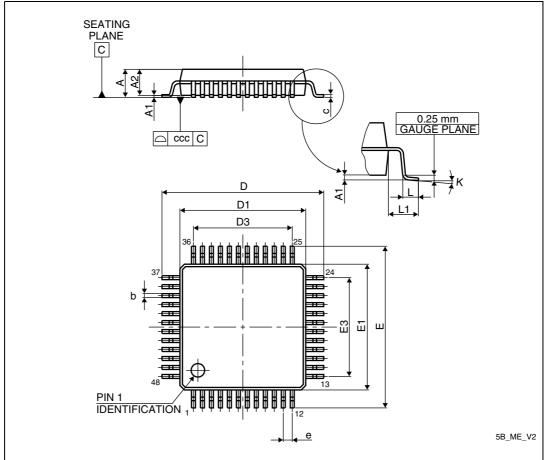

## 11.1.3 LQFP48 package information

Figure 50. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

Table 54. LQFP48 - 48-pin, 7x 7 mm low-profile quad flat package mechanical

| Symbol | mm    |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------|-------|-----------------------|--------|--------|--|

|        | Min   | Тур   | Max   | Min                   | Тур    | Max    |  |

| A      | -     | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050 | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170 | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| с      | 0.090 | -     | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | 8.800 | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

| D1     | 6.800 | 7.000 | 7.200 | 0.2677                | 0.2756 | 0.2835 |  |

| D3     | -     | 5.500 | -     | -                     | 0.2165 | -      |  |

| E      | 8.800 | 9.000 | 9.200 | 0.3465                | 0.3543 | 0.3622 |  |

## 12.2 Software tools

STM8 development tools are supported by a complete, free software package from STMicroelectronics that includes ST Visual Develop (STVD) IDE and the ST Visual Programmer (STVP) software interface. STVD provides seamless integration of the Cosmic and Raisonance C compilers for STM8. A free version that outputs up to 32 Kbytes of code is available.

## 12.2.1 STM8 toolset

**STM8** toolset with STVD integrated development environment and STVP programming software is available for free download at <u>www.st.com/mcu</u>. This package includes:

ST Visual Develop - Full-featured integrated development environment from ST, featuring

- Seamless integration of C and ASM toolsets

- Full-featured debugger

- Project management

- Syntax highlighting editor

- Integrated programming interface

- Support of advanced emulation features for STice such as code profiling and coverage

**ST Visual Programmer (STVP)** – Easy-to-use, unlimited graphical interface allowing read, write and verification of the STM8 microcontroller Flash program memory, data EEPROM and option bytes. STVP also offers project mode for saving programming configurations and automating programming sequences.

## 12.2.2 C and assembly toolchains

Control of C and assembly toolchains is seamlessly integrated into the STVD integrated development environment, making it possible to configure and control the building of the application directly from an easy-to-use graphical interface.

Available toolchains include:

- Cosmic C compiler for STM8 One free version that outputs up to 32 Kbytes of code is available. For more information, see www.cosmic-software.com.

- Raisonance C compiler for STM8 One free version that outputs up to 32 Kbytes of code. For more information, see www.raisonance.com.

- **STM8 assembler linker** Free assembly toolchain included in the STVD toolset, which allows you to assemble and link the application source code.

## 12.3 Programming tools

During the development cycle, STice provides in-circuit programming of the STM8 Flash microcontroller on the application board via the SWIM protocol. Additional tools are to include a low-cost in-circuit programmer as well as ST socket boards, which provide dedicated programming platforms with sockets for programming the STM8.

For production environments, programmers will include a complete range of gang and automated programming solutions from third-party tool developers already supplying programmers for the STM8 family.

| Date        | Revision    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10-Jul-2009 | 8<br>cont'd | Section 10: Electrical characteristics: Added data for TBD values;<br>updated Table 15: Voltage characteristics and Table 18: General<br>operating conditions; updated VCAP specifications in Table 18 and<br>in Section 10.3.1: VCAP external capacitor, updated Figure 18;<br>replaced Figure 19; updated Table 35: RAM and hardware registers;<br>updated Figure 22 and Figure 35; added Figure 40: Typical<br>application with I2C bus and timing diagram.<br>Removed Table 56: Junction temperature range.<br>Added link between ordering information Figure 59 and STM8S20xx<br>features Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 13-Apr-2010 | 9           | Document status changed from "preliminary data" to "datasheet".<br><i>Table 2: STM8S20xxx performance line features</i> : high sink I/O for<br>STM8S207C8 is 16 (not 13).<br><i>Table 3: Peripheral clock gating bit assignments in</i><br><i>CLK_PCKENR1/2 registers</i> : updated bit positions for TIM2 and<br>TIM3.<br><i>Figure 5: LQFP 48-pin pinout</i> : added CAN_TX and CAN_RX to pins<br>35 and 36; noted that these pins are available only in STM8S208xx<br>devices.<br><i>Figure 7: LQFP 32-pin pinout</i> : replaced uart2 with uart3.<br><i>Table 6: Pin description</i> : added footnotes concerning beCAN<br>availability and UART1_RX and UART3_RX pins.<br><i>Table 13: Option byte description</i> : added description of STM8L<br>bootloader option bytes to the option byte description table.<br>Added <i>Section 9: Unique ID</i> (and listed this attribute in <i>Features</i> ).<br><i>Section 10.3: Operating conditions</i> : replaced "C <sub>EXT</sub> " with "VCAP"<br>and added data for ESR and ESL; removed "low power dissipation"<br>condition for T <sub>A</sub> .<br><i>Table 26: Total current consumption in halt mode at VDD = 5 V</i> :<br>replaced max value of I <sub>DD(H)</sub> at 85 °C from 30 µA to 35 µA for the<br>condition "Flash in power-down mode, HSI clock after wakeup".<br><i>Table 33: HSI oscillator characteristics</i> : updated the ACC <sub>HSI</sub> factory<br>calibrated values.<br><i>Functional EMS (electromagnetic susceptibility)</i> and <i>Table 47</i> :<br>replaced "IEC 1000" with "IEC 61000".<br><i>Electromagnetic interference (EMI)</i> and <i>Table 48</i> : replaced "SAE<br>J1752/3" with "IEC 61967-2".<br><i>Table 57: Thermal characteristics</i> : changed the thermal resistance<br>junction-ambient value of LQFP32 (7x7 mm) from 59 °C/W to 60<br>°C/W. |  |  |

Table 58. Document revision history (continued)

| Date           | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-Sep-2010    | 10       | Added part number STM8S208M8 to <i>Table 1: Device summary</i> .<br>Updated "reset state" of <i>Table 5: Legend/abbreviations for pinout</i><br><i>table</i> .<br>Added footnote <i>4</i> to <i>Table 6: Pin description</i> .<br><i>Table 9: General hardware register map</i> : standardized all reset state<br>values; updated the reset state values of RST_SR, CLK_SWCR,<br>CLK_HSITRIMR, CLK_SWIMCCR, IWDG_KR, and ADC_DRx<br>registers; added the reset values of the CAN paged registers.<br><i>Figure 36: Recommended reset pin protection</i> : replaced 0.01 μF with<br>0.1 μF.<br><i>Figure 40: Typical application with I2C bus and timing diagram</i> :<br>t <sub>w</sub> (SCKH), t <sub>w</sub> (SCKL), t <sub>r</sub> (SCK), and t <sub>f</sub> (SCK) replaced by t <sub>w</sub> (SCLH), t <sub>w</sub> (SCLL),<br>t <sub>r</sub> (SCL), and t <sub>f</sub> (SCL) respectively. |

| 22-Mar-2011    | 11       | Table 1: Device summary: added STM8S207K8.         Table 2: STM8S20xxx performance line features: added         STM8S207K8 device and changed the RAM value of all other         devices to 6 Kbytes.         Figure 5, Figure 4, Figure 5, and Figure 7: removed TIM1_CH4 from         pins 80, 64, 48, and 32 respectively.         Table 6: Pin description: updated note 3 and added note 5.         Table 9: General hardware register map: removed I2C_PECR         register.         Section 10.3.7: Reset pin characteristics: added text regarding the         rest network.                                                                                                                                                                                                                                                                                                           |

| 10-Feb-2012 12 |          | <i>Figure 1: STM8S20xxx block diagram</i> : updated POR/PDR and BOR;<br>updated LINUART input; added legend.<br><i>Table 18: General operating conditions</i> : updated V <sub>CAP</sub> .<br><i>Table 26: Total current consumption in halt mode at VDD = 5 V</i> :<br>updated title, modified existing max column, and added new max<br>column (at 125 °C) with data.<br><i>Table 37: I/O static characteristics</i> : added new condition and new<br>max values for rise and fall time; added footnote <i>3</i> ; updated Typ and<br>max pull-up resistor values.<br><i>Section 10.3.7: Reset pin characteristics</i> : updated cross reference in<br>text below <i>Figure 35</i><br><i>Table 41: NRST pin characteristics</i> : updated Typ and max values of<br>the NRST pull-up resistor.                                                                                                 |