#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | STM8                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 24MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART               |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 1.5K x 8                                                              |

| RAM Size                   | 6K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.95V ~ 5.5V                                                          |

| Data Converters            | A/D 9x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | 44-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm8s208s6t3c |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device     | Pin count | Max. number of GPIOs<br>(I/O) | Ext. interrupt pins | Timer CAPCOM channels | Timer complementary outputs | A/D converter channels | High sink I/Os | High density Flash program memory<br>(bytes) | Data EEPROM<br>(bytes | RAM (bytes) | beCAN interface |

|------------|-----------|-------------------------------|---------------------|-----------------------|-----------------------------|------------------------|----------------|----------------------------------------------|-----------------------|-------------|-----------------|

| STM8S207MB | 80        | 68                            | 37                  | 9                     | 3                           | 16                     | 18             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S207M8 | 80        | 68                            | 37                  | 9                     | 3                           | 16                     | 18             | 64 K                                         | 2048                  | 6 K         |                 |

| STM8S207RB | 64        | 52                            | 36                  | 9                     | 3                           | 16                     | 16             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S207R8 | 64        | 52                            | 36                  | 9                     | 3                           | 16                     | 16             | 64 K                                         | 1536                  | 6 K         |                 |

| STM8S207R6 | 64        | 52                            | 36                  | 9                     | 3                           | 16                     | 16             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S207CB | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S207C8 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 64 K                                         | 1536                  | 6 K         | No              |

| STM8S207C6 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S207SB | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 128 K                                        | 1536                  | 6 K         |                 |

| STM8S207S8 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 64 K                                         | 1536                  | 6 K         |                 |

| STM8S207S6 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S207K8 | 32        | 25                            | 23                  | 8                     | 3                           | 7                      | 12             | 64 K                                         | 1024                  | 6 K         |                 |

| STM8S207K6 | 32        | 25                            | 23                  | 8                     | 3                           | 7                      | 12             | 32 K                                         | 1024                  | 6 K         |                 |

| STM8S208MB | 80        | 68                            | 37                  | 9                     | 3                           | 16                     | 18             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S208RB | 64        | 52                            | 37                  | 9                     | 3                           | 16                     | 16             | 128 K                                        | 2048                  | 6 K         |                 |

| STM8S208R8 | 64        | 52                            | 37                  | 9                     | 3                           | 16                     | 16             | 64 K                                         | 2048                  | 6 K         |                 |

| STM8S208R6 | 64        | 52                            | 37                  | 9                     | 3                           | 16                     | 16             | 32 K                                         | 2048                  | 6 K         |                 |

| STM8S208CB | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 128 K                                        | 2048                  | 6 K         | Vee             |

| STM8S208C8 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 64 K                                         | 2048                  | 6 K         | Yes             |

| STM8S208C6 | 48        | 38                            | 35                  | 9                     | 3                           | 10                     | 16             | 32 K                                         | 2048                  | 6 K         |                 |

| STM8S208SB | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 128 K                                        | 1536                  | 6 K         |                 |

| STM8S208S8 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 64 K                                         | 1536                  | 6 K         |                 |

| STM8S208S6 | 44        | 34                            | 31                  | 8                     | 3                           | 9                      | 15             | 32 K                                         | 1536                  | 6 K         |                 |

Table 2. STM8S20xxx performance line features

| Address                   | Block              | Register Label | Register Name                          | Reset               |

|---------------------------|--------------------|----------------|----------------------------------------|---------------------|

| 0.00.7500                 |                    | _              | _                                      | Status              |

| 0x00 7F00                 |                    | A              | Accumulator                            | 0x00                |

| 0x00 7F01                 |                    | PCE            | Program counter extended               | 0x00                |

| 0x00 7F02                 |                    | PCH            | Program counter high                   | 0x00                |

| 0x00 7F03                 |                    | PCL            | Program counter low                    | 0x00                |

| 0x00 7F04                 |                    | XH             | X index register high                  | 0x00                |

| 0x00 7F05                 | CPU <sup>(1)</sup> | XL             | X index register low                   | 0x00                |

| 0x00 7F06                 |                    | YH             | Y index register high                  | 0x00                |

| 0x00 7F07                 |                    | YL             | Y index register low                   | 0x00                |

| 0x00 7F08                 |                    | SPH            | Stack pointer high                     | 0x17 <sup>(2)</sup> |

| 0x00 7F09                 |                    | SPL            | Stack pointer low                      | 0xFF                |

| 0x00 7F0A                 |                    | CCR            | Condition code register                | 0x28                |

| 0x00 7F0B to<br>0x00 7F5F |                    |                | Reserved area (85 bytes)               |                     |

| 0x00 7F60                 | CPU                | CFG_GCR        | Global configuration register          | 0x00                |

| 0x00 7F70                 |                    | ITC_SPR1       | Interrupt software priority register 1 | 0xFF                |

| 0x00 7F71                 |                    | ITC_SPR2       | Interrupt software priority register 2 | 0xFF                |

| 0x00 7F72                 |                    | ITC_SPR3       | Interrupt software priority register 3 | 0xFF                |

| 0x00 7F73                 | ITO                | ITC_SPR4       | Interrupt software priority register 4 | 0xFF                |

| 0x00 7F74                 | ITC                | ITC_SPR5       | Interrupt software priority register 5 | 0xFF                |

| 0x00 7F75                 |                    | ITC_SPR6       | Interrupt software priority register 6 | 0xFF                |

| 0x00 7F76                 |                    | ITC_SPR7       | Interrupt software priority register 7 | 0xFF                |

| 0x00 7F77                 |                    | ITC_SPR8       | Interrupt software priority register 8 | 0xFF                |

| 0x00 7F78 to<br>0x00 7F79 |                    |                | Reserved area (2 bytes)                |                     |

| 0x00 7F80                 | SWIM               | SWIM_CSR       | SWIM control status register           | 0x00                |

| 0x00 7F81 to<br>0x00 7F8F |                    |                | Reserved area (15 bytes)               |                     |

| 0x00 7F90                 |                    | DM_BK1RE       | DM breakpoint 1 register extended byte | 0xFF                |

| 0x00 7F91                 |                    | DM_BK1RH       | DM breakpoint 1 register high byte     | 0xFF                |

| 0x00 7F92                 |                    | DM_BK1RL       | DM breakpoint 1 register low byte      | 0xFF                |

| 0x00 7F93                 |                    | DM_BK2RE       | DM breakpoint 2 register extended byte | 0xFF                |

| 0x00 7F94                 | DM                 | DM_BK2RH       | DM breakpoint 2 register high byte     | 0xFF                |

| 0x00 7F95                 |                    | DM_BK2RL       | DM breakpoint 2 register low byte      | 0xFF                |

| 0x00 7F96                 |                    | DM_CR1         | DM debug module control register 1     | 0x00                |

|                           |                    | DM_CR2         | DM debug module control register 2     | -                   |

# Table 10. CPU/SWIM/debug module/interrupt controller registers

|                           |       | J              |                                           |      |

|---------------------------|-------|----------------|-------------------------------------------|------|

| Address                   | Block | Register Label | Label Register Name                       |      |

| 0x00 7F98                 |       | DM_CSR1        | DM debug module control/status register 1 | 0x10 |

| 0x00 7F99                 | DM    | DM_CSR2        | DM debug module control/status register 2 | 0x00 |

| 0x00 7F9A                 |       | DM_ENFCTR      | DM enable function register               | 0xFF |

| 0x00 7F9B to<br>0x00 7F9F |       |                | Reserved area (5 bytes)                   |      |

#### Table 10. CPU/SWIM/debug module/interrupt controller registers (continued)

1. Accessible by debug module only

2. Product dependent value, see Figure 8: Memory map.

7 Interrupt vector mapping

|            | Table 11. Interrupt mapping |                                                  |                          |                                 |                           |  |  |  |  |

|------------|-----------------------------|--------------------------------------------------|--------------------------|---------------------------------|---------------------------|--|--|--|--|

| IRQ<br>no. | Source<br>block             | Description                                      | Wakeup from<br>Halt mode | Wakeup from<br>Active-halt mode | Vector address            |  |  |  |  |

|            | RESET                       | Reset                                            | Yes                      | Yes                             | 0x00 8000                 |  |  |  |  |

|            | TRAP                        | Software interrupt                               | -                        | -                               | 0x00 8004                 |  |  |  |  |

| 0          | TLI                         | External top level interrupt                     | -                        | -                               | 0x00 8008                 |  |  |  |  |

| 1          | AWU                         | Auto wake up from halt                           | -                        | Yes                             | 0x00 800C                 |  |  |  |  |

| 2          | CLK                         | Clock controller                                 | -                        | -                               | 0x00 8010                 |  |  |  |  |

| 3          | EXTI0                       | Port A external interrupts                       | Yes <sup>(1)</sup>       | Yes <sup>(1)</sup>              | 0x00 8014                 |  |  |  |  |

| 4          | EXTI1                       | Port B external interrupts                       | Yes                      | Yes                             | 0x00 8018                 |  |  |  |  |

| 5          | EXTI2                       | Port C external interrupts                       | Yes                      | Yes                             | 0x00 801C                 |  |  |  |  |

| 6          | EXTI3                       | Port D external interrupts                       | Yes                      | Yes                             | 0x00 8020                 |  |  |  |  |

| 7          | EXTI4                       | Port E external interrupts                       | Yes                      | Yes                             | 0x00 8024                 |  |  |  |  |

| 8          | beCAN                       | beCAN RX interrupt                               | Yes                      | Yes                             | 0x00 8028                 |  |  |  |  |

| 9          | beCAN                       | beCAN TX/ER/SC interrupt                         | -                        | -                               | 0x00 802C                 |  |  |  |  |

| 10         | SPI                         | End of transfer                                  | Yes                      | Yes                             | 0x00 8030                 |  |  |  |  |

| 11         | TIM1                        | TIM1 update/overflow/underflow/<br>trigger/break | -                        | -                               | 0x00 8034                 |  |  |  |  |

| 12         | TIM1                        | TIM1 capture/compare                             | -                        | -                               | 0x00 8038                 |  |  |  |  |

| 13         | TIM2                        | TIM2 update /overflow                            | -                        | -                               | 0x00 803C                 |  |  |  |  |

| 14         | TIM2                        | TIM2 capture/compare                             | -                        | -                               | 0x00 8040                 |  |  |  |  |

| 15         | TIM3                        | Update/overflow                                  | -                        | -                               | 0x00 8044                 |  |  |  |  |

| 16         | TIM3                        | Capture/compare                                  | -                        | -                               | 0x00 8048                 |  |  |  |  |

| 17         | UART1                       | Tx complete                                      | -                        | -                               | 0x00 804C                 |  |  |  |  |

| 18         | UART1                       | Receive register DATA FULL                       | -                        | -                               | 0x00 8050                 |  |  |  |  |

| 19         | l <sup>2</sup> C            | I <sup>2</sup> C interrupt                       | Yes                      | Yes                             | 0x00 8054                 |  |  |  |  |

| 20         | UART3                       | Tx complete                                      | -                        | -                               | 0x00 8058                 |  |  |  |  |

| 21         | UART3                       | Receive register DATA FULL                       | -                        | -                               | 0x00 805C                 |  |  |  |  |

| 22         | ADC2                        | ADC2 end of conversion                           | -                        | -                               | 0x00 8060                 |  |  |  |  |

| 23         | TIM4                        | TIM4 update/overflow                             | -                        | -                               | 0x00 8064                 |  |  |  |  |

| 24         | Flash                       | EOP/WR_PG_DIS                                    | -                        | -                               | 0x00 8068                 |  |  |  |  |

|            |                             | Reserved                                         |                          |                                 | 0x00 806C to<br>0x00 807C |  |  |  |  |

## Table 11. Interrupt mapping

1. Except PA1

# 9 Unique ID

The devices feature a 96-bit unique device identifier which provides a reference number that is unique for any device and in any context. The 96 bits of the identifier can never be altered by the user.

The unique device identifier can be read in single bytes and may then be concatenated using a custom algorithm.

The unique device identifier is ideally suited:

- For use as serial numbers

- For use as security keys to increase the code security in the program memory while using and combining this unique ID with software cryptographic primitives and protocols before programming the internal memory.

- To activate secure boot processes

| Address | Content                       | Unique ID bits |             |   |    |           |   |   |   |

|---------|-------------------------------|----------------|-------------|---|----|-----------|---|---|---|

| Address | description                   | 7              | 6           | 5 | 4  | 3         | 2 | 1 | 0 |

| 0x48CD  | X co-ordinate on the<br>wafer |                |             |   | U  | _ID[7:0]  |   |   |   |

| 0x48CE  |                               |                |             |   | U_ | _ID[15:8] |   |   |   |

| 0x48CF  | Y co-ordinate on the          |                |             |   | U_ | ID[23:16] |   |   |   |

| 0x48D0  | wafer                         |                | U_ID[31:24] |   |    |           |   |   |   |

| 0x48D1  | Wafer number                  |                | U_ID[39:32] |   |    |           |   |   |   |

| 0x48D2  |                               |                | U_ID[47:40] |   |    |           |   |   |   |

| 0x48D3  |                               | U_ID[55:48]    |             |   |    |           |   |   |   |

| 0x48D4  |                               |                |             |   | U_ | ID[63:56] |   |   |   |

| 0x48D5  | Lot number                    |                |             |   | U_ | ID[71:64] |   |   |   |

| 0x48D6  |                               | U_ID[79:72]    |             |   |    |           |   |   |   |

| 0x48D7  |                               |                |             |   | U_ | ID[87:80] |   |   |   |

| 0x48D8  |                               | U_ID[95:88]    |             |   |    |           |   |   |   |

#### Table 14. Unique ID registers (96 bits)

| Symbol                                  | Ratings                                                                                                      | Max. <sup>(1)</sup> | Unit |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------|------|--|--|

| I <sub>VDD</sub>                        | Total current into V <sub>DD</sub> power lines (source) <sup>(2)</sup>                                       | 60                  |      |  |  |

| I <sub>VSS</sub>                        | Total current out of $V_{SS}$ ground lines (sink) <sup>(2)</sup>                                             | 60                  |      |  |  |

| 1                                       | Output current sunk by any I/O and control pin                                                               |                     |      |  |  |

| I <sub>IO</sub>                         | Output current source by any I/Os and control pin                                                            | 20                  |      |  |  |

| ΣΙ <sub>ΙΟ</sub>                        | Total output current sourced (sum of all I/O and control pins) for devices with two $V_{DDIO}\rm pins^{(3)}$ | 200                 |      |  |  |

|                                         | Total output current sourced (sum of all I/O and control pins) for devices with one $V_{DDIO}\rm{pin}^{(3)}$ | 100                 | mA   |  |  |

|                                         | Total output current sunk (sum of all I/O and control pins) for devices with two $\rm V_{SSIO}\ pins^{(3)}$  | 160                 | IIIA |  |  |

|                                         | Total output current sunk (sum of all I/O and control pins) for devices with one $V_{SSIO}\text{pin}^{(3)}$  | 80                  |      |  |  |

|                                         | Injected current on NRST pin                                                                                 | ±4                  |      |  |  |

| I <sub>INJ(PIN)</sub> <sup>(4)(5)</sup> | Injected current on OSCIN pin                                                                                | ±4                  |      |  |  |

|                                         | Injected current on any other pin <sup>(6)</sup>                                                             | ±4                  |      |  |  |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$         | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>                                      | ±20                 |      |  |  |

#### Table 16. Current characteristics

1. Data based on characterization results, not tested in production.

- 2. All power (V<sub>DD</sub>, V<sub>DDIO</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSIO</sub>, V<sub>SSA</sub>) pins must always be connected to the external supply.

- 3. I/O pins used simultaneously for high current source/sink must be uniformly spaced around the package between the  $V_{DDIO}/V_{SSIO}$  pins.

- 4. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

- 5. Negative injection disturbs the analog performance of the device. See note in Section 10.3.10: 10-bit ADC characteristics on page 85.

- 6. When several inputs are submitted to a current injection, the maximum Σl<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with Σl<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

| Symbol           | Ratings                      | Value      | Unit |

|------------------|------------------------------|------------|------|

| T <sub>STG</sub> | Storage temperature range    | -65 to 150 | °C   |

| TJ               | Maximum junction temperature | 150        | 0    |

#### Table 17. Thermal characteristics

# 10.3 Operating conditions

The device must be used in operating conditions that respect the parameters in *Table 18*. In addition, full account must be taken of all physical capacitor characteristics and tolerances.

| Symbol                          | Parameter                                              | Conditions                                                                                                                                          | Min  | Max                | Unit |

|---------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| f <sub>CPU</sub>                | Internal CPU clock frequency                           | $T_A \le 105 \ ^{\circ}C$                                                                                                                           | 0    | 24                 | MHz  |

| 'CPU                            | Internal OF O clock frequency                          |                                                                                                                                                     | 0    | 16                 | MHz  |

| $V_{DD/}V_{DD_{IO}}$            | Standard operating voltage                             |                                                                                                                                                     | 2.95 | 5.5                | V    |

|                                 | C <sub>EXT</sub> : capacitance of external capacitor   |                                                                                                                                                     | 470  | 3300               | nF   |

| V <sub>CAP</sub> <sup>(1)</sup> | ESR of external capacitor                              | at 1 MHz <sup>(2)</sup>                                                                                                                             | -    | 0.3                | Ω    |

|                                 | ESL of external capacitor                              |                                                                                                                                                     | -    | 15                 | nH   |

| Pp <sup>(3)</sup>               | Power dissipation at $T_A = 85^{\circ}$ C for suffix 6 | 44, 48, 64, and 80-pin<br>devices, with output on 8<br>standard ports, 2 high sink<br>ports and 2 open drain ports<br>simultaneously <sup>(4)</sup> |      | 443                | mW   |

|                                 | or $T_A = 125^\circ$ C for suffix 3                    |                                                                                                                                                     | 360  |                    |      |

| T <sub>A</sub>                  | Ambient temperature for 6 suffix version               | Maximum power dissipation                                                                                                                           | -40  | 85                 |      |

| 'A                              | Ambient temperature for 3 suffix version               | Maximum power dissipation                                                                                                                           | -40  | 125                | °C   |

| ТJ                              | Junction temperature range                             | 6 suffix version                                                                                                                                    | -40  | 105                |      |

| ١J                              | Survey of temperature range                            | 3 suffix version                                                                                                                                    | -40  | 130 <sup>(5)</sup> |      |

|  | Table 18. | General | operating | conditions |

|--|-----------|---------|-----------|------------|

|--|-----------|---------|-----------|------------|

1. Care should be taken when selecting the capacitor, due to its tolerance, as well as the parameter dependency on temperature, DC bias and frequency in addition to other factors. The parameter maximum value must be respected for the full application range.

2. This frequency of 1 MHz as a condition for  $V_{CAP}$  parameters is given by design of internal regulator.

To calculate P<sub>Dmax</sub>(T<sub>A</sub>), use the formula P<sub>Dmax</sub> = (T<sub>Jmax</sub> - T<sub>A</sub>)/Θ<sub>JA</sub> (see Section 11.2: Thermal characteristics on page 108) with the value for T<sub>Jmax</sub> given in Table 18 above and the value for Θ<sub>JA</sub> given in Table 57: Thermal characteristics.

4. Refer to Section 11.2: Thermal characteristics on page 108 for the calculation method.

5. T<sub>Jmax</sub> is given by the test limit. Above this value the product behavior is not guaranteed.

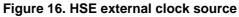

# **10.3.3** External clock sources and timing characteristics

## HSE user external clock

Subject to general operating conditions for  $V_{DD}$  and  $T_A$ .

| Table 31. HSE us | ser external clock | characteristics |

|------------------|--------------------|-----------------|

|------------------|--------------------|-----------------|

| Symbol                           | Parameter                               | Conditions                 | Min                   | Тур | Max                     | Unit |

|----------------------------------|-----------------------------------------|----------------------------|-----------------------|-----|-------------------------|------|

| f <sub>HSE_ext</sub>             | User external clock source<br>frequency |                            | 0                     |     | 24                      | MHz  |

| V <sub>HSEH</sub> <sup>(1)</sup> | OSCIN input pin high level voltage      |                            | 0.7 x V <sub>DD</sub> |     | V <sub>DD</sub> + 0.3 V | V    |

| V <sub>HSEL</sub> <sup>(1)</sup> | OSCIN input pin low level voltage       |                            | V <sub>SS</sub>       |     | 0.3 x V <sub>DD</sub>   | V    |

| I <sub>LEAK_HSE</sub>            | OSCIN input leakage<br>current          | $V_{SS} < V_{IN} < V_{DD}$ | -1                    |     | 1                       | μA   |

1. Data based on characterization results, not tested in production.

## HSE crystal/ceramic resonator oscillator

The HSE clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal resonator manufacturer for more details (frequency, package, accuracy...).

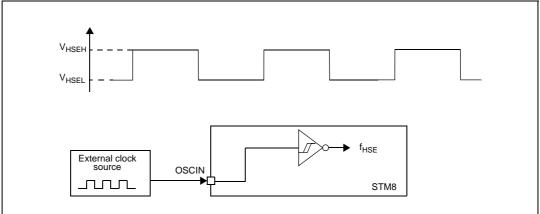

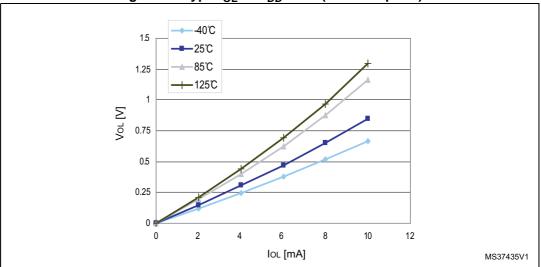

## **Typical output level curves**

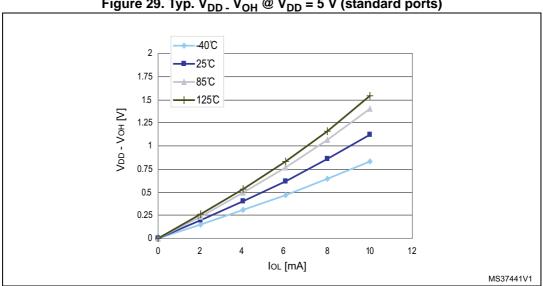

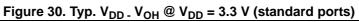

*Figure 24* to *Figure 31* show typical output level curves measured with output on a single pin.

# Figure 24. Typ. $V_{OL} @ V_{DD} = 3.3 V$ (standard ports)

Figure 29. Typ.  $V_{DD}$  V<sub>OH</sub> @  $V_{DD}$  = 5 V (standard ports)

# 10.3.7 Reset pin characteristics

Subject to general operating conditions for  $V_{\text{DD}}$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                                    | Conditions             | Min                         | <b>Typ</b> <sup>1)</sup> | Max                   | Unit |  |

|-------------------------|----------------------------------------------|------------------------|-----------------------------|--------------------------|-----------------------|------|--|

| V <sub>IL(NRST)</sub>   | NRST Input low level voltage <sup>(1)</sup>  |                        | -0.3 V                      |                          | 0.3 x V <sub>DD</sub> |      |  |

| V <sub>IH(NRST)</sub>   | NRST Input high level voltage <sup>(1)</sup> |                        | $0.7 	ext{ x V}_{	ext{DD}}$ |                          | V <sub>DD</sub> + 0.3 | V    |  |

| V <sub>OL(NRST)</sub>   | NRST Output low level voltage (1)            | I <sub>OL</sub> = 2 mA |                             |                          | 0.5                   |      |  |

| R <sub>PU(NRST)</sub>   | NRST Pull-up resistor <sup>(2)</sup>         |                        | 30                          | 55                       | 80                    | kΩ   |  |

| t <sub>IFP(NRST)</sub>  | NRST Input filtered pulse <sup>(3)</sup>     |                        |                             |                          | 75                    | ns   |  |

| t <sub>INFP(NRST)</sub> | NRST Input not filtered pulse <sup>(3)</sup> |                        | 500                         |                          |                       | ns   |  |

| t <sub>OP(NRST)</sub>   | NRST output pulse <sup>(1)</sup>             |                        | 15                          |                          |                       | μs   |  |

| Table 41. | NRST | pin  | characteristics  |

|-----------|------|------|------------------|

|           |      | PIII | character istics |

1. Data based on characterization results, not tested in production.

2. The  $\rm R_{\rm PU}$  pull-up equivalent resistor is based on a resistive transistor

3. Data guaranteed by design, not tested in production.

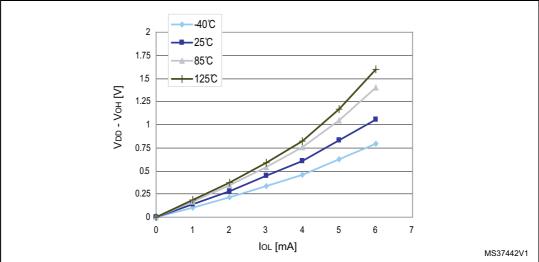

# Figure 33. Typical NRST $\rm V_{IL}$ and $\rm V_{IH}$ vs $\rm V_{DD}$ @ 4 temperatures

# 10.3.8 SPI serial peripheral interface

Unless otherwise specified, the parameters given in *Table 42* are derived from tests performed under ambient temperature,  $f_{MASTER}$  frequency and  $V_{DD}$  supply voltage conditions.  $t_{MASTER} = 1/f_{MASTER}$ .

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                               | Parameter                    | Conditions                      | Min                      | Max                      | Unit   |

|------------------------------------------------------|------------------------------|---------------------------------|--------------------------|--------------------------|--------|

| f <sub>SCK</sub>                                     |                              | Master mode                     | 0                        | 10                       | MHz    |

| 1/t <sub>c(SCK)</sub>                                | SPI clock frequency          | Slave mode                      | 0                        | 6                        | IVITIZ |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>           | SPI clock rise and fall time | Capacitive load: C = 30 pF      |                          | 25                       |        |

| t <sub>su(NSS)</sub> <sup>(1)</sup>                  | NSS setup time               | Slave mode                      | 4 x t <sub>MASTER</sub>  |                          |        |

| t <sub>h(NSS)</sub> <sup>(1)</sup>                   | NSS hold time                | Slave mode                      | 70                       |                          |        |

| t <sub>w(SCKH)</sub> (1)<br>t <sub>w(SCKL)</sub> (1) | SCK high and low time        | Master mode                     | t <sub>SCK</sub> /2 - 15 | t <sub>SCK</sub> /2 + 15 |        |

| t <sub>su(MI)</sub> (1)                              | Data input setup time        | Master mode                     | 5                        |                          |        |

| t <sub>su(SI)</sub> (1)                              |                              | Slave mode                      | 5                        |                          |        |

| t <sub>h(MI)</sub> (1)                               | Data input hold time         | Master mode                     | 7                        |                          | ns     |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1)     |                              | Slave mode                      | 10                       |                          |        |

| t <sub>a(SO)</sub> (1)(2)                            | Data output access time      | Slave mode                      |                          | 3 x t <sub>MASTER</sub>  |        |

| t <sub>dis(SO)</sub> <sup>(1)(3)</sup>               | Data output disable time     | Slave mode                      | 25                       |                          |        |

| t <sub>v(SO)</sub> <sup>(1)</sup>                    | Data output valid time       | Slave mode (after enable edge)  |                          | 75                       |        |

| t <sub>v(MO)</sub> <sup>(1)</sup>                    | Data output valid time       | Master mode (after enable edge) |                          | 30                       |        |

| t <sub>h(SO)</sub> <sup>(1)</sup>                    | Data autaut hald time        | Slave mode (after enable edge)  | 31                       |                          |        |

| t <sub>h(MO)</sub> <sup>(1)</sup>                    | Data output hold time        | Master mode (after enable edge) | 12                       |                          |        |

1. Values based on design simulation and/or characterization results, and not tested in production.

2. Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

3. Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z.

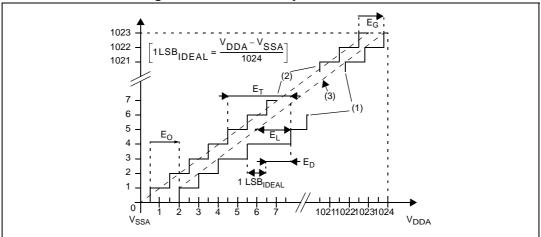

1. Example of an actual transfer curve.

- 2. The ideal transfer curve

- 3.

End point correlation line  $E_T$  = Total unadjusted error: maximum deviation between the actual and the ideal transfer curves.  $E_0$  = Offset error: deviation between the first actual transition and the first ideal one.  $E_G$  = Gain error: deviation between the last ideal transition and the last actual one.  $E_D$  = Differential linearity error: maximum deviation between actual steps and the ideal one.  $E_L$  = Integral linearity error: maximum deviation between any actual transition and the end point correlation between any actual transition and the end point correlation line.

## **Electromagnetic interference (EMI)**

Emission tests conform to the SAE IEC 61967-2 standard for test software, board layout and pin loading.

|                  |            |                                                                                    | Conditions        |                 |                  |                  |      |

|------------------|------------|------------------------------------------------------------------------------------|-------------------|-----------------|------------------|------------------|------|

| Symbol           | Parameter  |                                                                                    | Monitored         | Max             | Unit             |                  |      |

|                  |            | General conditions                                                                 | frequency band    | 8 MHz/<br>8 MHz | 8 MHz/<br>16 MHz | 8 MHz/<br>24 MHz |      |

|                  |            | k level $V_{DD} = 5 V$<br>$T_A = 25 °C$<br>LQFP80 package<br>conforming to SAE IEC | 0.1MHz to 30 MHz  | 15              | 20               | 24               |      |

|                  | Peak level |                                                                                    | 30 MHz to 130 MHz | 18              | 21               | 16               | dBµV |

| S <sub>EMI</sub> |            |                                                                                    | 130 MHz to 1 GHz  | -1              | 1                | 4                |      |

| SAE EMI<br>level |            | 61967-2                                                                            | SAE EMI level     | 2               | 2.5              | 2.5              |      |

1. Data based on characterization results, not tested in production.

## Absolute maximum ratings (electrical sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

### Electrostatic discharge (ESD)

Electrostatic discharges (3 positive then 3 negative pulses separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). This test conforms to the JESD22-A114A/A115A standard. For more details, refer to the application note AN1181.

| Symbol                | Ratings                                               | Conditions                                       | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|--------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (Human body model)    | $T_A = 25^{\circ}C$ , conforming to JESD22-A114  | А     | 2000                            | V    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (Charge device model) | T <sub>A</sub> = 25°C, conforming to JESD22-C101 | IV    | 1000                            | V    |

Table 49. ESD absolute maximum ratings

1. Data based on characterization results, not tested in production.

### Static latch-up

Two complementary static tests are required on 10 parts to assess the latch-up performance:

- A supply overvoltage (applied to each power supply pin)

- A current injection (applied to each input, output and configurable I/O pin) is performed on each sample.

This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

| Symbol           | Parameter             | Conditions              | Class <sup>(1)</sup> |

|------------------|-----------------------|-------------------------|----------------------|

| LU Static latch- |                       | T <sub>A</sub> = 25 °C  | А                    |

|                  | Static latch-up class | $T_A = 85 \ ^{\circ}C$  | А                    |

|                  |                       | T <sub>A</sub> = 125 °C | А                    |

| Table 50. I | Electrical | sensitivities |

|-------------|------------|---------------|

|-------------|------------|---------------|

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to class A it exceeds the JEDEC standard. B class strictly covers all the JEDEC criteria (international standard).

| Table 52. LQFP64 - 64-pin, 14 x 14 mm low-profile quad flat package mechanical |  |

|--------------------------------------------------------------------------------|--|

| data (continued)                                                               |  |

| Symbol |       | mm    |       |       | inches <sup>(1)</sup> |        |

|--------|-------|-------|-------|-------|-----------------------|--------|

|        | Min   | Тур   | Max   | Min   | Тур                   | Max    |

| k      | 0.0 ° | 3.5 ° | 7.0 ° | 0.0 ° | 3.5 °                 | 7.0 °  |

| CCC    |       |       | 0.100 |       |                       | 0.0039 |

1. Values in inches are converted from mm and rounded to four decimal places.

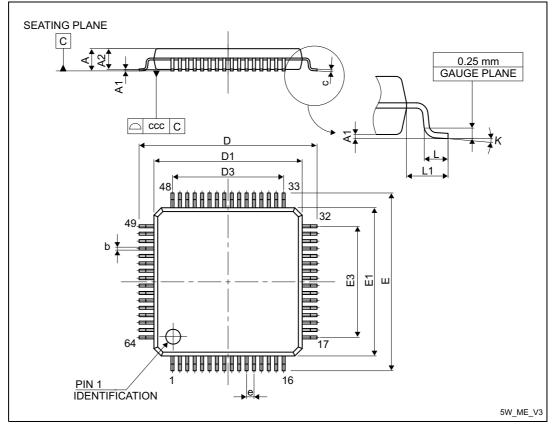

#### Figure 47. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

Table 53. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data

| Gala   |       |       |       |        |                       |        |  |

|--------|-------|-------|-------|--------|-----------------------|--------|--|

| Sympol |       | mm    |       |        | inches <sup>(1)</sup> |        |  |

| Symbol | Min   | Тур   | Max   | Min    | Тур                   | Мах    |  |

| А      | -     | -     | 1.600 | -      | -                     | 0.0630 |  |

| A1     | 0.050 | -     | 0.150 | 0.0020 | -                     | 0.0059 |  |

| A2     | 1.350 | 1.400 | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170 | 0.220 | 0.270 | 0.0067 | 0.0087                | 0.0106 |  |

| С      | 0.090 | -     | 0.200 | 0.0035 | -                     | 0.0079 |  |

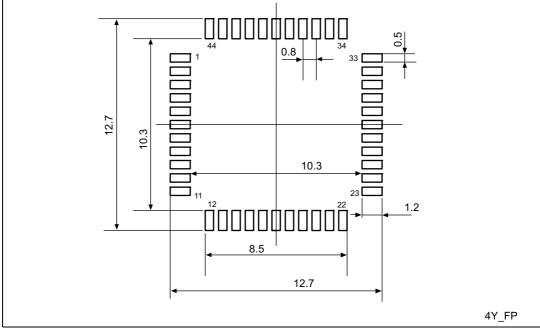

Figure 54. LQFP44 - 44-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

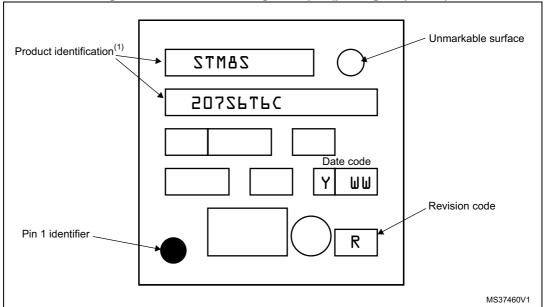

#### **Device marking**

The following figure shows the marking for the LQFP44 package.

Figure 55. LQFP44 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

DocID14733 Rev 13

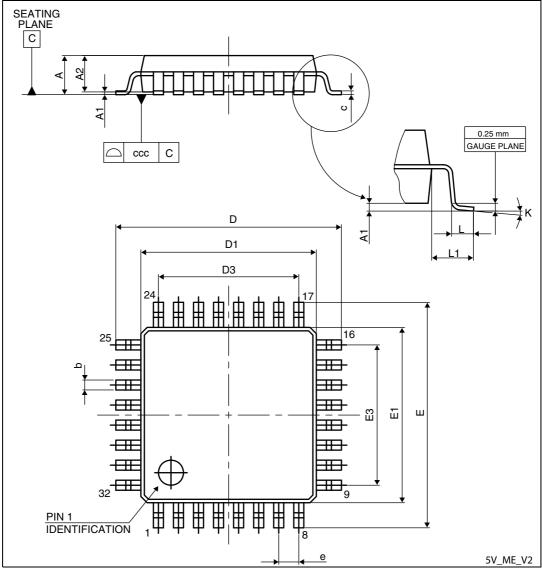

# 11.1.5 LQFP32 package information

Figure 56. LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline

DocID14733 Rev 13

| Date        | Revision    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Jul-2009 | 8<br>cont'd | Section 10: Electrical characteristics: Added data for TBD values;<br>updated Table 15: Voltage characteristics and Table 18: General<br>operating conditions; updated VCAP specifications in Table 18 and<br>in Section 10.3.1: VCAP external capacitor, updated Figure 18;<br>replaced Figure 19; updated Table 35: RAM and hardware registers;<br>updated Figure 22 and Figure 35; added Figure 40: Typical<br>application with I2C bus and timing diagram.<br>Removed Table 56: Junction temperature range.<br>Added link between ordering information Figure 59 and STM8S20xx<br>features Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13-Apr-2010 | 9           | Document status changed from "preliminary data" to "datasheet".<br><i>Table 2: STM8S20xxx performance line features</i> : high sink I/O for<br>STM8S207C8 is 16 (not 13).<br><i>Table 3: Peripheral clock gating bit assignments in</i><br><i>CLK_PCKENR1/2 registers</i> : updated bit positions for TIM2 and<br>TIM3.<br><i>Figure 5: LQFP 48-pin pinout</i> : added CAN_TX and CAN_RX to pins<br>35 and 36; noted that these pins are available only in STM8S208xx<br>devices.<br><i>Figure 7: LQFP 32-pin pinout</i> : replaced uart2 with uart3.<br><i>Table 6: Pin description</i> : added footnotes concerning beCAN<br>availability and UART1_RX and UART3_RX pins.<br><i>Table 13: Option byte description</i> : added description of STM8L<br>bootloader option bytes to the option byte description table.<br>Added <i>Section 9: Unique ID</i> (and listed this attribute in <i>Features</i> ).<br><i>Section 10.3: Operating conditions</i> : replaced "C <sub>EXT</sub> " with "VCAP"<br>and added data for ESR and ESL; removed "low power dissipation"<br>condition for T <sub>A</sub> .<br><i>Table 26: Total current consumption in halt mode at VDD = 5 V</i> :<br>replaced max value of I <sub>DD(H)</sub> at 85 °C from 30 µA to 35 µA for the<br>condition "Flash in power-down mode, HSI clock after wakeup".<br><i>Table 33: HSI oscillator characteristics</i> : updated the ACC <sub>HSI</sub> factory<br>calibrated values.<br><i>Functional EMS (electromagnetic susceptibility)</i> and <i>Table 47</i> :<br>replaced "IEC 1000" with "IEC 61000".<br><i>Electromagnetic interference (EMI)</i> and <i>Table 48</i> : replaced "SAE<br>J1752/3" with "IEC 61967-2".<br><i>Table 57: Thermal characteristics</i> : changed the thermal resistance<br>junction-ambient value of LQFP32 (7x7 mm) from 59 °C/W to 60<br>°C/W. |

Table 58. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved

DocID14733 Rev 13