Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | -                                                      |

| Peripherals                | POR, WDT                                               |

| Number of I/O              | 21                                                     |

| Program Memory Size        | 4KB (4K x 8)                                           |

| Program Memory Type        | ОТР                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 237 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 5.5V                                            |

| Data Converters            | A/D 8x8b                                               |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Through Hole                                           |

| Package / Case             | 28-DIP (0.600", 15.24mm)                               |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e8316psg |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

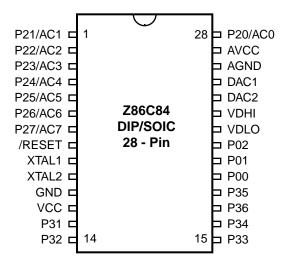

### **PIN DESCRIPTION** (Continued)

| Table 2. Z86C84 28-Pin DIP, SOIC, PLCC F | Pin Identification* |

|------------------------------------------|---------------------|

| <b>—</b> /•                              | <b>D</b> ! /!       |

| No          | Symbol                          | Function                           | Direction    |  |

|-------------|---------------------------------|------------------------------------|--------------|--|

| 1-7         | P21-P27                         | Port 2, Bit 1-7                    | Input/Output |  |

|             | or AC1-AC7                      | Analog In 1-7                      |              |  |

| 8           | /RESET                          | Reset                              | Input        |  |

| 9           | XTAL1                           | Oscillator Clock                   | Input        |  |

| 10          | XTAL2                           | Oscillator Clock                   | Output       |  |

| 11          | GND                             | Ground                             |              |  |

| 12          | V <sub>cc</sub>                 | Power                              |              |  |

| 13-15       | P31-P33                         | Port 3, Bits 1-3                   | Input        |  |

| 16          | P34                             | Port 3, Bit 4                      | Output       |  |

| 17          | P36                             | Port 3, Bit 6                      | Output       |  |

| 18          | P35                             | Port 3, Bit 5                      | Output       |  |

| 19-21       | P00-P02                         | Port 0, Bits 0-3                   | Input/Output |  |

| 22          | VDLO                            | D/A Ref. Volt.,Low                 | Input        |  |

| 23          | VDHI                            | D/A Ref. Volt.,High                | Input        |  |

| 24-25       | DAC2-1                          | D/A Converter                      | Output       |  |

| 26          | A <sub>GND</sub>                | Analog Ground                      |              |  |

| 27          | AV <sub>cc</sub>                | Analog Power                       |              |  |

| 28          | P20                             | Port 2, Bit 0                      | Input/Output |  |

|             | or AC0                          | Analog In 0                        |              |  |

| Note: * DIP | , PLCC and SOIC Pin Description | on and Configuration are identical |              |  |

|     | $\bigcirc$   |   |      |

|-----|--------------|---|------|

| D1  | 1 28         | Þ | D0   |

| D2  |              | Þ | NC   |

| D3  |              | Þ | NC   |

| D4  |              | Þ | NC   |

| D5  | Z86E83       | Þ | NC   |

| D6  | (EPROM Mode) | þ | NC   |

| D7  | DIP/SOIC     | Þ | NC   |

| NC  | 28 - Pin     | Þ | /PGM |

| /CE |              | Þ | CLK  |

| NC  |              | þ | CLR  |

| GND |              | þ | NC   |

| VCC |              | Þ | NC   |

| /OE |              | Þ | NC   |

| EPM | 14 15        | Þ | VPP  |

|     |              |   |      |

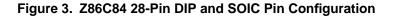

### Figure 4. Z86E83 EPROM Programing Mode 28-Pin DIP and SOIC Pin Configuration

| No    | Symbol          | Function           | Direction    |

|-------|-----------------|--------------------|--------------|

| 1-7   | D1-D7           | Data 1,2,3,4,5,6,7 | Input/Output |

| 8     | NC              | No Connection      |              |

| 9     | /CE             | Chip Enable        | Input        |

| 10    | NC              | No Connection      |              |

| 11    | GND             | Ground             |              |

| 12    | V <sub>cc</sub> | Power              |              |

| 13    | /OE             | Output Enable      | Input        |

| 14    | EPM             | EPROM Program Mode | Input        |

| 15    | V <sub>PP</sub> | Program Voltage    | Input        |

| 16-18 | NC              | No Connection      |              |

| 19    | CLR             | Clear CLock        | Input        |

| 20    | CLK             | Address            | Input        |

| 21    | /PGM            | Program Mode       | Input        |

| 22-27 | NC              | No Connection      |              |

| 28    | D0              | Data 0             | Input/Output |

### Table 3. Z86E83 EPROM Programming Mode 28-Pin DIP, PLCC and SOIC Pin Identification

Figure 7. Z86E83 EPROM Programming Mode 28-Pin PLCC Pin Configuration

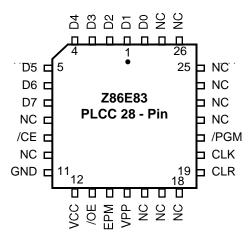

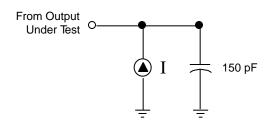

# STANDARD TEST CONDITIONS

The characteristics listed below apply for standard test conditions as noted. All voltages are referenced to Ground. Positive current flows into the referenced pin (Figure 8).

# **V**<sub>DD</sub> **SPECIFICATION**

$V_{DD}$  = 3.5V to 5.5V (Z86E83 only at 0° C to 70° C)

V<sub>DD</sub> = 3.0V to 5.5V (Z86C83/C84)

$V_{DD}$  = 4.5V to 5.5V (Z86E83 only at -40° C to 105° C)

### CAPACITANCE

$T_A = 25^{\circ}C$ ,  $V_{CC} = GND = 0V$ , f = 1.0 MHz, unmeasured pins returned to GND.

| Parameter          | Min | Мах   |

|--------------------|-----|-------|

| Input capacitance  | 0   | 15 pF |

| Output capacitance | 0   | 15 pF |

| I/O capacitance    | 0   | 15 pF |

# For Z86E83 Only

|                  |                                |                     | T <sub>A</sub> =     | 0° C                 | T <sub>A</sub> = -   | -40° C               | Typical |       |                                                   |       |

|------------------|--------------------------------|---------------------|----------------------|----------------------|----------------------|----------------------|---------|-------|---------------------------------------------------|-------|

|                  |                                |                     | to +70° C            |                      | to +1                | to +105° C           |         |       |                                                   |       |

| Sym              | Parameter                      | V <sub>CC</sub> [3] | Min                  | Max                  | Min                  | Max                  | @25°C   | Units | s Conditions                                      | Notes |

| V <sub>CH</sub>  | Clock Input High<br>Voltage    | 3.5V                | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 |                      |                      | 1.3     | V     | Driven by External<br>Clock Generator             |       |

|                  |                                | 5.5V                | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.5     | V     | Driven by External<br>Clock Generator             |       |

| V <sub>CL</sub>  | Clock Input Low<br>Voltage     | 3.5V                | GND-0.3              | 0.2 V <sub>CC</sub>  |                      |                      | 0.7     | V     | Driven by External<br>Clock Generator             |       |

|                  |                                | 5.5V                | GND-0.3              | 0.2 V <sub>CC</sub>  | GND-0.3              | 0.2 V <sub>CC</sub>  | 1.5     | V     | Driven by External<br>Clock Generator             |       |

| VIH              | Input High Voltage             | 3.5V                | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 |                      |                      | 1.3     | V     |                                                   |       |

|                  |                                | 5.5V                | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 0.7 V <sub>CC</sub>  | V <sub>CC</sub> +0.3 | 2.5     | V     |                                                   |       |

| V <sub>IL</sub>  | Input Low Voltage              | 3.5V                | GND-0.3              | 0.2 V <sub>CC</sub>  |                      |                      | 0.7     | V     |                                                   |       |

|                  |                                | 5.5V                | GND-0.3              | 0.2 V <sub>CC</sub>  | GND-0.3              | 0.2 V <sub>CC</sub>  | 1.5     | V     |                                                   |       |

| V <sub>OH1</sub> | Ouput High Voltage             | 3.5V                | V <sub>CC</sub> -0.4 |                      |                      |                      | 3.1     | V     | I <sub>OH</sub> = -2.0 mA                         | 8     |

| 0                |                                | 5.5V                | V <sub>CC</sub> -0.4 |                      | V <sub>CC</sub> -0.4 |                      | 4.8     | V     | I <sub>OH</sub> = -2.0 mA                         | 8     |

| V <sub>OL1</sub> | Output Low Voltage             | 3.5V                |                      | 0.6                  |                      |                      | 0.2     | V     | I <sub>OH</sub> = +4.0 mA                         | 8     |

| 021              |                                | 5.5V                |                      | 0.4                  |                      | 0.4                  | 0.1     | V     | I <sub>OH</sub> = +4.0 mA                         | 8     |

| V <sub>OL2</sub> | Output Low Voltage             | 3.5V                |                      | 1.2                  |                      |                      | 0.3     | V     | I <sub>OH</sub> = +6.0 mA                         | 8     |

| OLL              |                                | 5.5V                |                      | 1.2                  |                      | 1.2                  | 0.3     | V     | $I_{OH} = +10.0 \text{ mA}$                       | 8     |

| V <sub>RH</sub>  | Reset Input High               | 3.5V                | 0.8V <sub>CC</sub>   | V <sub>CC</sub>      |                      |                      | 1.5     | V     |                                                   |       |

|                  | Voltage                        | 5.5V                | 0.8V <sub>CC</sub>   | V <sub>CC</sub>      | 0.8V <sub>CC</sub>   | V <sub>CC</sub>      | 2.1     | V     |                                                   |       |

|                  |                                | 3.5V                | GND-0.3              |                      | 00                   | 00                   | 1.1     | V     |                                                   |       |

|                  |                                | 5.5V                |                      |                      | GND-0.3              | 0.2V <sub>CC</sub>   | 1.7     | V     |                                                   |       |

| VOFES            | Comparator Input               | 3.5V                |                      | 25                   |                      | 00                   | 10      | mV    |                                                   | 10    |

| ET               | Offset Voltage                 | 5.5V                |                      | 25                   |                      | 25                   | 10      | mV    |                                                   | 10    |

| $I_{IL}$         | Input Leakage                  | 3.5V                | -1                   | 1                    |                      |                      | <1      | μA    | $V_{IN} = 0V, V_{CC}$                             |       |

|                  |                                | 5.5V                | -1                   | 1                    | -1                   | 2                    | <1      | μA    | $V_{IN} = 0V, V_{CC}$                             |       |

| I <sub>OL</sub>  | Output Leakage                 | 3.5V                | -1                   | 1                    |                      |                      | <1      | μA    | $V_{IN} = 0V, V_{CC}$                             |       |

| -                |                                | 5.5V                | -1                   | 1                    | -1                   | 2                    | <1      | μA    | $V_{IN} = 0V, V_{CC}$                             |       |

| I <sub>IR</sub>  | Reset Input Current            | 3.5V                |                      | -130                 |                      |                      | -25     | μA    |                                                   |       |

|                  | ·                              | 5.5V                |                      | -180                 |                      | -180                 | -40     | μA    |                                                   |       |

| I <sub>CC</sub>  | Supply Current                 | 3.5V                |                      | 20                   |                      |                      | 7       | mA    | @16 MHz                                           | 1,4   |

|                  |                                | 5.5V                |                      | 25                   |                      | 25                   | 20      | mΑ    | @16 MHz                                           | 1,4   |

| I <sub>CC1</sub> | Standby Current<br>(HALT Mode) | 3.5V                |                      | 4.5                  |                      |                      | 2.0     | mA    | V <sub>IN</sub> = 0V, V <sub>CC</sub> @ 16<br>MHz | 1,4   |

|                  |                                | 5.5V                |                      | 8                    |                      | 8                    | 3.7     | mA    | V <sub>IN</sub> = 0V, V <sub>CC</sub> @ 16<br>MHz | 1,4   |

|                  |                                | 3.5V                |                      | 3.4                  |                      |                      | 1.5     | mA    | Clock divide by 16 @<br>16 MHz                    | 1,4   |

|                  |                                | 5.5V                |                      | 7.0                  |                      | 7.0                  | 2.9     | mA    | Clock divide by 16 @<br>16 MHz                    | 1,4   |

|                  |                                                   |                     | T <sub>A</sub> = | • 0° C                    | T <sub>A</sub> = | -40° C                | Typical |      |                                                             |               |

|------------------|---------------------------------------------------|---------------------|------------------|---------------------------|------------------|-----------------------|---------|------|-------------------------------------------------------------|---------------|

|                  |                                                   |                     | to +             | 70° C                     | to +             | 105° C                | [13]    |      |                                                             |               |

| Sym              | Parameter                                         | V <sub>CC</sub> [3] | Min              | Max                       | Min              | Max                   | @25°C   | Unit | s Conditions                                                | Notes         |

| I <sub>CC2</sub> | Standby Current<br>(STOP Mode)                    | 3.5V                |                  | 8                         |                  |                       | 1       | μA   | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>WDT is not Running | 1,6,11        |

|                  |                                                   | 5.5V                |                  | 10                        |                  | 20                    | 2       | μA   | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>WDT is not Running | 1,6,11        |

|                  |                                                   | 3.5V                |                  | 500                       |                  |                       | 310     | μA   | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>WDT is Running     | 1,6,11,<br>14 |

|                  |                                                   | 5.5V                |                  | 800                       |                  | 1000                  | 600     | μA   | V <sub>IN</sub> = 0V, V <sub>CC</sub><br>WDT is Running     | 1,6,11,<br>14 |

| V <sub>ICR</sub> | Input Common<br>Mode                              | 3.5V                | 0                | V <sub>CC</sub> -<br>1.0V | 0                |                       |         | V    |                                                             | 10            |

|                  |                                                   | 5.5V                | 0                | V <sub>CC</sub> -<br>1.0V | 0                | V <sub>CC</sub> -1.5V |         | V    |                                                             | 10            |

| I <sub>ALL</sub> | Auto Latch Low                                    | 3.5V                |                  | 8                         |                  |                       | 5       | μA   | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub>                       | 9             |

|                  | Current                                           | 5.5V                |                  | 15                        |                  | 20                    | 11      | μA   | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub>                       | 9             |

| I <sub>ALH</sub> | Auto Latch High                                   | 3.5V                |                  | -5                        |                  |                       | -3      | μA   | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub>                       | 9             |

|                  | Current                                           | 5.5V                |                  | -8                        |                  | -10                   | -6      | μA   | 0V <v<sub>IN<v<sub>CC</v<sub></v<sub>                       | 9             |

| V <sub>LV</sub>  | V <sub>CC</sub> Low-Voltage<br>Protection Voltage |                     | 2.0              | 3.3                       | 2.2              | 3.5                   | 3.0     | V    | 2 MHz max. Int. CLK<br>Frequency                            | 7             |

#### Notes:

1. Combined digital  $V_{CC}$  and analog  ${\sf AV}_{CC}$  supply currents

- 2. GND = 0V

- 3. V<sub>CC</sub> voltage specification of 3.5V guarantees 3.5V, and V<sub>CC</sub> voltage specification of 5.5V guarantees 5.0V  $\pm$ 0.5V

- 4. All outputs unloaded, I/O pins floating, inputs at rail

- 5. CL1 = CL2 = 100 pF

- 6. Same as note [4] except inputs at  $V_{\mbox{CC}}$

- 7. The  $V_{\mbox{LV}}$  increases as the temperature decreases

- 8. Standard Mode (not Low EMI)

- 9. Auto Latch (mask option) selected

- 10. For analog comparator, inputs when analog comparators are enabled

- 11. Clock must be forced Low, when XTAL 1 is clock-driven and XTAL2 is floating

- 12. Excludes clock pins

- 13. Typicals are at  $V_{CC}$  = 3.5V and 5.0V

- 14. Internal RC selected

## **AC ELECTRICAL CHARACTERISTICS**

Additional Timing Table (Low EMI Mode Only) For Z86E83 Only

|    |         |                               |          | T <sub>A</sub> = 0°C | to +70°C | T <sub>A</sub> = -40°C | to +105°C |       |         |

|----|---------|-------------------------------|----------|----------------------|----------|------------------------|-----------|-------|---------|

|    |         |                               | vcc      | 4 MHz                |          | 4 MHz                  |           |       |         |

| No | Symbol  | Parameter                     | [Note 6] | Min                  | Max      | Min                    | Max       | Units | Notes   |

| 1  | ТрС     | Input Clock Period            | 3.5V     | 250                  | DC       |                        |           | ns    | 1,7,8   |

|    |         |                               | 5.5V     | 250                  | DC       | 250                    | DC        | ns    | 1,7,8   |

| 2  | TrC,TfC | Clock Input Rise & Fall Times | 3.5V     |                      | 25       |                        |           | ns    | 1,7,8   |

|    |         |                               | 5.5V     |                      | 25       |                        | 25        | ns    | 1,7,8   |

| 3  | TwC     | Input Clock Width             | 3.5V     | 125                  |          |                        |           | ns    | 1,7,8   |

|    |         |                               | 5.5V     | 125                  |          | 125                    |           | ns    | 1,7,8   |

| 4  | TwTinL  | Timer Input Low Width         | 3.5V     | 100                  |          |                        |           | ns    | 1,7,8   |

|    |         |                               | 5.5V     | 70                   |          | 70                     |           | ns    | 1,7,8   |

| 5  | TwTinH  | Timer Input High Width        | 3.5V     | 3TpC                 |          |                        |           |       | 1,7,8   |

|    |         |                               | 5.5V     | 3TpC                 |          | 3TpC                   |           |       | 1,7,8   |

| 6  | TpTin   | Timer Input Period            | 3.5V     | 4TpC                 |          |                        |           |       | 1,7,8   |

|    |         |                               | 5.5V     | 4TpC                 |          | 4TpC                   |           |       | 1,7,8   |

| 7  | TrTin,  | Timer Input Rise & Fall Timer | 3.5V     |                      | 100      |                        |           | ns    | 1,7,8   |

|    | TfTin   |                               | 5.5V     |                      | 100      |                        | 100       | ns    | 1,7,8   |

| 8A | TwIL    | Int. Request Low Time         | 3.5V     | 100                  |          |                        |           | ns    | 1,2,7,8 |

|    |         |                               | 5.5V     | 70                   |          | 70                     |           | ns    | 1,2,7,8 |

| 8B | TwIL    | Int. Request Low Time         | 3.5V     | 3TpC                 |          |                        |           |       | 1,3,7,8 |

|    |         |                               | 5.5V     | 3TpC                 |          | 3TpC                   |           |       | 1,3,7,8 |

| 9  | TwIH    | Int. Request Input High Time  | 3.5V     | 3TpC                 |          |                        |           |       | 1,2,7,8 |

|    |         |                               | 5.5V     | 3TpC                 |          | 2TpC                   |           |       | 1,2,7,8 |

| 10 | Twsm    | Stop-Mode Recovery Width      | 3.5V     | 12                   |          |                        |           | ns    | 4,8     |

|    |         | Spec                          | 5.5V     | 12                   |          | 12                     |           | ns    | 4,8     |

| 11 | Tost    | Oscillator Start-up Time      | 3.5V     |                      | 5TpC     |                        |           |       | 4,8,9   |

|    |         |                               | 5.5V     |                      | 5TpC     |                        | 5TpC      |       | 4,8,9   |

#### Notes:

1. Timing Reference uses 0.7 V  $_{\rm CC}$  for a logic 1 and 0.2 V  $_{\rm CC}$  for a logic 0.

- 2. Interrupt request via Port 3 (P31-P33)

- 3. Interrupt request via Port 3 (P30)

- 4. SMR-D5 = 1, POR STOP Mode delay is on.

- 5. Reg. WDTMR

- 6. The V voltage specification of 3.5V guarantees 3.5V,  $_{\rm CC}$

and the V voltage specification of 5.5V guarantees 5.0V  $\pm 0.5$ V.

- 7. SMR D1 = 0

- 8. Maximum frequency for internal system clock is 4 MHz when using XTAL divide-by-one mode.

- 9. For LC oscillator and for oscillator driven by clock driver

| Table 8. | A/D Converter Electrical Characteristics |

|----------|------------------------------------------|

|          | $V_{cc} = 3.5V$                          |

| Parameter                         | Minimum               | Typical | Maximum               | Units |

|-----------------------------------|-----------------------|---------|-----------------------|-------|

| Resolution                        |                       | 8       |                       | Bits  |

| Integral non-linearity            |                       | 0.5     | 1                     | LSB   |

| Differential non-linearity        |                       | 0.5     | 1                     | LSB   |

| Zero Error at 25°C                |                       |         | 5.0                   | mV    |

| Supply Range                      | 3.5                   |         |                       | Volts |

| Power dissipation, no load        |                       | 20      | 40                    | mW    |

| Clock frequency                   |                       |         | 16                    | MHz   |

| Input voltage range               | VA <sub>LO</sub>      |         | VA <sub>HI</sub>      | Volts |

| Conversion time                   |                       |         | 35 x SCLK             | µsec  |

| Input capacitance on ANA          | 25                    |         | 40                    | pF    |

| VA <sub>H</sub> range             | VA <sub>LO</sub> +2.5 |         | AV <sub>cc</sub>      | Volts |

| VA <sub>LO</sub> range            | AN <sub>GND</sub>     |         | AV <sub>cc</sub> –2.5 | Volts |

| VA <sub>HI</sub> VA <sub>LO</sub> | 2.5                   |         | AV <sub>cc</sub>      | Volts |

#### Notes:

Voltage: 3.5V

Temp: 0-70°C

Conversion time is defined as the time from initiation of A-D conversion to storage of the digital result in the ADR register. SCLK = Internal Z8 System Clock (Bus Speed)

### For Z86E83

| Table 9. | A/D Converter Electrical Characteristics |

|----------|------------------------------------------|

|          | $V_{cc} = 5.0V \pm 10\%$                 |

| Parameter                         | Minimum               | Typical | Maximum               | Units |

|-----------------------------------|-----------------------|---------|-----------------------|-------|

| Resolution                        |                       | 8       |                       | Bits  |

| Integral non-linearity            |                       | 0.5     | 1                     | LSB   |

| Differential non-linearity        |                       | 0.5     | 1                     | LSB   |

| Zero Error at 25°C                |                       |         | 45                    | mV    |

| Supply Range                      | 4.5                   | 5.0     | 5.5                   | Volts |

| Power dissipation, no load        |                       | 50      | 85                    | mW    |

| Clock frequency                   |                       |         | 16                    | MHz   |

| Input voltage range               | VA <sub>LO</sub>      |         | VA <sub>HI</sub>      | Volts |

| Conversion time                   | 4.3                   |         | 35 x SCLK             | µsec  |

| Input capacitance on ANA          | 25                    |         | 40                    | pF    |

| VA <sub>H</sub> range             | VA <sub>LO</sub> +2.5 |         | AV <sub>cc</sub>      | Volts |

| VA <sub>LO</sub> range            | AN <sub>GND</sub>     |         | AV <sub>cc</sub> -2.5 | Volts |

| VA <sub>HI</sub> VA <sub>LO</sub> | 2.5                   |         | AV <sub>cc</sub>      | Volts |

#### Notes:

Voltage: 4.5V -5.5V

Temp: 0-70°C

Conversion time is defined as the time from initiation of A-D conversion to storage of the digital result in the ADR register. SCLK = Internal Z8 System Clock (Bus Speed)

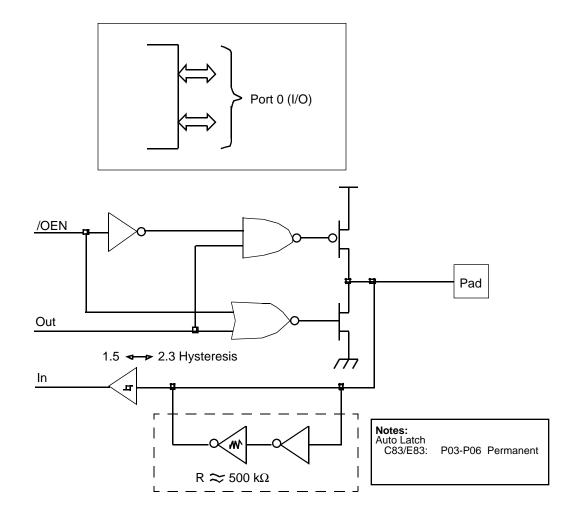

Figure 10. Port 0 Configuration

**Port 3 (P36-P31)** Port 3 is a 6-bit, CMOS-compatible port, with three fixed inputs (P33-P31) and three fixed outputs (P34-P36), configured under software control for Input/Output, Counter/Timers, interrupt, and port hand-shake. P31, P32, and P33 are standard CMOS inputs (no Auto Latches). Pins P34, P35, and P36 are push-pull output lines (Figure 11). Low EMI output buffers can be globally programmed by the software.

Two on-board comparators can process analog signals on P31 and P32 with reference to the voltage on P33. The analog function is enabled by programming Port 3 Mode Register (P3M bit 1). For Interrupt functions, Port 3, pin 3 is falling-edge interrupt input. P31 and P32 are programmable as rising, falling, or both edge triggered interrupts (IRQ register bits 6 and bit 7). P33 is the comparator reference voltage input when in Analog Mode. Access to Counter/Timers 1 is made through P31 ( $T_{IN}$ ) and P36 ( $T_{OUT}$ ). Handshake lines for Ports 0 and 2 are available on P31/P36 and P32/P35 (Table 10).

Port 3 also provides the following control functions: handshake for Ports 0 and 2 (/DAV and RDY); three external interrupt request signals (IRQ2-IRQ0); timer input and output signals ( $T_{IN}$  and  $T_{OUT}$ ).

Table 10. Port 3 Pin Assignments

| Pin                    | I/O | CTC1             | Analog  | Int. | P0 HS | P2 HS |  |

|------------------------|-----|------------------|---------|------|-------|-------|--|

| P31                    | IN  | T <sub>IN</sub>  | AN1     | IRQ2 |       | D/R   |  |

| P32                    | IN  |                  | AN2     | IRQ0 | D/R   |       |  |

| P33                    | IN  |                  | REF     | IRQ1 |       |       |  |

| P34                    | OUT |                  | AN1-OUT |      |       |       |  |

| P35                    | OUT |                  |         |      | R/D   |       |  |

| P36                    | OUT | T <sub>OUT</sub> |         |      |       | R/D   |  |

| Notes:                 |     |                  |         |      |       |       |  |

| HS = Handshake Signals |     |                  |         |      |       |       |  |

| D = /DAV               |     |                  |         |      |       |       |  |

| R = RDY                |     |                  |         |      |       |       |  |

**Auto Latch.** The Auto-Latch instruction puts valid CMOS levels on CMOS inputs that are not externally driven. Whether this level is 0 or 1, cannot be determined. A valid CMOS level, rather than a floating node, reduces excessive supply current flow in the input buffer.

**Note:** Pins 03, 04, 05, 06 have permanently enabled Auto Latches.

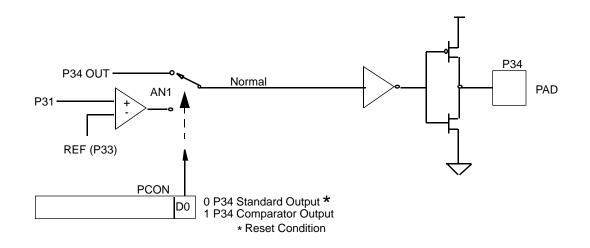

**Comparator Inputs.** Port 3, P31 and P32, each have a comparator front end. The comparator reference voltage, P33, is common to both comparators. In analog mode, the P33 input functions as a reference voltage to the comparators. In Analog Mode, the internal P33 register and its corresponding IRQ1 is connected to the Stop-Mode Recovery source selected by the SMR register. In this mode, any of the Stop-Mode Recovery sources are used to toggle the P33 bit or generate IRQ1. In Digital Mode, P33 can be used as a Port 3 register input or IRQ1 source. P34 outputs the comparator outputs by software programming the PCON Register bit D0 to 1.

**Note**: When enabling/or disabling the analog mode, the following is recommended:

- 1. allow two NOP delays before reading the comparator output

- 2. disable interrupts, switch to analog mode, clear interrupts, and then re-enable interrupts.

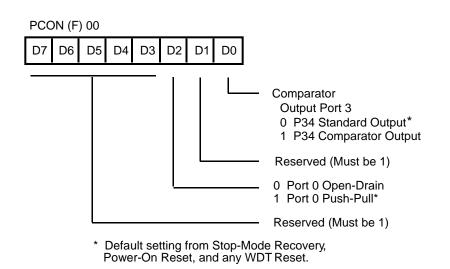

**Port Configuration Register (PCON).** The PCON configures the ports individually for comparator output on Port 3. The PCON Register is located in the Expanded Register File at Bank F, location 00 (Figure 13).

Bit 0 multiplexes comparator AN1 Output at P34. A "1" in this location brings the comparator output to P34 (Figure 14), and a "0" puts P34 into its standard I/O configuration.

**Note:** Only comparator output AN1 is multiplexed to a Port 3 output. Comparator AN2 output is not connected to any pins. Note that the PCON Register is reset upon the occurrence of a WDT RESET (not in STOP Mode), and Power-On Reset (POR).

Figure 13. Port Configuration Register (PCON) (Write-Only)

Figure 14. Port 3 P34 Output Configuration

# FUNCTIONAL DESCRIPTION (Continued)

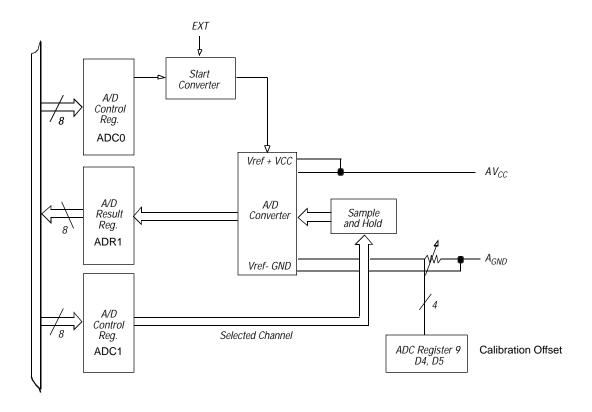

### **Analog-to-Digital Converter**

The Analog-to-Digital (ADC) is an 8-bit half flash converter that uses two reference resistor ladders for its upper 4 bits (MSBs) and lower 4 bits (LSBs) conversion. Two reference voltage pins,  $AV_{CC}$  and  $A_{GND}$ , are provided for external reference voltage supplies. During the sampling period from one of the eight channel inputs, the converter is also being auto-zeroed before starting the conversion. The conversion time is dependent on the internal clock frequency. The minimum conversion time is 35 x SCLK (see Figure 22).

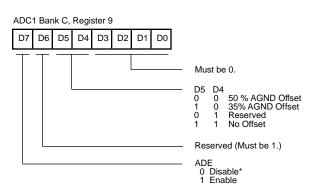

The ADC is controlled by the Z8 and its three registers (two Control and one Result) are mapped into the Extended Register File. A conversion can be initiated by writing to the ADC Control Register 0 after the ADC Control Register 1 is configured.

The start command is implemented in such a way as to begin a conversion at any time, if a conversion is in progress and a new start command is received, then the conversion in progress will be aborted and a new conversion will be initiated. This allows the programmed values to be changed without affecting a conversion-in-progress. The new values will take effect only after a new start command is received.

The ADC can be disabled (for low power) or enabled by a Control Register bit.

Though the ADC will function for a smaller input voltage and voltage reference, the noise and offsets remain constant over the specified electrical range. The errors of the converter will increase and the conversion time may also take slightly longer due to smaller input signals.

### **ADC Calibration Offset**

Specially matched resistors are program-enabled to allow 35 percent or 50 percent offset from  $A_{GND}$ . They may selectively enable these resistors to offset the  $A_{GND}$  by 50 percent (2.5V to 5V) or 35 percent (1.75V to 5V) thereby allowing the 8-bit ADC across a narrower voltage range. This will allow significant resolution improvement within the reduced voltage range.

**Note:** The AV<sub>CC</sub> must be the same value as V<sub>CC</sub> and A<sub>GND</sub> must be the same value as GND.

Figure 22. ADC Architecture

# FUNCTIONAL DESCRIPTION (Continued)

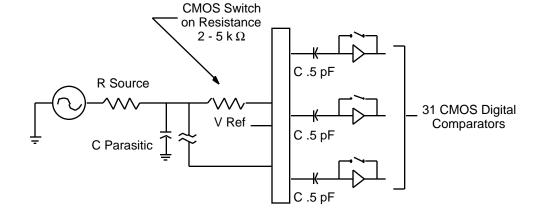

Figure 27 shows the input circuit of the ADC. When conversion starts the analog input voltage is connected to the MSB and LSB flash converter inputs as shown in the Input Impedance CKT diagram. Effectively, shunting 31 parallel internal resistance of the analog switches and simultaneously charging 31 parallel 0.5 pF capacitors, which is equivalent to seeing a 400 Ohms input impedance in par-

allel with a 16 pF capacitor. Other input stray capacitance adds about 10 pF to the input load. For input source resistances up to 2 Kohms can be used under normal operating condition without any degradation of the input settling time. For larger input source resistance, increasing conversion cycle time or adding a capacitor to the input may be required to compensate the input settling time problem.

Figure 27. Input Impedance of ADC

### **Typical Z8 A/D Conversion Sequence**

- Set the register pointer to Extended Bank (C), that is, SRP #%0C instruction.

- 4. Next, set ADE flag by loading ADC1 Control Register Bank (C) Register 9, bit 7. Also, load bits 0-4 of this same register to select a  $AV_{CC}$  or  $A_{GND}$  offset value. A precision voltage divider connected to the A/D resistive ladder can offset conversion dynamic range to specified limits within the  $AV_{CC}$  and  $A_{GND}$  limits. By loading Bank (C) Register 9, bits 0-4, with the appropriate value it is possible to select from these groups:

- a. No Offset. The Converter Dynamic range is from 0V to 5.0V for  $AV_{CC} = 5.0V$ .

- b. 35 Percent A<sub>GND</sub> Offset. The Converter Dynamic range is 1.75V 5.0V for AV<sub>CC</sub> = 5.0V.

- c. 50 Percent A<sub>GND</sub> Offset. The Converter Dynamic range is 2.5V 5.0V for AV<sub>CC</sub> = 5.0V.

- Select one of the eight A/D inputs for conversion by loading Bank (C) Register 8 with the desired attributes: Bits 0 - 2 select an A/D input, bits 3 and 4 select A/D conversion (or digital port I/O).

- Set Bank (C) Register 8, bit 3 to enable A/D conversion. (This flag can be set concurrently with step 3.) This flag is automatically reset when the A/D conversion is completed, so a bit test can be performed to determine A/D readiness if necessary.

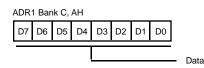

- Read the A/D result in Bank (C) Register A. Please note that the A/D result is not valid (indeterminate) unless ADE flag (Register 9, bit 7) was previously set, otherwise A/D converter output is tri-stated.

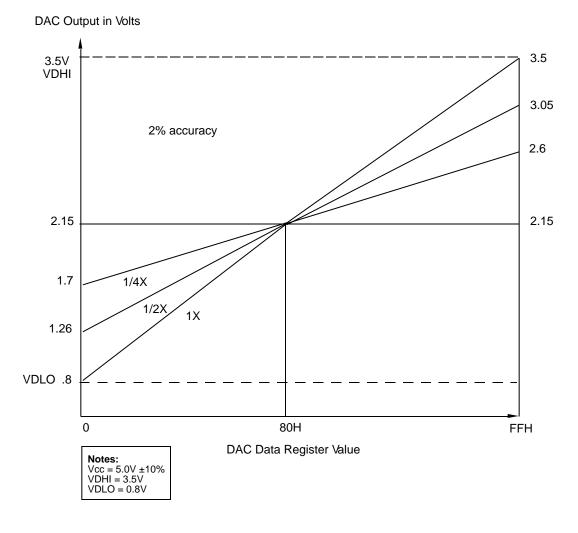

Figure 33. Gain Control on DAC

**Power-On Reset (POR).** A timer circuit clocked by a dedicated on-board RC oscillator or by the XTAL oscillator is used for the POR timer function. The POR time allows  $V_{CC}$  and the oscillator circuit to stabilize before instruction execution begins. The POR timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK Status

- Stop-Mode Recovery (If D5 of SMR Register = 1)

- WDT Time-Out (Including from STOP Mode)

The POR time is  $T_{POR}$  minimum. Bit 5 of the STOP Mode Register determines whether the POR timer is bypassed after Stop-Mode Recovery (typical for external clock and LC oscillators with fast start up time). **HALT.** Turns off the internal CPU clock but not the XTAL oscillation. The counter/timers and external interrupts IRQ0, IRQ1, and IRQ2 remain active. The device is recovered by interrupts, either externally or internally generated (a POR or a WDT time-out). An interrupt request must be executed (enabled) to exit HALT Mode. After the interrupt service routine, the program continues from the instruction after the HALT. In case of a POR or a WDT time-out, program execution will restart at address 000CH.

**STOP.** This instruction turns off the internal clock and external crystal oscillation and reduces the standby current to 10  $\mu$ A (typical) or less. The STOP Mode is terminated by a reset of either WDT time-out, POR, or Stop-Mode Recovery. This causes the processor to restart the application program at address 000CH.

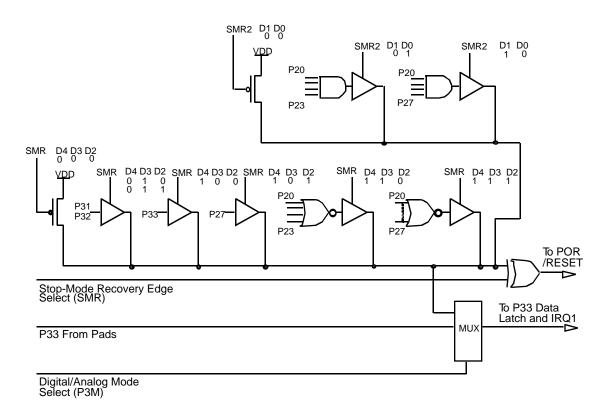

**Stop-Mode Recovery Source (D2, D3, and D4).** These three bits of the SMR register specify the wake-up source of the STOP recovery (Figure 37 and Table 13). When the Stop-Mode Recovery Sources are selected in this register then SMR2 register bits D0,D1 must be set to zero. P33-P31 and Port 2 cannot wake up from STOP Mode if the input lines are configured as analog inputs to the Analog comparator or Analog-to-Digital Converter.

**Note:** If the Port 2 pin is configured as an output, this output level will be read by the SMR circuitry.

| Table 13. | Stop-Mode | Recovery | y Source |

|-----------|-----------|----------|----------|

|-----------|-----------|----------|----------|

| S  | SMR:432 |    | Operation                           |  |

|----|---------|----|-------------------------------------|--|

| D4 | D3      | D2 | Description of Action               |  |

| 0  | 0       | 0  | POR and/or external reset recovery  |  |

| 0  | 0       | 1  | Reserved                            |  |

| 0  | 1       | 0  | P31 transition (not in Analog Mode) |  |

| 0  | 1       | 1  | P32 transition (not in Analog Mode) |  |

| 1  | 0       | 0  | P33 transition (not in Analog Mode) |  |

| 1  | 0       | 1  | P27 transition                      |  |

| 1  | 1       | 0  | Logical NOR of P20 through P23      |  |

| 1  | 1       | 1  | Logical NOR of P20 through P27      |  |

Stop-Mode Recovery Delay Select (D5). This bit, if High, enables the  $T_{POR}$  /RESET delay after Stop-Mode Recovery. The default configuration of this bit is "1". A POR or

WDT reset will override the selection and cause the reset delay to occur.

**Stop-Mode Recovery Edge Select (D6).** A "1" in this bit position indicates that a high level on the output to the exclusive Or-Gate input from the selected recovery source wakes the Z86C83/C84/E83 from STOP Mode. A "0" indicates low-level recovery. The default is 0 on POR. This bit is used for either SMR or SMR2.

**Cold or Warm Start (D7).** This bit is set by the device upon entering STOP Mode. A 0 in this bit (cold) indicates that the device resets by POR/WDT reset. A "1" in this bit (warm) indicates that the device awakens by a Stop-Mode Recovery source.

**Note:** A WDT reset out of STOP Mode will also set this bit to a "1".

**Stop-Mode Recovery Register 2 (SMR2).** This register contains additional Stop-Mode Recovery sources. When the Stop-Mode Recovery sources are selected in this register then SMR Register Bits D2, D3, and D4 must be 0.

#### Table 14. Stop-Mode Recovery Source

| SMR:10 Operation<br>D1 D0 Description of Action |   | Operation<br>Description of Action |

|-------------------------------------------------|---|------------------------------------|

| 0                                               | 0 | POR and/or external reset recovery |

| 0                                               | 1 | Logical AND of P20 through P23     |

| 1                                               | 0 | Logical AND of P20 through P27     |

Figure 37. Stop-Mode Recovery Source

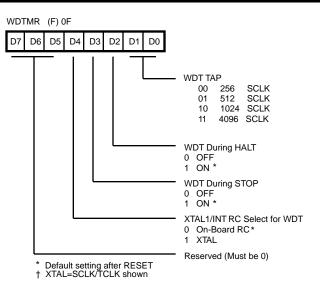

#### Figure 39. Watch-Dog Timer Mode Register (Write Only)

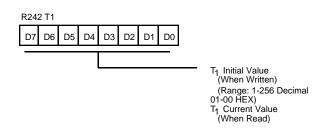

**WDT Time Select (D1, D0).** Selects the WDT time-out period. It is configured as shown in Table 15.

|                                                             |    | Time-Out of     | Time-Out of |  |  |

|-------------------------------------------------------------|----|-----------------|-------------|--|--|

| D1                                                          | D0 | Internal RC OSC | SCLK Clock  |  |  |

| 0                                                           | 0  | 6.25 ms min     | 256 SCLK    |  |  |

| 0                                                           | 1  | 12.5 ms min     | 512 SCLK    |  |  |

| 1                                                           | 0  | 25 ms min       | 1024 SCLK   |  |  |

| 1                                                           | 1  | 100 ms min      | 4096 SCLK   |  |  |

| <b>Note:</b> The minimum time shown is for $V_{cc}$ @ 5.0V. |    |                 |             |  |  |

Table 15. WDT Time Select (Min. @ 5.0V)

**WDT During HALT (D2).** This bit determines whether or not the WDT is active during HALT Mode. A "1" indicates active during HALT. The default is "1".

**Note:** If WDT is permanently selected (always ON mode), the WDT will continue to run even if set not to run in STOP or HALT Mode.

**WDT During STOP (D3).** This bit determines whether or not the WDT is active during STOP Mode. Since XTAL clock is stopped during STOP Mode, unless as specified below, the on-board RC has to be selected as the clock source to the POR counter. A "1" indicates active during STOP. The default is "1". If bits D3 and D4 are both set to "1", the WDT only, is driven by the external clock during STOP Mode.

#### Notes:

- 1. If WDT is permanently selected (always ON mode) using internal on-board RC oscillator, the WDT will continue to run even if set not to run in STOP or HALT Mode.

- WDT instructions affect the Z (Zero), S (Sign), and V (Overflow) flags.

**On-Board, Power-On-Reset RC or External XTAL1 Oscillator Select (D4).** This bit determines which oscillator source is used to clock the internal POR and WDT counter chain. If the bit is a "1", the internal RC oscillator is bypassed and the POR and WDT clock source is driven from the external pin, XTAL1. The default configuration of this bit is 0, which selects the RC oscillator. If the XTAL1 pin is selected as the oscillator source for the WDT, during STOP Mode, the oscillator will be stopped and the WDT will not run. This is true even if the WDT is selected to run during STOP Mode.

$V_{CC}$  Voltage Comparator. An on-board Voltage Comparator checks that  $V_{CC}$  is at the required level to ensure correct operation of the device. RESET is globally driven if  $V_{CC}$  is below the specified voltage (typically 2.6V).

**ROM Protect.** ROM Protect is mask or OTP bit-programmable. It is selected by the customer at the time the ROM code is submitted.

### **ROM Mask Selectable Options**

There are two ROM mask options that must be selected at the time the ROM mask is ordered (ROM code submitted) for the Z86C83/C84 and three Z86E83 OTP bit options.

#### Table 16. Selectable Options

| Option                   | Selection |

|--------------------------|-----------|

| Permanent WDT            | Yes/No    |

| ROM Protect              | Yes/No    |

| EPROM/TEST Mode Disable* | Yes/No    |

Note:

\*For Z86E83 only

EPROM/TEST Mode Disable - On the Z86E83, the user can permanently disable entry into EPROM Mode and TEST Mode by programming this bit.

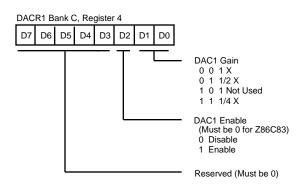

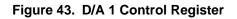

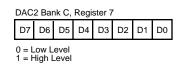

Figure 44. D/A 2 Control Register

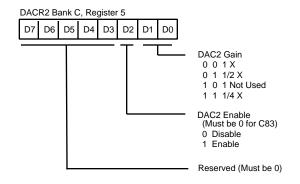

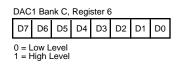

#### Figure 45. D/A 1 Data Register

Figure 46. D/A 2 Data Register

Figure 41. ADC Control Register 1 (Read/Write)

Figure 42. AD Result Register (Read Only)

# **Z8 CONTROL REGISTERS**

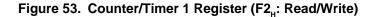

### Figure 52. Timer Mode Register (F1<sub>µ</sub>: Read/Write)

10

11 Internal Clock Out

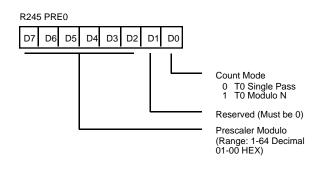

Figure 57. Port 3 Mode Register (F7<sub>H</sub>: Write-Only)

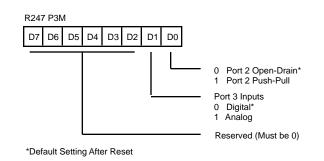

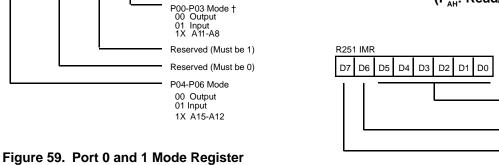

(F8<sub>H</sub>: Write-Only)

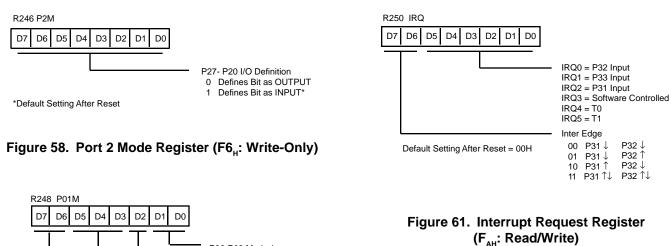

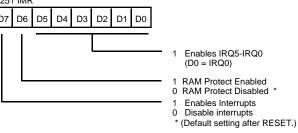

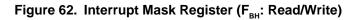

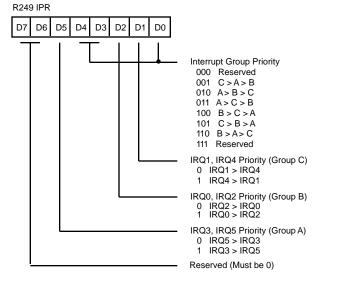

Figure 60. Interrupt Priority Register (F9.: Write-Only)

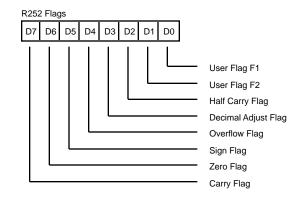

Figure 63. Flag Register (F<sub>CH</sub>: Read/Write)

# **ORDERING INFORMATION**

|             | Z86C83<br>16 MHz |             |             | Z86E83<br>16 MHz |             |

|-------------|------------------|-------------|-------------|------------------|-------------|

| 28-Pin DIP  | 28-Pin SOIC      | 28-Pin PLCC | 28-Pin DIP  | 28-Pin SOIC      | 28-Pin PLCC |

| Z86C8316PSC | Z86C8316SSC      | Z86C8316VSC | Z86E8316PSC | Z86E8316SSC      | Z86E8316VSC |

| Z86C8316PEC | Z86C8316SEC      | Z86C8316VEC | Z86E8316PEC | Z86E8316SEC      | Z86E8316VEC |

|             | Z86C84<br>16 MHz |             |             |                  |             |

| 28-Pin DIP  | 28-Pin SOIC      | 28-Pin PLCC |             |                  |             |

| Z86C8416PSC | Z86C8416SSC      | Z86C8416VSC |             |                  |             |

| Z86C8416PEC | Z86C8416SEC      | Z86C8416VEC |             |                  |             |

For fast results, contact your local Zilog sales office for assistance in ordering the part desired.

### Package

P = Plastic DIP S = Plastic SOIC

### Temperature

$S = 0^{\circ}C$  to  $+ 70^{\circ}C$  $E = -40^{\circ}C$  to  $+105^{\circ}C$

#### Example:

Z 86C83 16 P S C is a Z86C83, 16 MHz, DIP, 0°C to +70°C, Plastic Standard Flow **Environmental Flow** Temperature Package Speed

> Product Number Zilog Prefix

Speed

16 = 16 MHz

Environmental

C = Plastic Standard

DS97DZ80700