Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Obsolete                                                        |

| Core Processor             | XCore                                                           |

| Core Size                  | 32-Bit 24-Core                                                  |

| Speed                      | 4000MIPS                                                        |

| Connectivity               | -                                                               |

| Peripherals                |                                                                 |

| Number of I/O              | 176                                                             |

| Program Memory Size        | 2MB (2M x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1M x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 0.95V ~ 3.6V                                                    |

| Data Converters            | -                                                               |

| Oscillator Type            | External                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 374-LFBGA                                                       |

| Supplier Device Package    | 374-FBGA (18x18)                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xlf224-1024-fb374-i40 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

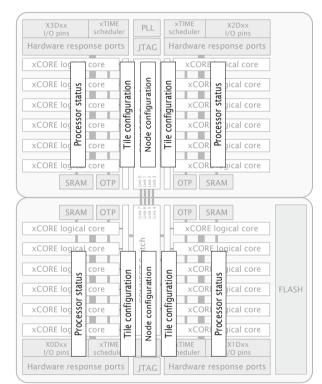

| 1   | xCORE Multicore Microcontrollers         |

|-----|------------------------------------------|

| 2   | XLF224-1024-FB374 Features               |

| 3   | Pin Configuration                        |

| 4   | Signal Description                       |

| 5   | Example Application Diagram              |

| 6   | Product Overview                         |

| 7   | PLL                                      |

| 8   | Boot Procedure                           |

| 9   | Memory                                   |

| 10  | JTAG                                     |

| 11  | Board Integration                        |

| 12  | DC and Switching Characteristics         |

| 13  | Package Information                      |

| 14  | Ordering Information                     |

| App | endices                                  |

| A   | Configuration of the XLF224-1024-FB374 3 |

| В   | Processor Status Configuration           |

| С   | Tile Configuration                       |

| D   | Node Configuration                       |

| E   | JTAG, xSCOPE and Debugging               |

| F   | Schematics Design Check List             |

| G   | PCB Layout Design Check List             |

| Н   | Associated Design Documentation          |

| 1   | Related Documentation                    |

| J   | Revision History                         |

### TO OUR VALUED CUSTOMERS

It is our intention to provide you with accurate and comprehensive documentation for the hardware and software components used in this product. To subscribe to receive updates, visit <a href="http://www.xmos.com/">http://www.xmos.com/</a>.

XMOS Ltd. is the owner or licensee of the information in this document and is providing it to you "AS IS" with no warranty of any kind, express or implied and shall have no liability in relation to its use. XMOS Ltd. makes no representation that the information, or any particular implementation thereof, is or will be free from any claims of infringement and again, shall have no liability in relation to any such claims.

XMOS and the XMOS logo are registered trademarks of XMOS Ltd in the United Kingdom and other countries, and may not be used without written permission. Company and product names mentioned in this document are the trademarks or registered trademarks of their respective owners.

| Signal         | Function                                      |                 |                 |                 |                   |                   | Tuno       | Proportion           |

|----------------|-----------------------------------------------|-----------------|-----------------|-----------------|-------------------|-------------------|------------|----------------------|

| X1D67          |                                               |                 |                 |                 |                   | 32A <sup>16</sup> | Type       | Properties<br>IO, PD |

| X1D67<br>X1D68 | $X_0 L2_{out}^1$                              |                 |                 |                 |                   | 32A <sup>17</sup> | I/0<br>I/0 | IO, PD               |

| X1D68<br>X1D69 | $X_0 L2_{out}^2$                              |                 |                 |                 |                   | 32A <sup>18</sup> |            |                      |

|                | X <sub>0</sub> L2 <sup>3</sup> <sub>out</sub> |                 |                 |                 |                   | 32A <sup>10</sup> | I/0        | IO, PD               |

| X1D70<br>X2D00 | X <sub>0</sub> L2 <sup>4</sup> <sub>out</sub> | 1A <sup>0</sup> |                 |                 |                   | 32A <sup>13</sup> | I/0        | IO, PD               |

| X2D00<br>X2D02 |                                               | 1A°             | 4A <sup>0</sup> | 8A <sup>0</sup> | 16A <sup>0</sup>  | 32A <sup>20</sup> | I/0        | IO, PD               |

|                |                                               |                 |                 | -               |                   | 32A <sup>23</sup> | I/0        | IO, PD               |

| X2D03          |                                               |                 | 4A <sup>1</sup> | 8A <sup>1</sup> | 16A <sup>1</sup>  |                   | I/0        | IO, PD               |

| X2D04          |                                               |                 | 4B <sup>0</sup> | 8A <sup>2</sup> | 16A <sup>2</sup>  | 32A <sup>22</sup> | I/0        | IO, PD               |

| X2D05          |                                               |                 | 4B <sup>1</sup> | 8A <sup>3</sup> | 16A <sup>3</sup>  | 32A <sup>23</sup> | I/O        | IO, PD               |

| X2D06          |                                               |                 | 4B <sup>2</sup> | 8A <sup>4</sup> | 16A <sup>4</sup>  | 32A <sup>24</sup> | I/O        | IO, PD               |

| X2D07          |                                               |                 | 4B <sup>3</sup> | 8A <sup>5</sup> | 16A <sup>5</sup>  | 32A <sup>25</sup> | I/O        | IO, PD               |

| X2D08          |                                               |                 | 4A <sup>2</sup> | 8A <sup>6</sup> | 16A <sup>6</sup>  | 32A <sup>26</sup> | I/O        | IO, PD               |

| X2D09          |                                               |                 | 4A <sup>3</sup> | 8A <sup>7</sup> | 16A <sup>7</sup>  | 32A <sup>27</sup> | I/O        | IO, PD               |

| X2D11          |                                               | 1D <sup>0</sup> |                 |                 |                   |                   | I/0        | IO, PD               |

| X2D12          |                                               | 1E <sup>0</sup> |                 |                 |                   |                   | I/0        | IO, PD               |

| X2D13          |                                               | 1F <sup>0</sup> |                 |                 |                   |                   | I/O        | IO, PD               |

| X2D14          |                                               |                 | 4C <sup>0</sup> | 8B <sup>0</sup> | 16A <sup>8</sup>  | 32A <sup>28</sup> | I/O        | IO, PD               |

| X2D15          |                                               |                 | 4C <sup>1</sup> | 8B1             | 16A <sup>9</sup>  | 32A <sup>29</sup> | I/O        | IO, PD               |

| X2D16          | X <sub>2</sub> L4 <sup>4</sup> in             |                 | 4D <sup>0</sup> | 8B <sup>2</sup> | 16A <sup>10</sup> |                   | I/0        | IO, PD               |

| X2D17          | X <sub>2</sub> L4 <sup>3</sup>                |                 | 4D <sup>1</sup> | 8B <sup>3</sup> | 16A <sup>11</sup> |                   | I/0        | IO, PD               |

| X2D18          | X <sub>2</sub> L4 <sup>2</sup> <sub>in</sub>  |                 | 4D <sup>2</sup> | 8B <sup>4</sup> | 16A <sup>12</sup> |                   | I/0        | IO, PD               |

| X2D19          | X <sub>2</sub> L4 <sup>1</sup> <sub>in</sub>  |                 | 4D <sup>3</sup> | 8B <sup>5</sup> | 16A <sup>13</sup> |                   | I/0        | IO, PD               |

| X2D20          |                                               |                 | 4C <sup>2</sup> | 8B <sup>6</sup> | 16A <sup>14</sup> | 32A <sup>30</sup> | I/0        | IO, PD               |

| X2D21          |                                               |                 | 4C <sup>3</sup> | 8B <sup>7</sup> | 16A <sup>15</sup> | 32A <sup>31</sup> | I/0        | IO, PD               |

| X2D22          |                                               | 1G <sup>0</sup> |                 |                 |                   |                   | I/0        | IO, PD               |

| X2D23          |                                               | 1H <sup>0</sup> |                 |                 |                   |                   | I/0        | IO, PD               |

| X2D24          | X <sub>2</sub> L7 <sup>0</sup>                | 110             |                 |                 |                   |                   | I/O        | IO, PD               |

| X2D25          | X <sub>2</sub> L7 <sup>0</sup> <sub>out</sub> | 1J <sup>0</sup> |                 |                 |                   |                   | I/0        | IO, PD               |

| X2D26          | X <sub>2</sub> L7 <sup>3</sup> <sub>out</sub> |                 | 4E <sup>0</sup> | 8C <sup>0</sup> | 16B <sup>0</sup>  |                   | I/0        | IO, PD               |

| X2D27          | X <sub>2</sub> L7 <sup>4</sup> <sub>out</sub> |                 | 4E <sup>1</sup> | 8C <sup>1</sup> | 16B <sup>1</sup>  |                   | I/0        | IO, PD               |

| X2D28          |                                               |                 | 4F <sup>0</sup> | 8C <sup>2</sup> | 16B <sup>2</sup>  |                   | I/0        | IO, PD               |

| X2D29          |                                               |                 | 4F <sup>1</sup> | 8C <sup>3</sup> | 16B <sup>3</sup>  |                   | I/O        | IO, PD               |

| X2D30          |                                               |                 | 4F <sup>2</sup> | 8C <sup>4</sup> | 16B <sup>4</sup>  |                   | I/O        | IO, PD               |

| X2D31          |                                               |                 | 4F <sup>3</sup> | 8C <sup>5</sup> | 16B <sup>5</sup>  |                   | I/O        | IO, PD               |

| X2D32          |                                               |                 | 4E <sup>2</sup> | 8C <sup>6</sup> | 16B <sup>6</sup>  |                   | I/O        | IO, PD               |

| X2D33          |                                               |                 | 4E <sup>3</sup> | 8C <sup>7</sup> | 16B <sup>7</sup>  |                   | I/O        | IO, PD               |

| X2D34          | X <sub>2</sub> L7 <sup>1</sup>                | 1K <sup>0</sup> |                 |                 |                   |                   | I/O        | IO, PD               |

| X2D35          | X <sub>2</sub> L7 <sup>2</sup> <sub>out</sub> | 1L0             |                 |                 |                   |                   | I/O        | IO, PD               |

| X2D36          | 112 - 1 Out                                   | 1M <sup>0</sup> |                 | 8D <sup>0</sup> | 16B <sup>8</sup>  |                   | I/O        | IO, PD               |

| X2D30<br>X2D49 | X <sub>2</sub> L5 <sup>4</sup>                | 1141            |                 | 00              | TOD               | 32A <sup>0</sup>  | 1/0        | IO, PD               |

| X2D49<br>X2D50 | $X_2L5_{in}^3$<br>$X_2L5_{in}^3$              |                 |                 |                 |                   | 32A <sup>1</sup>  | I/O        | IO, PD               |

| X2D50<br>X2D51 | $X_2LS_{in}^2$<br>$X_2LS_{in}^2$              |                 |                 |                 |                   | 32A <sup>2</sup>  | I/O        | IO, PD               |

| X2D51<br>X2D52 |                                               |                 |                 |                 |                   | 32A <sup>-</sup>  | I/O        | IO, PD               |

| 72032          | X <sub>2</sub> L5 <sup>1</sup><br>in          |                 |                 |                 |                   | 52A5              | 1/0        |                      |

|                |                                               |                 |                 |                 |                   |                   |            | (continued)          |

-XMOS<sup>®</sup>-

## XLF224-1024-FB374 Datasheet

| Signal | Function                                         | Туре | Properties |

|--------|--------------------------------------------------|------|------------|

| X3D32  | 4E <sup>2</sup> 8C <sup>6</sup> 16B <sup>6</sup> | I/0  | IOT, PD    |

| X3D33  | 4E <sup>3</sup> 8C <sup>7</sup> 16B <sup>7</sup> | I/0  | IOT, PD    |

| X3D40  | 8D <sup>4</sup> 16B <sup>12</sup>                | I/0  | IOT, PD    |

| X3D41  | 8D <sup>5</sup> 16B <sup>13</sup>                | I/0  | IOT, PD    |

| X3D42  | 8D <sup>6</sup> 16B <sup>14</sup>                | I/0  | IOT, PD    |

| X3D43  | 8D <sup>7</sup> 16B <sup>15</sup>                | I/0  | IOT, PD    |

|         | System pins (4)     |       |            |  |  |  |  |  |  |  |  |

|---------|---------------------|-------|------------|--|--|--|--|--|--|--|--|

| Signal  | Function            | Туре  | Properties |  |  |  |  |  |  |  |  |

| CLK     | PLL reference clock | Input | IO, PD, ST |  |  |  |  |  |  |  |  |

| DEBUG_N | Multi-chip debug    | I/O   | IO, PU     |  |  |  |  |  |  |  |  |

| MODE0   | Boot mode select    | Input | PU         |  |  |  |  |  |  |  |  |

| MODE1   | Boot mode select    | Input | PU         |  |  |  |  |  |  |  |  |

Figure 7 also lists the values of OD, F and R, which are the registers that define the ratio of the tile frequency to the oscillator frequency:

$$F_{core} = F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \times \frac{1}{OD+1}$$

*OD*, *F* and *R* must be chosen so that  $0 \le R \le 63$ ,  $0 \le F \le 4095$ ,  $0 \le OD \le 7$ , and  $260MHz \le F_{osc} \times \frac{F+1}{2} \times \frac{1}{R+1} \le 1.3GHz$ . The *OD*, *F*, and *R* values can be modified by writing to the digital node PLL configuration register.

The MODE pins must be held at a static value during and after deassertion of the system reset.

If a different tile frequency is required (eg, 500 MHz), then the PLL must be reprogrammed after boot to provide the required tile frequency. The XMOS tools perform this operation by default. Further details on configuring the clock can be found in the xCORE-200 Clock Frequency Control document.

# 8 Boot Procedure

The device is kept in reset by driving RST\_N low. When in reset, all GPIO pins have a pull-down enabled. The processor must be held in reset until VDDIOL is in spec for at least 1 ms. When the device is taken out of reset by releasing RST\_N the processor starts its internal reset process. After 15-150  $\mu$ s (depending on the input clock) the processor boots.

Pin X2D06 must be pulled high with an external pull-up whilst the chip comes out of reset, to ensure that tile 2 will boot from link. X2D04, X2D05, and X2D07 should be kept low whilst the chip comes out of reset.

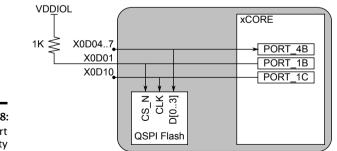

The device boots from a QSPI flash (IS25LQ016B) that is embedded in the device. The QSPI flash is connected to the ports on Tile 0 as shown in Figure 8. An external 1K resistor must connect X0D01 to VDDIOL. X0D10 should ideally not be connected. If X0D10 is connected, then a 150 ohm series resistor close to the device is recommended. X0D04..X0D07 should be not connected.

The xCORE Tile boot procedure is illustrated in Figure 9. If bit 5 of the security register (*see*  $\S9.1$ ) is set, the device boots from OTP. Otherwise, the device boots from the internal flash.

Figure 8: QSPI port connectivity

| Feature              | Bit  | Description                                                                                                                                                                                                                                |  |  |  |  |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Disable JTAG         | 0    | The JTAG interface is disabled, making it impossible<br>for the tile state or memory content to be accessed<br>via the JTAG interface.                                                                                                     |  |  |  |  |

| Disable Link access  | 1    | Other tiles are forbidden access to the processor state<br>via the system switch. Disabling both JTAG and Link<br>access transforms an xCORE Tile into a "secure island"<br>with other tiles free for non-secure user application<br>code. |  |  |  |  |

| Secure Boot          | 5    | The xCORE Tile is forced to boot from address 0 of<br>the OTP, allowing the xCORE Tile boot ROM to be<br>bypassed ( <i>see</i> §8).                                                                                                        |  |  |  |  |

| Redundant rows       | 7    | Enables redundant rows in OTP.                                                                                                                                                                                                             |  |  |  |  |

| Sector Lock 0        | 8    | Disable programming of OTP sector 0.                                                                                                                                                                                                       |  |  |  |  |

| Sector Lock 1        | 9    | Disable programming of OTP sector 1.                                                                                                                                                                                                       |  |  |  |  |

| Sector Lock 2        | 10   | Disable programming of OTP sector 2.                                                                                                                                                                                                       |  |  |  |  |

| Sector Lock 3        | 11   | Disable programming of OTP sector 3.                                                                                                                                                                                                       |  |  |  |  |

| OTP Master Lock      | 12   | Disable OTP programming completely: disables up<br>dates to all sectors and security register.                                                                                                                                             |  |  |  |  |

| Disable JTAG-OTP     | 13   | Disable all (read & write) access from the JTAG inter face to this OTP.                                                                                                                                                                    |  |  |  |  |

| Disable Global Debug | 14   | Disables access to the DEBUG_N pin.                                                                                                                                                                                                        |  |  |  |  |

|                      | 2115 | General purpose software accessable security registe available to end-users.                                                                                                                                                               |  |  |  |  |

|                      | 3122 | General purpose user programmable JTAG UserIE code extension.                                                                                                                                                                              |  |  |  |  |

Figure 10: Security register features

register is loaded from the OTP on power up. All additional data in OTP is copied from the OTP to SRAM and executed first on the processor.

The OTP memory is programmed using three special I/O ports: the OTP address port is a 16-bit port with resource ID 0x100200, the OTP data is written via a 32-bit port with resource ID 0x200100, and the OTP control is on a 16-bit port with ID 0x100300. Programming is performed through libotp and xburn.

### 9.2 SRAM

Each xCORE Tile integrates a single 256KBSRAM bank for both instructions and data. All internal memory is 32 bits wide, and instructions are either 16-bit or 32-bit. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one tile clock cycle. There is no dedicated external memory interface, although data memory can be expanded through appropriate use of the ports.

-XMOS-

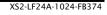

XS2-LF24A-1024-FB374

The JTAG usercode register can be read by using the USERCODE instruction. Its contents are specified in Figure 13. The OTP User ID field is read from bits [22:31] of the security register on xCORE Tile 0, *see* §9.1 (all zero on unprogrammed devices).

Figure 13: USERCODE return value

|         | Bit | Bit31 Usercode Register Bit0 |   |   |      |      |    |   |        |   |     | it0 |                  |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|---------|-----|------------------------------|---|---|------|------|----|---|--------|---|-----|-----|------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 3:<br>「 |     |                              |   | 0 | TP U | lser | ID |   | Unused |   |     |     | Silicon Revision |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| E       | 0   | 0                            | 0 | 0 | 0    | 0    | 0  | 0 | 0      | 0 | 0   | 0   | 0                | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| e       |     |                              | 0 |   |      | (    | )  |   |        | ( | ) 2 |     |                  | 2 | 8 |   |   | 0 |   |   | 0 |   |   | 0 |   |   |   |   |   |   |   |   |

# 11 Board Integration

The device has the following power supply pins:

- ▶ VDD pins for the xCORE Tile

- ▶ VDDIO pins for the I/O lines

- PLL\_AVDD pins for the PLL

- OTP\_VCC pins for the OTP

Several pins of each type are provided to minimize the effect of inductance within the package, all of which must be connected. The power supplies must be brought up monotonically and input voltages must not exceed specification at any time.

The VDD supply must ramp from 0V to its final value within 10 ms to ensure correct startup.

The VDDIO and OTP\_VCC supply must ramp to its final value before VDD reaches 0.4 V.

The PLL\_AVDD supply should be separated from the other noisier supplies on the board. The PLL requires a very clean power supply, and a low pass filter (for example, a  $2.2 \Omega$  resistor and 100 nF multi-layer ceramic capacitor) is recommended on this pin.

The following ground pins are provided:

- PLL\_AGND for PLL\_AVDD

- GND for all other supplies

All ground pins must be connected directly to the board ground.

The VDD and VDDIO supplies should be decoupled close to the chip by several 100 nF low inductance multi-layer ceramic capacitors between the supplies and GND (for example, 100nF 0402 for every other supply pin). The ground side of the decoupling capacitors should have as short a path back to the GND pins as possible. A bulk decoupling capacitor of at least 10 uF should be placed on each of these supplies.

# 12 DC and Switching Characteristics

| Symbol   | Parameter                                     | MIN   | ТҮР  | MAX   | UNITS | Notes |

|----------|-----------------------------------------------|-------|------|-------|-------|-------|

| VDD      | Tile DC supply voltage                        | 0.95  | 1.00 | 1.05  | V     |       |

| VDDIO    | I/O supply voltage                            | 2.30  | 3.30 | 3.60  | V     |       |

| VDDIOT_0 | I/O supply voltage                            | 2.25  | 3.30 | 3.60  | V     |       |

| VDDIOT_1 | I/O supply voltage                            | 2.25  | 3.30 | 3.60  | V     |       |

| USB_VDD  | USB tile DC supply voltage                    | 0.95  | 1.00 | 1.05  | V     |       |

| VDD33    | Peripheral supply                             | 3.135 | 3.30 | 3.465 | V     |       |

| PLL_AVDD | PLL analog supply                             | 0.95  | 1.00 | 1.05  | V     |       |

| CI       | xCORE Tile I/O load<br>capacitance            |       |      | 25    | pF    |       |

| Та       | Ambient operating<br>temperature (Commercial) | 0     |      | 70    | °C    |       |

|          | Ambient operating<br>temperature (Industrial) | -40   |      | 85    | °C    |       |

| Tj       | Junction temperature                          |       |      | 125   | °C    |       |

| Tstg     | Storage temperature                           | -65   |      | 150   | °C    |       |

## 12.1 Operating Conditions

Figure 14: Operating conditions

## 12.2 DC Characteristics, VDDIO=3V3

| Symbol | Parameter                                | MIN   | ТҮР | MAX  | UNITS | Notes |

|--------|------------------------------------------|-------|-----|------|-------|-------|

| V(IH)  | Input high voltage                       | 2.00  |     | 3.60 | V     | А     |

| V(IL)  | Input low voltage                        | -0.30 |     | 0.70 | V     | А     |

| V(OH)  | Output high voltage                      | 2.20  |     |      | V     | В, С  |

| V(OL)  | Output low voltage                       |       |     | 0.40 | V     | В, С  |

| I(PU)  | Internal pull-up current (Vin=0V)        | -100  |     |      | μA    | D     |

| I(PD)  | Internal pull-down current<br>(Vin=3.3V) |       |     | 100  | μA    | D     |

| I(LC)  | Input leakage current                    | -10   |     | 10   | μA    |       |

Figure 15: DC characteristics

A All pins except power supply pins.

B Pins X1D40, X1D41, X1D42, X1D43, X1D26, X1D27, X3D40, X3D41, X3D42, X3D43, X3D26, and X3D27 are nominal 8 mA drivers, the remainder of the general-purpose I/Os are 4 mA.

C Measured with 4 mA drivers sourcing 4 mA, 8 mA drivers sourcing 8 mA.

D Used to guarantee logic state for an I/O when high impedance. The internal pull-ups/pull-downs should not be used to pull external circuitry. In order to pull the pin to the opposite state, a 4K7 resistor is recommended to overome the internal pull current.

# Appendices

# A Configuration of the XLF224-1024-FB374

The device is configured through banks of registers, as shown in Figure 26.

### Figure 26: Registers

The following communication sequences specify how to access those registers. Any messages transmitted contain the most significant 24 bits of the channel-end to which a response is to be sent. This comprises the node-identifier and the channel number within the node. if no response is required on a write operation, supply 24-bits with the last 8-bits set, which suppresses the reply message. Any multi-byte data is sent most significant byte first.

# A.1 Accessing a processor status register

The processor status registers are accessed directly from the processor instruction set. The instructions GETPS and SETPS read and write a word. The register number should be translated into a processor-status resource identifier by shifting the register number left 8 places, and ORing it with 0x0B. Alternatively, the functions getps(reg) and setps(reg,value) can be used from XC.

### B.4 xCORE Tile boot status: 0x03

This read-only register describes the boot status of the xCORE tile.

| Bits  | Perm | Init | Description                                               |

|-------|------|------|-----------------------------------------------------------|

| 31:24 | RO   | -    | Reserved                                                  |

| 23:16 | RO   |      | Processor number.                                         |

| 15:9  | RO   | -    | Reserved                                                  |

| 8     | RO   |      | Overwrite BOOT_MODE.                                      |

| 7:6   | RO   | -    | Reserved                                                  |

| 5     | RO   |      | Indicates if core1 has been powered off                   |

| 4     | RO   |      | Cause the ROM to not poll the OTP for correct read levels |

| 3     | RO   |      | Boot ROM boots from RAM                                   |

| 2     | RO   |      | Boot ROM boots from JTAG                                  |

| 1:0   | RO   |      | The boot PLL mode pin value.                              |

0x03: xCORE Tile boot status

# B.5 Security configuration: 0x05

Copy of the security register as read from OTP.

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31    | RW   |      | Disables write permission on this register                  |

| 30:15 | RO   | -    | Reserved                                                    |

| 14    | RW   |      | Disable access to XCore's global debug                      |

| 13    | RO   | -    | Reserved                                                    |

| 12    | RW   |      | lock all OTP sectors                                        |

| 11:8  | RW   |      | lock bit for each OTP sector                                |

| 7     | RW   |      | Enable OTP reduanacy                                        |

| 6     | RO   | -    | Reserved                                                    |

| 5     | RW   |      | Override boot mode and read boot image from OTP             |

| 4     | RW   |      | Disable JTAG access to the PLL/BOOT configuration registers |

| 3:1   | RO   | -    | Reserved                                                    |

| 0     | RW   |      | Disable access to XCore's JTAG debug TAP                    |

**0x05:** Security configuration

|                                       | Bits  | Perm           | Init | Description                                        |

|---------------------------------------|-------|----------------|------|----------------------------------------------------|

|                                       | 31:24 | CRO            |      | Processor ID of this XCore.                        |

| 0x00:                                 | 23:16 | CRO            |      | Number of the node in which this XCore is located. |

| Device                                | 15:8  | CRO            |      | XCore revision.                                    |

| identification 7:0 CRO XCore version. |       | XCore version. |      |                                                    |

## C.2 xCORE Tile description 1: 0x01

This register describes the number of logical cores, synchronisers, locks and channel ends available on this xCORE tile.

| Bits  | Perm | Init | Description              |

|-------|------|------|--------------------------|

| 31:24 | CRO  |      | Number of channel ends.  |

| 23:16 | CRO  |      | Number of the locks.     |

| 15:8  | CRO  |      | Number of synchronisers. |

| 7:0   | RO   | -    | Reserved                 |

### C.3 xCORE Tile description 2: 0x02

This register describes the number of timers and clock blocks available on this xCORE tile.

0x02: xCORE Tile description 2

0x01: xCORE Tile description 1

|      | Bits  | Perm | Init | Description             |

|------|-------|------|------|-------------------------|

| x02: | 31:16 | RO   | -    | Reserved                |

| Tile | 15:8  | CRO  |      | Number of clock blocks. |

| on 2 | 7:0   | CRO  |      | Number of timers.       |

# C.4 Control PSwitch permissions to debug registers: 0x04

-XMOS-

This register can be used to control whether the debug registers (marked with permission CRW) are accessible through the tile configuration registers. When this bit is set, write -access to those registers is disabled, preventing debugging of the xCORE tile over the interconnect.

| Bits  | Perm | Init | Description                                                 |

|-------|------|------|-------------------------------------------------------------|

| 31    | CRO  |      | Disables write permission on this register                  |

| 30:15 | RO   | -    | Reserved                                                    |

| 14    | CRO  |      | Disable access to XCore's global debug                      |

| 13    | RO   | -    | Reserved                                                    |

| 12    | CRO  |      | lock all OTP sectors                                        |

| 11:8  | CRO  |      | lock bit for each OTP sector                                |

| 7     | CRO  |      | Enable OTP reduanacy                                        |

| 6     | RO   | -    | Reserved                                                    |

| 5     | CRO  |      | Override boot mode and read boot image from OTP             |

| 4     | CRO  |      | Disable JTAG access to the PLL/BOOT configuration registers |

| 3:1   | RO   | -    | Reserved                                                    |

| 0     | CRO  |      | Disable access to XCore's JTAG debug TAP                    |

0x07: Security configuration

# C.8 Debug scratch: 0x20 .. 0x27

A set of registers used by the debug ROM to communicate with an external debugger, for example over the switch. This is the same set of registers as the Debug Scratch registers in the processor status.

0x20 .. 0x27 Debug scratch

| 0x27:<br>ebug | Bits | Perm | Init | Description |

|---------------|------|------|------|-------------|

| ratch         | 31:0 | CRW  |      | Value.      |

# C.9 PC of logical core 0: 0x40

Value of the PC of logical core 0.

0x40 PC of logical core 0

| <b>0x40:</b><br>gical | Bits | Perm | Init | Description |  |

|-----------------------|------|------|------|-------------|--|

| ore 0                 | 31:0 | CRO  |      | Value.      |  |

-XMOS

# C.10 PC of logical core 1: 0x41

Value of the PC of logical core 1.

**0x41:** PC of logical core 1

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

## C.11 PC of logical core 2: 0x42

Value of the PC of logical core 2.

0x42: PC of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

# C.12 PC of logical core 3: 0x43

Value of the PC of logical core 3.

| 0x43:         |      |      |      |             |

|---------------|------|------|------|-------------|

| PC of logical | Bits | Perm | Init | Description |

| core 3        | 31:0 | CRO  |      | Value.      |

### C.13 PC of logical core 4: 0x44

Value of the PC of logical core 4.

**0x44**: PC of logical core 4

| <b>0x44:</b><br>ogical | Bits | Perm | Init | Description |

|------------------------|------|------|------|-------------|

| ore 4                  | 31:0 | CRO  |      | Value.      |

# C.14 PC of logical core 5: 0x45

Value of the PC of logical core 5.

**0x45:** PC of logical core 5

| -   | Bits | Perm | Init | Description |

|-----|------|------|------|-------------|

| . [ | 31:0 | CRO  |      | Value.      |

Bits

31:0

## C.15 PC of logical core 6: 0x46

Value of the PC of logical core 6.

**0x46:** PC of logical core 6

Perm

Init

Description

CRO

Value.

# C.16 PC of logical core 7: 0x47

Value of the PC of logical core 7.

0x47 PC of logical core 7

| 0x47:<br>gical | Bits | Perm | Init | Description |

|----------------|------|------|------|-------------|

| ore 7          | 31:0 | CRO  |      | Value.      |

# C.17 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| <b>0x60:</b><br>ogical | Bits | Perm | Init | Description |  |

|------------------------|------|------|------|-------------|--|

| ore 0                  | 31:0 | CRO  |      | Value.      |  |

# C.18 SR of logical core 1: 0x61

Value of the SR of logical core 1

**0x61** SR of logical core 1

| 61:<br>cal | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| e 1        | 31:0 | CRO  |      | Value.      |

# C.19 SR of logical core 2: 0x62

Value of the SR of logical core 2

48

**0x62** SR of logical core 2

| <b>x62:</b><br>gical | Bits | Perm | Init | Description |

|----------------------|------|------|------|-------------|

| re 2                 | 31:0 | CRO  |      | Value.      |

# C.20 SR of logical core 3: 0x63

Value of the SR of logical core 3

0x63: SR of logical core 3

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

# C.21 SR of logical core 4: 0x64

Value of the SR of logical core 4

| 0x64:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 4        | 31:0 | CRO  |      | Value.      |

### C.22 SR of logical core 5: 0x65

Value of the SR of logical core 5

**0x65** SR of logical core 5

| <b>x65:</b><br>gical | Bits | Perm | Init | Description |

|----------------------|------|------|------|-------------|

| ore 5                | 31:0 | CRO  |      | Value.      |

# C.23 SR of logical core 6: 0x66

Value of the SR of logical core 6

**0x66:** SR of logical core 6

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | CRO  |      | Value.      |

# C.24 SR of logical core 7: 0x67

Value of the SR of logical core 7

| 0x67:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 7        | 31:0 | CRO  |      | Value.      |

## D.8 System JTAG device ID register: 0x09

**0x09** System JTAG device ID register

|           | Bits  | Perm | Init | Description |

|-----------|-------|------|------|-------------|

| -         | 31:28 | RO   |      |             |

| <b>):</b> | 27:12 | RO   |      |             |

| 2         | 11:1  | RO   |      |             |

| r         | 0     | RO   |      |             |

### D.9 System USERCODE register: 0x0A

**0x0A** System USERCODE register

| <b>4:</b><br>n | Bits  | Perm | Init | Description                                |

|----------------|-------|------|------|--------------------------------------------|

| E              | 31:18 | RO   |      | JTAG USERCODE value programmed into OTP SR |

| er             | 17:0  | RO   |      | metal fixable ID code                      |

### D.10 Directions 0-7: 0x0C

This register contains eight directions, for packets with a mismatch in bits 7..0 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

| Bits  | Perm | Init | Description                                     |

|-------|------|------|-------------------------------------------------|

| 31:28 | RW   | 0    | The direction for packets whose dimension is 7. |

| 27:24 | RW   | 0    | The direction for packets whose dimension is 6. |

| 23:20 | RW   | 0    | The direction for packets whose dimension is 5. |

| 19:16 | RW   | 0    | The direction for packets whose dimension is 4. |

| 15:12 | RW   | 0    | The direction for packets whose dimension is 3. |

| 11:8  | RW   | 0    | The direction for packets whose dimension is 2. |

| 7:4   | RW   | 0    | The direction for packets whose dimension is 1. |

| 3:0   | RW   | 0    | The direction for packets whose dimension is 0. |

0x0C: Directions 0-7

### D.11 Directions 8-15: 0x0D

This register contains eight directions, for packets with a mismatch in bits 15..8 of the node-identifier. The direction in which a packet will be routed is goverened by the most significant mismatching bit.

-XMOS-

# E JTAG, xSCOPE and Debugging

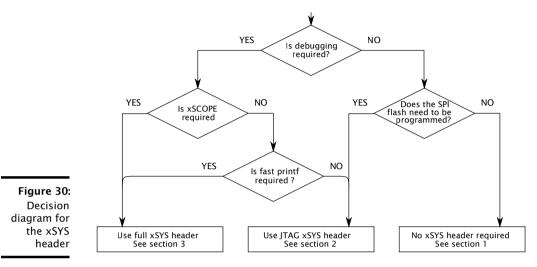

If you intend to design a board that can be used with the XMOS toolchain and xTAG debugger, you will need an xSYS header on your board. Figure 30 shows a decision diagram which explains what type of xSYS connectivity you need. The three subsections below explain the options in detail.

E.1 No xSYS header

The use of an xSYS header is optional, and may not be required for volume production designs. However, the XMOS toolchain expects the xSYS header; if you do not have an xSYS header then you must provide your own method for writing to flash/OTP and for debugging.

### E.2 JTAG-only xSYS header

The xSYS header connects to an xTAG debugger, which has a 20-pin 0.1" female IDC header. The design will hence need a male IDC header. We advise to use a boxed header to guard against incorrect plug-ins. If you use a 90 degree angled header, make sure that pins 2, 4, 6, ..., 20 are along the edge of the PCB.

Connect pins 4, 8, 12, 16, 20 of the xSYS header to ground, and then connect:

- ▶ TDI to pin 5 of the xSYS header

- TMS to pin 7 of the xSYS header

- TCK to pin 9 of the xSYS header

- DEBUG\_N to pin 11 of the xSYS header

TDO to pin 13 of the xSYS header

The RST\_N net should be open-drain, active-low, and have a pull-up to VDDIO.

### E.3 Full xSYS header

For a full xSYS header you will need to connect the pins as discussed in Section E.2, and then connect a 2-wire xCONNECT Link to the xSYS header. The links can be found in the Signal description table (Section 4): they are labelled XL0, XL1, etc in the function column. The 2-wire link comprises two inputs and outputs, labelled  ${}^{1}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{in}$ , and  ${}^{1}_{in}$ . For example, if you choose to use XL0 for xSCOPE I/O, you need to connect up XL0 ${}^{1}_{out}$ , XL0 ${}^{0}_{out}$ , XL0 ${}^{1}_{in}$ , XL0 ${}^{1}_{in}$  as follows:

- XL0<sup>1</sup><sub>out</sub> (X0D43) to pin 6 of the xSYS header with a 33R series resistor close to the device.

- XL0<sup>0</sup><sub>out</sub> (X0D42) to pin 10 of the xSYS header with a 33R series resistor close to the device.

- ▶ XL0<sup>0</sup><sub>in</sub> (X0D41) to pin 14 of the xSYS header.

- >  $XLO_{in}^{1}$  (X0D40) to pin 18 of the xSYS header.

# G PCB Layout Design Check List

✓ This section is a checklist for use by PCB designers using the XS2-LF24A-1024-FB374. Each of the following sections contains items to check for each design.

### G.1 Ground Plane

- Each ground ball has a via to minimize impedance and conduct heat away from the device. (Section 11.2)

- Other than ground vias, there are no (or only a few) vias underneath or closely around the device. This create a good, solid, ground plane.

### G.2 Power supply decoupling

- The decoupling capacitors are all placed close to a supply pin (Section 11).

- $\Box$  The decoupling capacitors are spaced around the device (Section 11).

- The ground side of each decoupling capacitor has a direct path back to the center ground of the device.

### G.3 PLL\_AVDD

The PLL\_AVDD filter (especially the capacitor) is placed close to the PLL\_AVDD pin (Section 11).

# H Associated Design Documentation

| Document Title                                  | Information                               | Document Number |

|-------------------------------------------------|-------------------------------------------|-----------------|

| Estimating Power Consumption For XS1-LF Devices | Power consumption                         | X4271           |

| Programming XC on XMOS Devices                  | Timers, ports, clocks, cores and channels | X9577           |

| xTIMEcomposer User Guide                        | Compilers, assembler and linker/mapper    | X3766           |

|                                                 | Timing analyzer, xScope, debugger         |                 |

|                                                 | Flash and OTP programming utilities       |                 |

# I Related Documentation

| Document Title                                   | Information                         | Document Number |

|--------------------------------------------------|-------------------------------------|-----------------|

| The XMOS XS1 Architecture                        | ISA manual                          | X7879           |

| XS1 Port I/O Timing                              | Port timings                        | X5821           |

| xCONNECT Architecture                            | Link, switch and system information | X4249           |

| XS1-LF Link Performance and Design<br>Guidelines | Link timings                        | X2999           |

| XS1-LF Clock Frequency Control                   | Advanced clock control              | X1433           |

| XS1-L Active Power Conservation                  | Low-power mode during idle          | X7411           |